#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc502t-i-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

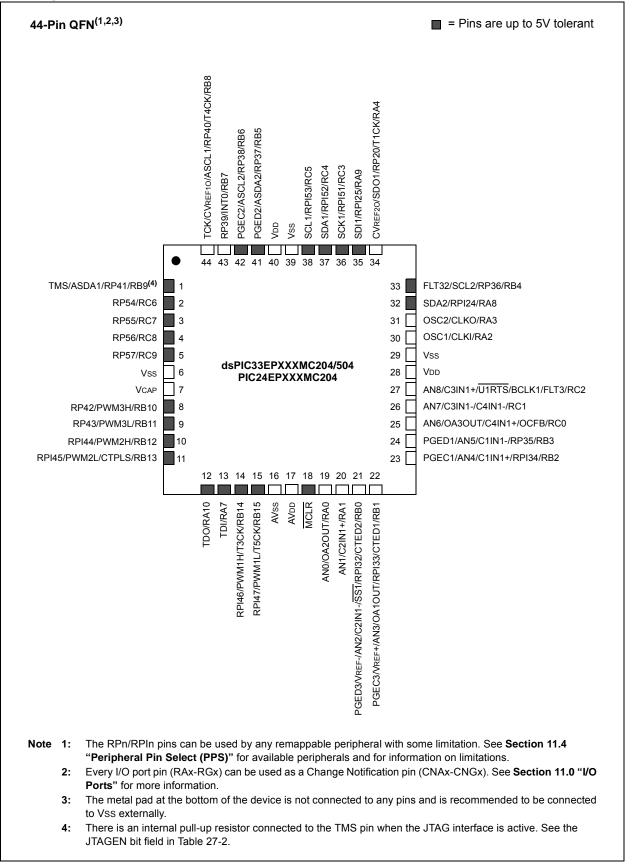

### Pin Diagrams (Continued)

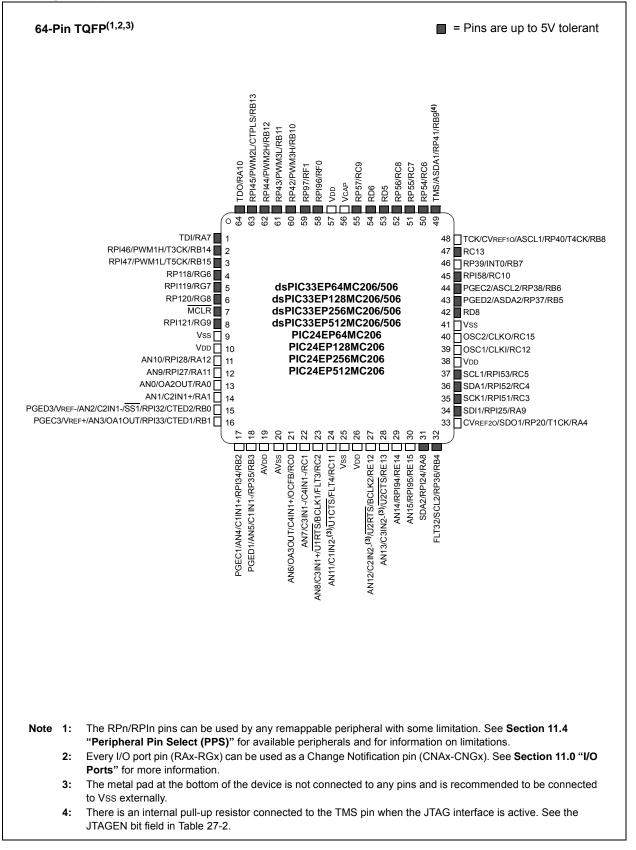

### Pin Diagrams (Continued)

## 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

#### 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

#### 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

#### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

#### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

#### REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

#### REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      | —     | —     | _     | _          | _     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|        |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          | •                                                                                                                                       |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

#### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 17-7: VEL1CNT: VELOCITY COUNTER 1 REGISTER

| R/W-0                                                 | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|-------------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|

|                                                       |       |       | VELC  | NT<15:8>                           |       |       |       |

| bit 15                                                |       |       |       |                                    |       |       | bit 8 |

|                                                       |       |       |       |                                    |       |       |       |

| R/W-0                                                 | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                       |       |       | VELC  | NT<7:0>                            |       |       |       |

| bit 7                                                 |       |       |       |                                    |       |       | bit 0 |

|                                                       |       |       |       |                                    |       |       |       |

| Legend:                                               |       |       |       |                                    |       |       |       |

| R = Readable bit W = Writable bit                     |       |       | oit   | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is clear |       |       | ared  | x = Bit is unkr                    | nown  |       |       |

bit 15-0 VELCNT<15:0>: Velocity Counter bits

#### REGISTER 17-8: INDX1CNTH: INDEX COUNTER 1 HIGH WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------------------|----------|-------|-------|-------|

|        |       |       | INDXCN <sup>®</sup> | T<31:24> |       |       |       |

| bit 15 |       |       |                     |          |       |       | bit 8 |

|        |       |       |                     |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | INDXCN              | T<23:16> |       |       |       |

| bit 7  |       |       |                     |          |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 INDXCNT<31:16>: High Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

#### REGISTER 17-9: INDX1CNTL: INDEX COUNTER 1 LOW WORD REGISTER

'1' = Bit is set

| <b>Legend:</b><br>R = Readable b | it    | W = Writable bit |        | U = Unimplen | nented bit, reac | l as '0' |       |

|----------------------------------|-------|------------------|--------|--------------|------------------|----------|-------|

| bit 7                            |       |                  |        |              |                  |          | bit 0 |

|                                  |       |                  | INDXC  | NT<7:0>      |                  |          |       |

| R/W-0                            | R/W-0 | R/W-0            | R/W-0  | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| bit 15                           |       |                  |        |              |                  |          | bit 8 |

|                                  |       |                  | INDXCN | NT<15:8>     |                  |          |       |

| R/W-0                            | R/W-0 | R/W-0            | R/W-0  | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

'0' = Bit is cleared

bit 15-0 INDXCNT<15:0>: Low Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

-n = Value at POR

x = Bit is unknown

## 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This insures          |  | that  | the       | first | fr | ame |

|-------|-----------------------|--|-------|-----------|-------|----|-----|

|       | transmission a        |  | after | initializ | ation | is | not |

|       | shifted or corrupted. |  |       |           |       |    |     |

- 2. In Non-Framed 3-Wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose Sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPIx specifications in Section 30.0 "Electrical Characteristics" for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPIx data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

#### 18.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 18.2.1 KEY RESOURCES

- "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

| U-0          | U-0                                                        | R-0                        | R-0   | R-0                  | R-0              | R-0                | R-0   |  |  |  |

|--------------|------------------------------------------------------------|----------------------------|-------|----------------------|------------------|--------------------|-------|--|--|--|

| _            |                                                            | FBP5                       | FBP4  | FBP3                 | FBP2             | FBP1               | FBP0  |  |  |  |

| bit 15       |                                                            |                            |       |                      |                  |                    | bit 8 |  |  |  |

|              |                                                            |                            |       |                      |                  |                    |       |  |  |  |

| U-0          | U-0                                                        | R-0                        | R-0   | R-0                  | R-0              | R-0                | R-0   |  |  |  |

|              |                                                            | FNRB5                      | FNRB4 | FNRB3                | FNRB2            | FNRB1              | FNRB0 |  |  |  |

| bit 7        |                                                            |                            |       |                      |                  |                    | bit ( |  |  |  |

| Legend:      |                                                            |                            |       |                      |                  |                    |       |  |  |  |

| R = Readab   | le bit                                                     | W = Writable               | bit   | U = Unimplen         | nented bit, read | d as '0'           |       |  |  |  |

| -n = Value a | t POR                                                      | '1' = Bit is set           |       | '0' = Bit is cleared |                  | x = Bit is unknown |       |  |  |  |

|              |                                                            |                            |       |                      |                  |                    |       |  |  |  |

| bit 15-14    | Unimpleme                                                  | ented: Read as '           | 0'    |                      |                  |                    |       |  |  |  |

| bit 13-8     | FBP<5:0>: FIFO Buffer Pointer bits                         |                            |       |                      |                  |                    |       |  |  |  |

|              | 011111 = RB31 buffer                                       |                            |       |                      |                  |                    |       |  |  |  |

|              | 011110 <b>= F</b>                                          | RB30 buffer                |       |                      |                  |                    |       |  |  |  |

|              | •                                                          |                            |       |                      |                  |                    |       |  |  |  |

|              | •                                                          |                            |       |                      |                  |                    |       |  |  |  |

|              | •<br>000001 = TRB1 buffer                                  |                            |       |                      |                  |                    |       |  |  |  |

|              | 000001 = 1 RB1 buffer<br>000000 = TRB0 buffer              |                            |       |                      |                  |                    |       |  |  |  |

| bit 7-6      | Unimpleme                                                  | ented: Read as '           | 0'    |                      |                  |                    |       |  |  |  |

| bit 5-0      | <b>FNRB&lt;5:0&gt;:</b> FIFO Next Read Buffer Pointer bits |                            |       |                      |                  |                    |       |  |  |  |

|              | 011111 = RB31 buffer                                       |                            |       |                      |                  |                    |       |  |  |  |

|              | 011110 = RB30 buffer                                       |                            |       |                      |                  |                    |       |  |  |  |

|              | •                                                          |                            |       |                      |                  |                    |       |  |  |  |

|              | •                                                          |                            |       |                      |                  |                    |       |  |  |  |

|              | •                                                          |                            |       |                      |                  |                    |       |  |  |  |

|              |                                                            |                            |       |                      |                  |                    |       |  |  |  |

|              |                                                            | FRB1 buffer<br>FRB0 buffer |       |                      |                  |                    |       |  |  |  |

#### REGISTER 21-5: CxFIFO: ECANx FIFO STATUS REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |                     |                       |                                    |       |        |       |  |

|------------------------------------|-------|---------------------|-----------------------|------------------------------------|-------|--------|-------|--|

|                                    | R/W-0 | R/W-0               | R/W-0                 | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    | F7BF  | °<3:0>              |                       |                                    | F6BF  | P<3:0> |       |  |

| bit 15                             |       |                     |                       |                                    |       |        | bit 8 |  |

| R/W-0                              | R/W-0 | R/W-0               | R/W-0                 | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    | F5BF  | °<3:0>              |                       | F4BP<3:0>                          |       |        |       |  |

| bit 7                              |       |                     |                       |                                    |       |        | bit 0 |  |

| Legend:                            |       |                     |                       |                                    |       |        |       |  |

| R = Readable bi                    | t     | W = Writable        | bit                   | U = Unimplemented bit, read as '0' |       |        |       |  |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleare | red x = Bit is unknow |                                    | nown  |        |       |  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |

|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|-----------------|----------|-------|--|

|               | F11BF                                              | P<3:0>                                                                                        |                                                | F10BP<3:0>                              |                 |          |       |  |

| bit 15        |                                                    |                                                                                               |                                                |                                         |                 |          | bit 8 |  |

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |

| F9BP<3:0>     |                                                    |                                                                                               |                                                |                                         | F8B             | P<3:0>   |       |  |

| bit 7         |                                                    |                                                                                               |                                                |                                         |                 |          | bit 0 |  |

| Legend:       |                                                    |                                                                                               |                                                |                                         |                 |          |       |  |

| R = Readabl   | le bit                                             | W = Writable                                                                                  | bit                                            | U = Unimplen                            | nented bit, rea | d as '0' |       |  |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                              |                                                | '0' = Bit is cleared x = Bit is unknown |                 |          | nown  |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | RX Buffer Mar<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer<br>4                              |                 |          |       |  |

| bit 11-8      | F10BP<3:0>                                         | : RX Buffer Ma                                                                                | sk for Filter 1                                | 0 bits (same val                        | ues as bits<1   | 5:12>)   |       |  |

| bit 7-4       | F9BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 9 b                               | oits (same value                        | s as bits<15:1  | 2>)      |       |  |

| bit 3-0       | F8BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 8 k                               | oits (same value                        | s as bits<15:1  | 2>)      |       |  |

|               |                                                    |                                                                                               |                                                |                                         |                 |          |       |  |

© 2011-2013 Microchip Technology Inc.

### 22.2 CTMU Control Registers

| REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1                                         |                                                                                                                                                                     |                  |       |                      |                  |                        |        |  |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|----------------------|------------------|------------------------|--------|--|

| R/W-0                                                                                    | U-0                                                                                                                                                                 | R/W-0            | R/W-0 | R/W-0                | R/W-0            | R/W-0                  | R/W-0  |  |

| CTMUEN                                                                                   | _                                                                                                                                                                   | CTMUSIDL         | TGEN  | EDGEN                | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |  |

| bit 15                                                                                   |                                                                                                                                                                     |                  |       |                      |                  |                        | bit 8  |  |

|                                                                                          |                                                                                                                                                                     |                  |       |                      |                  |                        |        |  |

| U-0                                                                                      | U-0                                                                                                                                                                 | U-0              | U-0   | U-0                  | U-0              | U-0                    | U-0    |  |

|                                                                                          |                                                                                                                                                                     | —                | _     |                      | <u> </u>         |                        | _      |  |

| bit 7                                                                                    |                                                                                                                                                                     |                  |       |                      |                  |                        | bit 0  |  |

|                                                                                          |                                                                                                                                                                     |                  |       |                      |                  |                        |        |  |

| Legend:                                                                                  |                                                                                                                                                                     |                  |       |                      |                  |                        |        |  |

| R = Readable                                                                             | e bit                                                                                                                                                               | W = Writable b   | oit   | U = Unimplen         | nented bit, read | as '0'                 |        |  |

| -n = Value at                                                                            | POR                                                                                                                                                                 | '1' = Bit is set |       | '0' = Bit is cleared |                  | x = Bit is unknown     |        |  |

| bit 15 <b>CTMUEN:</b> CTMU Enable bit<br>1 = Module is enabled<br>0 = Module is disabled |                                                                                                                                                                     |                  |       |                      |                  |                        |        |  |

| bit 14                                                                                   | Unimpleme                                                                                                                                                           | nted: Read as '0 | 3     |                      |                  |                        |        |  |

| bit 13                                                                                   | bit 13 <b>CTMUSIDL:</b> CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |                  |       |                      |                  |                        |        |  |

| bit 12                                                                                   | bit 12 TGEN: Time Generation Enable bit                                                                                                                             |                  |       |                      |                  |                        |        |  |

#### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

## 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0            | R/W-0                                                                                       | R/W-0                           | R/W-0            | R/W-0           | R/W-0   |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------|---------------------------------|------------------|-----------------|---------|

| PTGCLK2         | PTGCLK1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PTGCLK0          | PTGDIV4                                                                                     | PTGDIV3                         | PTGDIV2          | PTGDIV1         | PTGDIV0 |

| bit 15          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                | 1                                                                                           |                                 | 1                |                 | bit     |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0            | R/W-0                                                                                       | U-0                             | R/W-0            | R/W-0           | R/W-0   |

| PTGPWD3         | PTGPWD2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PTGPWD1          | PTGPWD0                                                                                     | _                               | PTGWDT2          | PTGWDT1         | PTGWDTC |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                                                                                             |                                 |                  |                 | bit     |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                                                                                             |                                 |                  |                 |         |

| R = Readable    | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | W = Writable     | bit                                                                                         | U = Unimpler                    | mented bit, read | l as '0'        |         |

| -n = Value at F | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | '1' = Bit is set |                                                                                             | '0' = Bit is cle                | ared             | x = Bit is unkr | nown    |

| bit 15-13       | 111 = Reserv<br>110 = Reserv<br>101 = PTG m<br>100 = PTG m<br>011 = PTG m<br>010 = PTG m<br>001 = PTG m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  | urce will be T3<br>urce will be T2<br>urce will be T1<br>urce will be TA<br>urce will be Fc | SCLK<br>SCLK<br>CLK<br>D<br>DSC |                  |                 |         |

| bit 12-8        | PTGDIV<4:0>: PTG Module Clock Prescaler (divider) bits<br>11111 = Divide-by-32<br>11110 = Divide-by-31<br>•<br>•<br>•<br>00001 = Divide-by-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |                                                                                             |                                 |                  |                 |         |

| bit 7-4         | 00000 = Divide-by-1<br><b>PTGPWD&lt;3:0&gt;:</b> PTG Trigger Output Pulse-Width bits<br>1111 = All trigger outputs are 16 PTG clock cycles wide<br>1110 = All trigger outputs are 15 PTG clock cycles wide<br>0001 = All trigger outputs are 2 PTG clock cycles wide<br>0001 = All trigger outputs are 1 PTG clock cycles wide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |                                                                                             |                                 |                  |                 |         |

| bit 3           | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ted: Read as '   | 0'                                                                                          |                                 |                  |                 |         |

| bit 2-0         | <ul> <li>0000 = All trigger outputs are 1 PTG clock cycle wide</li> <li>Unimplemented: Read as '0'</li> <li>PTGWDT&lt;2:0&gt;: Select PTG Watchdog Timer Time-out Count Value bits</li> <li>111 = Watchdog Timer will time-out after 512 PTG clocks</li> <li>110 = Watchdog Timer will time-out after 256 PTG clocks</li> <li>101 = Watchdog Timer will time-out after 128 PTG clocks</li> <li>100 = Watchdog Timer will time-out after 32 PTG clocks</li> <li>011 = Watchdog Timer will time-out after 32 PTG clocks</li> <li>010 = Watchdog Timer will time-out after 32 PTG clocks</li> <li>010 = Watchdog Timer will time-out after 32 PTG clocks</li> <li>010 = Watchdog Timer will time-out after 16 PTG clocks</li> <li>010 = Watchdog Timer will time-out after 8 PTG clocks</li> <li>001 = Watchdog Timer will time-out after 8 PTG clocks</li> <li>000 = Watchdog Timer is disabled</li> </ul> |                  |                                                                                             |                                 |                  |                 |         |

## REGISTER 24-2: PTGCON: PTG CONTROL REGISTER

| R/W-0         | R/W-0                                                                                                                                                             | R/W-0            | U-0                 | U-0              | R/W-0            | R/W-0               | R/W-0               |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|------------------|------------------|---------------------|---------------------|--|--|--|

| CON           | COE <sup>(2)</sup>                                                                                                                                                | CPOL             | _                   | —                | OPMODE           | CEVT                | COUT                |  |  |  |

| bit 15        |                                                                                                                                                                   |                  |                     |                  |                  |                     | bit 8               |  |  |  |

|               |                                                                                                                                                                   |                  |                     |                  |                  |                     |                     |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                             | U-0              | R/W-0               | U-0              | U-0              | R/W-0               | R/W-0               |  |  |  |

| EVPOL1        | EVPOL0                                                                                                                                                            | —                | CREF <sup>(1)</sup> | —                | —                | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |  |  |  |

| bit 7         |                                                                                                                                                                   |                  |                     |                  |                  |                     | bit (               |  |  |  |

| Legend:       |                                                                                                                                                                   |                  |                     |                  |                  |                     |                     |  |  |  |

| R = Readabl   | le bit                                                                                                                                                            | W = Writable     | bit                 | U = Unimple      | mented bit, read | as '0'              |                     |  |  |  |

| -n = Value at | t POR                                                                                                                                                             | '1' = Bit is set |                     | '0' = Bit is cle | eared            | x = Bit is unknown  |                     |  |  |  |

|               |                                                                                                                                                                   |                  |                     |                  |                  |                     |                     |  |  |  |

| bit 15        | CON: Op Amp/Comparator Enable bit                                                                                                                                 |                  |                     |                  |                  |                     |                     |  |  |  |

|               | <ul><li>1 = Op amp/comparator is enabled</li><li>0 = Op amp/comparator is disabled</li></ul>                                                                      |                  |                     |                  |                  |                     |                     |  |  |  |

|               |                                                                                                                                                                   |                  |                     |                  |                  |                     |                     |  |  |  |

| bit 14        | <b>COE:</b> Comparator Output Enable bit <sup>(2)</sup>                                                                                                           |                  |                     |                  |                  |                     |                     |  |  |  |

|               | <ul> <li>1 = Comparator output is present on the CxOUT pin</li> <li>0 = Comparator output is internal only</li> </ul>                                             |                  |                     |                  |                  |                     |                     |  |  |  |

| bit 13        | <b>CPOL:</b> Comparator Output Polarity Select bit                                                                                                                |                  |                     |                  |                  |                     |                     |  |  |  |

|               | 1 = Comparator output is inverted                                                                                                                                 |                  |                     |                  |                  |                     |                     |  |  |  |

|               | 0 = Compara                                                                                                                                                       | tor output is no | t inverted          |                  |                  |                     |                     |  |  |  |

| bit 12-11     | Unimplemen                                                                                                                                                        | ted: Read as '   | 0'                  |                  |                  |                     |                     |  |  |  |

| bit 10        | OPMODE: Op Amp/Comparator Operation Mode Select bit                                                                                                               |                  |                     |                  |                  |                     |                     |  |  |  |

|               | <ul> <li>1 = Circuit operates as an op amp</li> <li>0 = Circuit operates as a comparator</li> </ul>                                                               |                  |                     |                  |                  |                     |                     |  |  |  |

| bit 9         | CEVT: Comparator Event bit                                                                                                                                        |                  |                     |                  |                  |                     |                     |  |  |  |

|               | <ul> <li>1 = Comparator event according to the EVPOL&lt;1:0&gt; settings occurred; disables future triggers ar<br/>interrupts until the bit is cleared</li> </ul> |                  |                     |                  |                  |                     |                     |  |  |  |

|               | 0 = Comparator event did not occur                                                                                                                                |                  |                     |                  |                  |                     |                     |  |  |  |

| bit 8         | COUT: Comparator Output bit                                                                                                                                       |                  |                     |                  |                  |                     |                     |  |  |  |

|               | When CPOL = 0 (non-inverted polarity):<br>1 = VIN+ > VIN-                                                                                                         |                  |                     |                  |                  |                     |                     |  |  |  |

|               | 1 = VIN + > VIN - 0 = VIN + < VIN - 0                                                                                                                             |                  |                     |                  |                  |                     |                     |  |  |  |

|               | When CPOL = 1 (inverted polarity):                                                                                                                                |                  |                     |                  |                  |                     |                     |  |  |  |

|               | 1 = VIN + < VIN-                                                                                                                                                  |                  |                     |                  |                  |                     |                     |  |  |  |

|               | 0 = VIN + > VI                                                                                                                                                    |                  |                     |                  |                  |                     |                     |  |  |  |

#### **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3)

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

| AC CHARACTERISTICS |                       |                                               | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |          |           |       |                                                         |

|--------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|-------|---------------------------------------------------------|