#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 28-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc502t-i-ss |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

# 3.1 Registers

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

# 3.2 Instruction Set

The instruction set for dsPIC33EPXXXGP50X and dsPIC33EPXXXMC20X/50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. The instruction set for PIC24EPXXXGP/MC20X devices has the MCU class of instructions only and does not support DSP instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

# 3.3 Data Space Addressing

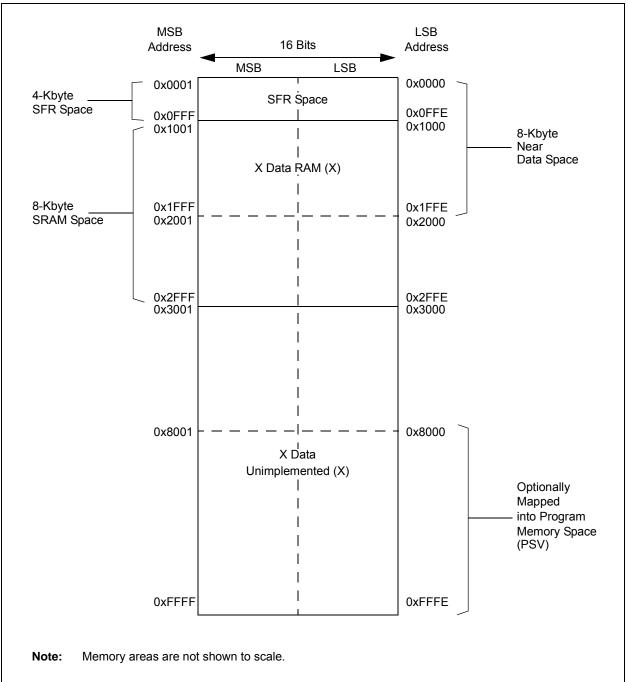

The base Data Space can be addressed as 64 Kbytes (32K words).

The Data Space includes two ranges of memory, referred to as X and Y data memory. Each memory range is accessible through its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Spaces have memory locations that are device-specific, and are described further in the data memory maps in **Section 4.2 "Data Address Space"**.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 32-Kbyte aligned program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to the "**Data Memory**" (DS70595) and "**Program Memory**" (DS70613) sections in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on EDS, PSV and table accesses.

On the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms. PIC24EPXXXGP/MC20X devices do not support Modulo and Bit-Reversed Addressing.

# 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- · Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1       | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|-------------|--------|--------|----------|-------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF       | DMA0IF | T1IF   | OC1IF    | IC1IF       | <b>INTOIF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _           | INT1IF | CNIF   | CMIF     | MI2C1IF     | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      | _      | _          | _      | _      |        | _          | —      | _     | IC4IF  | IC3IF       | DMA3IF | C1IF   | C1RXIF   | SPI2IF      | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | MI2C2IF  | SI2C2IF     | —             | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      |        | _          | —      | _     | C1TXIF | _           | —      | CRCIF  | U2EIF    | U1EIF       | —             | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | —          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | —             | 0000          |

| IFS9         | 0812  |        |        | _          | _      | _      | _      | _          | _      | _     | PTG3IF | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF   | _             | 0000          |

| IEC0         | 0820  |        | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE       | INT0IE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _      | _           | INT1IE | CNIE   | CMIE     | MI2C1IE     | SI2C1IE       | 0000          |

| IEC2         | 0824  |        |        | _          | _      | _      | _      | _          | _      | _     | IC4IE  | IC3IE       | DMA3IE | C1IE   | C1RXIE   | SPI2IE      | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | MI2C2IE  | SI2C2IE     | _             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | —      |        |        |            | _      | —     | C1TXIE |             |        | CRCIE  | U2EIE    | U1EIE       |               | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | _        | _           | _             | 0000          |

| IEC9         | 0832  | _      | _      | —          | —      |        | _      |            | _      | _     | PTG3IE | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE   | _             | 0000          |

| IPC0         | 0840  |        |        | T1IP<2:0>  | >      | _      | (      | OC1IP<2:0  | >      | _     |        | IC1IP<2:0>  |        | _      |          | NT0IP<2:0>  |               | 4444          |

| IPC1         | 0842  |        |        | T2IP<2:0>  | >      | _      | (      | C2IP<2:0   | >      | _     |        | IC2IP<2:0>  |        | _      | D        | MA0IP<2:0>  |               | 4444          |

| IPC2         | 0844  |        | ι      | J1RXIP<2:0 | 0>     | _      | Ş      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0 | >      | _      |          | T3IP<2:0>   |               | 4444          |

| IPC3         | 0846  |        |        | _          | _      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>  |        | _      | U        | J1TXIP<2:0> |               | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0   | >      | _      |        | CMIP<2:0   | >      | _     | I      | WI2C1IP<2:0 | >      | _      | S        | I2C1IP<2:0> |               | 4444          |

| IPC5         | 084A  |        |        | _          | _      | _      | _      | _          | _      | _     | _      | _           | _      | _      |          | NT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  |        |        | T4IP<2:0>  | >      | _      | (      | C4IP<2:0   | >      | _     |        | OC3IP<2:0>  |        | _      | D        | MA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  |        | ι      | U2TXIP<2:0 | )>     | _      | L      | I2RXIP<2:  | 0>     | _     |        | INT2IP<2:0> | •      | _      |          | T5IP<2:0>   |               | 4444          |

| IPC8         | 0850  |        |        | C1IP<2:0>  | >      | _      | C      | 1RXIP<2:   | 0>     | _     |        | SPI2IP<2:0> | •      | _      | S        | PI2EIP<2:0> |               | 4444          |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>  |        | _      | D        | MA3IP<2:0>  |               | 0444          |

| IPC11        | 0856  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | _        | _           | _             | 0000          |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | II2C2IP<2: | 0>     | _     |        | SI2C2IP<2:0 | >      | _      | _        | _           | _             | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | )>     | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>  |        | _      | _        | _           | _             | 4440          |

| IPC17        | 0862  | _      | _      | _          | _      | _      | C      | 1TXIP<2:   | )>     | _     | _      | _           | —      | _      | _        | _           | _             | 0400          |

| IPC19        | 0866  | _      | _      | —          | _      | _      |        | _          | —      | _     |        | CTMUIP<2:0  | >      | _      | —        |             |               | 0040          |

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>     | _      |        | ICDIP<2:0  | >      | _     | _      | —           | _      | _      | —        | _           | _             | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:  | 0>     | —      | PT     | GWDTIP<    | 2:0>   | _     | PT     | GSTEPIP<2   | :0>    | _      | _        | _           | _             | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | TG3IP<2:   | )>     | _     |        | PTG2IP<2:0  | >      | _      | Р        | TG1IP<2:0>  |               | 0444          |

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name  | Addr          | Bit 15    | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10                        | Bit 9  | Bit 8                         | Bit 7                                                      | Bit 6    | Bit 5  | Bit 4 | Bit 3             | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|-----------|-----------|--------|--------|--------|-------------------------------|--------|-------------------------------|------------------------------------------------------------|----------|--------|-------|-------------------|--------|--------|--------|---------------|

|            | 0400-<br>041E |           |           |        |        |        |                               |        | See defini                    | ion when W                                                 | 'IN = x  |        |       |                   |        |        |        |               |

| C1BUFPNT1  | 0420          |           | F3BF      | P<3:0> |        |        | F2BI                          | ><3:0> |                               |                                                            | F1BP     | <3:0>  |       |                   | F0BP   | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          |           | F7BF      | ><3:0> |        |        | F6BI                          | ><3:0> |                               |                                                            | F5BP     | <3:0>  |       |                   | F4BP   | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |           | F11B      | P<3:0> |        |        | F10B                          | P<3:0> |                               |                                                            | F9BP     | <3:0>  |       | F8BP<3:0>         |        |        |        | 0000          |

| C1BUFPNT4  | 0426          |           | F15B      | P<3:0> |        |        | F14B                          | P<3:0> |                               |                                                            | F13B     | D<3:0> |       |                   | F12BF  | P<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |           |           |        | SID<   | :10:3> |                               |        |                               |                                                            | SID<2:0> |        | _     | MIDE — EID<17:16> |        |        |        | xxxx          |

| C1RXM0EID  | 0432          |           |           |        | EID<   | :15:8> |                               |        |                               |                                                            |          |        | EID<  | 7:0>              |        |        |        | xxxx          |

| C1RXM1SID  | 0434          |           |           |        | SID<   | :10:3> |                               |        |                               |                                                            | SID<2:0> |        | _     | MIDE              | —      | EID<   | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |           |           |        | EID<   | :15:8> |                               |        |                               |                                                            |          |        | EID<  | 7:0>              |        |        |        | xxxx          |

| C1RXM2SID  | 0438          |           |           |        | SID<   | :10:3> |                               |        |                               | SID<2:0> — MIDE — EID<17                                   |          |        |       |                   |        | 17:16> | xxxx   |               |

| C1RXM2EID  | 043A          |           |           |        | EID<   | :15:8> |                               |        |                               | EID<7:0>                                                   |          |        |       |                   |        |        | xxxx   |               |

| C1RXF0SID  | 0440          |           | SID<10:3> |        |        |        |                               |        |                               | SID<2:0> — EXIDE                                           |          |        |       |                   | —      | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |           | EID<15:8> |        |        |        |                               |        |                               | EID<7:0>                                                   |          |        |       |                   |        |        | xxxx   |               |

| C1RXF1SID  | 0444          |           | SID<10:3> |        |        |        |                               |        |                               |                                                            | SID<2:0> |        | _     | EXIDE             | —      | EID<   | 17:16> | xxxx          |

| C1RXF1EID  | 0446          |           | EID<15:8> |        |        |        |                               |        |                               |                                                            |          |        | EID<  | 7:0>              |        |        |        | xxxx          |

| C1RXF2SID  | 0448          |           |           |        | SID<   | :10:3> |                               |        |                               |                                                            | SID<2:0> |        | —     | EXIDE             | —      | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |           |           |        | EID<   | :15:8> |                               |        |                               |                                                            |          |        | EID<  | 7:0>              |        |        |        | xxxx          |

| C1RXF3SID  | 044C          |           |           |        | SID<   | :10:3> |                               |        |                               |                                                            | SID<2:0> |        | —     | EXIDE             | —      | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |           |           |        | EID<   | :15:8> |                               |        |                               | EID<7:0>                                                   |          |        |       |                   |        | xxxx   |        |               |

| C1RXF4SID  | 0450          |           |           |        | SID<   | :10:3> |                               |        |                               | SID<2:0> —                                                 |          |        |       | EXIDE — EID<17:16 |        |        |        | xxxx          |

| C1RXF4EID  | 0452          |           |           |        | EID<   | :15:8> |                               |        |                               | EID<7:0>                                                   |          |        |       |                   |        |        | xxxx   |               |

| C1RXF5SID  | 0454          |           |           |        | SID<   | :10:3> |                               |        |                               | SID<2:0>         —         EXIDE         —         EID<17: |          |        |       |                   | 17:16> | xxxx   |        |               |

| C1RXF5EID  | 0456          |           |           |        | EID<   | :15:8> |                               |        |                               |                                                            |          |        | EID<  | 7:0>              |        |        |        | xxxx          |

| C1RXF6SID  | 0458          |           |           |        | SID<   | :10:3> |                               |        |                               |                                                            | SID<2:0> |        | —     | EXIDE             | —      | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |           |           |        | EID<   | :15:8> |                               |        |                               |                                                            |          |        | EID<  | 7:0>              |        |        |        | xxxx          |

| C1RXF7SID  | 045C          |           |           |        | SID<   | :10:3> |                               |        |                               |                                                            | SID<2:0> |        | —     | EXIDE             | —      | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |           | EID<15:8> |        |        |        |                               |        |                               |                                                            |          |        | EID<  | 7:0>              |        |        |        | xxxx          |

| C1RXF8SID  | 0460          |           | SID<10:3> |        |        |        |                               |        | SID<2:0> —                    |                                                            |          |        | EXIDE | —                 | EID<   | 17:16> | xxxx   |               |

| C1RXF8EID  | 0462          |           | EID<15:8> |        |        |        |                               |        |                               | EID<7:0>                                                   |          |        |       |                   |        | xxxx   |        |               |

| C1RXF9SID  | 0464          |           | SID<10:3> |        |        |        |                               |        | SID<2:0> — EXIDE — EID<17:16> |                                                            |          |        |       |                   | 17:16> | xxxx   |        |               |

| C1RXF9EID  | 0466          |           | EID<15:8> |        |        |        |                               |        |                               |                                                            |          | EID<   |       |                   |        |        | xxxx   |               |

| C1RXF10SID | 0468          | SID<10:3> |           |        |        |        | SID<2:0> — EXIDE — EID<17:16> |        |                               |                                                            |          | 17:16> | xxxx  |                   |        |        |        |               |

| C1RXF10EID | 046A          | EID<15:8> |           |        |        |        | EID<7:0>                      |        |                               |                                                            |          | xxxx   |       |                   |        |        |        |               |

| C1RXF11SID | 046C          |           | SID<10:3> |        |        |        |                               |        |                               | SID<2:0>                                                   |          | —      | EXIDE | -                 | EID<   | 17:16> | xxxx   |               |

## TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-34: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3    | Bit 2 | Bit 1   | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|---------|--------|--------|-------|-------|----------|-------|-------|--------|----------|-------|---------|-------|---------------|

| NVMCON    | 0728  | WR     | WREN   | WRERR  | NVMSIDL | _      | _      | —     | _     | _        | _     | _     | —      |          | NVMC  | )P<3:0> |       | 0000          |

| NVMADRL   | 072A  |        |        |        |         |        |        |       | NVMAD | )R<15:0> |       |       |        |          |       |         |       | 0000          |

| NVMADRH   | 072C  | _      | _      | _      | _       | -      | _      | _     | _     |          |       |       | NVMADF | R<23:16> |       |         |       | 0000          |

| NVMKEY    | 072E  |        |        | _      | —       | _      |        | —     | -     |          |       |       | NVMKE  | Y<7:0>   |       |         |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-35: SYSTEM CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7   | Bit 6  | Bit 5  | Bit 4   | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|-----------|--------|--------|--------|-----------|-------|---------|--------|--------|---------|-------|--------|-------|-------|---------------|

| RCON      | 0740  | TRAPR  | IOPUWR | _         | _      | VREGSF | _      | СМ        | VREGS | EXTR    | SWR    | SWDTEN | WDTO    | SLEEP | IDLE   | BOR   | POR   | Note 1        |

| OSCCON    | 0742  | _      | 0      | COSC<2:0> |        | —      |        | NOSC<2:0> |       | CLKLOCK | IOLOCK | LOCK   | _       | CF    | _      | _     | OSWEN | Note 2        |

| CLKDIV    | 0744  | ROI    | [      | OOZE<2:0> |        | DOZEN  | F      | RCDIV<2:0 | >     | PLLPOS  | T<1:0> | _      |         | F     | LLPRE< | 4:0>  |       | 0030          |

| PLLFBD    | 0746  | _      | _      | _         | _      | —      | _      | _         |       |         |        | PLLD   | IV<8:0> |       |        |       |       | 0030          |

| OSCTUN    | 0748  | _      | _      | _         | _      | —      | _      | _         | _     | _       |        |        |         | TUN≤  | <5:0>  |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses.

## TABLE 4-36: REFERENCE CLOCK REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON   | 074E  | ROON   | —      | ROSSLP | ROSEL  |        | RODI   | V<3:0> |       | _     | _     | —     | _     | _     | —     | _     | -     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

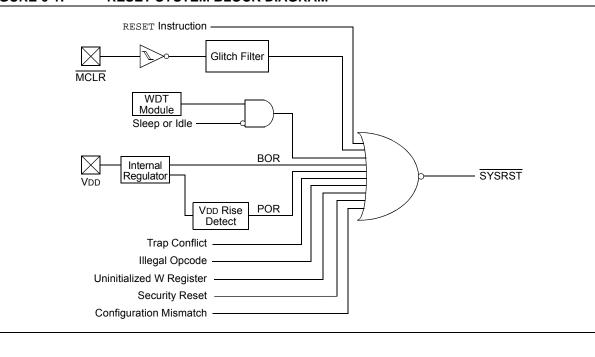

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

## TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

| R/W-0         | U-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ROON          |                                                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                   | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15        |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       | •                     | bit                   |

| U-0           | U-0                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |

|               | _                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | _                     |                       | _                     |                       |

| bit 7         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       | bit                   |

| Legend:       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| R = Readable  | e bit                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                                                                                   | U = Unimpler          | nented bit, read      | l as '0'              |                       |

| -n = Value at |                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as '                                                                                                                                                                                                                                                                                                                                        | out is disabled                                                                                                                                                                                                       |                       | .K pin <sup>(2)</sup> |                       |                       |

| bit 13        | -                                                                                                                                                                                                                                            | ference Oscilla                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       | en hit                |                       |                       |                       |

|               | 1 = Reference                                                                                                                                                                                                                                | e oscillator out<br>e oscillator out                                                                                                                                                                                                                                                                                                                                                                     | out continues                                                                                                                                                                                                         | to run in Sleep       |                       |                       |                       |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                               | erence Oscillato<br>crystal is used<br>lock is used as                                                                                                                                                                                                                                                                                                                                                   | as the refere                                                                                                                                                                                                         | nce clock             |                       |                       |                       |

| bit 11-8      | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>1000 = Refer<br>1011 = Refer<br>1001 = Refer<br>1000 = Refer<br>0111 = Refer<br>0111 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer<br>0011 = Refer | Reference Os<br>rence clock divi<br>rence clock divi | ded by 32,763<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 8                     |                       |                       |                       |

|               | 0000 = Refer                                                                                                                                                                                                                                 | ence clock                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                     |                       |                       |                       |                       |

## REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

## 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

# 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

## 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0         | R/W-0                          | R/W-0                                      | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|---------------|--------------------------------|--------------------------------------------|-------------------|-------------------|------------------|-----------------|-------|

| QCAPEN        | FLTREN                         | QFDIV2                                     | QFDIV1            | QFDIV0            | OUTFNC1          | OUTFNC0         | SWPAB |

| bit 15        | ·                              | ·                                          |                   |                   |                  |                 | bit 8 |

| R/W-0         | R/W-0                          | R/W-0                                      | R/W-0             | R-x               | R-x              | R-x             | R-x   |

| HOMPOL        | IDXPOL                         | QEBPOL                                     | QEAPOL            | HOME              | INDEX            | QEB             | QEA   |

| bit 7         |                                |                                            |                   | TIOME             | INDEX            | QLD             | bit ( |

| Legend:       |                                |                                            |                   |                   |                  |                 |       |

| R = Readable  | e bit                          | W = Writable                               | bit               | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at |                                | '1' = Bit is set                           |                   | '0' = Bit is cle  |                  | x = Bit is unkn | own   |

|               |                                |                                            |                   |                   |                  |                 |       |

| bit 15        | QCAPEN: Q                      | EI Position Cou                            | nter Input Cap    | ture Enable bit   |                  |                 |       |

|               |                                | tch event trigge                           |                   |                   |                  |                 |       |

|               |                                | tch event does                             |                   | -                 |                  |                 |       |

| bit 14        |                                | Ax/QEBx/INDX                               | •                 | tal Filter Enable | e dit            |                 |       |

|               |                                | digital filter is e<br>digital filter is d |                   | sed)              |                  |                 |       |

| bit 13-11     |                                | : QEAx/QEBx/II                             |                   |                   | Iter Clock Divid | le Select bits  |       |

|               | 111 = 1:128                    |                                            |                   | g                 |                  |                 |       |

|               | 110 = 1:64 cl                  | lock divide                                |                   |                   |                  |                 |       |

|               | 101 = 1:32 cl                  |                                            |                   |                   |                  |                 |       |

|               | 100 = 1:16 cl                  |                                            |                   |                   |                  |                 |       |

|               | 011 = 1:8 clo<br>010 = 1:4 clo |                                            |                   |                   |                  |                 |       |

|               | 001 = 1:4 Clo                  |                                            |                   |                   |                  |                 |       |

|               | 000 = 1:1 clo                  |                                            |                   |                   |                  |                 |       |

| bit 10-9      | OUTFNC<1:                      | 0>: QEI Module                             | Output Functi     | on Mode Selec     | ct bits          |                 |       |

|               |                                | NCMPx pin goe                              | -                 |                   |                  | GEC             |       |

|               |                                | NCMPx pin goe                              |                   |                   |                  |                 |       |

|               |                                | NCMPx pin goe                              | s high when P     | $OS1CNT \ge QE$   | IIGEC            |                 |       |

| L:1 0         | 00 = Output i                  |                                            |                   |                   |                  |                 |       |

| bit 8         |                                | ap QEA and QE                              | •                 |                   |                  |                 |       |

|               |                                | d QEBx are sw<br>d QEBx are not            |                   | quadrature dec    | coder logic      |                 |       |

| bit 7         | HOMPOL: H                      | OMEx Input Po                              | larity Select bit |                   |                  |                 |       |

|               | 1 = Input is in                |                                            |                   |                   |                  |                 |       |

| bit 6         | 0 = Input is n                 |                                            | ty Soloot bit     |                   |                  |                 |       |

|               | 1 = Input is in                | OXx Input Polari                           | ly Select bit     |                   |                  |                 |       |

|               | 0 = Input is n                 |                                            |                   |                   |                  |                 |       |

| bit 5         | -                              | EBx Input Polar                            | itv Select bit    |                   |                  |                 |       |

|               | 1 = Input is i                 | •                                          | .,                |                   |                  |                 |       |

|               | 0 = Input is r                 |                                            |                   |                   |                  |                 |       |

| bit 4         | QEAPOL: Q                      | EAx Input Polar                            | ity Select bit    |                   |                  |                 |       |

|               | 1 = Input is i                 |                                            |                   |                   |                  |                 |       |

|               | 0 = Input is r                 | not inverted                               |                   |                   |                  |                 |       |

| bit 3         | HOME: Statu                    |                                            |                   |                   |                  |                 |       |

| DIL 3         | <b>HOME</b> . Statu            |                                            | out Pin Alter Po  | olarity Control   |                  |                 |       |

| DIL 3         | 1 = Pin is at<br>0 = Pin is at | logic '1'                                  | out Pin Aiter Po  | bianty Control    |                  |                 |       |

# REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER

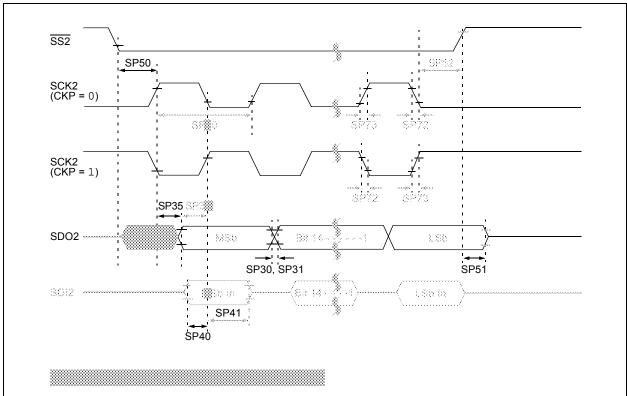

# 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This   | insures    | that  | the       | first | fr | ame |

|-------|--------|------------|-------|-----------|-------|----|-----|

|       | transr | nission    | after | initializ | ation | is | not |

|       | shifte | d or corru | pted. |           |       |    |     |

- 2. In Non-Framed 3-Wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose Sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPIx specifications in Section 30.0 "Electrical Characteristics" for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPIx data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

## 18.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

## 18.2.1 KEY RESOURCES

- "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | R/W-x                                                                                                                                       | U-0                                     | U-0         | U-0              | R/W-x            | R/W-x           | R/W-x   |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------|------------------|------------------|-----------------|---------|--|--|--|

| _             | WAKFIL                                                                                                                                      | _                                       | —           |                  | SEG2PH2          | SEG2PH1         | SEG2PH0 |  |  |  |

| bit 15        |                                                                                                                                             |                                         |             |                  |                  |                 | bit     |  |  |  |

| R/W-x         | R/W-x                                                                                                                                       | R/W-x                                   | R/W-x       | R/W-x            | R/W-x            | R/W-x           | R/W-x   |  |  |  |

|               |                                                                                                                                             |                                         |             | 1                |                  | 1               |         |  |  |  |

| SEG2PHTS      | SAM                                                                                                                                         | SEG1PH2                                 | SEG1PH1     | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |  |  |  |

| bit 7         |                                                                                                                                             |                                         |             |                  |                  |                 | bit     |  |  |  |

| Legend:       |                                                                                                                                             |                                         |             |                  |                  |                 |         |  |  |  |

| R = Readable  | e bit                                                                                                                                       | W = Writable                            | bit         | U = Unimpler     | nented bit, read | l as '0'        |         |  |  |  |

| -n = Value at | POR                                                                                                                                         | '1' = Bit is set                        |             | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |

|               |                                                                                                                                             |                                         |             |                  |                  |                 |         |  |  |  |

| bit 15        | Unimplemer                                                                                                                                  | nted: Read as '                         | 0'          |                  |                  |                 |         |  |  |  |

| bit 14        |                                                                                                                                             | lect CAN Bus L                          |             | Vake-up bit      |                  |                 |         |  |  |  |

|               |                                                                                                                                             | N bus line filter<br>line filter is not |             | e-up             |                  |                 |         |  |  |  |

| bit 13-11     | Unimplemer                                                                                                                                  | nted: Read as '                         | 0'          |                  |                  |                 |         |  |  |  |

| bit 10-8      | SEG2PH<2:0                                                                                                                                  | 0>: Phase Segr                          | nent 2 bits |                  |                  |                 |         |  |  |  |

|               | 111 = Length is 8 x Tq                                                                                                                      |                                         |             |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                           |                                         |             |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                           |                                         |             |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                           |                                         |             |                  |                  |                 |         |  |  |  |

|               | 000 = Length                                                                                                                                | n is 1 x Tq                             |             |                  |                  |                 |         |  |  |  |

| bit 7         | SEG2PHTS: Phase Segment 2 Time Select bit                                                                                                   |                                         |             |                  |                  |                 |         |  |  |  |

|               | <ul> <li>1 = Freely programmable</li> <li>0 = Maximum of SEG1PHx bits or Information Processing Time (IPT), whichever is greater</li> </ul> |                                         |             |                  |                  |                 |         |  |  |  |

| bit 6         | <b>SAM:</b> Sample of the CAN Bus Line bit                                                                                                  |                                         |             |                  |                  |                 |         |  |  |  |

|               |                                                                                                                                             | is sampled three<br>is sampled once     |             |                  |                  |                 |         |  |  |  |

| bit 5-3       | SEG1PH<2:0                                                                                                                                  | 0>: Phase Segr                          | nent 1 bits | -                |                  |                 |         |  |  |  |

|               | 111 = Length is 8 x TQ                                                                                                                      |                                         |             |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                           |                                         |             |                  |                  |                 |         |  |  |  |

|               | •                                                                                                                                           |                                         |             |                  |                  |                 |         |  |  |  |