Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc504-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

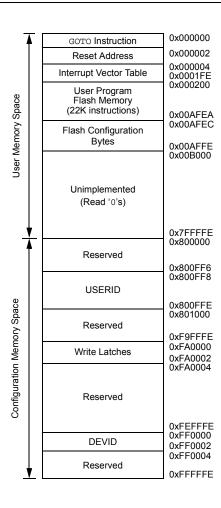

#### FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

| TABLE 4   | 4-9:  | INPUT  |        | JRE 1 T | HROUG  | H INPU    | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |       |       |       |          |          |       |               |

|-----------|-------|--------|--------|---------|--------|-----------|--------|-------|--------------|--------------|----------|-------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _      | —      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | -            | —            | ICI<     | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC1CON2   | 0142  | _      | _      |         | _      |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144  |        |        |         |        |           |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC1TMR    | 0146  |        |        |         |        |           |        |       | Input Capt   | ture 1 Time  | r        |       |       |       |          |          |       | 0000          |

| IC2CON1   | 0148  |        | —      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC2CON2   | 014A  |        | _      |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC2BUF    | 014C  |        |        |         |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |        |        |         |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |       |       |          |          |       | 0000          |

| IC3CON1   | 0150  |        | _      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |        | _      |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |        |        |         |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |        |        |         |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |       |       |          |          |       | 0000          |

| IC4CON1   | 0158  |        | _      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _      | _      |         | -      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  |        |        |         |        |           |        | Inp   | ut Capture 4 | 4 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC4TMR    | 015E  |        |        |         |        |           |        |       | Input Capt   | ure 4 Time   | r        |       |       |       |          |          |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

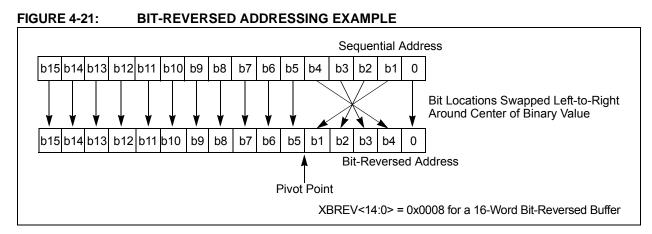

## TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      | Bit-Reversed Address |    |    |    |         |

|----|----|-------|-----------|---------|----------------------|----|----|----|---------|

| A3 | A2 | A1    | A0        | Decimal | A3                   | A2 | A1 | A0 | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0                    | 0  | 0  | 0  | 0       |

| 0  | 0  | 0     | 1         | 1       | 1                    | 0  | 0  | 0  | 8       |

| 0  | 0  | 1     | 0         | 2       | 0                    | 1  | 0  | 0  | 4       |

| 0  | 0  | 1     | 1         | 3       | 1                    | 1  | 0  | 0  | 12      |

| 0  | 1  | 0     | 0         | 4       | 0                    | 0  | 1  | 0  | 2       |

| 0  | 1  | 0     | 1         | 5       | 1                    | 0  | 1  | 0  | 10      |

| 0  | 1  | 1     | 0         | 6       | 0                    | 1  | 1  | 0  | 6       |

| 0  | 1  | 1     | 1         | 7       | 1                    | 1  | 1  | 0  | 14      |

| 1  | 0  | 0     | 0         | 8       | 0                    | 0  | 0  | 1  | 1       |

| 1  | 0  | 0     | 1         | 9       | 1                    | 0  | 0  | 1  | 9       |

| 1  | 0  | 1     | 0         | 10      | 0                    | 1  | 0  | 1  | 5       |

| 1  | 0  | 1     | 1         | 11      | 1                    | 1  | 0  | 1  | 13      |

| 1  | 1  | 0     | 0         | 12      | 0                    | 0  | 1  | 1  | 3       |

| 1  | 1  | 0     | 1         | 13      | 1                    | 0  | 1  | 1  | 11      |

| 1  | 1  | 1     | 0         | 14      | 0                    | 1  | 1  | 1  | 7       |

| 1  | 1  | 1     | 1         | 15      | 1                    | 1  | 1  | 1  | 15      |

## REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                       | R/W-0            | R/W-0              | R/W-0 |  |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|-----------------------------|------------------|--------------------|-------|--|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                | >                |                    |       |  |

| bit 15             |                                            |                                                 |                                            |                             |                  |                    | bit 8 |  |

|                    |                                            |                                                 |                                            |                             |                  |                    |       |  |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                         | U-0              | U-0                | U-0   |  |

| _                  |                                            |                                                 | —                                          |                             |                  | <u> </u>           | _     |  |

| bit 7              |                                            |                                                 |                                            |                             |                  |                    | bit 0 |  |

|                    |                                            |                                                 |                                            |                             |                  |                    |       |  |

| Legend:            |                                            |                                                 |                                            |                             |                  |                    |       |  |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplem                | nented bit, read | l as '0'           |       |  |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is clea           | ared             | x = Bit is unknown |       |  |

|                    |                                            |                                                 |                                            |                             |                  |                    |       |  |

|                    |                                            |                                                 |                                            |                             |                  |                    |       |  |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                             |                  |                    |       |  |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers) | the Correspon    | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                             | the Correspon    | ding RPn Pin b     | its   |  |

## REGISTER 11-16: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38 (dsPIC33EPXXXMC20X AND PIC24EPXXXMC20X DEVICES ONLY)

|              | -         |                                      |       |                  |                   | -               |                |

|--------------|-----------|--------------------------------------|-------|------------------|-------------------|-----------------|----------------|

| U-0          | R/W-0     | R/W-0                                | R/W-0 | R/W-0            | R/W-0             | R/W-0           | R/W-0          |

|              |           |                                      |       | DTCMP1R<6:       | 0>                |                 |                |

| bit 15       |           |                                      |       |                  |                   |                 | bit 8          |

|              |           |                                      |       |                  |                   |                 |                |

| U-0          | U-0       | U-0                                  | U-0   | U-0              | U-0               | U-0             | U-0            |

| —            | —         | —                                    | _     |                  | _                 | —               | —              |

| bit 7        |           |                                      |       |                  |                   |                 | bit C          |

|              |           |                                      |       |                  |                   |                 |                |

| Legend:      |           |                                      |       |                  |                   |                 |                |

| R = Readal   | ole bit   | W = Writable                         | bit   | U = Unimpler     | mented bit, read  | d as '0'        |                |

| -n = Value a | at POR    | '1' = Bit is set                     | :     | '0' = Bit is cle | ared              | x = Bit is unkr | nown           |

|              |           |                                      |       |                  |                   |                 |                |

| bit 15       | Unimpleme | nted: Read as '                      | 0'    |                  |                   |                 |                |

| bit 14-8     |           | 6:0>: Assign PV<br>1-2 for input pin |       | •                | on Input 1 to the | e Corresponding | g RPn Pin bits |

|              | 1111001 = | Input tied to RP                     | 1121  |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              |           | Input tied to CM                     | P1    |                  |                   |                 |                |

|              |           | Input tied to Vss                    |       |                  |                   |                 |                |

| bit 7-0      |           | nted: Read as '                      |       |                  |                   |                 |                |

|              |           |                                      | -     |                  |                   |                 |                |

| U-0             | U-0        | R/W-0                               | R/W-0                 | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |  |  |

|-----------------|------------|-------------------------------------|-----------------------|--------------------------|------------------|-----------------|-------|--|--|

| —               | —          |                                     |                       | RP57                     | R<5:0>           |                 |       |  |  |

| bit 15          |            |                                     |                       |                          |                  |                 | bit 8 |  |  |

|                 |            |                                     |                       |                          |                  |                 |       |  |  |

| U-0             | U-0        | R/W-0                               | R/W-0                 | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |  |  |

| _               | —          |                                     |                       | RP56                     | R<5:0>           |                 |       |  |  |

| bit 7           |            |                                     |                       |                          |                  |                 | bit 0 |  |  |

|                 |            |                                     |                       |                          |                  |                 |       |  |  |

| Legend:         |            |                                     |                       |                          |                  |                 |       |  |  |

| R = Readable I  | bit        | W = Writable                        | bit                   | U = Unimplen             | nented bit, read | d as '0'        |       |  |  |

| -n = Value at P | OR         | '1' = Bit is set                    | :                     | '0' = Bit is clea        | ared             | x = Bit is unkr | iown  |  |  |

|                 |            |                                     |                       |                          |                  |                 |       |  |  |

| bit 15-14       | Unimplemen | ted: Read as '                      | 0'                    |                          |                  |                 |       |  |  |

| bit 13-8        |            | : Peripheral Ou<br>-3 for periphera |                       | is Assigned to<br>mbers) | RP57 Output F    | Pin bits        |       |  |  |

| bit 7-6         | Unimplemen | ted: Read as '                      | <b>J:</b> Read as '0' |                          |                  |                 |       |  |  |

## REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

| R/W-0              | U-0                  | R/W-0                 | U-0                   | U-0 | U-0 | U-0                  | U-0   |

|--------------------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| TON <sup>(1)</sup> | —                    | TSIDL <sup>(2)</sup>  | —                     | —   | —   | —                    | —     |

| bit 15             |                      |                       |                       |     |     |                      | bit 8 |

|                    |                      |                       |                       |     |     |                      |       |

| U-0                | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

| —                  | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> |     | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7              |                      |                       |                       |     |     |                      | bit 0 |

|                    |                      |                       |                       |     |     |                      |       |

### REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| Legend:      |                        |                                                                               |                                          |                                   |

|--------------|------------------------|-------------------------------------------------------------------------------|------------------------------------------|-----------------------------------|

| R = Readal   | ole bit                | W = Writable bit                                                              | U = Unimplemented bit                    | , read as '0'                     |

| -n = Value a | at POR                 | '1' = Bit is set                                                              | '0' = Bit is cleared                     | x = Bit is unknown                |

| bit 15       | TON: Tin               | nery On bit <sup>(1)</sup>                                                    |                                          |                                   |

|              |                        | s 16-bit Timery<br>s 16-bit Timery                                            |                                          |                                   |

| bit 14       | •                      | mented: Read as '0'                                                           |                                          |                                   |

| bit 13       | -                      | imery Stop in Idle Mode bit                                                   | 2)                                       |                                   |

|              |                        | ontinues module operation winues module operation in Id                       | when device enters Idle mode<br>lle mode |                                   |

| bit 12-7     | Unimple                | mented: Read as '0'                                                           |                                          |                                   |

| bit 6        | TGATE:                 | Timery Gated Time Accumu                                                      | lation Enable bit <sup>(1)</sup>         |                                   |

|              | When TC<br>This bit is | <u>CS = 1:</u><br>s ignored.                                                  |                                          |                                   |

|              |                        | <u>CS = 0:</u><br>d time accumulation is enab<br>d time accumulation is disab |                                          |                                   |

| bit 5-4      | TCKPS<                 | 1:0>: Timery Input Clock Pre                                                  | escale Select bits <sup>(1)</sup>        |                                   |

|              | 11 <b>= 1:2</b> 5      |                                                                               |                                          |                                   |

|              | 10 = 1:64<br>01 = 1:8  | 1                                                                             |                                          |                                   |

|              | 01 = 1.8               |                                                                               |                                          |                                   |

| bit 3-2      | Unimple                | mented: Read as '0'                                                           |                                          |                                   |

| bit 1        | -                      | nery Clock Source Select bit                                                  | (1,3)                                    |                                   |

|              |                        | nal clock is from pin, TyCK (<br>nal clock (FP)                               | (on the rising edge)                     |                                   |

| bit 0        | Unimple                | mented: Read as '0'                                                           |                                          |                                   |

|              |                        | peration is enabled (T2CON<br>set through TxCON.                              | <3> = 1), these bits have no e           | ffect on Timery operation; all ti |

|              |                        |                                                                               |                                          |                                   |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

# REGISTER 16-13: IOCONX: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1 SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0 OSYNC: Output Override Synchronization bit

1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWMx period boundary

- 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

|                                   | R/W-0 | R/W-0            | R/W-0                                 | R/W-0                                                            | R/W-0                                                                                                  | R/W-0                                                                                                    |  |

|-----------------------------------|-------|------------------|---------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

|                                   |       | QEIG             | EC<31:24>                             |                                                                  |                                                                                                        |                                                                                                          |  |

|                                   |       |                  |                                       |                                                                  |                                                                                                        | bit 8                                                                                                    |  |

|                                   | DAMO  |                  |                                       |                                                                  | DAMO                                                                                                   |                                                                                                          |  |

| R/W-U                             | R/W-0 |                  |                                       | R/W-U                                                            | R/W-U                                                                                                  | R/W-0                                                                                                    |  |

|                                   |       | QEIGE            | EC<23:16>                             |                                                                  |                                                                                                        |                                                                                                          |  |

|                                   |       |                  |                                       |                                                                  |                                                                                                        | bit (                                                                                                    |  |

|                                   |       |                  |                                       |                                                                  |                                                                                                        |                                                                                                          |  |

| R = Readable bit W = Writable bit |       | t                | U = Unimplemented bit, read as '0'    |                                                                  |                                                                                                        |                                                                                                          |  |

| -n = Value at POR                 |       | '1' = Bit is set |                                       | '0' = Bit is cleared                                             |                                                                                                        | x = Bit is unknown                                                                                       |  |

|                                   |       | W = Writable bi  | R/W-0 R/W-0 QEIGI<br>W = Writable bit | R/W-0 R/W-0 R/W-0 QEIGEC<23:16><br>W = Writable bit U = Unimplem | R/W-0     R/W-0     R/W-0       QEIGEC<23:16>       W = Writable bit       U = Unimplemented bit, real | R/W-0       R/W-0       R/W-0       R/W-0         QEIGEC<23:16>       U = Unimplemented bit, read as '0' |  |

## REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                               | R/W-0   | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|-------------------------------------|---------|-----------------|-------|-------|

|                                    |       |       | QEIGE                               | C<15:8> |                 |       |       |

| bit 15                             |       |       |                                     |         |                 |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                               | R/W-0   | R/W-0           | R/W-0 | R/W-0 |

|                                    |       |       | QEIG                                | EC<7:0> |                 |       |       |

| bit 7                              |       |       |                                     |         |                 |       | bit 0 |

| Legend:                            |       |       |                                     |         |                 |       |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimplemented bit, read as '0'  |         |                 |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unl |         | x = Bit is unki | nown  |       |

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

| U-0                                                          | U-0                                                                                                                                                                                                                                              | U-0                                                                                          | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|

|                                                              | —                                                                                                                                                                                                                                                | _                                                                                            | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |

| bit 15                                                       |                                                                                                                                                                                                                                                  | •                                                                                            |                                       | •                    | •                    | •                    | bit                  |  |  |  |

| R/W-0                                                        | R/W-0                                                                                                                                                                                                                                            | R/W-0                                                                                        | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| SSEN <sup>(2)</sup>                                          | CKP                                                                                                                                                                                                                                              | MSTEN                                                                                        | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |

| bit 7                                                        | CKF                                                                                                                                                                                                                                              | WIGTEN                                                                                       | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |  |  |  |

|                                                              |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

| Legend:                                                      |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

| R = Readabl                                                  | le bit                                                                                                                                                                                                                                           | W = Writable                                                                                 | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |  |  |  |

| -n = Value at                                                | t POR                                                                                                                                                                                                                                            | '1' = Bit is se                                                                              | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |  |  |  |

|                                                              |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

| bit 15-13                                                    | Unimplemen                                                                                                                                                                                                                                       | ted: Read as                                                                                 | 0'                                    |                      |                      |                      |                      |  |  |  |

| bit 12                                                       |                                                                                                                                                                                                                                                  |                                                                                              | bit (SPIx Mas                         | -                    | ()                   |                      |                      |  |  |  |

|                                                              |                                                                                                                                                                                                                                                  |                                                                                              | sabled, pin fun                       | ctions as I/O        |                      |                      |                      |  |  |  |

| oit 11                                                       |                                                                                                                                                                                                                                                  | <ul> <li>0 = Internal SPIx clock is enabled</li> <li>DISSDO: Disable SDOx Pin bit</li> </ul> |                                       |                      |                      |                      |                      |  |  |  |

| 1 = SDOx pin is not used by the module; pin functions as I/O |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

|                                                              | 0 = SDOx pin is controlled by the module, pin functions as 1/O                                                                                                                                                                                   |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

| bit 10                                                       | MODE16: Word/Byte Communication Select bit                                                                                                                                                                                                       |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

|                                                              | 1 = Communication is word-wide (16 bits)                                                                                                                                                                                                         |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

|                                                              | 0 = Communication is byte-wide (8 bits)                                                                                                                                                                                                          |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

| bit 9                                                        | SMP: SPIx Data Input Sample Phase bit                                                                                                                                                                                                            |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

|                                                              | Master mode                                                                                                                                                                                                                                      | -                                                                                            | end of data o                         | utout time           |                      |                      |                      |  |  |  |

|                                                              |                                                                                                                                                                                                                                                  |                                                                                              | middle of data                        |                      |                      |                      |                      |  |  |  |

|                                                              | Slave mode:                                                                                                                                                                                                                                      | ·                                                                                            |                                       |                      |                      |                      |                      |  |  |  |

|                                                              | SMP must be cleared when SPIx is used in Slave mode.                                                                                                                                                                                             |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

| bit 8                                                        |                                                                                                                                                                                                                                                  | CKE: SPIx Clock Edge Select bit <sup>(1)</sup>                                               |                                       |                      |                      |                      |                      |  |  |  |

|                                                              | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)</li> </ul> |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

| bit 7                                                        |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      | ve clock state (I    |                      |  |  |  |

|                                                              | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(2)</sup><br>1 = SSx pin is used for Slave mode                                                                                                                                           |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

|                                                              | $1 = \frac{33}{55}$ pin is used for Slave mode<br>0 = SSx pin is not used by the module; pin is controlled by port function                                                                                                                      |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

| bit 6                                                        | CKP: Clock F                                                                                                                                                                                                                                     | <b>CKP:</b> Clock Polarity Select bit                                                        |                                       |                      |                      |                      |                      |  |  |  |

|                                                              |                                                                                                                                                                                                                                                  |                                                                                              | nigh level; activ<br>ow level; active |                      |                      |                      |                      |  |  |  |

| bit 5                                                        | MSTEN: Mas                                                                                                                                                                                                                                       | ter Mode Enat                                                                                | ole bit                               |                      |                      |                      |                      |  |  |  |

|                                                              | 1 = Master m<br>0 = Slave mo                                                                                                                                                                                                                     |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

| Note 1: T                                                    | he CKE bit is not                                                                                                                                                                                                                                | used in Frame                                                                                | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |  |  |  |

|                                                              | his bit must be cl                                                                                                                                                                                                                               |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

| <b>0</b>                                                     |                                                                                                                                                                                                                                                  |                                                                                              |                                       |                      |                      |                      |                      |  |  |  |

## REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

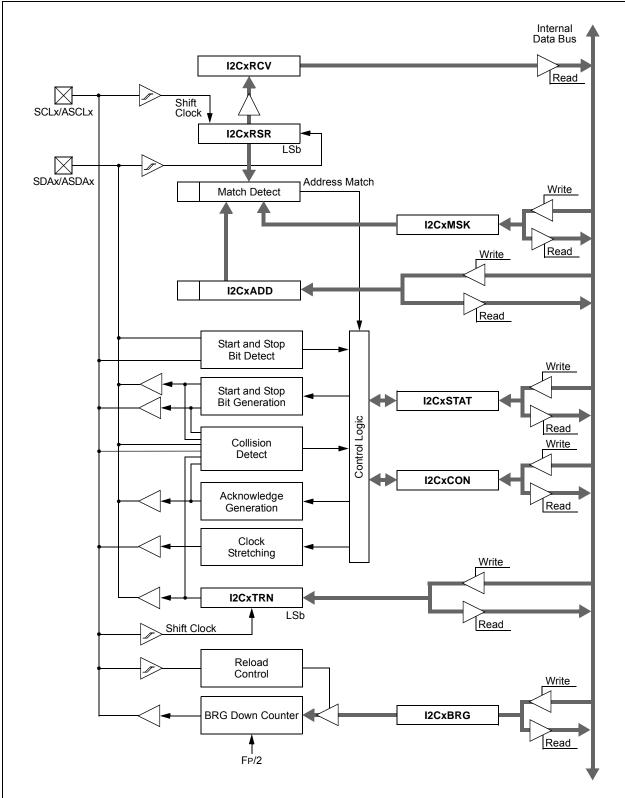

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

## 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

## 23.1 Key Features

## 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

## 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

|              | R/W-0         | U-0                                | U-0                         | U-0             | R/W-0                                | R/W-0                | R/W-0                |  |  |

|--------------|---------------|------------------------------------|-----------------------------|-----------------|--------------------------------------|----------------------|----------------------|--|--|

| CSS31        | CSS30         | —                                  | —                           | _               | CSS26 <sup>(2)</sup>                 | CSS25 <sup>(2)</sup> | CSS24 <sup>(2)</sup> |  |  |

| bit 15       | - 1           |                                    |                             |                 |                                      |                      | bit 8                |  |  |

|              |               |                                    |                             |                 |                                      |                      |                      |  |  |

| U-0          | U-0           | U-0                                | U-0                         | U-0             | U-0                                  | U-0                  | U-0                  |  |  |

| _            |               | _                                  | _                           | _               |                                      | _                    |                      |  |  |

| bit 7        |               |                                    |                             |                 |                                      |                      | bit (                |  |  |

|              |               |                                    |                             |                 |                                      |                      |                      |  |  |

| Legend:      |               |                                    |                             |                 |                                      |                      |                      |  |  |

| R = Readab   | le bit        | W = Writable                       | bit                         | U = Unimple     | emented bit, read                    | d as '0'             |                      |  |  |

| -n = Value a | t POR         | '1' = Bit is set                   |                             | '0' = Bit is cl | eared                                | x = Bit is unk       | nown                 |  |  |

|              |               |                                    |                             |                 |                                      |                      |                      |  |  |

| bit 15       |               | 1 Input Scan S                     |                             |                 |                                      |                      |                      |  |  |

|              |               |                                    |                             |                 | input scan (Ope                      |                      |                      |  |  |

|              | •             | •                                  |                             | surement for ir | nput scan (Open                      | )                    |                      |  |  |

| bit 14       |               | ADC1 Input Scan Selection bit      |                             |                 |                                      |                      |                      |  |  |

|              |               |                                    |                             |                 | or input scan (CT<br>input scan (CTN |                      |                      |  |  |

| bit 13-11    | Unimplemen    | ted: Read as '                     | 0'                          |                 |                                      |                      |                      |  |  |

| bit 10       | CSS26: ADC    | 1 Input Scan S                     | election bit <sup>(2)</sup> |                 |                                      |                      |                      |  |  |

|              | 1 = Selects C | cts OA3/AN6 for input scan         |                             |                 |                                      |                      |                      |  |  |

|              | 0 = Skips OA  | 3/AN6 for input                    | scan                        |                 |                                      |                      |                      |  |  |

| bit 9        | CSS25: ADC    | 1 Input Scan S                     | election bit <sup>(2)</sup> |                 |                                      |                      |                      |  |  |

|              | 1 = Selects C | 1 = Selects OA2/AN0 for input scan |                             |                 |                                      |                      |                      |  |  |

|              | 0 = Skips OA  | 2/AN0 for input                    | scan                        |                 |                                      |                      |                      |  |  |

| bit 8        | CSS24: ADC    | 1 Input Scan S                     | election bit <sup>(2)</sup> |                 |                                      |                      |                      |  |  |

|              |               | 0A1/AN3 for inp                    |                             |                 |                                      |                      |                      |  |  |

|              | 0 = Skips OA  | 1/AN3 for input                    | scan                        |                 |                                      |                      |                      |  |  |

|              |               |                                    |                             |                 |                                      |                      |                      |  |  |

## REGISTER 23-7: AD1CSSH: ADC1 INPUT SCAN SELECT REGISTER HIGH<sup>(1)</sup>

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

| R/W-0      | R/W-0                                 | R/W-0                                                                                                                                         | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |

|------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------------------|-----------------|--------|--|--|--|

| ADCTS4     | ADCTS3                                | ADCTS2                                                                                                                                        | ADCTS1         | IC4TSS           | IC3TSS                       | IC2TSS          | IC1TSS |  |  |  |

| bit 15     |                                       |                                                                                                                                               |                |                  |                              |                 | bit 8  |  |  |  |

| R/W-0      | R/W-0                                 | R/W-0                                                                                                                                         | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |

| OC4CS      |                                       | OC2CS                                                                                                                                         | OC1CS          | OC4TSS           | OC3TSS                       | OC2TSS          | OC1TSS |  |  |  |

| bit 7      |                                       | 00100                                                                                                                                         |                |                  |                              |                 | bit (  |  |  |  |

| Legend:    |                                       |                                                                                                                                               |                |                  |                              |                 |        |  |  |  |

| R = Reada  | ble bit                               | W = Writable                                                                                                                                  | bit            | U = Unimplei     | mented bit, read             | l as '0'        |        |  |  |  |

| -n = Value | at POR                                | '1' = Bit is set                                                                                                                              |                | '0' = Bit is cle |                              | x = Bit is unkr | nown   |  |  |  |

|            |                                       |                                                                                                                                               |                |                  |                              |                 |        |  |  |  |

| bit 15     | ADCTS4: Sa                            | mple Trigger P                                                                                                                                | TGO15 for AE   | OC bit           |                              |                 |        |  |  |  |

|            | 1 = Generate                          | es Trigger wher                                                                                                                               | the broadcas   | t command is     | executed                     |                 |        |  |  |  |

|            | 0 = Does not                          | generate Trigg                                                                                                                                | er when the b  | roadcast com     | mand is execute              | ed              |        |  |  |  |

| bit 14     |                                       | mple Trigger P                                                                                                                                |                |                  |                              |                 |        |  |  |  |

|            |                                       | es Trigger wher                                                                                                                               |                |                  |                              | al              |        |  |  |  |

| bit 13     |                                       |                                                                                                                                               |                |                  | mand is execute              | a               |        |  |  |  |

| DIE 13     |                                       | mple Trigger P<br>es Trigger wher                                                                                                             |                |                  | evecuted                     |                 |        |  |  |  |

|            |                                       |                                                                                                                                               |                |                  | mand is execute              | ed              |        |  |  |  |

| bit 12     |                                       | mple Trigger P                                                                                                                                |                |                  |                              |                 |        |  |  |  |

|            | 1 = Generate                          | es Trigger wher                                                                                                                               | the broadcas   | t command is     | executed                     |                 |        |  |  |  |

|            |                                       |                                                                                                                                               |                |                  | mand is execute              | ed              |        |  |  |  |

| bit 11     | -                                     | C4TSS: Trigger/Synchronization Source for IC4 bit                                                                                             |                |                  |                              |                 |        |  |  |  |

|            |                                       |                                                                                                                                               |                |                  | ast command is broadcast con |                 | ited   |  |  |  |

| bit 10     | IC3TSS: Trig                          | ger/Synchroniz                                                                                                                                | ation Source f | for IC3 bit      |                              |                 |        |  |  |  |

|            |                                       |                                                                                                                                               |                |                  | ast command is broadcast con |                 | ited   |  |  |  |

| bit 9      | IC2TSS: Trig                          | ger/Synchroniz                                                                                                                                | ation Source f | for IC2 bit      |                              |                 |        |  |  |  |

|            |                                       |                                                                                                                                               |                |                  | ast command is broadcast con |                 | ited   |  |  |  |

| bit 8      |                                       | ger/Synchroniz                                                                                                                                |                |                  |                              |                 |        |  |  |  |

|            |                                       |                                                                                                                                               |                |                  | ast command is broadcast con |                 | ited   |  |  |  |

| bit 7      |                                       | <ul> <li>Does not generate Trigger/Synchronization when the broadcast command is executed</li> <li>OC4CS: Clock Source for OC4 bit</li> </ul> |                |                  |                              |                 |        |  |  |  |

|            |                                       | es clock pulse v<br>generate clock                                                                                                            |                |                  |                              | cuted           |        |  |  |  |

| bit 6      |                                       | <ul> <li>Does not generate clock pulse when the broadcast command is executed</li> <li>OC3CS: Clock Source for OC3 bit</li> </ul>             |                |                  |                              |                 |        |  |  |  |

|            |                                       | es clock pulse v<br>aenerate clock                                                                                                            |                |                  | d is executed command is exe | cuted           |        |  |  |  |

| bit 5      |                                       | ck Source for C                                                                                                                               | -              |                  |                              |                 |        |  |  |  |

|            | 1 = Generate                          | es clock pulse v                                                                                                                              | when the broad |                  | d is executed command is exe | cuted           |        |  |  |  |

|            | This register is rea<br>PTGSTRT = 1). | -                                                                                                                                             |                |                  |                              |                 | and    |  |  |  |

|            | This register is on                   | lv used with the                                                                                                                              | PTGCTRI. OI    | PTION = 1111     | Step command                 | L               |        |  |  |  |

|            |                                       | .,                                                                                                                                            |                |                  | c.op commune                 | •               |        |  |  |  |

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup>

## 24.4 Step Commands and Format

#### TABLE 24-1: PTG STEP COMMAND FORMAT

| Step Command Byte: |             |             |  |  |  |  |

|--------------------|-------------|-------------|--|--|--|--|

| STEPx<7:0>         |             |             |  |  |  |  |

| CMD<3:0>           |             | OPTION<3:0> |  |  |  |  |

| bit 7              | bit 4 bit 3 | bit 0       |  |  |  |  |

| bit 7-4 | CMD<3:0> | Step<br>Command | Command Description                                                                                                                                                                      |