Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

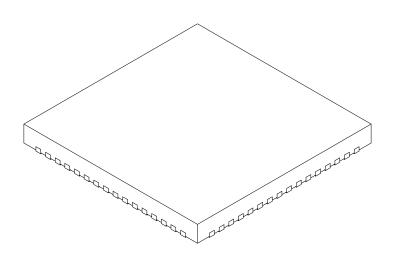

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8×8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc504-h-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

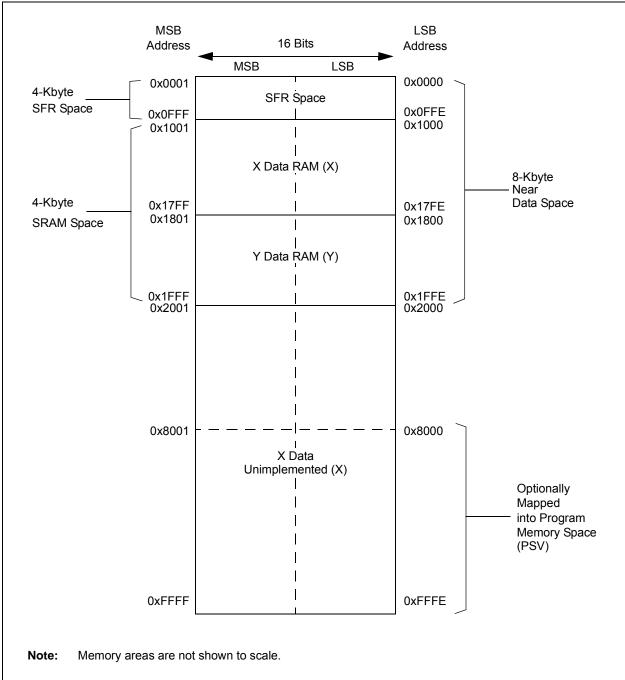

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

| IABLE 4         | Image: ABLE 4-16:       QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY |        |                   |          |            |            |          |          |             |        |        |            |          | r      |        |        |        |               |

|-----------------|------------------------------------------------------------------------------------------------------|--------|-------------------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| File Name       | Addr.                                                                                                | Bit 15 | Bit 14            | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON         | 01C0                                                                                                 | QEIEN  | —                 | QEISIDL  |            | PIMOD<2:0> |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI1IOC         | 01C2                                                                                                 | QCAPEN | FLTREN            |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| <b>QEI1STAT</b> | 01C4                                                                                                 | _      | _                 | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL        | 01C6                                                                                                 |        | POSCNT<15:0> 000  |          |            |            |          |          |             |        |        |            |          |        |        | 0000   |        |               |

| POS1CNTH        | 01C8                                                                                                 |        | POSCNT<31:16> 000 |          |            |            |          |          |             |        |        |            |          |        |        | 0000   |        |               |

| POS1HLD         | 01CA                                                                                                 |        |                   |          |            |            |          |          | POSHLD<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| VEL1CNT         | 01CC                                                                                                 |        |                   |          |            |            |          |          | VELCNT<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRL        | 01CE                                                                                                 |        |                   |          |            |            |          |          | INTTMR<15:  | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRH        | 01D0                                                                                                 |        | INTTMR<31:16> 00  |          |            |            |          |          |             |        |        |            |          | 0000   |        |        |        |               |

| INT1HLDL        | 01D2                                                                                                 |        |                   |          |            |            |          |          | INTHLD<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDH        | 01D4                                                                                                 |        |                   |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL       | 01D6                                                                                                 |        |                   |          |            |            |          |          | INDXCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH       | 01D8                                                                                                 |        |                   |          |            |            |          |          | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD        | 01DA                                                                                                 |        |                   |          |            |            |          |          | INDXHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL        | 01DC                                                                                                 |        |                   |          |            |            |          |          | QEIGEC<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1ICL</b>  | 01DC                                                                                                 |        |                   |          |            |            |          |          | QEIIC<15:0  | >      |        |            |          |        |        |        |        | 0000          |

| QEI1GECH        | 01DE                                                                                                 |        |                   |          |            |            |          |          | QEIGEC<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| QEI1ICH         | 01DE                                                                                                 |        |                   |          |            |            |          |          | QEIIC<31:16 | š>     |        |            |          |        |        |        |        | 0000          |

| QEI1LECL        | 01E0                                                                                                 |        |                   |          |            |            |          |          | QEILEC<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1LECH</b> | 01E2                                                                                                 |        |                   |          |            |            |          |          | QEILEC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 4.8 Interfacing Program and Data Memory Spaces

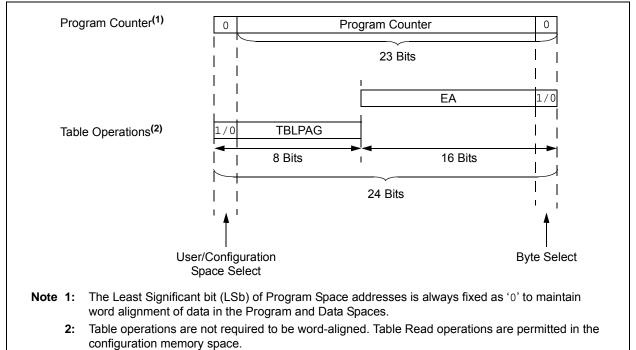

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

### TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address        |          |               |        |     |  |  |  |

|------------------------|---------------|------------------------------|----------|---------------|--------|-----|--|--|--|

| Access Type            | Space         | <23>                         | <22:16>  | <15>          | <14:1> | <0> |  |  |  |

| Instruction Access     | User          | 0                            | PC<22:1> |               |        |     |  |  |  |

| (Code Execution)       |               | 0xx xxxx xxxx xxxx xxxx xxx0 |          |               |        |     |  |  |  |

| TBLRD/TBLWT            | User          | TBLPAG<7:0> Data EA<15:0>    |          |               |        |     |  |  |  |

| (Byte/Word Read/Write) |               | 0                            | xxx xxxx | XXXX XXX      | ***    |     |  |  |  |

|                        | Configuration | TBLPAG<7:0>                  |          | Data EA<15:0> |        |     |  |  |  |

|                        |               | 1                            | xxx xxxx | XXXX XX       | ***    |     |  |  |  |

### FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

## 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

### 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

### 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

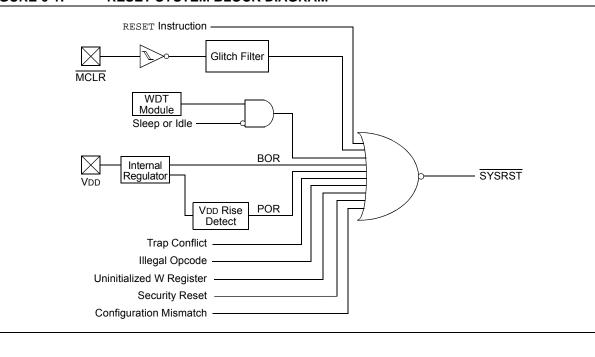

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

## 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

## 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

## 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "*dsPIC33/PIC24 Family Reference Manual*".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

| U-0                                                                | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0 |  |

|--------------------------------------------------------------------|--------------|----------------------------------------------------------|---------------|-------------------|---------------|-----------------|-------|--|

| —                                                                  |              |                                                          |               | IC4R<6:0>         |               |                 |       |  |

| bit 15                                                             |              |                                                          |               |                   |               |                 | bit 8 |  |

|                                                                    |              |                                                          |               |                   |               |                 |       |  |

| U-0                                                                | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0 |  |

| —                                                                  |              |                                                          |               | IC3R<6:0>         |               |                 |       |  |

| bit 7                                                              |              |                                                          |               |                   |               |                 | bit C |  |

|                                                                    |              |                                                          |               |                   |               |                 |       |  |

| Legend:                                                            |              |                                                          |               |                   |               |                 |       |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |              |                                                          |               |                   |               |                 |       |  |

| -n = Value a                                                       | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown  |  |

|                                                                    | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |               |                 |       |  |

| bit 7                                                              | Unimpleme    | nted: Read as 'o                                         | )'            |                   |               |                 |       |  |

| bit 6-0                                                            | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi | n bits          |       |  |

## REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

### REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|--------------------|-------|--|

| —            |                           |                                                                                                    |                            | QEB1R<6:0>        |                 |                    |       |  |

| bit 15       |                           |                                                                                                    |                            |                   |                 |                    | bit 8 |  |

|              |                           |                                                                                                    |                            |                   |                 |                    |       |  |

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

| —            |                           |                                                                                                    |                            | QEA1R<6:0>        |                 |                    |       |  |

| bit 7        |                           |                                                                                                    |                            |                   |                 |                    | bit 0 |  |

|              |                           |                                                                                                    |                            |                   |                 |                    |       |  |

| Legend:      |                           |                                                                                                    |                            |                   |                 |                    |       |  |

| R = Readat   | ole bit                   | W = Writable                                                                                       | bit                        | U = Unimplen      | nented bit, rea | ad as '0'          |       |  |

| -n = Value a | at POR                    | '1' = Bit is set                                                                                   |                            | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |

|              | 1111001 =                 | 1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss                    | 121<br>P1                  |                   |                 |                    |       |  |

| bit 7        | Unimpleme                 | nted: Read as '                                                                                    | 0'                         |                   |                 |                    |       |  |

| bit 6-0      | (see Table 1<br>1111001 = | >: Assign A (QE<br>1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss | selection nun<br>121<br>P1 |                   | n Pin bits      |                    |       |  |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

| R-0 | R-0              | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |

|-----|------------------|------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|     |                  | TERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |

|     |                  |                              |                                                    |                                                                                                |                                                                                           | bit 8                                                                                                                |

|     |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

| R-0 | R-0              | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |

|     |                  | RERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |

|     |                  |                              |                                                    |                                                                                                |                                                                                           | bit 0                                                                                                                |

|     |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

|     |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

| oit | W = Writable b   | it                           | U = Unimplemented bit, read as '0'                 |                                                                                                |                                                                                           |                                                                                                                      |

| OR  | '1' = Bit is set |                              | '0' = Bit is cleared x = Bit is unknow             |                                                                                                |                                                                                           |                                                                                                                      |

|     | R-0              | R-0 R-0<br>it W = Writable b | TERR<br>R-0 R-0 R-0<br>RERR<br>it W = Writable bit | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT<7:0> | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT | TERRCNT<7:0>         R-0       R-0       R-0       R-0         RERRCNT<7:0>       U = Unimplemented bit, read as '0' |

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

| bit 7-6 | SJW<1:0>: Synchronization Jump Width bits    |

|---------|----------------------------------------------|

|         | 11 = Length is 4 x TQ                        |

|         | $10 = \text{Length is } 3 \times \text{Tq}$  |

|         | $01 = \text{Length is } 2 \times \text{T} Q$ |

|         | $00 = \text{Length is } 1 \times \text{Tq}$  |

```

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

```

```

11 1111 = TQ = 2 x 64 x 1/FCAN

```

•

- 00 0010 = TQ = 2 x 3 x 1/FCAN 00 0001 = TQ = 2 x 2 x 1/FCAN

- 00 0000 = Tq = 2 x 1 x 1/FCAN

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

#### REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

RXOVF4

| bit 7            |                                                                |                                    | bit 0 |  |  |

|------------------|----------------------------------------------------------------|------------------------------------|-------|--|--|

|                  |                                                                |                                    |       |  |  |

| Legend:          | C = Writable bit, but only '0' can be written to clear the bit |                                    |       |  |  |

| R = Readable bit | W = Writable bit                                               | U = Unimplemented bit, read as '0' |       |  |  |

RXOVF3

RXOVF2

| R = Readable bit  | vv = vvritable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|--------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

RXOVF6

RXOVF7

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

RXOVF5

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0     | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   |

|-----------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23   | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7 bit |         |         |         |         |         |         |         |

| Legend:           | C = Writable bit, but or | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit                                          | t, read as '0'     |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

RXOVF0

RXOVF1

NOTES:

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                            | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|--------------------------------------------------|------------------------------------|-------|-------|-------|

|                 |       |                  | PTGT0                                            | _IM<15:8>                          |       |       |       |

| bit 15          |       |                  |                                                  |                                    |       |       | bit 8 |

|                 |       |                  |                                                  |                                    |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                            | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | PTGT0                                            | LIM<7:0>                           |       |       |       |

| bit 7           |       |                  |                                                  |                                    |       |       | bit 0 |

|                 |       |                  |                                                  |                                    |       |       |       |

| Legend:         |       |                  |                                                  |                                    |       |       |       |

| R = Readable    | bit   | W = Writable b   | bit                                              | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at P | POR   | '1' = Bit is set | it is set '0' = Bit is cleared x = Bit is unknow |                                    |       | nown  |       |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGT1LIM<15:8> |       |       |       |       |       |       |       |  |

| bit 15         |       |       |       |       |       |       | bit 8 |  |

|                |       |       |       |       |       |       |       |  |

| R/W-0         | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|---------------|-------------|-------|-------|-------|-------|-------|-------|--|--|

| PTGT1LIM<7:0> |             |       |       |       |       |       |       |  |  |

| bit 7         | bit 7 bit 0 |       |       |       |       |       |       |  |  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

| Base<br>Instr<br># | Assembly<br>Mnemonic Assembly Syntax Description |                                  | # of<br>Words                                    | # of<br>Cycles <sup>(2)</sup>               | Status Flags<br>Affected |    |                         |  |

|--------------------|--------------------------------------------------|----------------------------------|--------------------------------------------------|---------------------------------------------|--------------------------|----|-------------------------|--|

| 25 DAW             |                                                  | DAW Wn Wn Wn = decimal adjust Wn |                                                  | Wn = decimal adjust Wn                      | 1                        | 1  | С                       |  |

| 26                 | DEC                                              | DEC                              | f                                                | f = f - 1                                   | 1                        | 1  | C,DC,N,OV,Z             |  |

|                    |                                                  | DEC                              | f,WREG                                           | WREG = f – 1                                | 1                        | 1  | C,DC,N,OV,Z             |  |

|                    |                                                  | DEC                              | Ws,Wd                                            | Wd = Ws - 1                                 | 1                        | 1  | C,DC,N,OV,Z             |  |

| 27                 | DEC2                                             | DEC2                             | f                                                | f = f - 2                                   | 1                        | 1  | C,DC,N,OV,Z             |  |

|                    |                                                  | DEC2                             | f,WREG                                           | WREG = f – 2                                | 1                        | 1  | C,DC,N,OV,Z             |  |

|                    |                                                  | DEC2                             | Ws,Wd                                            | Wd = Ws - 2                                 | 1                        | 1  | C,DC,N,OV,Z             |  |

| 28                 | DISI                                             | DISI                             | #lit14                                           | Disable Interrupts for k instruction cycles | 1                        | 1  | None                    |  |

| 29                 | DIV                                              | DIV.S                            | Wm,Wn                                            | Signed 16/16-bit Integer Divide             | 1                        | 18 | N,Z,C,OV                |  |

|                    |                                                  | DIV.SD                           | Wm,Wn                                            | Signed 32/16-bit Integer Divide             | 1                        | 18 | N,Z,C,OV                |  |

|                    |                                                  | DIV.U                            | Wm,Wn                                            | Unsigned 16/16-bit Integer Divide           | 1                        | 18 | N,Z,C,OV                |  |

|                    |                                                  | DIV.UD                           | Wm,Wn                                            | Unsigned 32/16-bit Integer Divide           | 1                        | 18 | N,Z,C,OV                |  |

| 30                 | DIVF                                             | DIVF                             | Wm , Wn <sup>(1)</sup>                           | Signed 16/16-bit Fractional Divide          | 1                        | 18 | N,Z,C,OV                |  |

| 31                 | DO                                               | DO                               | #lit15,Expr <sup>(1)</sup>                       | Do code to PC + Expr, lit15 + 1 times       | 2                        | 2  | None                    |  |

|                    |                                                  | DO                               | Wn, Expr(1)                                      | Do code to PC + Expr, (Wn) + 1 times        | 2                        | 2  | None                    |  |

| 32                 | ED                                               | ED                               | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance (no accumulate)          | 1                        | 1  | OA,OB,OAB,<br>SA,SB,SAB |  |

| 33                 | EDAC                                             | EDAC                             | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance                          | 1                        | 1  | OA,OB,OAB,<br>SA,SB,SAB |  |

| 34                 | EXCH                                             | EXCH                             | Wns,Wnd                                          | Swap Wns with Wnd                           | 1                        | 1  | None                    |  |

| 35                 | FBCL                                             | FBCL                             | Ws,Wnd                                           | Find Bit Change from Left (MSb) Side        | 1                        | 1  | С                       |  |

| 36                 | FF1L                                             | FF1L                             | Ws,Wnd                                           | Find First One from Left (MSb) Side         |                          | 1  | С                       |  |

| 37                 | FF1R                                             | FF1R                             | Ws,Wnd                                           | Find First One from Right (LSb) Side        |                          | 1  | С                       |  |

| 38                 | GOTO                                             | GOTO                             | Expr                                             | Go to address                               | 2                        | 4  | None                    |  |

|                    |                                                  | GOTO                             | Wn                                               | Go to indirect                              | 1                        | 4  | None                    |  |

|                    |                                                  | GOTO.L                           | Wn                                               | Go to indirect (long address)               | 1                        | 4  | None                    |  |

| 39                 | INC                                              | INC                              | f                                                | f = f + 1                                   | 1                        | 1  | C,DC,N,OV,Z             |  |

|                    |                                                  | INC                              | f,WREG                                           | WREG = f + 1                                | 1                        | 1  | C,DC,N,OV,Z             |  |

|                    |                                                  | INC                              | Ws,Wd                                            | Wd = Ws + 1                                 | 1                        | 1  | C,DC,N,OV,Z             |  |

| 40                 | INC2                                             | INC2                             | f                                                | f = f + 2                                   | 1                        | 1  | C,DC,N,OV,Z             |  |

|                    |                                                  | INC2                             | f,WREG                                           | WREG = f + 2                                | 1                        | 1  | C,DC,N,OV,Z             |  |

|                    |                                                  | INC2                             | Ws,Wd                                            | Wd = Ws + 2                                 | 1                        | 1  | C,DC,N,OV,Z             |  |

| 41                 | IOR                                              | IOR                              | f                                                | f = f .IOR. WREG                            | 1                        | 1  | N,Z                     |  |

|                    |                                                  | IOR                              | f,WREG                                           | WREG = f .IOR. WREG                         | 1                        | 1  | N,Z                     |  |

|                    |                                                  | IOR                              | #litl0,Wn                                        | Wd = lit10 .IOR. Wd                         | 1                        | 1  | N,Z                     |  |

|                    |                                                  | IOR                              | Wb,Ws,Wd                                         | Wd = Wb .IOR. Ws                            | 1                        | 1  | N,Z                     |  |

|                    |                                                  | IOR                              | Wb,#lit5,Wd                                      | Wd = Wb .IOR. lit5                          | 1                        | 1  | N,Z                     |  |

| 42                 | LAC                                              | LAC                              | Wso,#Slit4,Acc                                   | Load Accumulator                            | 1                        | 1  | OA,OB,OAB,<br>SA,SB,SAB |  |

| 43                 | LNK                                              | LNK                              | #lit14                                           | Link Frame Pointer                          | 1                        | 1  | SFA                     |  |

| 44                 | LSR                                              | LSR                              | f                                                | f = Logical Right Shift f                   | 1                        | 1  | C,N,OV,Z                |  |

|                    |                                                  | LSR                              | f,WREG                                           | WREG = Logical Right Shift f                | 1                        | 1  | C,N,OV,Z                |  |

|                    |                                                  | LSR                              | Ws,Wd                                            | Wd = Logical Right Shift Ws                 | 1                        | 1  | C,N,OV,Z                |  |

|                    |                                                  | LSR                              | Wb,Wns,Wnd                                       | Wnd = Logical Right Shift Wb by Wns         | 1                        | 1  | N,Z                     |  |

|                    |                                                  | LSR                              | Wb,#lit5,Wnd                                     | Wnd = Logical Right Shift Wb by lit5        | 1                        | 1  | N,Z                     |  |

| 45                 | MAC                                              | MAC                              | Wm*Wn, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Accumulate                     | 1                        | 1  | OA,OB,OAB,<br>SA,SB,SAB |  |

|                    |                                                  | MAC                              | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd <sup>(1)</sup>      | Square and Accumulate                       | 1                        | 1  | OA,OB,OAB,<br>SA,SB,SAB |  |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

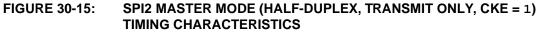

#### TABLE 30-34: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |    |            |                                |

|--------------------|-----------------------|----------------------------------------------|-------------------------------------------------------|---|----|------------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min. Typ. <sup>(2)</sup> Max. Units Conditions        |   |    | Conditions |                                |

| SP10               | FscP                  | Maximum SCK2 Frequency                       | —                                                     | _ | 15 | MHz        | (Note 3)                       |

| SP20               | TscF                  | SCK2 Output Fall Time                        | —                                                     | — | _  | ns         | See Parameter DO32<br>(Note 4) |

| SP21               | TscR                  | SCK2 Output Rise Time                        | —                                                     | — | _  | ns         | See Parameter DO31<br>(Note 4) |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                   | —                                                     | — | _  | ns         | See Parameter DO32<br>(Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                   | -                                                     | _ |    | ns         | See Parameter DO31<br>(Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge    | —                                                     | 6 | 20 | ns         |                                |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge | 30                                                    | — | _  | ns         |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACTERISTICS |                  | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |                              |                     |                              |        |                                            |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------|------------------------------|--------|--------------------------------------------|

| Param<br>No.       | Symbol           | Characteristic                                                                                                                                                                                                                                                                                  | Min.                         | Тур. <sup>(2)</sup> | Max.                         | Units  | Conditions                                 |

| Op Am              | p DC Chara       | cteristics                                                                                                                                                                                                                                                                                      |                              |                     |                              |        |                                            |

| CM40               | VCMR             | Common-Mode Input<br>Voltage Range                                                                                                                                                                                                                                                              | AVss                         | _                   | AVDD                         | V      |                                            |

| CM41               | CMRR             | Common-Mode<br>Rejection Ratio <sup>(3)</sup>                                                                                                                                                                                                                                                   | —                            | 40                  | —                            | db     | VCM = AVDD/2                               |

| CM42               | VOFFSET          | Op Amp Offset<br>Voltage <sup>(3)</sup>                                                                                                                                                                                                                                                         | —                            | ±5                  | —                            | mV     |                                            |

| CM43               | Vgain            | Open-Loop Voltage<br>Gain <sup>(3)</sup>                                                                                                                                                                                                                                                        | _                            | 90                  | _                            | db     |                                            |

| CM44               | los              | Input Offset Current                                                                                                                                                                                                                                                                            | _                            | -                   | _                            | _      | See pad leakage currents in Table 30-11    |

| CM45               | lв               | Input Bias Current                                                                                                                                                                                                                                                                              | _                            | _                   | _                            | _      | See pad leakage currents in Table 30-11    |

| CM46               | Ιουτ             | Output Current                                                                                                                                                                                                                                                                                  | _                            |                     | 420                          | μA     | With minimum value of RFEEDBACK (CM48)     |

| CM48               | RFEEDBACK        | Feedback Resistance<br>Value                                                                                                                                                                                                                                                                    | 8                            | -                   | _                            | kΩ     |                                            |

| CM49a              | VOADC            | Output Voltage                                                                                                                                                                                                                                                                                  | AVss + 0.077                 | —                   | AVDD - 0.077                 | V      | Ιουτ = 420 μΑ                              |

|                    |                  | Measured at OAx Using                                                                                                                                                                                                                                                                           | AVss + 0.037                 | —                   | AVDD - 0.037                 | V      | Ιουτ = 200 μΑ                              |

|                    |                  | ADC <sup>(3,4)</sup>                                                                                                                                                                                                                                                                            | AVss + 0.018                 |                     | AVDD - 0.018                 | V      | Ιουτ = 100 μΑ                              |

| CM49b              | VOUT             | Output Voltage                                                                                                                                                                                                                                                                                  | AVss + 0.210                 | —                   | AVDD - 0.210                 | V      | Ιουτ = 420 μΑ                              |

|                    |                  | Measured at OAxOUT<br>Pin <sup>(3,4,5)</sup>                                                                                                                                                                                                                                                    | AVss + 0.100<br>AVss + 0.050 | _                   | AVDD – 0.100<br>AVDD – 0.050 | V<br>V | Ιουτ = 200 μΑ<br>Ιουτ = 100 μΑ             |

| CM51               | RINT1 <b>(6)</b> | Internal Resistance 1<br>(Configuration A<br>and B) <sup>(3,4,5)</sup>                                                                                                                                                                                                                          | 198                          | 264                 | 317                          | Ω      | Min = -40°C<br>Typ = +25°C<br>Max = +125°C |

#### TABLE 30-53: OP AMP/COMPARATOR SPECIFICATIONS (CONTINUED)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** Parameter is characterized but not tested in manufacturing.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: Resistances can vary by ±10% between op amps.

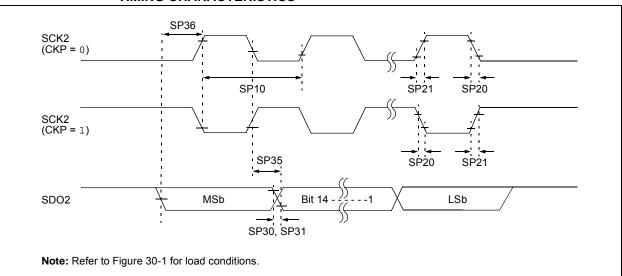

#### 33.2 Package Details

#### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES   |       |          |       |  |  |

|----------------------------|----------|-------|----------|-------|--|--|

| Dimension                  | n Limits | MIN   | NOM      | MAX   |  |  |

| Number of Pins             | Ν        | 28    |          |       |  |  |

| Pitch                      | е        |       | .100 BSC |       |  |  |

| Top to Seating Plane       | Α        | -     | -        | .200  |  |  |

| Molded Package Thickness   | A2       | .120  | .135     | .150  |  |  |

| Base to Seating Plane      | A1       | .015  | -        | -     |  |  |

| Shoulder to Shoulder Width | E        | .290  | .310     | .335  |  |  |

| Molded Package Width       | E1       | .240  | .285     | .295  |  |  |

| Overall Length             | D        | 1.345 | 1.365    | 1.400 |  |  |

| Tip to Seating Plane       | L        | .110  | .130     | .150  |  |  |

| Lead Thickness             | С        | .008  | .010     | .015  |  |  |

| Upper Lead Width           | b1       | .040  | .050     | .070  |  |  |

| Lower Lead Width           | b        | .014  | .018     | .022  |  |  |

| Overall Row Spacing §      | eB       | _     | -        | .430  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                  |                       | MILLIMETERS |          |      |  |

|------------------------|-----------------------|-------------|----------|------|--|

| Dimension              | Limits                | MIN         | NOM      | MAX  |  |

| Number of Pins         | N                     |             | 64       |      |  |

| Pitch                  | е                     |             | 0.50 BSC |      |  |

| Overall Height         | A                     | 0.80        | 0.90     | 1.00 |  |

| Standoff               | A1                    | 0.00        | 0.02     | 0.05 |  |

| Contact Thickness      | A3                    | 0.20 REF    |          |      |  |

| Overall Width          | rall Width E 9.00 BSC |             |          |      |  |

| Exposed Pad Width      | E2                    | 5.30        | 5.40     | 5.50 |  |

| Overall Length         | D                     | 9.00 BSC    |          |      |  |

| Exposed Pad Length     | D2                    | 5.30        | 5.40     | 5.50 |  |

| Contact Width          | b                     | 0.20        | 0.25     | 0.30 |  |

| Contact Length         | L                     | 0.30        | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K                     | 0.20        | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2

| Section Name                                                                                              | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

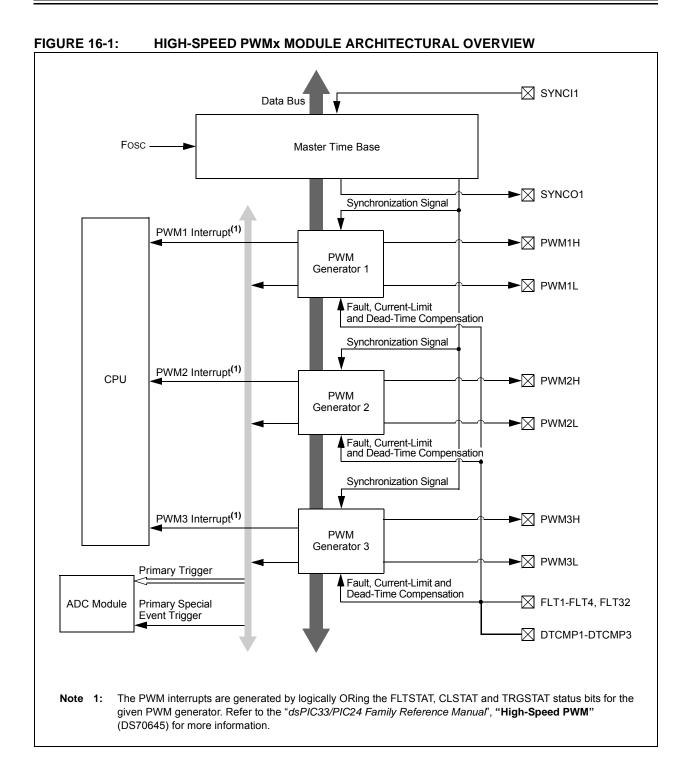

| Section 16.0 "High-Speed<br>PWM Module<br>(dsPIC33EPXXXMC20X/50X<br>and PIC24EPXXXMC20X<br>Devices Only)" | Updated the High-Speed PWM Module Register Interconnection Diagram (see Figure 16-2).<br>Added the TRGCONx and TRIGx registers (see Register 16-12 and Register 16-14, respectively).                                                                                                                                                                                                                                                                                                         |