Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

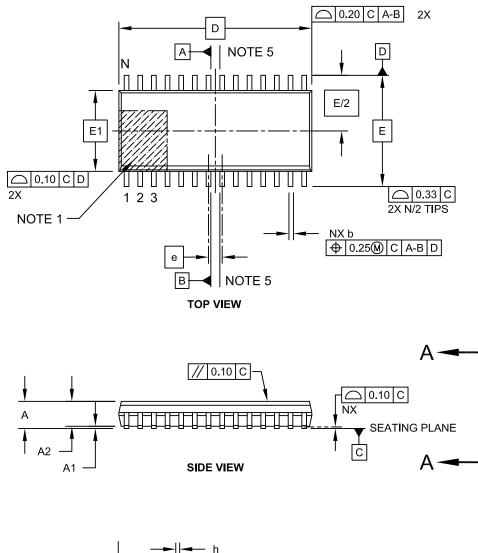

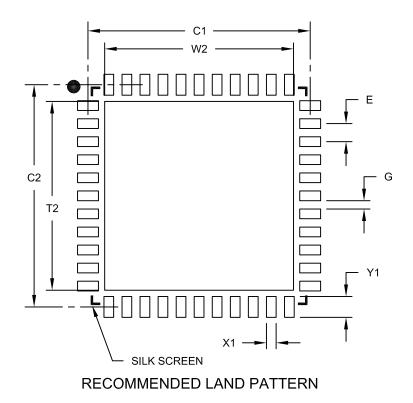

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc504-h-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.7 CPU Control Registers

| REGISTER               | 3-1: SR: CI                                                                                                             | PU STATUS I                                                           | REGISTER                    |                    |                    |                   |               |  |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------|--------------------|--------------------|-------------------|---------------|--|--|--|--|

| R/W-0                  | R/W-0                                                                                                                   | R/W-0                                                                 | R/W-0                       | R/C-0              | R/C-0              | R-0               | R/W-0         |  |  |  |  |

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>                                                                                                       | SA <sup>(1,4)</sup>                                                   | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup> | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC            |  |  |  |  |

| bit 15                 |                                                                                                                         |                                                                       |                             |                    |                    |                   | bit 8         |  |  |  |  |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                                                                                                  | R/W-0 <sup>(2,3)</sup>                                                | R-0                         | R/W-0              | R/W-0              | R/W-0             | R/W-0         |  |  |  |  |

| IPL2                   | IPL1                                                                                                                    | IPL0                                                                  | RA                          | N                  | OV                 | Z                 | С             |  |  |  |  |

| bit 7                  | ·                                                                                                                       | •                                                                     |                             | •                  |                    |                   | bit (         |  |  |  |  |

| Legend:                |                                                                                                                         | C = Clearable                                                         | e bit                       |                    |                    |                   |               |  |  |  |  |

| R = Readab             | le bit                                                                                                                  | W = Writable                                                          | bit                         | U = Unimpler       | nented bit, read   | l as '0'          |               |  |  |  |  |

| -n = Value a           | t POR                                                                                                                   | '1'= Bit is set                                                       |                             | '0' = Bit is cle   | ared               | x = Bit is unkr   | iown          |  |  |  |  |

|                        |                                                                                                                         |                                                                       |                             |                    |                    |                   |               |  |  |  |  |

| bit 15                 | OA: Accumul                                                                                                             | ator A Overflov                                                       | v Status bit <sup>(1)</sup> |                    |                    |                   |               |  |  |  |  |

|                        | 1 = Accumula                                                                                                            | ator A has over                                                       | flowed                      |                    |                    |                   |               |  |  |  |  |

|                        | 0 = Accumula                                                                                                            | ator A has not o                                                      | verflowed                   |                    |                    |                   |               |  |  |  |  |

| bit 14                 | OB: Accumul                                                                                                             | ator B Overflov                                                       | v Status bit <sup>(1)</sup> |                    |                    |                   |               |  |  |  |  |

|                        | 1 = Accumulator B has overflowed                                                                                        |                                                                       |                             |                    |                    |                   |               |  |  |  |  |

|                        |                                                                                                                         | 0 = Accumulator B has not overflowed                                  |                             |                    |                    |                   |               |  |  |  |  |

| bit 13                 | SA: Accumulator A Saturation 'Sticky' Status bit <sup>(1,4)</sup>                                                       |                                                                       |                             |                    |                    |                   |               |  |  |  |  |

|                        |                                                                                                                         | ator A is saturat<br>ator A is not sat                                |                             | en saturated at    | some time          |                   |               |  |  |  |  |

| bit 12                 | <b>SB:</b> Accumulator B Saturation 'Sticky' Status bit <sup>(1,4)</sup>                                                |                                                                       |                             |                    |                    |                   |               |  |  |  |  |

|                        | 1 = Accumula                                                                                                            | ator B is saturat<br>ator B is not sat                                | ted or has bee              |                    | some time          |                   |               |  |  |  |  |

| bit 11                 |                                                                                                                         |                                                                       |                             | vorflow Status     | ы#(1)              |                   |               |  |  |  |  |

|                        | <b>OAB:</b> OA    OB Combined Accumulator Overflow Status bit <sup>(1)</sup><br>1 = Accumulators A or B have overflowed |                                                                       |                             |                    |                    |                   |               |  |  |  |  |

|                        | 1 = Accumulators A or B have overflowed<br>0 = Neither Accumulators A or B have overflowed                              |                                                                       |                             |                    |                    |                   |               |  |  |  |  |

| bit 10                 |                                                                                                                         | SAB: SA    SB Combined Accumulator 'Sticky' Status bit <sup>(1)</sup> |                             |                    |                    |                   |               |  |  |  |  |

|                        | 1 = Accumulators A or B are saturated or have been saturated at some time                                               |                                                                       |                             |                    |                    |                   |               |  |  |  |  |

|                        | 0 = Neither A                                                                                                           | ccumulators A                                                         | or B are satur              | ated               |                    |                   |               |  |  |  |  |

| bit 9                  | DA: DO Loop                                                                                                             | Active bit <sup>(1)</sup>                                             |                             |                    |                    |                   |               |  |  |  |  |

|                        | 1 = DO <b>loop is</b>                                                                                                   | 1 = DO  loop is in progress                                           |                             |                    |                    |                   |               |  |  |  |  |

|                        | 0 = DO loop is not in progress                                                                                          |                                                                       |                             |                    |                    |                   |               |  |  |  |  |

| bit 8                  | DC: MCU AL                                                                                                              | U Half Carry/Bo                                                       | orrow bit                   |                    |                    |                   |               |  |  |  |  |

|                        |                                                                                                                         | out from the 4th sult occurred                                        | low-order bit (             | for byte-sized c   | lata) or 8th low-  | order bit (for wo | rd-sized data |  |  |  |  |

|                        | 0 = No carry                                                                                                            |                                                                       |                             | oit (for byte-siz  | ed data) or 8th    | low-order bit (f  | or word-size  |  |  |  |  |

|                        | his bit is available                                                                                                    |                                                                       |                             |                    |                    |                   | -             |  |  |  |  |

| L                      | he IPL<2:0> bits<br>evel. The value ir<br>PL<3> = 1.                                                                    |                                                                       |                             |                    |                    |                   |               |  |  |  |  |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

| 0/11        |                     |                | Before       |                        | After          |              |                        |  |  |  |  |  |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|--|--|--|--|

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |  |  |  |  |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |  |  |  |  |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |  |  |  |  |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |  |  |  |  |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |  |  |  |  |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |  |  |  |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |  |  |  |  |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |  |  |  |  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0          | U-0          | U-0                                                                                               | U-0           | U-0                                     | U-0              | U-0    | U-0    |  |  |  |  |

|--------------|--------------|---------------------------------------------------------------------------------------------------|---------------|-----------------------------------------|------------------|--------|--------|--|--|--|--|

| —            | —            | —                                                                                                 | —             | —                                       | —                | —      | —      |  |  |  |  |

| bit 15       |              |                                                                                                   |               |                                         |                  |        | bit 8  |  |  |  |  |

|              |              |                                                                                                   |               |                                         |                  |        |        |  |  |  |  |

| U-0          | U-0          | U-0                                                                                               | U-0           | R-0                                     | R-0              | R-0    | R-0    |  |  |  |  |

|              |              | <u> </u>                                                                                          | _             | PWCOL3                                  | PWCOL2           | PWCOL1 | PWCOL0 |  |  |  |  |

| bit 7        |              |                                                                                                   |               |                                         |                  |        | bit 0  |  |  |  |  |

|              |              |                                                                                                   |               |                                         |                  |        |        |  |  |  |  |

| Legend:      |              |                                                                                                   |               |                                         |                  |        |        |  |  |  |  |

| R = Readab   | le bit       | W = Writable                                                                                      | bit           | U = Unimpler                            | mented bit, read | as '0' |        |  |  |  |  |

| -n = Value a | t POR        | '1' = Bit is set                                                                                  |               | '0' = Bit is cleared x = Bit is unknown |                  |        |        |  |  |  |  |

|              |              |                                                                                                   |               |                                         |                  |        |        |  |  |  |  |

| bit 15-4     | Unimplemen   | ted: Read as '                                                                                    | 0'            |                                         |                  |        |        |  |  |  |  |

| bit 3        | PWCOL3: DI   | MA Channel 3 F                                                                                    | Peripheral Wi | rite Collision Fla                      | ag bit           |        |        |  |  |  |  |

|              |              | 1 = Write collision is detected                                                                   |               |                                         |                  |        |        |  |  |  |  |

|              |              | collision is dete                                                                                 |               |                                         |                  |        |        |  |  |  |  |

| bit 2        |              |                                                                                                   | •             | rite Collision Fla                      | ag bit           |        |        |  |  |  |  |

|              |              | <ul> <li>1 = Write collision is detected</li> <li>0 = No write collision is detected</li> </ul>   |               |                                         |                  |        |        |  |  |  |  |

| bit 1        |              |                                                                                                   |               | rito Collision Els                      | a hit            |        |        |  |  |  |  |

| DILI         |              | <b>PWCOL1:</b> DMA Channel 1 Peripheral Write Collision Flag bit<br>= Write collision is detected |               |                                         |                  |        |        |  |  |  |  |

|              |              | collision is dete                                                                                 |               |                                         |                  |        |        |  |  |  |  |

| bit 0        | PWCOL0: DI   | MA Channel 0 F                                                                                    | Peripheral Wi | rite Collision Fla                      | ag bit           |        |        |  |  |  |  |

|              |              | lision is detecte                                                                                 | •             | -                                       | <b>č</b>         |        |        |  |  |  |  |

|              | 0 = No write | collision is dete                                                                                 | ected         |                                         |                  |        |        |  |  |  |  |

|              |              |                                                                                                   |               |                                         |                  |        |        |  |  |  |  |

# REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

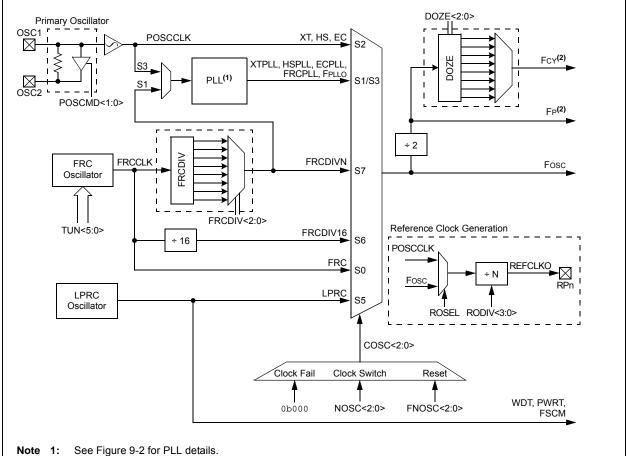

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

# FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **"Oscillator"** (DS70580) in the *"dsPIC33/ PIC24 Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

| U-0          | U-0                 | U-0                                | U-0   | U-0                  | U-0              | U-0                | U-0   |  |  |  |

|--------------|---------------------|------------------------------------|-------|----------------------|------------------|--------------------|-------|--|--|--|

| —            | —                   | —                                  | _     | —                    | —                | —                  | _     |  |  |  |

| bit 15       |                     |                                    |       |                      |                  |                    | bit 8 |  |  |  |

|              |                     |                                    |       |                      |                  |                    |       |  |  |  |

| U-0          | R/W-0               | R/W-0                              | R/W-0 | R/W-0                | R/W-0            | R/W-0              | R/W-0 |  |  |  |

| —            |                     |                                    |       | INT2R<6:0>           |                  |                    |       |  |  |  |

| bit 7        |                     |                                    |       |                      |                  |                    | bit 0 |  |  |  |

|              |                     |                                    |       |                      |                  |                    |       |  |  |  |

| Legend:      |                     |                                    |       |                      |                  |                    |       |  |  |  |

| R = Readal   | ole bit             | W = Writable                       | bit   | U = Unimpler         | mented bit, read | as '0'             |       |  |  |  |

| -n = Value a | at POR              | '1' = Bit is set                   |       | '0' = Bit is cleared |                  | x = Bit is unknown |       |  |  |  |

|              |                     |                                    |       |                      |                  |                    |       |  |  |  |

| bit 15-7     | Unimplemen          | ted: Read as 'd                    | )'    |                      |                  |                    |       |  |  |  |

| bit 6-0      |                     | Assign Externa<br>-2 for input pin |       |                      | orresponding RI  | Pn Pin bits        |       |  |  |  |

|              | 1111001 <b>= lr</b> | 1111001 = Input tied to RPI121     |       |                      |                  |                    |       |  |  |  |

|              |                     |                                    |       |                      |                  |                    |       |  |  |  |

|              |                     |                                    |       |                      |                  |                    |       |  |  |  |

|              | 0000001 – Ir        | put tied to CMI                    | ⊃1    |                      |                  |                    |       |  |  |  |

|              |                     | put tied to Civil                  |       |                      |                  |                    |       |  |  |  |

|              |                     |                                    |       |                      |                  |                    |       |  |  |  |

|              |                     |                                    |       |                      |                  |                    |       |  |  |  |

## REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>— T2CKR<6:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                     |                  |       |                                         |                  |                 |       |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------------------|-------|-----------------------------------------|------------------|-----------------|-------|--|

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0          | U-0                 | U-0              | U-0   | U-0                                     | U-0              | U-0             | U-0   |  |

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _            | -                   | —                | _     | —                                       | —                | —               | —     |  |

| —       T2CKR<6:0>         bit 7       t         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15       |                     |                  |       |                                         |                  |                 | bit 8 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                                         |                  |                 |       |  |

| bit 7       Image: Constraint of the system of | U-0          | R/W-0               | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0           | R/W-0 |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <td< td=""><td>—</td><td></td><td></td><td></td><td>T2CKR&lt;6:0&gt;</td><td>&gt;</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —            |                     |                  |       | T2CKR<6:0>                              | >                |                 |       |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7        |                     |                  |       |                                         |                  |                 | bit 0 |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                     |                  |       |                                         |                  |                 |       |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:      |                     |                  |       |                                         |                  |                 |       |  |

| bit 15-7 Unimplemented: Read as '0'<br>bit 6-0 T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readab   | ole bit             | W = Writable I   | bit   | U = Unimpler                            | mented bit, read | as '0'          |       |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -n = Value a | at POR              | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |                 |       |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                     |                  |       |                                         |                  |                 |       |  |

| (see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15-7     | Unimplemen          | ted: Read as 'd  | )'    |                                         |                  |                 |       |  |

| 1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 6-0      |                     | •                |       | · · ·                                   | he Correspondir  | ng RPn pin bits | 5     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       | ,                                       |                  |                 |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                                         |                  |                 |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                                         |                  |                 |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000001 = Ir        | nout tied to CM  | ⊃1    |                                         |                  |                 |       |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                     |                  |       |                                         |                  |                 |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000000 <b>- II</b> | iput tied to vss |       |                                         |                  |                 |       |  |

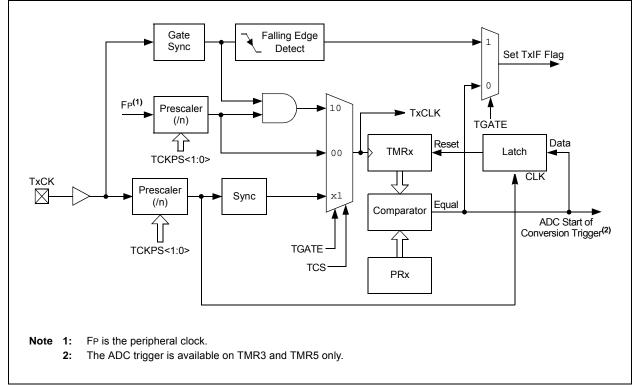

### FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

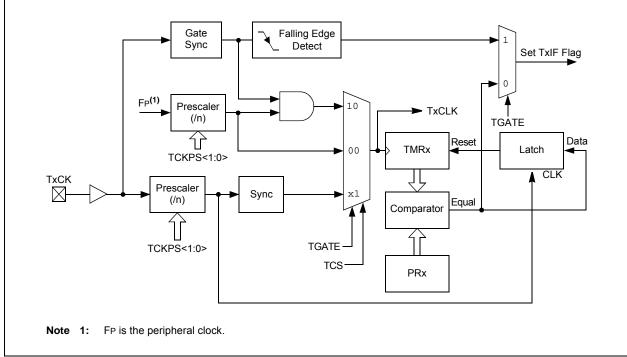

# FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

# 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits  |

|---------|--------------------------------------------------------------|

|         | 11111 = OCxRS compare event is used for synchronization      |

|         | 11110 = INT2 pin synchronizes or triggers OCx                |

|         | 11101 = INT1 pin synchronizes or triggers OCx                |

|         | 11100 = CTMU module synchronizes or triggers OCx             |

|         | 11011 = ADC1 module synchronizes or triggers OCx             |

|         | 11010 = CMP3 module synchronizes or triggers OCx             |

|         | 11001 = CMP2 module synchronizes or triggers OCx             |

|         | 11000 = CMP1 module synchronizes or triggers OCx             |

|         | 10111 = Reserved                                             |

|         | 10110 = Reserved                                             |

|         | 10101 = Reserved                                             |

|         | 10100 = Reserved                                             |

|         | 10011 = IC4 input capture event synchronizes or triggers OCx |

|         | 10010 = IC3 input capture event synchronizes or triggers OCx |

|         | 10001 = IC2 input capture event synchronizes or triggers OCx |

|         | 10000 = IC1 input capture event synchronizes or triggers OCx |