Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betans                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

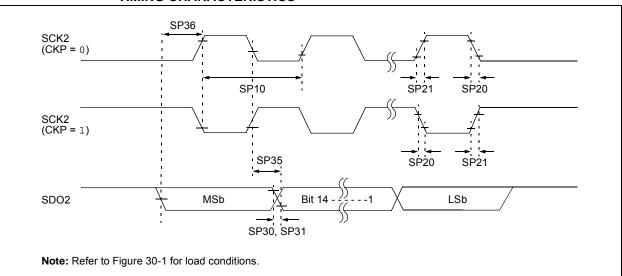

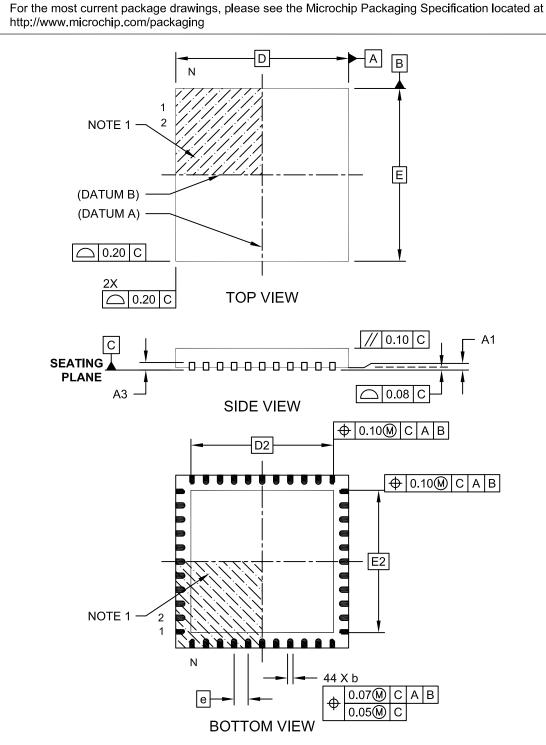

| Mounting Type              | Surface Mount                                                                     |

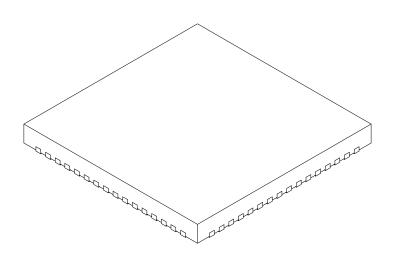

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc504t-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

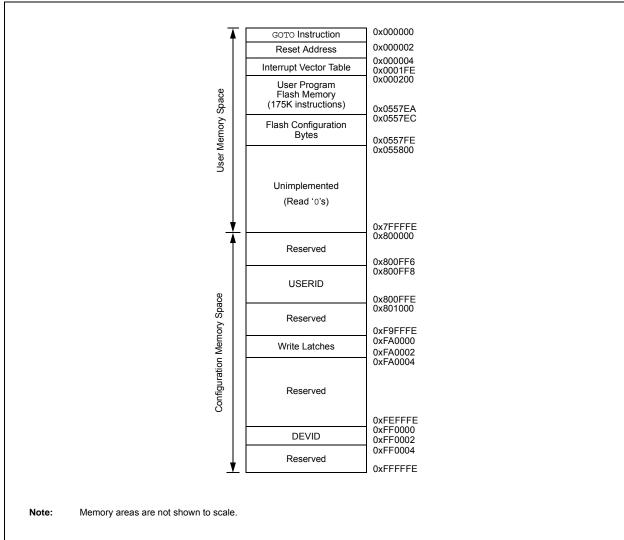

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

| TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY (CONTINUED) |      |                |        |        |        |        |        |          |                               |                               |       |       |       |       |       |       |       |               |

|------------------------------------------------------------------------------------------------------------|------|----------------|--------|--------|--------|--------|--------|----------|-------------------------------|-------------------------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| File Name                                                                                                  | Addr | Bit 15         | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8                         | Bit 7                         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID                                                                                                 | 046E |                |        |        | EID<   | :15:8> |        |          |                               |                               |       |       | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF12SID                                                                                                 | 0470 | 0470 SID<10:3> |        |        |        |        |        |          | SID<2:0> — EXIDE — EID<17:16> |                               |       |       |       | xxxx  |       |       |       |               |

| C1RXF12EID                                                                                                 | 0472 | 0472 EID<15:8> |        |        |        |        |        | EID<7:0> |                               |                               |       |       |       |       | xxxx  |       |       |               |

| C1RXF13SID                                                                                                 | 0474 | 4 SID<10:3>    |        |        |        |        |        |          | SID<2:0>                      |                               | _     | EXIDE | —     | EID<1 | 7:16> | xxxx  |       |               |

| C1RXF13EID                                                                                                 | 0476 |                |        |        | EID<   | :15:8> |        |          |                               | EID<7:0>                      |       |       |       |       |       | xxxx  |       |               |

| C1RXF14SID                                                                                                 | 0478 |                |        |        | SID<   | :10:3> |        |          |                               | SID<2:0> — EXIDE — EID<17:16> |       |       |       |       |       | 7:16> | xxxx  |               |

| C1RXF14EID                                                                                                 | 047A | 7A EID<15:8>   |        |        |        |        |        |          |                               |                               | EID<  | 7:0>  |       |       |       | xxxx  |       |               |

| C1RXF15SID                                                                                                 | 047C | 47C SID<10:3>  |        |        |        |        |        |          | SID<2:0>                      |                               | _     | EXIDE | _     | EID<1 | 7:16> | xxxx  |       |               |

| C1RXF15EID                                                                                                 | 047E |                |        |        | EID<   | :15:8> |        |          |                               |                               |       |       | EID<  | 7:0>  |       |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | —      | _      | _      | _      | —      | —     | —      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —      | _     | —     | AMOD  | E<1:0> | —       | —      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       | •     | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | —      | —      | _      | _      | —      | —     | —      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | —      | _      | _      |        | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1CNT   | 0B1E  | _      | —      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA2CON   | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _      | _      | _      | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | _      | —      | —      | —      | —      | —      |       | _      | —     | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |        |        |        |        |        |        |       | DSADR< | 15:0> |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | —      | —      | —      | —      | —      | —     | —      |       |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|--------|-------|-------|--------|---------------------|-----|-------|-------|

| VAR    | —     | US1   | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15 |       | •     |        |                     |     |       | bit 8 |

|        |       |       |        |                     |     |       |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7  |       | •     |        |                     |     |       | bit 0 |

|        |       |       |        |                     |     |       |       |

|        |       |       |        |                     |     |       |       |

# **REGISTER 7-2:** CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                      |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared | x = Bit is unknown |

bit

| VAR: Variable Exception Processing Latency Control                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>1 = Variable exception processing is enabled</li> </ol>                                                              |

| 0 = Fixed exception processing is enabled                                                                                     |

| IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                                |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

|                                                                                                                               |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# 13.2 Timer Control Registers

| R/W-0         | U-0                                                            | R/W-0                              | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |

|---------------|----------------------------------------------------------------|------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|

| TON           |                                                                | TSIDL                              | —              | _                |                 |                 | _     |  |  |

| bit 15        |                                                                |                                    |                |                  |                 |                 | bit 8 |  |  |

|               |                                                                |                                    |                |                  |                 |                 |       |  |  |

| U-0           | R/W-0                                                          | R/W-0                              | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |

| _             | TGATE                                                          | TCKPS1                             | TCKPS0         | T32              | _               | TCS             | _     |  |  |

| bit 7         |                                                                |                                    |                |                  |                 |                 | bit ( |  |  |

| <u> </u>      |                                                                |                                    |                |                  |                 |                 |       |  |  |

| Legend:       | - 1-:4                                                         |                                    |                | II II.           |                 |                 |       |  |  |

| R = Readable  |                                                                | W = Writable                       |                | -                | nented bit, rea |                 |       |  |  |

| -n = Value at | PUR                                                            | '1' = Bit is set                   |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |  |  |

| bit 15        | TON: Timerx                                                    | On hit                             |                |                  |                 |                 |       |  |  |

|               | When T32 = 2                                                   |                                    |                |                  |                 |                 |       |  |  |

|               | 1 = Starts 32-                                                 | bit Timerx/y                       |                |                  |                 |                 |       |  |  |

|               | 0 = Stops 32-                                                  |                                    |                |                  |                 |                 |       |  |  |

|               | <u>When T32 = 0</u><br>1 = Starts 16-                          |                                    |                |                  |                 |                 |       |  |  |

|               | 0 = Stops 16-                                                  |                                    |                |                  |                 |                 |       |  |  |

| bit 14        | Unimplemen                                                     | ted: Read as '                     | )'             |                  |                 |                 |       |  |  |

| bit 13        | TSIDL: Timerx Stop in Idle Mode bit                            |                                    |                |                  |                 |                 |       |  |  |

|               | 1 = Discontinues module operation when device enters Idle mode |                                    |                |                  |                 |                 |       |  |  |

|               |                                                                | s module opera                     |                | ode              |                 |                 |       |  |  |

| bit 12-7      | -                                                              | ted: Read as '                     |                |                  |                 |                 |       |  |  |

| bit 6         |                                                                | erx Gated Time                     | Accumulation   | Enable bit       |                 |                 |       |  |  |

|               | When TCS =<br>This bit is igno                                 |                                    |                |                  |                 |                 |       |  |  |

|               | When TCS =                                                     |                                    |                |                  |                 |                 |       |  |  |

|               | 1 = Gated tim                                                  | e accumulatior                     |                |                  |                 |                 |       |  |  |

|               |                                                                | e accumulation                     |                |                  |                 |                 |       |  |  |

| bit 5-4       |                                                                | : Timerx Input                     | Clock Prescal  | e Select bits    |                 |                 |       |  |  |

|               | 11 = 1:256<br>10 = 1:64                                        |                                    |                |                  |                 |                 |       |  |  |

|               | 01 = 1:8                                                       |                                    |                |                  |                 |                 |       |  |  |

|               | 00 = 1:1                                                       |                                    |                |                  |                 |                 |       |  |  |

| bit 3         | T32: 32-Bit Ti                                                 | mer Mode Sele                      | ect bit        |                  |                 |                 |       |  |  |

|               |                                                                | nd Timery form<br>nd Timery act as |                |                  |                 |                 |       |  |  |

| bit 2         | Unimplemen                                                     | ted: Read as '                     | )'             |                  |                 |                 |       |  |  |

| bit 1         | TCS: Timerx                                                    | Clock Source S                     | elect bit      |                  |                 |                 |       |  |  |

|               | 1 = External c<br>0 = Internal cl                              | clock is from pir<br>lock (FP)     | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |

| bit 0         | Unimplomon                                                     | ted: Read as '                     | ı'             |                  |                 |                 |       |  |  |

# REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| —               | —     |                  |       | DTR)             | <13:8>          |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | DTR   | x<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

# REGISTER 16-10: DTRx: PWMx DEAD-TIME REGISTER

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0                                                                      | R/W-0           | R/W-0    | R/W-0 |  |  |

|-----------------|-------|------------------|-------|----------------------------------------------------------------------------|-----------------|----------|-------|--|--|

| —               | _     |                  |       | ALTDTR                                                                     | x<13:8>         |          |       |  |  |

| bit 15          |       |                  |       |                                                                            |                 |          | bit 8 |  |  |

|                 |       |                  |       |                                                                            |                 |          |       |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                                                      | R/W-0           | R/W-0    | R/W-0 |  |  |

|                 |       |                  | ALTDT | Rx<7:0>                                                                    |                 |          |       |  |  |

| bit 7           |       |                  |       |                                                                            |                 |          | bit 0 |  |  |

| Legend:         |       |                  |       |                                                                            |                 |          |       |  |  |

| R = Readable    | bit   | W = Writable t   | oit   | U = Unimplem                                                               | ented bit, read | d as '0' |       |  |  |

| -n = Value at P | OR    | '1' = Bit is set |       | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                 |          |       |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

# REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|              | R/W-0         | U-0                 | U-0                         | U-0             | R/W-0                                | R/W-0                | R/W-0                |

|--------------|---------------|---------------------|-----------------------------|-----------------|--------------------------------------|----------------------|----------------------|

| CSS31        | CSS30         | —                   | —                           | _               | CSS26 <sup>(2)</sup>                 | CSS25 <sup>(2)</sup> | CSS24 <sup>(2)</sup> |

| bit 15       | - 1           |                     |                             |                 |                                      |                      | bit 8                |

|              |               |                     |                             |                 |                                      |                      |                      |

| U-0          | U-0           | U-0                 | U-0                         | U-0             | U-0                                  | U-0                  | U-0                  |

| _            |               | _                   | _                           | _               |                                      | _                    |                      |

| bit 7        |               |                     |                             |                 |                                      |                      | bit (                |

|              |               |                     |                             |                 |                                      |                      |                      |

| Legend:      |               |                     |                             |                 |                                      |                      |                      |

| R = Readab   | le bit        | W = Writable        | bit                         | U = Unimple     | emented bit, read                    | d as '0'             |                      |

| -n = Value a | t POR         | '1' = Bit is set    |                             | '0' = Bit is cl | eared                                | x = Bit is unk       | nown                 |

|              |               |                     |                             |                 |                                      |                      |                      |

| bit 15       |               | 1 Input Scan S      |                             |                 |                                      |                      |                      |

|              |               |                     |                             |                 | input scan (Ope                      |                      |                      |

|              | •             | •                   |                             | surement for ir | nput scan (Open                      | )                    |                      |

| bit 14       |               | 1 Input Scan S      |                             |                 |                                      |                      |                      |

|              |               |                     |                             |                 | or input scan (CT<br>input scan (CTN |                      |                      |

| bit 13-11    | Unimplemen    | ted: Read as '      | 0'                          |                 |                                      |                      |                      |

| bit 10       | CSS26: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              | 1 = Selects C | )<br>A3/AN6 for inp | ut scan                     |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 3/AN6 for input     | scan                        |                 |                                      |                      |                      |

| bit 9        | CSS25: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              | 1 = Selects C | 0A2/AN0 for inp     | ut scan                     |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 2/AN0 for input     | scan                        |                 |                                      |                      |                      |

| bit 8        | CSS24: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              |               | 0A1/AN3 for inp     |                             |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 1/AN3 for input     | scan                        |                 |                                      |                      |                      |

|              |               |                     |                             |                 |                                      |                      |                      |

# REGISTER 23-7: AD1CSSH: ADC1 INPUT SCAN SELECT REGISTER HIGH<sup>(1)</sup>

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

# 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| АС СН        | AC CHARACTERISTICS |                                                                |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                                                                                             |  |  |  |  |  |

|--------------|--------------------|----------------------------------------------------------------|------|------------------------------------------------------|------|-------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Param<br>No. | Symbol             | Characteristic <sup>(1)</sup>                                  | Min. | Тур. <sup>(2)</sup>                                  | Max. | Units | Conditions                                                                                                  |  |  |  |  |  |

| SY00         | Τρυ                | Power-up Period                                                | _    | 400                                                  | 600  | μS    |                                                                                                             |  |  |  |  |  |

| SY10         | Tost               | Oscillator Start-up Time                                       |      | 1024 Tosc                                            |      |       | Tosc = OSC1 period                                                                                          |  |  |  |  |  |

| SY12         | Twdt               | Watchdog Timer<br>Time-out Period                              | 0.81 | 0.98                                                 | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |  |  |  |  |  |

|              |                    |                                                                | 3.26 | 3.91                                                 | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |  |  |  |  |  |

| SY13         | Tioz               | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer Reset | 0.68 | 0.72                                                 | 1.2  | μS    |                                                                                                             |  |  |  |  |  |

| SY20         | TMCLR              | MCLR Pulse Width (low)                                         | 2    | _                                                    |      | μS    |                                                                                                             |  |  |  |  |  |

| SY30         | TBOR               | BOR Pulse Width (low)                                          | 1    | _                                                    |      | μS    |                                                                                                             |  |  |  |  |  |

| SY35         | TFSCM              | Fail-Safe Clock Monitor<br>Delay                               | _    | 500                                                  | 900  | μS    | -40°C to +85°C                                                                                              |  |  |  |  |  |

| SY36         | TVREG              | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time | _    | —                                                    | 30   | μS    |                                                                                                             |  |  |  |  |  |

| SY37         | Toscdfrc           | FRC Oscillator Start-up<br>Delay                               | 46   | 48                                                   | 54   | μS    |                                                                                                             |  |  |  |  |  |

| SY38         | Toscdlprc          | LPRC Oscillator Start-up<br>Delay                              |      | —                                                    | 70   | μS    |                                                                                                             |  |  |  |  |  |

# TABLE 30-22:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

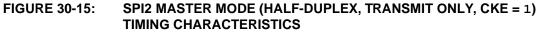

#### TABLE 30-34: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |  |

|--------------------|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |  |

| SP10               | FscP                  | Maximum SCK2 Frequency                       | _                                                                                                                                                                                                                                                                                     | _                   | 15   | MHz   | (Note 3)                       |  |

| SP20               | TscF                  | SCK2 Output Fall Time                        | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP21               | TscR                  | SCK2 Output Rise Time                        | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO31<br>(Note 4) |  |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                   | -                                                                                                                                                                                                                                                                                     | _                   |      | ns    | See Parameter DO31<br>(Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge    | —                                                                                                                                                                                                                                                                                     | 6                   | 20   | ns    |                                |  |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge | 30                                                                                                                                                                                                                                                                                    | —                   | _    | ns    |                                |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

# TABLE 30-37:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHA | ARACTERIS             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |              |                     |                          |       |                                |  |

|--------|-----------------------|-------------------------------------------------------|--------------|---------------------|--------------------------|-------|--------------------------------|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                         | Min.         | Тур. <sup>(2)</sup> | Max.                     | Units | Conditions                     |  |

| SP70   | FscP                  | Maximum SCK2 Input<br>Frequency                       | -            | -                   | Lesser<br>of FP<br>or 15 | MHz   | (Note 3)                       |  |

| SP72   | TscF                  | SCK2 Input Fall Time                                  | _            |                     |                          | ns    | See Parameter DO32<br>(Note 4) |  |

| SP73   | TscR                  | SCK2 Input Rise Time                                  | —            |                     |                          | ns    | See Parameter DO31<br>(Note 4) |  |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                            | —            |                     |                          | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                            | —            | _                   | _                        | ns    | See Parameter DO31 (Note 4)    |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge             | —            | 6                   | 20                       | ns    |                                |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge          | 30           | _                   | _                        | ns    |                                |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge            | 30           |                     |                          | ns    |                                |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge             | 30           |                     |                          | ns    |                                |  |

| SP50   | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input       | 120          | _                   | _                        | ns    |                                |  |

| SP51   | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance                | 10           | _                   | 50                       | ns    | (Note 4)                       |  |

| SP52   | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                                 | 1.5 TCY + 40 | _                   | _                        | ns    | (Note 4)                       |  |

| SP60   | TssL2doV              | SDO2 Data Output Valid after<br>SS2 Edge              | —            |                     | 50                       | ns    |                                |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

| AC CHARACTERISTICS |        |                                                  |          | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |         |       |                                                           |  |  |

|--------------------|--------|--------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-----------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                                   | Min.     | Тур.                                                                                                                                                                                                                                                                                          | Max.    | Units | Conditions                                                |  |  |

|                    |        | ADC A                                            | Accuracy | (12-Bit                                                                                                                                                                                                                                                                                       | Mode)   |       |                                                           |  |  |

| AD20a              | Nr     | Resolution                                       | 12       | 2 Data Bi                                                                                                                                                                                                                                                                                     | ts      | bits  |                                                           |  |  |

| AD21a              | INL    | Integral Nonlinearity                            | -2.5     |                                                                                                                                                                                                                                                                                               | 2.5     | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                               |  |  |

|                    |        |                                                  | -5.5     | _                                                                                                                                                                                                                                                                                             | 5.5     | LSb   | +85°C < TA ≤ +125°C (Note 2)                              |  |  |

| AD22a              | DNL    | Differential Nonlinearity                        | -1       | —                                                                                                                                                                                                                                                                                             | 1       | LSb   | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                     |  |  |

|                    |        |                                                  | -1       | —                                                                                                                                                                                                                                                                                             | 1       | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                         |  |  |

| AD23a              | Gerr   | Gain Error <sup>(3)</sup>                        | -10      | —                                                                                                                                                                                                                                                                                             | 10      | LSb   | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                     |  |  |

|                    |        |                                                  | -10      | _                                                                                                                                                                                                                                                                                             | 10      | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                         |  |  |

| AD24a              | EOFF   | Offset Error                                     | -5       | _                                                                                                                                                                                                                                                                                             | 5       | LSb   | $-40^{\circ}C \leq TA \leq +85^{\circ}C \text{ (Note 2)}$ |  |  |

|                    |        |                                                  | -5       | _                                                                                                                                                                                                                                                                                             | 5       | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                         |  |  |

| AD25a              | —      | Monotonicity                                     | —        | —                                                                                                                                                                                                                                                                                             | —       |       | Guaranteed                                                |  |  |

|                    |        | Dynamic                                          | Performa | ance (12-                                                                                                                                                                                                                                                                                     | Bit Mod | e)    |                                                           |  |  |

| AD30a              | THD    | Total Harmonic Distortion <sup>(3)</sup>         | _        | 75                                                                                                                                                                                                                                                                                            | _       | dB    |                                                           |  |  |

| AD31a              | SINAD  | Signal to Noise and<br>Distortion <sup>(3)</sup> | —        | 68                                                                                                                                                                                                                                                                                            | _       | dB    |                                                           |  |  |

| AD32a              | SFDR   | Spurious Free Dynamic<br>Range <sup>(3)</sup>    | —        | 80                                                                                                                                                                                                                                                                                            | —       | dB    |                                                           |  |  |

| AD33a              | Fnyq   | Input Signal Bandwidth <sup>(3)</sup>            | —        | 250                                                                                                                                                                                                                                                                                           | —       | kHz   |                                                           |  |  |

| AD34a              | ENOB   | Effective Number of Bits <sup>(3)</sup>          | 11.09    | 11.3                                                                                                                                                                                                                                                                                          | _       | bits  |                                                           |  |  |

# TABLE 30-58: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

3: Parameters are characterized but not tested in manufacturing.

| AC CHARACTERISTICS |        |                                                                                                     |                                                                                                                                                                                              | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> |       |       |                                         |  |  |  |

|--------------------|--------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-----------------------------------------|--|--|--|

|                    |        |                                                                                                     | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                                                                      |       |       |                                         |  |  |  |

| Param<br>No.       | Symbol | Characteristic                                                                                      | Min.                                                                                                                                                                                         | Тур.                                                                                 | Max.  | Units | Conditions                              |  |  |  |

|                    |        | Cloci                                                                                               | k Parame                                                                                                                                                                                     | eters                                                                                |       |       |                                         |  |  |  |

| AD50               | TAD    | ADC Clock Period                                                                                    | 76                                                                                                                                                                                           | _                                                                                    | _     | ns    |                                         |  |  |  |

| AD51               | tRC    | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                    |                                                                                                                                                                                              | 250                                                                                  | _     | ns    |                                         |  |  |  |

|                    | •      | Conv                                                                                                | version F                                                                                                                                                                                    | Rate                                                                                 |       | •     |                                         |  |  |  |

| AD55               | tCONV  | Conversion Time                                                                                     |                                                                                                                                                                                              | 12 Tad                                                                               | _     |       |                                         |  |  |  |

| AD56               | FCNV   | Throughput Rate                                                                                     | _                                                                                                                                                                                            | —                                                                                    | 1.1   | Msps  | Using simultaneous sampling             |  |  |  |

| AD57a              | TSAMP  | Sample Time when Sampling any ANx Input                                                             | 2 Tad                                                                                                                                                                                        | —                                                                                    | _     | —     |                                         |  |  |  |

| AD57b              | TSAMP  | Sample Time when Sampling the Op Amp Outputs (Configuration A and Configuration B) <sup>(4,5)</sup> | 4 Tad                                                                                                                                                                                        | _                                                                                    | —     | —     |                                         |  |  |  |

|                    |        | Timin                                                                                               | g Param                                                                                                                                                                                      | eters                                                                                |       |       |                                         |  |  |  |

| AD60               | tPCS   | Conversion Start from Sample<br>Trigger <sup>(2,3)</sup>                                            | 2 Tad                                                                                                                                                                                        | —                                                                                    | 3 Tad | —     | Auto-convert trigger is<br>not selected |  |  |  |

| AD61               | tPSS   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2,3))</sup>                                    | 2 Tad                                                                                                                                                                                        | —                                                                                    | 3 Tad | —     |                                         |  |  |  |

| AD62               | tcss   | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2,3)</sup>                                | _                                                                                                                                                                                            | 0.5 Tad                                                                              |       | —     |                                         |  |  |  |

| AD63               | tdpu   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup>                           |                                                                                                                                                                                              | —                                                                                    | 20    | μs    | (Note 6)                                |  |  |  |

### TABLE 30-61: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

### TABLE 30-62: DMA MODULE TIMING REQUIREMENTS

|              |                                | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |      |       |            |  |

|--------------|--------------------------------|-------------------------------------------------------|---|------|-------|------------|--|

| Param<br>No. | Characteristic                 | Min. Typ. <sup>(1)</sup>                              |   | Max. | Units | Conditions |  |

| DM1          | DMA Byte/Word Transfer Latency | 1 Tcy <b>(2)</b>                                      | _ | _    | ns    |            |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because DMA transfers use the CPU data bus, this time is dependent on other functions on the bus.

<sup>© 2011-2013</sup> Microchip Technology Inc.

| AC CHARACTERISTICS                        |        |                           |              | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |          |                   |                                                  |  |  |  |

|-------------------------------------------|--------|---------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|--------------------------------------------------|--|--|--|

| Param<br>No.                              | Symbol | Characteristic            | Min          | Тур                                                                                                                                    | Max      | Units             | Conditions                                       |  |  |  |

| ADC Accuracy (12-Bit Mode) <sup>(1)</sup> |        |                           |              |                                                                                                                                        |          |                   |                                                  |  |  |  |

| HAD20a                                    | Nr     | Resolution <sup>(3)</sup> | 12 Data Bits |                                                                                                                                        |          | bits              |                                                  |  |  |  |

| HAD21a                                    | INL    | Integral Nonlinearity     | -5.5         | _                                                                                                                                      | 5.5      | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD22a                                    | DNL    | Differential Nonlinearity | -1           | _                                                                                                                                      | 1        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD23a                                    | Gerr   | Gain Error                | -10          |                                                                                                                                        | 10       | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD24a                                    | EOFF   | Offset Error              | -5           | —                                                                                                                                      | 5        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

|                                           |        | Dynamic I                 | Performa     | nce (12-                                                                                                                               | Bit Mode | e) <sup>(2)</sup> |                                                  |  |  |  |

| HAD33a                                    | Fnyq   | Input Signal Bandwidth    | _            | _                                                                                                                                      | 200      | kHz               |                                                  |  |  |  |

# TABLE 31-12: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

# TABLE 31-13: ADC MODULE SPECIFICATIONS (10-BIT MODE)

| AC CHARACTERISTICS |        |                           |                   | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |                      |                   |                                                  |  |  |

|--------------------|--------|---------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|--------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic            | Min Typ Max Units |                                                                                                                                     |                      | Units             | Conditions                                       |  |  |

|                    |        | ADC A                     | ccuracy           | (10-Bit I                                                                                                                           | Mode) <sup>(1)</sup> |                   |                                                  |  |  |

| HAD20b             | Nr     | Resolution <sup>(3)</sup> | 10 Data Bits      |                                                                                                                                     |                      | bits              |                                                  |  |  |

| HAD21b             | INL    | Integral Nonlinearity     | -1.5              | _                                                                                                                                   | 1.5                  | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |  |  |

| HAD22b             | DNL    | Differential Nonlinearity | -0.25             | _                                                                                                                                   | 0.25                 | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |  |  |

| HAD23b             | Gerr   | Gain Error                | -2.5              |                                                                                                                                     | 2.5                  | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

| HAD24b             | EOFF   | Offset Error              | -1.25             | _                                                                                                                                   | 1.25                 | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

|                    |        | Dynamic P                 | erforma           | nce (10-                                                                                                                            | Bit Mode             | e) <sup>(2)</sup> |                                                  |  |  |