Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 44-VTLA (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc504t-e-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

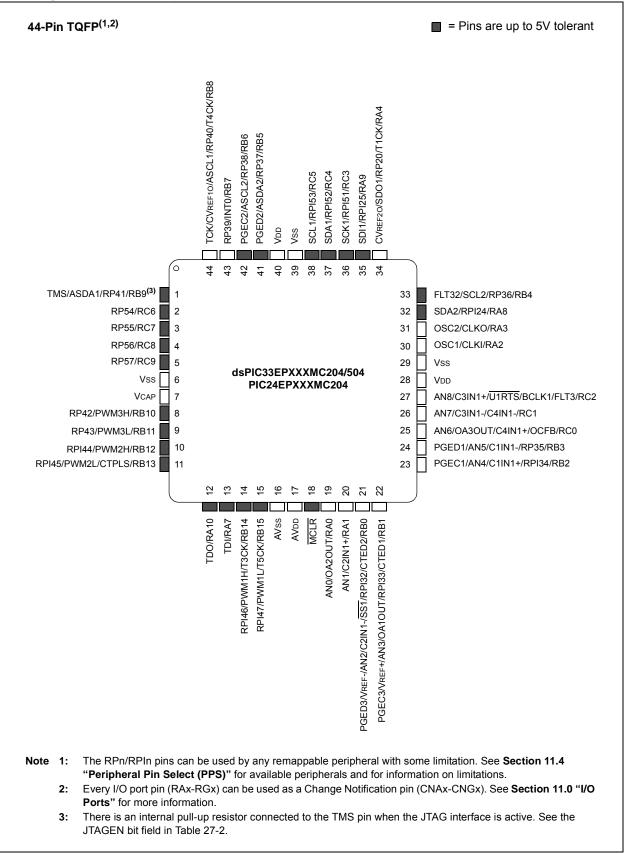

## Pin Diagrams (Continued)

## 3.8 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

## 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.9 DSP Engine (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- · Signed, unsigned or mixed-sign DSP multiply (US)

- · Conventional or convergent rounding (RND)

- · Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

|             | SUMMARY                 |                   |

|-------------|-------------------------|-------------------|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

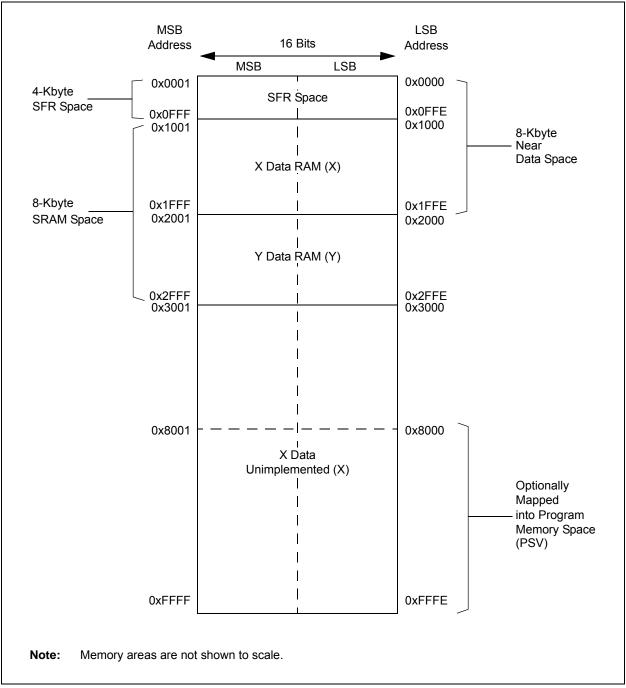

# FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

|                                                     | Vector  | IRQ        | IVT Address       | Inte            | errupt Bit L | ocation      |

|-----------------------------------------------------|---------|------------|-------------------|-----------------|--------------|--------------|

| Interrupt Source                                    |         |            | Flag              | Enable          | Priority     |              |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10>        | IEC3<10>     | IPC14<10:8>  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _               | _            | _            |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>         | IEC4<1>      | IPC16<6:4>   |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>         | IEC4<2>      | IPC16<10:8>  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>         | IEC4<3>      | IPC16<14:12> |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —               | _            | —            |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>         | IEC4<6>      | IPC17<10:8>  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —               | _            | —            |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13>        | IEC4<13>     | IPC19<6:4>   |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —               | _            | —            |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14>        | IEC5<14>     | IPC23<10:8>  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | 0000D2 IFS5<15> |              | IPC23<14:12> |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>         | IEC6<0>      | IPC24<2:0>   |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —               | _            | —            |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14>        | IEC8<14>     | IPC35<10:8>  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15>        | IEC8<15>     | IPC35<14:12> |

| Reserved                                            | 152     | 144        | 0x000134          | —               | _            | _            |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>         | IEC9<1>      | IPC36<6:4>   |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>         | IEC9<2>      | IPC36<10:8>  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>         | IEC9<3>      | IPC36<14:12> |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>         | IEC9<4>      | IPC37<2:0>   |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>         | IEC9<5>      | IPC37<6:4>   |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>         | IEC9<6>      | IPC37<10:8>  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —               | —            | _            |

|                                                     | Lowe    | est Natura | I Order Priority  |                 |              |              |

## TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| U-0             | U-0                                                                                          | U-0                                                                                                                                                                     | U-0                                                                             | R-0               | R-0              | R-0             | R-0     |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------|------------------|-----------------|---------|--|--|--|

|                 | —                                                                                            |                                                                                                                                                                         |                                                                                 | ILR3              | ILR2             | ILR1            | ILR0    |  |  |  |

| bit 15          |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 | bit 8   |  |  |  |

| R-0             | R-0                                                                                          | R-0                                                                                                                                                                     | R-0                                                                             | R-0               | R-0              | R-0             | R-0     |  |  |  |

| VECNUM7         | VECNUM6                                                                                      | VECNUM5                                                                                                                                                                 | VECNUM4                                                                         | VECNUM3           | VECNUM2          | VECNUM1         | VECNUM0 |  |  |  |

| bit 7           |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 | bit C   |  |  |  |

| Legend:         |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |

| R = Readable    | bit                                                                                          | W = Writable                                                                                                                                                            | bit                                                                             | U = Unimplen      | nented bit, read | as '0'          |         |  |  |  |

| -n = Value at I | POR                                                                                          | '1' = Bit is set                                                                                                                                                        |                                                                                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |

| bit 15-12       | Unimplemen                                                                                   | ted: Read as '                                                                                                                                                          | 0'                                                                              |                   |                  |                 |         |  |  |  |

| bit 11-8        | -                                                                                            | w CPU Interru                                                                                                                                                           |                                                                                 | el bits           |                  |                 |         |  |  |  |

|                 |                                                                                              | Interrupt Priorit                                                                                                                                                       | -                                                                               |                   |                  |                 |         |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |

|                 |                                                                                              | Interrupt Priorif<br>Interrupt Priorif                                                                                                                                  |                                                                                 |                   |                  |                 |         |  |  |  |

| bit 7-0         | VECNUM<7:0>: Vector Number of Pending Interrupt bits                                         |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |

|                 | 11111111 = 255, Reserved; do not use                                                         |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |

|                 | 00001000 = 8<br>00000111 = 7<br>00000110 = 8<br>00000101 = 8<br>00000100 = 7<br>00000011 = 3 | 9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d<br>6, Generic soft<br>5, DMAC error<br>4, Math error tr<br>3, Stack error t<br>2, Generic hard<br>1, Address erro | rnal Interrupt C<br>o not use<br>error trap<br>trap<br>rap<br>d trap<br>or trap | )                 |                  |                 |         |  |  |  |

## REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

## **10.0 POWER-SAVING FEATURES**

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | Sleep mode |  |

|--------|-------------|---|-----|-----|--------|------|------------|--|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | Idle mode  |  |

## 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

## 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0        | R/W-0                               | R/W-0 | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

|-----------------|------------|-------------------------------------|-------|--------------------------|------------------|-----------------|-------|

| —               | —          |                                     |       | RP57                     | R<5:0>           |                 |       |

| bit 15          |            |                                     |       |                          |                  |                 | bit 8 |

|                 |            |                                     |       |                          |                  |                 |       |

| U-0             | U-0        | R/W-0                               | R/W-0 | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

| _               | —          |                                     |       | RP56                     | R<5:0>           |                 |       |

| bit 7           |            |                                     |       |                          |                  |                 | bit 0 |

|                 |            |                                     |       |                          |                  |                 |       |

| Legend:         |            |                                     |       |                          |                  |                 |       |

| R = Readable I  | bit        | W = Writable                        | bit   | U = Unimplen             | nented bit, read | d as '0'        |       |

| -n = Value at P | OR         | '1' = Bit is set                    | :     | '0' = Bit is clea        | ared             | x = Bit is unkr | iown  |

|                 |            |                                     |       |                          |                  |                 |       |

| bit 15-14       | Unimplemen | ted: Read as '                      | 0'    |                          |                  |                 |       |

| bit 13-8        |            | : Peripheral Ou<br>-3 for periphera |       | is Assigned to<br>mbers) | RP57 Output F    | Pin bits        |       |

| bit 7-6         | Unimplemen | ted: Read as '                      | 0'    |                          |                  |                 |       |

#### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

## 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

| R/W-0         | R/W-0                                                                                                                    | R/W-0                                      | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| QCAPEN        | FLTREN                                                                                                                   | QFDIV2                                     | QFDIV1            | QFDIV0            | OUTFNC1          | OUTFNC0         | SWPAB |  |  |  |  |

| bit 15        | ·                                                                                                                        | ·                                          |                   |                   |                  |                 | bit 8 |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                    | R/W-0                                      | R/W-0             | R-x               | R-x              | R-x             | R-x   |  |  |  |  |

| HOMPOL        | IDXPOL                                                                                                                   | QEBPOL                                     | QEAPOL            | HOME              | INDEX            | QEB             | QEA   |  |  |  |  |

| bit 7         |                                                                                                                          |                                            |                   | TIOME             | INDEX            | QLD             | bit ( |  |  |  |  |

| Legend:       |                                                                                                                          |                                            |                   |                   |                  |                 |       |  |  |  |  |

| R = Readable  | e bit                                                                                                                    | W = Writable                               | bit               | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value at |                                                                                                                          | '1' = Bit is set                           |                   | '0' = Bit is cle  |                  | x = Bit is unkn | own   |  |  |  |  |

|               |                                                                                                                          |                                            |                   |                   |                  |                 |       |  |  |  |  |

| bit 15        | QCAPEN: Q                                                                                                                | EI Position Cou                            | nter Input Cap    | ture Enable bit   |                  |                 |       |  |  |  |  |

|               |                                                                                                                          | tch event trigge                           |                   |                   |                  |                 |       |  |  |  |  |

|               |                                                                                                                          | tch event does                             |                   | -                 |                  |                 |       |  |  |  |  |

| bit 14        |                                                                                                                          | Ax/QEBx/INDX                               | •                 | tal Filter Enable | e dit            |                 |       |  |  |  |  |

|               |                                                                                                                          | digital filter is e<br>digital filter is d |                   | sed)              |                  |                 |       |  |  |  |  |

| bit 13-11     | • •                                                                                                                      | •                                          |                   |                   | Iter Clock Divid | le Select bits  |       |  |  |  |  |

|               | <b>QFDIV&lt;2:0&gt;:</b> QEAx/QEBx/INDXx/HOMEx Digital Input Filter Clock Divide Select bits<br>111 = 1:128 clock divide |                                            |                   |                   |                  |                 |       |  |  |  |  |

|               | 110 = 1:64 clock divide                                                                                                  |                                            |                   |                   |                  |                 |       |  |  |  |  |

|               | 101 = 1:32 clock divide                                                                                                  |                                            |                   |                   |                  |                 |       |  |  |  |  |

|               | 100 = 1:16  clock divide                                                                                                 |                                            |                   |                   |                  |                 |       |  |  |  |  |

|               | 011 = 1:8 clock divide<br>010 = 1:4 clock divide                                                                         |                                            |                   |                   |                  |                 |       |  |  |  |  |

|               | 010 = 1.4 clock divide<br>001 = 1.2 clock divide                                                                         |                                            |                   |                   |                  |                 |       |  |  |  |  |

|               | 000 = 1:1 clo                                                                                                            |                                            |                   |                   |                  |                 |       |  |  |  |  |

| bit 10-9      | OUTFNC<1:                                                                                                                | 0>: QEI Module                             | Output Functi     | on Mode Selec     | ct bits          |                 |       |  |  |  |  |

|               |                                                                                                                          | NCMPx pin goe                              | -                 |                   |                  | GEC             |       |  |  |  |  |

|               |                                                                                                                          | NCMPx pin goe                              |                   |                   |                  |                 |       |  |  |  |  |

|               |                                                                                                                          | NCMPx pin goe                              | s high when P     | $OS1CNT \ge QE$   | IIGEC            |                 |       |  |  |  |  |

| L:1 0         | 00 = Output i                                                                                                            |                                            |                   |                   |                  |                 |       |  |  |  |  |

| bit 8         | <b>SWPAB:</b> Swap QEA and QEB Inputs bit<br>1 = QEAx and QEBx are swapped prior to quadrature decoder logic             |                                            |                   |                   |                  |                 |       |  |  |  |  |

|               |                                                                                                                          | d QEBx are swi<br>d QEBx are not           |                   | quadrature dec    | coder logic      |                 |       |  |  |  |  |

| bit 7         | HOMPOL: H                                                                                                                | OMEx Input Po                              | larity Select bit |                   |                  |                 |       |  |  |  |  |

|               | 1 = Input is in                                                                                                          |                                            |                   |                   |                  |                 |       |  |  |  |  |

| bit 6         | 0 = Input is n                                                                                                           |                                            | ty Soloot bit     |                   |                  |                 |       |  |  |  |  |

|               | 1 = Input is in                                                                                                          | OXx Input Polari                           | ly Select bit     |                   |                  |                 |       |  |  |  |  |

|               | 0 = Input is n                                                                                                           |                                            |                   |                   |                  |                 |       |  |  |  |  |

| bit 5         | -                                                                                                                        | EBx Input Polar                            | itv Select bit    |                   |                  |                 |       |  |  |  |  |

|               | 1 = Input is i                                                                                                           | •                                          | .,                |                   |                  |                 |       |  |  |  |  |

|               | 0 = Input is r                                                                                                           |                                            |                   |                   |                  |                 |       |  |  |  |  |

| bit 4         | QEAPOL: Q                                                                                                                | EAx Input Polar                            | ity Select bit    |                   |                  |                 |       |  |  |  |  |

|               | 1 = Input is i                                                                                                           |                                            |                   |                   |                  |                 |       |  |  |  |  |

|               | 0 = Input is r                                                                                                           | not inverted                               |                   |                   |                  |                 |       |  |  |  |  |

| bit 3         | HOME: Statu                                                                                                              |                                            |                   |                   |                  |                 |       |  |  |  |  |

| DIL 3         | <b>HOME</b> . Statu                                                                                                      |                                            | out Pin Alter Po  | olarity Control   |                  |                 |       |  |  |  |  |

| DIL 3         | 1 = Pin is at<br>0 = Pin is at                                                                                           | logic '1'                                  | out Pin Aiter Po  | bianty Control    |                  |                 |       |  |  |  |  |

## REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INDXH | LD<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INDXF | ILD<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

## REGISTER 17-10: INDX1HLD: INDEX COUNTER 1 HOLD REGISTER

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDX1CNTH bits

### REGISTER 17-11: QEI1ICH: QEI1 INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0                             | R/W-0            | R/W-0                            | R/W-0                                  | R/W-0                                                                                 | R/W-0                                                                                                                                                      | R/W-0                                                                                         |  |

|-----------------------------------|------------------|----------------------------------|----------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

|                                   |                  | QEIIC                            | <31:24>                                |                                                                                       |                                                                                                                                                            |                                                                                               |  |

|                                   |                  |                                  |                                        |                                                                                       |                                                                                                                                                            | bit 8                                                                                         |  |

|                                   |                  |                                  |                                        |                                                                                       |                                                                                                                                                            |                                                                                               |  |

| R/W-0                             | R/W-0            | R/W-0                            | R/W-0                                  | R/W-0                                                                                 | R/W-0                                                                                                                                                      | R/W-0                                                                                         |  |

|                                   |                  | QEIIC                            | <23:16>                                |                                                                                       |                                                                                                                                                            |                                                                                               |  |

|                                   |                  |                                  |                                        |                                                                                       |                                                                                                                                                            | bit 0                                                                                         |  |

|                                   |                  |                                  |                                        |                                                                                       |                                                                                                                                                            |                                                                                               |  |

|                                   |                  |                                  |                                        |                                                                                       |                                                                                                                                                            |                                                                                               |  |

| R = Readable bit W = Writable bit |                  | bit                              | U = Unimplemented bit, read as '0'     |                                                                                       |                                                                                                                                                            |                                                                                               |  |

| DR                                | '1' = Bit is set |                                  | '0' = Bit is cleared x = Bit is unknow |                                                                                       |                                                                                                                                                            | nown                                                                                          |  |

|                                   | R/W-0            | R/W-0 R/W-0<br>it W = Writable I | QEIIC<br>R/W-0 R/W-0 QEIIC<br>QEIIC    | QEIIC<31:24><br>R/W-0 R/W-0 R/W-0<br>QEIIC<23:16><br>it W = Writable bit U = Unimplem | QEIIC<31:24>           R/W-0         R/W-0         R/W-0           QEIIC<23:16>            it         W = Writable bit         U = Unimplemented bit, real | QEIIC<31:24>           R/W-0         R/W-0         R/W-0         R/W-0           QEIIC<23:16> |  |

bit 15-0 **QEIIC<31:16>:** High Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

#### REGISTER 17-12: QEI1ICL: QEI1 INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0   | R/W-0           | R/W-0 | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|---------|-----------------|-------|-------|

|                                   |       |                  | QEII                               | C<15:8> |                 |       |       |

| bit 15                            |       |                  |                                    |         |                 |       | bit 8 |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0   | R/W-0           | R/W-0 | R/W-0 |

|                                   |       |                  | QEI                                | C<7:0>  |                 |       |       |

| bit 7                             |       |                  |                                    |         |                 |       | bit C |

| Legend:                           |       |                  |                                    |         |                 |       |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |         |                 |       |       |

| -n = Value at P                   | OR    | '1' = Bit is set | et '0' = Bit is cleared            |         | x = Bit is unkr | nown  |       |

bit 15-0 **QEIIC<15:0>:** Low Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

| U-0                     | U-0                        | U-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |  |

|-------------------------|----------------------------|------------------------------------|---------|------------------|-----------------|------------------|---------|--|--|

| _                       | _                          |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1          | FILHIT0 |  |  |

| bit 15                  | <b>I</b>                   |                                    |         |                  |                 |                  | bit 8   |  |  |

|                         |                            |                                    |         |                  |                 |                  |         |  |  |

| U-0                     | R-1                        | R-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |  |

| _                       | ICODE6                     | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1           | ICODE0  |  |  |

| bit 7                   |                            |                                    |         |                  |                 |                  | bit     |  |  |

| Logondi                 |                            |                                    |         |                  |                 |                  |         |  |  |

| Legend:<br>R = Readable | - hit                      | W = Writable                       | hit     | LI – Unimplor    | mented bit, rea | d as '0'         |         |  |  |

| -n = Value at           |                            | '1' = Bit is set                   |         | '0' = Bit is cle |                 | x = Bit is unkr  |         |  |  |

|                         | FUR                        |                                    |         |                  | aleu            | x – Dit is uliki |         |  |  |

| bit 15-13               | Unimplemen                 | ted: Read as '                     | 0'      |                  |                 |                  |         |  |  |

| bit 12-8                | =                          | Filter Hit Num                     |         |                  |                 |                  |         |  |  |

|                         |                            | 1 = Reserved                       |         |                  |                 |                  |         |  |  |

|                         | 01111 <b>= Filte</b>       | er 15                              |         |                  |                 |                  |         |  |  |

|                         | •                          |                                    |         |                  |                 |                  |         |  |  |

|                         | •                          |                                    |         |                  |                 |                  |         |  |  |

|                         | •<br>00001 = Filter 1      |                                    |         |                  |                 |                  |         |  |  |

|                         | 00001 = Filte              |                                    |         |                  |                 |                  |         |  |  |

| bit 7                   |                            | ted: Read as '                     | 0'      |                  |                 |                  |         |  |  |

| bit 6-0                 | -                          | : Interrupt Flag                   |         |                  |                 |                  |         |  |  |

|                         |                            | 11111 = Rese                       |         |                  |                 |                  |         |  |  |

|                         |                            | IFO almost full                    |         |                  |                 |                  |         |  |  |

|                         |                            | leceiver overflo                   |         |                  |                 |                  |         |  |  |

|                         | 1000010 = K<br>1000001 = E | Vake-up interru<br>rror interrupt  | μ       |                  |                 |                  |         |  |  |

|                         | 1000000 = N                |                                    |         |                  |                 |                  |         |  |  |

|                         | •                          |                                    |         |                  |                 |                  |         |  |  |

|                         | •                          |                                    |         |                  |                 |                  |         |  |  |

|                         | •                          |                                    |         |                  |                 |                  |         |  |  |

|                         |                            | 11111 = Rese                       |         |                  |                 |                  |         |  |  |

|                         | •                          | B15 buffer inte                    | inupt   |                  |                 |                  |         |  |  |

|                         | •                          |                                    |         |                  |                 |                  |         |  |  |

|                         | •                          |                                    |         |                  |                 |                  |         |  |  |

|                         | 0001001 <b>= R</b>         | B9 buffer inter                    | rupt    |                  |                 |                  |         |  |  |

|                         |                            | B8 buffer inter                    |         |                  |                 |                  |         |  |  |

|                         |                            | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                  |         |  |  |

|                         |                            | RB5 buffer inte                    |         |                  |                 |                  |         |  |  |

|                         |                            | RB4 buffer inte                    |         |                  |                 |                  |         |  |  |

|                         | 0000011 <b>= T</b>         | RB3 buffer inte                    | errupt  |                  |                 |                  |         |  |  |

|                         |                            |                                    |         |                  |                 |                  |         |  |  |

|                         |                            | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                  |         |  |  |

## REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

## 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

## REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit ( |

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

## REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|---------------|-------|-------|-------|-------|-------|-------|--|

|        | PTGHOLD<15:8> |       |       |       |       |       |       |  |

| bit 15 |               |       |       |       |       |       | bit 8 |  |

| R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|--------------|-------|-------|-------|-------|-------|-------|--|

|       | PTGHOLD<7:0> |       |       |       |       |       |       |  |

| bit 7 |              |       |       |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# TABLE 30-38:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHA | RACTERIS              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |              |                     |                          |       |                             |

|--------|-----------------------|-------------------------------------------------------|--------------|---------------------|--------------------------|-------|-----------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                         | Min.         | Typ. <sup>(2)</sup> | Max.                     | Units | Conditions                  |

| SP70   | FscP                  | Maximum SCK2 Input<br>Frequency                       | -            | _                   | Lesser<br>of FP<br>or 11 | MHz   | (Note 3)                    |

| SP72   | TscF                  | SCK2 Input Fall Time                                  | —            | —                   | _                        | ns    | See Parameter DO32 (Note 4) |

| SP73   | TscR                  | SCK2 Input Rise Time                                  | _            | -                   | -                        | ns    | See Parameter DO31 (Note 4) |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                            | —            | -                   | -                        | ns    | See Parameter DO32 (Note 4) |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                            | —            | —                   | _                        | ns    | See Parameter DO31 (Note 4) |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge             | —            | 6                   | 20                       | ns    |                             |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge          | 30           | —                   | _                        | ns    |                             |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge            | 30           | —                   |                          | ns    |                             |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge             | 30           | —                   | _                        | ns    |                             |

| SP50   | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input       | 120          | —                   | -                        | ns    |                             |

| SP51   | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance                | 10           | _                   | 50                       | ns    | (Note 4)                    |

| SP52   | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                                 | 1.5 TCY + 40 | —                   | _                        | ns    | (Note 4)                    |

| SP60   | TssL2doV              | SDO2 Data Output Valid after<br>SS2 Edge              | —            | —                   | 50                       | ns    |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

#### FIGURE 30-29: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

## 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

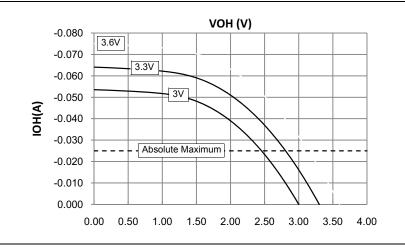

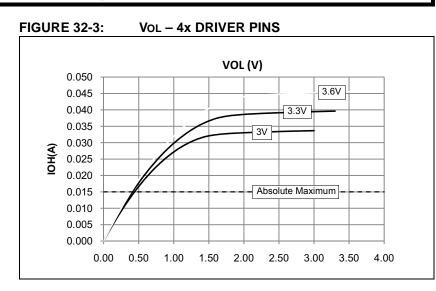

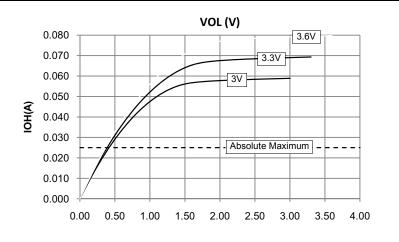

**FIGURE 32-1: VOH – 4x DRIVER PINS** VOH (V) -0.050 -0.045 3.6V -0.040 3.3V -0.035 3V -0.030 IOH(A) -0.025 -0.020 Absolute Maximum -0.015 -0.010 -0.005 0.000 0.50 1.00 2.00 2.50 3.00 3.50 0.00 1.50 4.00

## FIGURE 32-2: VOH – 8x DRIVER PINS

## FIGURE 32-4: Vol – 8x DRIVER PINS

| Section Name                                                                                              | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 16.0 "High-Speed<br>PWM Module<br>(dsPIC33EPXXXMC20X/50X<br>and PIC24EPXXXMC20X<br>Devices Only)" | Updated the High-Speed PWM Module Register Interconnection Diagram (see Figure 16-2).<br>Added the TRGCONx and TRIGx registers (see Register 16-12 and Register 16-14, respectively).                                                                                                                                                                                                                                                                                                         |

| Section 21.0 "Enhanced<br>CAN (ECAN™) Module<br>(dsPIC33EPXXXGP/MC50X<br>Devices Only)"                   | Updated the CANCKS bit value definitions in CiCTRL1: ECAN Control Register 1 (see Register 21-1).                                                                                                                                                                                                                                                                                                                                                                                             |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                                                     | Updated the IRNG<1:0> bit value definitions and added Note 2 in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                                                                                                                                                                                        |

| Section 25.0 "Op amp/<br>Comparator Module"                                                               | Updated the Op amp/Comparator I/O Operating Modes Diagram (see Figure 25-1).<br>Updated the User-programmable Blanking Function Block Diagram (see Figure 25-3).<br>Updated the Digital Filter Interconnect Block Diagram (see Figure 25-4).<br>Added <b>Section 25.1 "Op amp Application Considerations</b> ".<br>Added Note 2 to the Comparator Control Register (see Register 25-2).<br>Updated the bit definitions in the Comparator Mask Gating Control Register (see<br>Register 25-5). |

| Section 27.0 "Special<br>Features"                                                                        | Updated the FICD Configuration Register, updated Note 1, and added Note 3 in the Configuration Byte Register Map (see Table 27-1).<br>Added <b>Section 27.2 "User ID Words"</b> .                                                                                                                                                                                                                                                                                                             |

| Section 30.0 "Electrical<br>Characteristics"                                                              | <ul> <li>Updated the following Absolute Maximum Ratings:</li> <li>Maximum current out of Vss pin</li> <li>Maximum current into VDD pin</li> <li>Added Note 1 to the Operating MIPS vs. Voltage (see Table 30-1).</li> </ul>                                                                                                                                                                                                                                                                   |

|                                                                                                           | Updated all Idle Current (IIDLE) Typical and Maximum DC Characteristics values (see Table 30-7).                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                           | Updated all Doze Current (IDOZE) Typical and Maximum DC Characteristics values (see Table 30-9).                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                           | Added Note 2, removed Parameter CM24, updated the Typical values Parameters CM10, CM20, CM21, CM32, CM41, CM44, and CM45, and updated the Minimum values for CM40 and CM41, and the Maximum value for CM40 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                                                                                                                                                                                                 |