Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

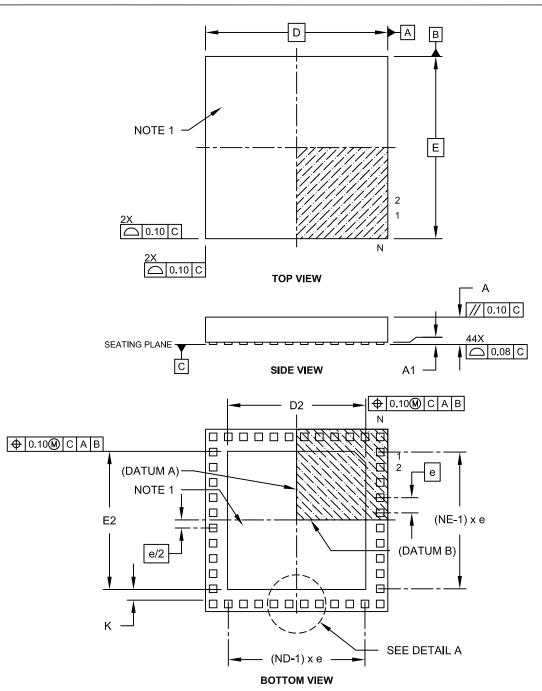

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc506-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

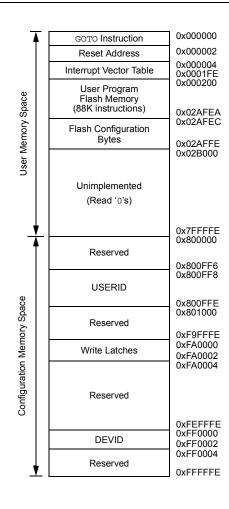

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9          | Bit 8  | Bit 7 | Bit 6  | Bit 5           | Bit 4         | Bit 3  | Bit 2    | Bit 1        | Bit 0   | All<br>Reset |

|--------------|-------|--------|--------|------------|--------|--------|--------|----------------|--------|-------|--------|-----------------|---------------|--------|----------|--------------|---------|--------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF        | T3IF   | T2IF  | OC2IF  | IC2IF           | DMA0IF        | T1IF   | OC1IF    | IC1IF        | INTOIF  | 0000         |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF          | DMA2IF | _     | _      | _               | INT1IF        | CNIF   | CMIF     | MI2C1IF      | SI2C1IF | 0000         |

| IFS2         | 0804  | _      | _      | _          | _      |        |        |                | _      | _     | IC4IF  | IC3IF           | DMA3IF        | C1IF   | C1RXIF   | SPI2IF       | SPI2EIF | 0000         |

| IFS3         | 0806  | _      | _      | _          | _      |        | QEI1IF | PSEMIF         | _      | _     | _      | _               | _             | _      | MI2C2IF  | SI2C2IF      | _       | 0000         |

| IFS4         | 0808  | _      | _      | CTMUIF     |        |        |        | -              | _      | _     | C1TXIF | _               | _             | CRCIF  | U2EIF    | U1EIF        |         | 0000         |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          |        |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            |         | 0000         |

| IFS6         | 080C  | _      | _      | _          |        |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            | PWM3IF  | 0000         |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          |        |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            |         | 0000         |

| IFS9         | 0812  | _      | —      | _          | _      | _      |        |                | _      | —     | PTG3IF | PTG2IF          | PTG1IF        | PTG0IF | PTGWDTIF | PTGSTEPIF    |         | 0000         |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE        | T3IE   | T2IE  | OC2IE  | IC2IE           | DMA0IE        | T1IE   | OC1IE    | IC1IE        | INTOIE  | 0000         |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE          | DMA2IE | —     | _      | —               | INT1IE        | CNIE   | CMIE     | MI2C1IE      | SI2C1IE | 0000         |

| IEC2         | 0824  | _      | _      | _          | _      | _      |        | _              | _      | _     | IC4IE  | IC3IE           | <b>DMA3IE</b> | C1IE   | C1RXIE   | SPI2IE       | SPI2EIE | 0000         |

| IEC3         | 0826  | _      | _      | _          | _      | _      | QEI1IE | PSEMIE         | _      | _     | _      | _               | _             | _      | MI2C2IE  | SI2C2IE      | _       | 0000         |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      |        |        | _              | _      | _     | C1TXIE | _               | _             | CRCIE  | U2EIE    | U1EIE        | _       | 0000         |

| IEC5         | 082A  | PWM2IE | PWM1IE | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC6         | 082C  | _      | _      | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | PWM3IE  | 0000         |

| IEC7         | 082E  | _      | _      | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC9         | 0832  | _      | _      | _          | _      | _      |        | _              | _      | _     | PTG3IE | PTG2IE          | PTG1IE        | PTG0IE | PTGWDTIE | PTGSTEPIE    | _       | 0000         |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0      | >      | _     |        | IC1IP<2:0>      |               | _      |          | INT0IP<2:0>  |         | 4444         |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0      | >      | _     |        | IC2IP<2:0>      |               | _      | [        | DMA0IP<2:0>  |         | 4444         |

| IPC2         | 0844  | _      | l      | J1RXIP<2:0 | >      | _      |        | SPI1IP<2:0     | )>     | _     |        | SPI1EIP<2:0     | >             |        |          | T3IP<2:0>    |         | 4444         |

| IPC3         | 0846  | _      | _      | _          | _      | _      | C      | MA1IP<2:       | 0>     | _     |        | AD1IP<2:0>      |               |        |          | U1TXIP<2:0>  |         | 0444         |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |        | CMIP<2:0       | >      | _     |        | MI2C1IP<2:0     | >             |        | 5        | SI2C1IP<2:0> |         | 4444         |

| IPC5         | 084A  | _      | _      | _          | _      | _      |        | _              | _      | _     | _      | _               | _             |        |          | INT1IP<2:0>  |         | 0004         |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0      | >      | _     |        | OC3IP<2:0>      |               |        | [        | DMA2IP<2:0>  |         | 4444         |

| IPC7         | 084E  | _      | 1      | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:      | 0>     | _     |        | INT2IP<2:0>     |               |        |          | T5IP<2:0>    |         | 4444         |

| IPC8         | 0850  | _      |        | C1IP<2:0>  |        | _      | C      | 2:<br>2:<br>2: | 0>     | _     |        | SPI2IP<2:0>     |               |        | 5        | SPI2EIP<2:0> |         | 4444         |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0      | >      | _     |        | IC3IP<2:0>      |               |        | [        | DMA3IP<2:0>  |         | 0444         |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | 112C2IP<2:     | 0>     | _     |        | SI2C2IP<2:0     | >             | _      | _        | _            | _       | 0440         |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (      | QEI1IP<2:(     | )>     | _     |        | PSEMIP<2:0      | >             | _      | _        | _            | _       | 0440         |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |        | U2EIP<2:0      |        | _     |        | U1EIP<2:0>      |               | _      | <u> </u> | _            | _       | 4440         |

| IPC17        | 0862  | _      | _      | _          | _      | _      |        | C1TXIP<2:      |        | _     | _      | _               | —             | _      | _        | _            | _       | 0400         |

| IPC19        | 0866  | _      | _      |            |        | _      |        |                |        |       |        | L<br>CTMUIP<2:0 | >             |        | <u> </u> | _            | _       | 0040         |

### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

DS70000657H-page 73

|                 |       |        |                   |         |         |         |            |         |          |         |        |       |       |        |          |          |        | All    |  |

|-----------------|-------|--------|-------------------|---------|---------|---------|------------|---------|----------|---------|--------|-------|-------|--------|----------|----------|--------|--------|--|

| File Name       | Addr. | Bit 15 | Bit 14            | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9   | Bit 8    | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0  | Resets |  |

| PTGCST          | 0AC0  | PTGEN  | —                 | PTGSIDL | PTGTOGL |         | PTGSWT     | PTGSSEN | PTGIVIS  | PTGSTRT | PTGWTO | _     | _     | —      | —        | PTGIT    | M<1:0> | 0000   |  |

| PTGCON          | 0AC2  | F      | PTGCLK<2          | :0>     |         | F       | PTGDIV<4:0 | >       |          |         | PTGPWD | <3:0> |       | _      | P        | TGWDT<2: | 0>     | 0000   |  |

| PTGBTE          | 0AC4  |        | ADC               | TS<4:1> |         | IC4TSS  | IC3TSS     | IC2TSS  | IC1TSS   | OC4CS   | OC3CS  | OC2CS | OC1CS | OC4TSS | OC3TSS   | OC2TSS   | OC1TSS | 0000   |  |

| PTGHOLD         | 0AC6  |        |                   |         |         |         |            |         | PTGHOLD  | <15:0>  |        |       |       |        |          |          |        | 0000   |  |

| <b>PTGT0LIM</b> | 0AC8  |        |                   |         |         |         |            |         | PTGT0LIM | <15:0>  |        |       |       |        |          |          |        | 0000   |  |

| PTGT1LIM        | 0ACA  |        |                   |         |         |         |            |         |          |         |        |       | 0000  |        |          |          |        |        |  |

| PTGSDLIM        | 0ACC  |        |                   |         |         |         |            |         |          |         |        |       | 0000  |        |          |          |        |        |  |

| <b>PTGC0LIM</b> | 0ACE  |        | PTGC0LIM<15:0> 00 |         |         |         |            |         |          |         |        |       | 0000  |        |          |          |        |        |  |

| PTGC1LIM        | 0AD0  |        |                   |         |         |         |            |         | PTGC1LIN | <15:0>  |        |       |       |        |          |          |        | 0000   |  |

| PTGADJ          | 0AD2  |        |                   |         |         |         |            |         | PTGADJ<  | :15:0>  |        |       |       |        |          |          |        | 0000   |  |

| PTGL0           | 0AD4  |        |                   |         |         |         |            |         | PTGL0<   | 15:0>   |        |       |       |        |          |          |        |        |  |

| PTGQPTR         | 0AD6  | —      | —                 | —       | —       | _       | —          | —       | _        | —       | —      | -     |       | P      | TGQPTR<4 | 4:0>     |        | 0000   |  |

| PTGQUE0         | 0AD8  |        |                   |         | STEP    | 1<7:0>  |            |         |          |         |        |       | STEPO | )<7:0> |          |          |        | 0000   |  |

| PTGQUE1         | 0ADA  |        |                   |         | STEP    | '3<7:0> |            |         |          |         |        |       | STEP2 | 2<7:0> |          |          |        | 0000   |  |

| PTGQUE2         | 0ADC  |        |                   |         | STEP    | 25<7:0> |            |         |          |         |        |       | STEP4 | <7:0>  |          |          |        | 0000   |  |

| PTGQUE3         | 0ADE  |        |                   |         | STEP    | 7<7:0>  |            |         |          |         |        |       | STEP6 | 6<7:0> |          |          |        | 0000   |  |

| PTGQUE4         | 0AE0  |        |                   |         | STEP    | 9<7:0>  |            |         |          |         |        |       | STEP8 | 8<7:0> |          |          |        | 0000   |  |

| PTGQUE5         | 0AE2  |        |                   |         | STEP    | 11<7:0> |            |         |          |         |        |       | STEP1 | 0<7:0> |          |          |        | 0000   |  |

| PTGQUE6         | 0AE4  |        |                   |         | STEP    | 13<7:0> |            |         |          |         |        |       | STEP1 | 2<7:0> |          |          |        | 0000   |  |

| PTGQUE7         | 0AE6  |        |                   |         | STEP    | 15<7:0> |            |         |          |         |        |       | STEP1 | 4<7:0> |          |          |        | 0000   |  |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

### TABLE 4-49: PORTD REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|--------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD        | 0E30  | _      | _      | _      |        | _      | _      | _     | TRISD8 |       | TRISD6 | TRISD5 |       |       |       |       | _     | 0160          |

| PORTD        | 0E32  | _      | _      |        | _      | _      | _      |       | RD8    | —     | RD6    | RD5    | —     | _     | _     | _     |       | xxxx          |

| LATD         | 0E34  | _      | _      |        | _      | _      | _      |       | LATD8  | —     | LATD6  | LATD5  | —     | _     | _     | _     |       | xxxx          |

| ODCD         | 0E36  | _      |        |        | -      |        |        |       | ODCD8  | —     | ODCD6  | ODCD5  | —     | _     | _     | _     |       | 0000          |

| CNEND        | 0E38  | _      |        |        | -      |        |        |       | CNIED8 | —     | CNIED6 | CNIED5 | —     | _     | _     | _     |       | 0000          |

| CNPUD        | 0E3A  | _      | _      |        | _      | _      | _      |       | CNPUD8 | —     | CNPUD6 | CNPUD5 | —     | _     | _     | _     |       | 0000          |

| CNPDD        | 0E3C  | _      | _      |        | _      | _      | _      |       | CNPDD8 | —     | CNPDD6 | CNPDD5 | —     | _     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-50: PORTE REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISE        | 0E40  | TRISE15 | TRISE14 | TRISE13 | TRISE12 | —      | _      | _     | —     | _     |       | -     | —     | —     | _     | —     |       | F000          |

| PORTE        | 0E42  | RE15    | RE14    | RE13    | RE12    | _      | —      | —     | —     | -     | —     | —     | _     | —     | —     | —     | —     | xxxx          |

| LATE         | 0E44  | LATE15  | LATE14  | LATE13  | LATE12  | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | xxxx          |

| ODCE         | 0E46  | ODCE15  | ODCE14  | ODCE13  | ODCE12  | —      | -      | -     | _     |       |       | -     | —     | —     | _     | _     | -     | 0000          |

| CNENE        | 0E48  | CNIEE15 | CNIEE14 | CNIEE13 | CNIEE12 | _      | —      | —     | —     | -     | —     | —     | _     | —     | —     | —     | —     | 0000          |

| CNPUE        | 0E4A  | CNPUE15 | CNPUE14 | CNPUE13 | CNPUE12 | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | 0000          |

| CNPDE        | 0E4C  | CNPDE15 | CNPDE14 | CNPDE13 | CNPDE12 | _      | _      | _     | _     | -     | _     | —     | _     | —     | _     | _     | _     | 0000          |

| ANSELE       | 0E4E  | ANSE15  | ANSE14  | ANSE13  | ANSE12  |        | —      | _     | —     | _     | _     | _     |       |       | _     |       | _     | F000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-51: PORTF REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISF        | 0E50  | —      | -      | —      |        | —      |        | —     | -     | -     | —     | -     | -     | —     | -     | TRISF1 | TRISF0 | 0003          |

| PORTF        | 0E52  | —      | —      | _      | —      | —      | —      | —     | _     | —     | —     | —     | —     | —     | —     | RF1    | RF0    | xxxx          |

| LATF         | 0E54  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | LATF1  | LATF0  | xxxx          |

| ODCF         | 0E56  | _      | -      | _      | -      | —      | -      | —     |       |       | —     |       |       | _     | -     | ODCF1  | ODCF0  | 0000          |

| CNENF        | 0E58  |        | —      | -      |        | —      | -      | _     | -     | -     | —     | -     | -     | —     | -     | CNIEF1 | CNIEF0 | 0000          |

| CNPUF        | 0E5A  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | CNPUF1 | CNPUF0 | 0000          |

| CNPDF        | 0E5C  | _      | _      | _      | _      | -      |        | _     | _     | _     | _     | _     | _     | _     | -     | CNPDF1 | CNPDF0 | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0         | R/W-0                                     | U-0                                    | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |

|---------------|-------------------------------------------|----------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|

| TRAPF         | R IOPUWR                                  | —                                      | _             | VREGSF                | —                 | CM               | VREGS         |

| bit 15        |                                           |                                        |               |                       |                   |                  | bit 8         |

| <b>D</b> 4440 |                                           | DANIO                                  | DAMO          | DAMA                  | DAMO              |                  |               |

| R/W-0         |                                           | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR<br>bit 7 | SWR                                       | SWDTEN <sup>(2)</sup>                  | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |

|               |                                           |                                        |               |                       |                   |                  | bit (         |

| Legend:       |                                           |                                        |               |                       |                   |                  |               |

| R = Reada     | able bit                                  | W = Writable I                         | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |

| -n = Value    | at POR                                    | '1' = Bit is set                       |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |

|               |                                           |                                        |               |                       |                   |                  |               |

| bit 15        | •                                         | Reset Flag bit                         |               |                       |                   |                  |               |

|               |                                           | onflict Reset ha<br>onflict Reset ha   |               | d                     |                   |                  |               |

| bit 14        | •                                         | gal Opcode or                          |               |                       | et Flag bit       |                  |               |

|               |                                           | I opcode detec                         |               |                       | •                 | lized W registe  | er used as ar |

|               |                                           | Pointer caused                         |               |                       |                   |                  |               |

|               | -                                         | l opcode or Uni                        |               | egister Reset h       | as not occurred   | d                |               |

| bit 13-12     | -                                         | ted: Read as '                         |               |                       | . 1.9             |                  |               |

| bit 11        |                                           | ash Voltage Reg<br>Itage regulator i   |               |                       | p bit             |                  |               |

|               |                                           | ltage regulator (                      |               | •                     | ing Sleep         |                  |               |

| bit 10        |                                           | ted: Read as '                         | -             | ,,                    | <b>5 F</b>        |                  |               |

| bit 9         | CM: Configur                              | ation Mismatch                         | Flag bit      |                       |                   |                  |               |

|               | 1 = A Configu                             | uration Mismatc<br>uration Mismatc     | h Reset has   |                       |                   |                  |               |

| bit 8         | VREGS: Volta                              | age Regulator S                        | Standby Durir | ng Sleep bit          |                   |                  |               |

|               | •                                         | egulator is active<br>egulator goes in | •             | •                     | еер               |                  |               |

| bit 7         | EXTR: Extern                              | nal Reset (MCL                         | R) Pin bit    |                       |                   |                  |               |

|               |                                           | Clear (pin) Res<br>Clear (pin) Res     |               |                       |                   |                  |               |

| bit 6         | SWR: Softwa                               | re RESET (Instr                        | uction) Flag  | bit                   |                   |                  |               |

|               |                                           | instruction has instruction has        |               |                       |                   |                  |               |

| bit 5         | SWDTEN: So                                | oftware Enable/                        | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |

|               | 1 = WDT is e<br>0 = WDT is di             |                                        |               |                       |                   |                  |               |

| bit 4         | WDTO: Watc                                | hdog Timer Tim                         | e-out Flag bi | it                    |                   |                  |               |

|               |                                           | e-out has occur<br>e-out has not oc    |               |                       |                   |                  |               |

| Note 1:       | All of the Reset sta<br>cause a device Re |                                        | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir     | onfiguration bit i                     | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/S-0                | U-0                                                         | U-0                                                                                 | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |  |  |  |  |  |

|----------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|--|--|

| FORCE <sup>(1)</sup> |                                                             | _                                                                                   | _                     | —                |                  | _               |         |  |  |  |  |  |  |  |

| bit 15               |                                                             |                                                                                     |                       |                  |                  |                 | bit 8   |  |  |  |  |  |  |  |

|                      |                                                             |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

| R/W-0                | R/W-0                                                       | R/W-0                                                                               | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |  |  |

| IRQSEL7              | IRQSEL6                                                     | IRQSEL5                                                                             | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |  |  |  |  |  |

| bit 7                |                                                             |                                                                                     |                       |                  |                  |                 | bit     |  |  |  |  |  |  |  |

| Legend:              |                                                             | S = Settable b                                                                      | oit                   |                  |                  |                 |         |  |  |  |  |  |  |  |

| R = Readable         | bit                                                         | W = Writable                                                                        | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |  |  |  |

| -n = Value at F      | POR                                                         | '1' = Bit is set                                                                    |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |  |  |

|                      |                                                             |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

| bit 15               | FORCE: Force                                                | e DMA Transfe                                                                       | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 1 = Forces a single DMA transfer (Manual mode)              |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 0 = Automati                                                | c DMA transfer                                                                      | initiation by D       | DMA request      |                  |                 |         |  |  |  |  |  |  |  |

| bit 14-8             | Unimplemented: Read as '0'                                  |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

| bit 7-0              | IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits          |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 01000110 = ECAN1 – TX Data Request <sup>(2)</sup>           |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 00100110 = IC4 – Input Capture 4                            |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | 00100101 = IC3 – Input Capture 3<br>00100010 = ECAN1 – RX Data Ready <sup>(2)</sup> |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | SPI2 Transfer I                                                                     | -                     |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | UART2TX – UA                                                                        |                       | itter            |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | UART2RX – U                                                                         |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | TMR5 – Timer5                                                                       |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 00011011 =                                                  | TMR4 – Timer4                                                                       | 1                     |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | OC4 – Output (                                                                      |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 00011001 = OC3 – Output Compare 3                           |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | ADC1 – ADC1                                                                         |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | UART1TX – UA                                                                        |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 00001011 = UART1RX – UART1 Receiver                         |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 00001010 = SPI1 – Transfer Done<br>00001000 = TMR3 – Timer3 |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 00000111 = TMR2 – Timer2                                    |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | OC2 – Output (                                                                      |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | IC2 – Input Ca                                                                      |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 00000010 = OC1 – Output Compare 1                           |                                                                                     |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      |                                                             | IC1 – Input Ca                                                                      |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                      | 00000000 =                                                  | INT0 – Externa                                                                      | I Interrupt 0         |                  |                  |                 |         |  |  |  |  |  |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

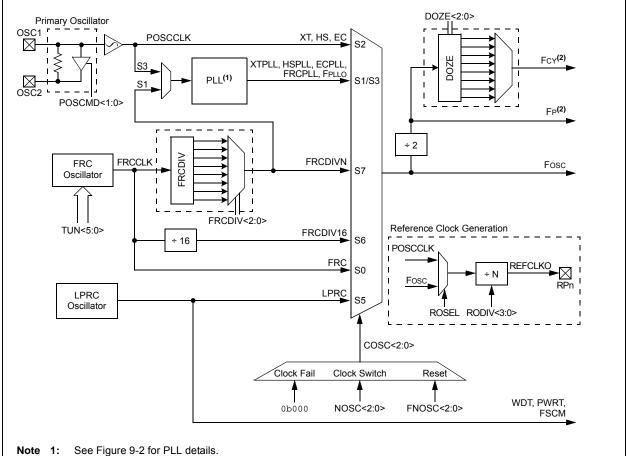

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

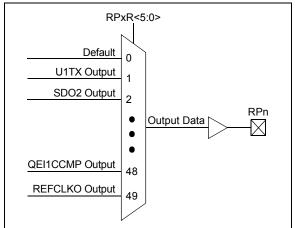

#### 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

#### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

#### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

| U-0             | U-0   | U-0              | U-0   | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

| —               | -     | —                | —     |                   | LEB             | <11:8>          |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | LEE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | id as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

## REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

| U-0                          | U-0               | U-0                                   | U-0            | U-0          | U-0              | U-0             | U-0   |

|------------------------------|-------------------|---------------------------------------|----------------|--------------|------------------|-----------------|-------|

| _                            | —                 | —                                     |                | —            | —                | —               | _     |

| bit 15                       |                   |                                       |                |              |                  |                 | bit   |

|                              |                   |                                       |                |              |                  |                 |       |

| R/W-0                        | R/W-0             | R/W-0                                 | U-0            | R/W-0        | R/W-0            | R/W-0           | R/W-0 |

| IVRIE                        | WAKIE             | ERRIE                                 | —              | FIFOIE       | RBOVIE           | RBIE            | TBIE  |

| bit 7                        |                   |                                       |                |              |                  |                 | bit   |

|                              |                   |                                       |                |              |                  |                 |       |

| <b>Legend:</b><br>R = Readab | la hit            | W = Writable b                        | .it            |              | montod bit rook  | l oo 'O'        |       |

| n = Value a                  |                   | '1' = Bit is set                      | אנ             | 0 = Onimpler | mented bit, read | x = Bit is unkr |       |

|                              | IL POR            | I = DILIS SEL                         |                |              | areu             |                 | IOWI  |

| bit 15-8                     | Unimplemen        | ted: Read as '0                       | ,              |              |                  |                 |       |

| bit 7                        | -                 | Message Inter                         |                | bit          |                  |                 |       |

|                              |                   | request is enabl                      | •              | ~            |                  |                 |       |

|                              |                   | request is not er                     |                |              |                  |                 |       |

| bit 6                        | WAKIE: Bus        | Wake-up Activit                       | y Interrupt E  | nable bit    |                  |                 |       |

|                              |                   | equest is enabl                       |                |              |                  |                 |       |

|                              |                   | request is not er                     |                |              |                  |                 |       |

| bit 5                        |                   | Interrupt Enabl                       |                |              |                  |                 |       |

|                              |                   | request is enabl<br>request is not er |                |              |                  |                 |       |

| bit 4                        |                   | ted: Read as '0                       |                |              |                  |                 |       |

| bit 3                        | -                 | Almost Full Int                       |                | o hit        |                  |                 |       |

| DIL J                        |                   | request is enabl                      | •              | ebit         |                  |                 |       |

|                              |                   | request is not er                     |                |              |                  |                 |       |

| bit 2                        | <b>RBOVIE:</b> RX | Buffer Overflow                       | / Interrupt Er | nable bit    |                  |                 |       |

|                              | 1 = Interrupt     | equest is enabl                       | ed             |              |                  |                 |       |

|                              | 0 = Interrupt i   | request is not er                     | nabled         |              |                  |                 |       |

| bit 1                        |                   | ffer Interrupt En                     |                |              |                  |                 |       |

|                              |                   | equest is enabl                       |                |              |                  |                 |       |

|                              |                   | request is not er                     | nabled         |              |                  |                 |       |

|                              | •                 | •                                     |                |              |                  |                 |       |

| bit 0                        | TBIE: TX Buf      | fer Interrupt Ena<br>request is enabl | able bit       |              |                  |                 |       |

#### REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER

| R/W-0         | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|---------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|------------------|-----------------|--------|

|               | F15B                         | P<3:0>                                                                                                                     |                                                |                   | F14BI            | P<3:0>          |        |

| bit 15        |                              |                                                                                                                            |                                                |                   |                  |                 | bit 8  |

| R/W-0         | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| 1010 0        |                              | P<3:0>                                                                                                                     | 10110                                          |                   |                  | P<3:0>          | 1010 0 |

| bit 7         |                              |                                                                                                                            |                                                |                   |                  |                 | bit 0  |

| Legend:       |                              |                                                                                                                            |                                                |                   |                  |                 |        |

| R = Readabl   | e bit                        | W = Writable                                                                                                               | bit                                            | U = Unimplen      | nented bit, read | d as '0'        |        |

| -n = Value at | t POR                        | '1' = Bit is set                                                                                                           | :                                              | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

| bit 15-12     | 1111 = Filte<br>1110 = Filte | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | differ<br>4       |                  |                 |        |

| bit 11-8      | F14BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val  | ues as bits<15   | :12>)           |        |

| bit 7-4       | F13BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 3 bits (same val  | ues as bits<15   | :12>)           |        |

| bit 3-0       | F12BP<3:0:                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 2 bits (same val  | ues as bits<15   | :12>)           |        |

### REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

| R/W-0        | R/W-0                                                                                                                    | R/W-0                                 | R/W-0            | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|-------------------|------------------|--------------------|-------|--|--|--|

| ITRIM5       | ITRIM4                                                                                                                   | ITRIM3                                | ITRIM2           | ITRIM1            | ITRIM0           | IRNG1              | IRNG0 |  |  |  |

| oit 15       |                                                                                                                          |                                       |                  |                   |                  |                    | bit   |  |  |  |

|              |                                                                                                                          |                                       |                  |                   |                  |                    |       |  |  |  |

| U-0          | U-0                                                                                                                      | U-0                                   | U-0              | U-0               | U-0              | U-0                | U-0   |  |  |  |

|              | —                                                                                                                        |                                       |                  |                   | <u> </u>         |                    |       |  |  |  |

| oit 7        |                                                                                                                          |                                       |                  |                   |                  |                    | bit   |  |  |  |

| _egend:      |                                                                                                                          |                                       |                  |                   |                  |                    |       |  |  |  |

| R = Readabl  | e hit                                                                                                                    | W = Writable                          | hit              | II = I Inimplen   | nented bit, read | t as 'O'           |       |  |  |  |

| n = Value at |                                                                                                                          | '1' = Bit is set '0' = Bit is cleared |                  |                   |                  | x = Bit is unknown |       |  |  |  |

|              |                                                                                                                          |                                       |                  |                   | arcu             |                    |       |  |  |  |

| oit 15-10    | ITRIM<5:0>: (                                                                                                            | Current Source                        | Trim bits        |                   |                  |                    |       |  |  |  |

|              | ITRIM<5:0>: Current Source Trim bits<br>011111 = Maximum positive change from nominal current + 62%                      |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 011110 = Maximum positive change from nominal current + 60%                                                              |                                       |                  |                   |                  |                    |       |  |  |  |

|              | •                                                                                                                        |                                       |                  |                   |                  |                    |       |  |  |  |

|              |                                                                                                                          |                                       |                  |                   |                  |                    |       |  |  |  |

|              |                                                                                                                          |                                       |                  |                   |                  |                    |       |  |  |  |

|              | -                                                                                                                        |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 000010 = Minimum positive change from nominal current + 4%<br>000001 = Minimum positive change from nominal current + 2% |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 000000 = Nominal current output specified by IRNG<1:0>                                                                   |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 111111 = Minimum negative change from nominal current – 2%                                                               |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 111110 = Minimum negative change from nominal current – 4%                                                               |                                       |                  |                   |                  |                    |       |  |  |  |

|              | •                                                                                                                        |                                       |                  |                   |                  |                    |       |  |  |  |

|              | •                                                                                                                        |                                       |                  |                   |                  |                    |       |  |  |  |

|              | •                                                                                                                        |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 100010 = Maximum negative change from nominal current – 60%                                                              |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 100001 = Maximum negative change from nominal current – 62%                                                              |                                       |                  |                   |                  |                    |       |  |  |  |

| oit 9-8      | IRNG<1:0>: Current Source Range Select bits                                                                              |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 11 = $100 \times \text{Base Current}^{(2)}$                                                                              |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 10 = 10 × Base Current <sup>(2)</sup>                                                                                    |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 01 = Base Current Level <sup>(2)</sup>                                                                                   |                                       |                  |                   |                  |                    |       |  |  |  |

|              | 00 = 1000 × E                                                                                                            | Base Current <sup>(1,</sup>           | 2)               |                   |                  |                    |       |  |  |  |

| oit 7-0      | Unimplemented: Read as '0'                                                                                               |                                       |                  |                   |                  |                    |       |  |  |  |

| Note 1: Th   | his current range                                                                                                        | o is not availab                      | lo to bo used w  | with the internel | tomporature n    | aasuromont di      | odo   |  |  |  |

|              | •                                                                                                                        |                                       | rce Specificatio |                   | •                |                    |       |  |  |  |

#### REGISTER 22-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

2: Refer to the CTMU Current Source Specifications (Table 30-56) in Section 30.0 "Electrical Characteristics" for the current range selection values.

### 27.6 JTAG Interface

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |

|-------|----------------------------------------------|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |

|       | Reference Manual" for further information    |

|       | on usage, configuration and operation of the |

|       | JTAG interface.                              |

## 27.7 In-Circuit Serial Programming

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

### 27.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

### 27.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X, and PIC24EPXXXGP/MC20X devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to "CodeGuard<sup>™</sup> Security" (DS70634) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

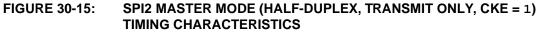

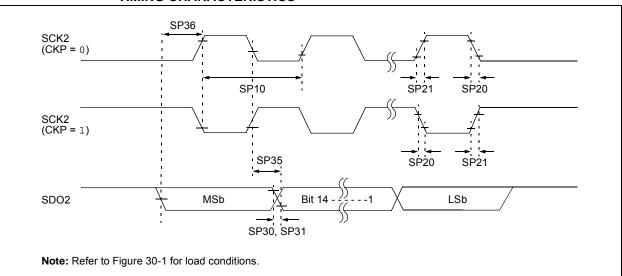

#### TABLE 30-34: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                      |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                                |

|--------------------|--------------------------------------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol Characteristic <sup>(1)</sup> |                                              | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP10               | FscP                                 | Maximum SCK2 Frequency                       | _                                                     | _                   | 15   | MHz   | (Note 3)                       |

| SP20               | TscF                                 | SCK2 Output Fall Time                        | —                                                     | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP21               | TscR                                 | SCK2 Output Rise Time                        | —                                                     | —                   | _    | ns    | See Parameter DO31<br>(Note 4) |

| SP30               | TdoF                                 | SDO2 Data Output Fall Time                   | —                                                     | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP31               | TdoR                                 | SDO2 Data Output Rise Time                   | -                                                     | _                   |      | ns    | See Parameter DO31<br>(Note 4) |

| SP35               | TscH2doV,<br>TscL2doV                | SDO2 Data Output Valid after<br>SCK2 Edge    | —                                                     | 6                   | 20   | ns    |                                |

| SP36               | TdiV2scH,<br>TdiV2scL                | SDO2 Data Output Setup to<br>First SCK2 Edge | 30                                                    | —                   | _    | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

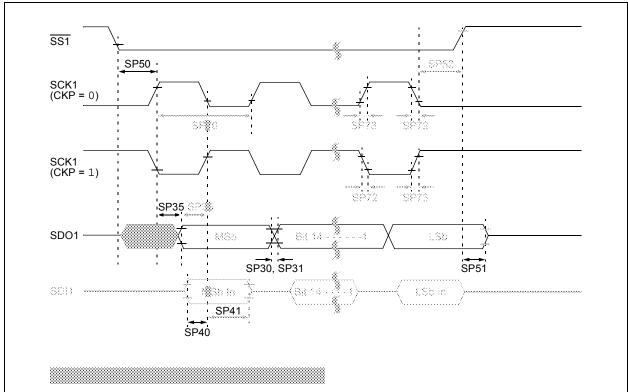

#### FIGURE 30-28: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

| DC CHARACTERISTICS        |                  |                                                                        | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array} $ |                     |                              |        |                                            |  |  |

|---------------------------|------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------|--------|--------------------------------------------|--|--|

| Param<br>No.              | Symbol           | Characteristic                                                         | Min.                                                                                                                                                                                                                                                                                        | Тур. <sup>(2)</sup> | Max.                         | Units  | Conditions                                 |  |  |