Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc506-i-mr |

TABLE 4-3: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6          | Bit 5       | Bit 4   | Bit 3   | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|----------------|-------------|---------|---------|----------|--------------|---------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF          | IC2IF       | DMA0IF  | T1IF    | OC1IF    | IC1IF        | INT0IF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _              | _           | INT1IF  | CNIF    | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  | _      | ı      | _          | ı      | _      | _      | _          | _      | _     | IC4IF          | IC3IF       | DMA3IF  | _       | ı        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | 1      | _          | 1      | _      | _      | _          | _      | _     | _              | _           | ı       | _       | MI2C2IF  | SI2C2IF      | _       | 0000          |

| IFS4         | 8080  | _      |        | CTMUIF     |        | _      | _      | _          | _      | _     | _              | _           |         | CRCIF   | U2EIF    | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          |        | _      | _      | _          | _      | _     | _              | _           | _       | _       | _        | _            | _       | 0000          |

| IFS9         | 0812  | _      | _      | _          |        | _      | _      | _          | _      | _     | PTG3IF         | PTG2IF      | PTG1IF  | PTG0IF  | PTGWDTIF | PTGSTEPIF    | _       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE          | IC2IE       | DMA0IE  | T1IE    | OC1IE    | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _              | _           | INT1IE  | CNIE    | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | 1      | _          | 1      | _      | _      | _          | _      | _     | IC4IE          | IC3IE       | DMA3IE  | _       | ı        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | 1      | _          | 1      | _      | _      | _          | _      | _     | _              | _           | ı       | _       | MI2C2IE  | SI2C2IE      | _       | 0000          |

| IEC4         | 0828  | _      | 1      | CTMUIE     | 1      | _      | _      | _          | _      | _     | _              | _           | ı       | CRCIE   | U2EIE    | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | 1      | _      | _      | _          | _      | _     | _              | _           | ı       | _       | ı        | ı            | _       | 0000          |

| IEC9         | 0832  | _      | 1      | _          | 1      | _      | _      | _          | _      | _     | PTG3IE         | PTG2IE      | PTG1IE  | PTG0IE  | PTGWDTIE | PTGSTEPIE    | _       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0  | >      | _     |                | IC1IP<2:0>  |         | _       |          | NT0IP<2:0>   |         | 4444          |

| IPC1         | 0842  |        |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0  | >      | _     |                | IC2IP<2:0>  |         | _       |          | MA0IP<2:0>   |         | 4444          |

| IPC2         | 0844  |        | J      | J1RXIP<2:0 | >      | _      | 0)     | SPI1IP<2:0 | )>     | _     |                | SPI1EIP<2:0 | >       | _       |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          |        | _      | D      | MA1IP<2:   | 0>     | _     |                | AD1IP<2:0>  |         | _       | ι        | J1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0>  |        | _      |        | CMIP<2:0   | >      | _     |                | MI2C1IP<2:0 | >       | _       | S        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  |        | 1      | _          | 1      | _      | _      | _          | _      | _     | _              | _           | ı       | _       |          | NT1IP<2:0>   |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0  | >      | _     |                | OC3IP<2:0>  |         | _       |          | MA2IP<2:0>   |         | 4444          |

| IPC7         | 084E  |        | l      | J2TXIP<2:0 | >      | _      | U      | 12RXIP<2:  | 0>     | _     |                | INT2IP<2:0> | •       | _       |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |        | 1      | _          | 1      | _      | _      | _          | _      | _     |                | SPI2IP<2:0> | •       | _       | S        | PI2EIP<2:0>  |         | 0044          |

| IPC9         | 0852  |        | 1      | _          | 1      | _      |        | IC4IP<2:0  | >      | _     |                | IC3IP<2:0>  |         | _       |          | MA3IP<2:0>   |         | 0444          |

| IPC12        | 0858  |        | 1      | _          | 1      | _      | M      | II2C2IP<2: | 0>     | _     |                | SI2C2IP<2:0 | >       | _       | ı        | ı            | _       | 0440          |

| IPC16        | 0860  |        |        | CRCIP<2:0> | •      | _      | _      | J2EIP<2:0  | >      | _     |                | U1EIP<2:0>  |         | _       | ı        | ı            | _       | 4440          |

| IPC19        | 0866  |        | 1      | _          | 1      | _      | _      | _          | _      | _     |                | CTMUIP<2:0  | >       | _       | ı        | ı            | _       | 0040          |

| IPC35        | 0886  | -      | ,      | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >      |       | _              | _           | _       | _       | _        | _            | _       | 4400          |

| IPC36        | 0888  |        | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>   | _     | P <sup>-</sup> | TGSTEPIP<2  | :0>     | _       | I        | ı            | _       | 4440          |

| IPC37        | 088A  | -      | -      | _          | -      | _      | P      | TG3IP<2:0  | 0>     |       |                | PTG2IP<2:0  | >       | _       | F        | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | _      |        |        |            |        | _     | DIV0ERR        | DMACERR     | MATHERR | ADDRERR | STKERR   | OSCFAIL      | _       | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | -      |        |        |            |        | _     | _              |             |         |         | INT2EP   | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _      | -      | _          | -      |        | _      |            |        | _     | _              | DAE         | DOOVR   | _       | -        |              | _       | 0000          |

| INTCON4      | 08C6  | _      | -      | _          | -      |        |        |            | _      | _     | _              | _           |         | _       | -        | _            | SGHT    | 0000          |

| INTTREG      | 08C8  |        | -      | _          | _      |        | ILR<   | 3:0>       |        |       |                |             | VECNU   | JM<7:0> |          |              |         | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                    | Bit 8                     | Bit 7 | Bit 6 | Bit 5     | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|--------------------------|---------------------------|-------|-------|-----------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | _       | _      | _       | _      | _      | _      | _                        | — — I2C1 Receive Register |       |       |           |             |              |       |       | 0000  |               |

| I2C1TRN      | 0202  | -       | _      | -       | _      | _      | _      | _                        | -                         |       |       |           | I2C1 Trans  | mit Register |       |       |       | 00FF          |

| I2C1BRG      | 0204  | -       | _      | 1       | -      | _      | _      | -                        | — Baud Rate Generator     |       |       |           |             |              |       |       |       | 0000          |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                   | SMEN                      | GCEN  | STREN | ACKDT     | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                   | ADD10                     | IWCOL | I2COV | D_A       | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      |                          |                           |       |       | I2C1 Addr | ess Registe | r            |       |       |       | 0000          |

| I2C1MSK      | 020C  | -       | _      | -       | _      | _      | _      |                          |                           |       |       | I2C1 Add  | dress Mask  |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | -       | _      | -       | _      | _      | _      | _                        | -                         |       |       |           | I2C2 Recei  | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | -       | _      | -       | _      | _      | _      | _                        | -                         |       |       |           | I2C2 Trans  | mit Register |       |       |       | 00FF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | -      | _                        |                           |       |       | Bau       | d Rate Gene | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                   | SMEN                      | GCEN  | STREN | ACKDT     | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                   | ADD10                     | IWCOL | I2COV | D_A       | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | 1       | _      | _      | -      | I2C2 Address Register 00 |                           |       |       |           |             |              | 0000  |       |       |               |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | -      | I2C2 Address Mask 0      |                           |       |       |           |             |              | 0000  |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

|             |       | . •                                 |        | ,, <del></del> |        |        |        | _     |                          |            |          | _                 | _            |          |       |        |       |               |

|-------------|-------|-------------------------------------|--------|----------------|--------|--------|--------|-------|--------------------------|------------|----------|-------------------|--------------|----------|-------|--------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15                              | Bit 14 | Bit 13         | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                    | Bit 7      | Bit 6    | Bit 5             | Bit 4        | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE      | 0220  | UARTEN                              | _      | USIDL          | IREN   | RTSMD  | _      | UEN<  | :1:0>                    | WAKE       | LPBACK   | ABAUD             | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1                            | UTXINV | UTXISEL0       | ı      | UTXBRK | UTXEN  | UTXBF | TRMT                     | URXIS      | SEL<1:0> | ADDEN             | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _                                   | -      | _              | ı      |        | -      | _     |                          |            |          | UART1             | 1 Transmit F | Register |       |        |       | xxxx          |

| U1RXREG     | 0226  | _                                   | -      | _              | ı      |        | _      | _     |                          |            |          | UART <sup>2</sup> | 1 Receive R  | tegister |       |        |       | 0000          |

| U1BRG       | 0228  |                                     |        |                |        |        |        | Baud  | Rate Gen                 | erator Pre | scaler   |                   |              |          |       |        |       | 0000          |

| U2MODE      | 0230  | UARTEN                              | -      | USIDL          | IREN   | RTSMD  | _      | UEN<  | :1:0>                    | WAKE       | LPBACK   | ABAUD             | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1                            | UTXINV | UTXISEL0       | ı      | UTXBRK | UTXEN  | UTXBF | TRMT                     | URXIS      | SEL<1:0> | ADDEN             | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _                                   | -      | _              | ı      |        | _      | _     | UART2 Transmit Register  |            |          |                   |              |          |       | xxxx   |       |               |

| U2RXREG     | 0236  | _                                   |        | _              | -      | _      | _      | _     | UART2 Receive Register 0 |            |          |                   |              |          |       |        | 0000  |               |

| U2BRG       | 0238  | Baud Rate Generator Prescaler 00000 |        |                |        |        |        |       |                          |            | 0000     |                   |              |          |       |        |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

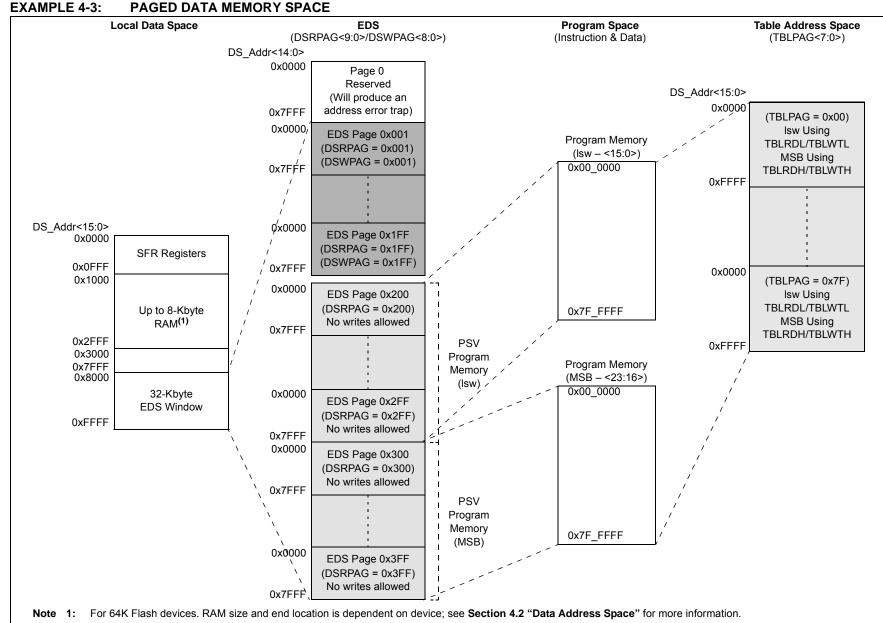

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

2: Clearing the DSxPAG in software has no effect.

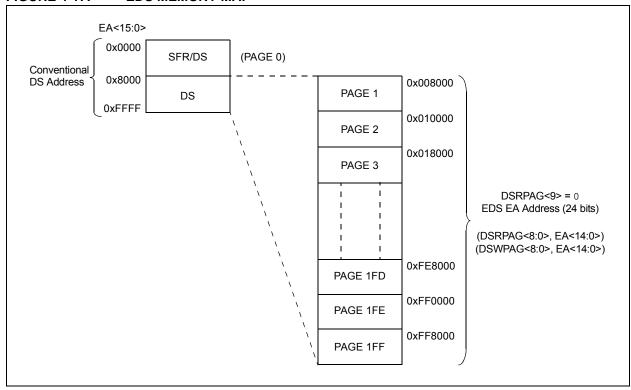

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit. EA<15>=1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "Program Space Visibility from Data Space" section in "Program Memory" (DS70613) of the "dsPIC33/PIC24 Family Reference Manual".

#### FIGURE 4-17: EDS MEMORY MAP

# 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note:

The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

# 4.7 Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all these conditions are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XBREV<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

Note:

All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XBREVx value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XBREVx) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note:

Modulo Addressing and Bit-Reversed Addressing can be enabled simultaneously using the same W register, but Bit-Reversed Addressing operation will always take precedence for data writes when enabled.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

TABLE 7-1: INTERRUPT VECTOR DETAILS

| Intermed Course                               | Vector | IRQ        | D/T Address       | Inte     | errupt Bit L | ocation     |

|-----------------------------------------------|--------|------------|-------------------|----------|--------------|-------------|

| Interrupt Source                              | #      | #          | IVT Address       | Flag     | Enable       | Priority    |

|                                               | Highe  | est Natura | al Order Priority |          |              |             |

| INT0 – External Interrupt 0                   | 8      | 0          | 0x000014          | IFS0<0>  | IEC0<0>      | IPC0<2:0>   |

| IC1 – Input Capture 1                         | 9      | 1          | 0x000016          | IFS0<1>  | IEC0<1>      | IPC0<6:4>   |

| OC1 – Output Compare 1                        | 10     | 2          | 0x000018          | IFS0<2>  | IEC0<2>      | IPC0<10:8>  |

| T1 – Timer1                                   | 11     | 3          | 0x00001A          | IFS0<3>  | IEC0<3>      | IPC0<14:12> |

| DMA0 – DMA Channel 0                          | 12     | 4          | 0x00001C          | IFS0<4>  | IEC0<4>      | IPC1<2:0>   |

| IC2 – Input Capture 2                         | 13     | 5          | 0x00001E          | IFS0<5>  | IEC0<5>      | IPC1<6:4>   |

| OC2 – Output Compare 2                        | 14     | 6          | 0x000020          | IFS0<6>  | IEC0<6>      | IPC1<10:8>  |

| T2 – Timer2                                   | 15     | 7          | 0x000022          | IFS0<7>  | IEC0<7>      | IPC1<14:12> |

| T3 – Timer3                                   | 16     | 8          | 0x000024          | IFS0<8>  | IEC0<8>      | IPC2<2:0>   |

| SPI1E – SPI1 Error                            | 17     | 9          | 0x000026          | IFS0<9>  | IEC0<9>      | IPC2<6:4>   |

| SPI1 – SPI1 Transfer Done                     | 18     | 10         | 0x000028          | IFS0<10> | IEC0<10>     | IPC2<10:8>  |

| U1RX – UART1 Receiver                         | 19     | 11         | 0x00002A          | IFS0<11> | IEC0<11>     | IPC2<14:12> |

| U1TX – UART1 Transmitter                      | 20     | 12         | 0x00002C          | IFS0<12> | IEC0<12>     | IPC3<2:0>   |

| AD1 – ADC1 Convert Done                       | 21     | 13         | 0x00002E          | IFS0<13> | IEC0<13>     | IPC3<6:4>   |

| DMA1 – DMA Channel 1                          | 22     | 14         | 0x000030          | IFS0<14> | IEC0<14>     | IPC3<10:8>  |

| Reserved                                      | 23     | 15         | 0x000032          | _        | _            | _           |

| SI2C1 – I2C1 Slave Event                      | 24     | 16         | 0x000034          | IFS1<0>  | IEC1<0>      | IPC4<2:0>   |

| MI2C1 – I2C1 Master Event                     | 25     | 17         | 0x000036          | IFS1<1>  | IEC1<1>      | IPC4<6:4>   |

| CM – Comparator Combined Event                | 26     | 18         | 0x000038          | IFS1<2>  | IEC1<2>      | IPC4<10:8>  |

| CN - Input Change Interrupt                   | 27     | 19         | 0x00003A          | IFS1<3>  | IEC1<3>      | IPC4<14:12> |

| INT1 – External Interrupt 1                   | 28     | 20         | 0x00003C          | IFS1<4>  | IEC1<4>      | IPC5<2:0>   |

| Reserved                                      | 29-31  | 21-23      | 0x00003E-0x000042 | _        | _            | _           |

| DMA2 – DMA Channel 2                          | 32     | 24         | 0x000044          | IFS1<8>  | IEC1<8>      | IPC6<2:0>   |

| OC3 – Output Compare 3                        | 33     | 25         | 0x000046          | IFS1<9>  | IEC1<9>      | IPC6<6:4>   |

| OC4 – Output Compare 4                        | 34     | 26         | 0x000048          | IFS1<10> | IEC1<10>     | IPC6<10:8>  |

| T4 – Timer4                                   | 35     | 27         | 0x00004A          | IFS1<11> | IEC1<11>     | IPC6<14:12> |

| T5 – Timer5                                   | 36     | 28         | 0x00004C          | IFS1<12> | IEC1<12>     | IPC7<2:0>   |

| INT2 – External Interrupt 2                   | 37     | 29         | 0x00004E          | IFS1<13> | IEC1<13>     | IPC7<6:4>   |

| U2RX – UART2 Receiver                         | 38     | 30         | 0x000050          | IFS1<14> | IEC1<14>     | IPC7<10:8>  |

| U2TX – UART2 Transmitter                      | 39     | 31         | 0x000052          | IFS1<15> | IEC1<15>     | IPC7<14:12> |

| SPI2E – SPI2 Error                            | 40     | 32         | 0x000054          | IFS2<0>  | IEC2<0>      | IPC8<2:0>   |

| SPI2 – SPI2 Transfer Done                     | 41     | 33         | 0x000056          | IFS2<1>  | IEC2<1>      | IPC8<6:4>   |

| C1RX – CAN1 RX Data Ready <sup>(1)</sup>      | 42     | 34         | 0x000058          | IFS2<2>  | IEC2<2>      | IPC8<10:8>  |

| C1 – CAN1 Event <sup>(1)</sup>                | 43     | 35         | 0x00005A          | IFS2<3>  | IEC2<3>      | IPC8<14:12> |

| DMA3 – DMA Channel 3                          | 44     | 36         | 0x00005C          | IFS2<4>  | IEC2<4>      | IPC9<2:0>   |

| IC3 – Input Capture 3                         | 45     | 37         | 0x00005E          | IFS2<5>  | IEC2<5>      | IPC9<6:4>   |

| IC4 – Input Capture 4                         | 46     | 38         | 0x000060          | IFS2<6>  | IEC2<6>      | IPC9<10:8>  |

| Reserved                                      | 47-56  | 39-48      | 0x000062-0x000074 | _        | _            | _           |

| SI2C2 - I2C2 Slave Event                      | 57     | 49         | 0x000076          | IFS3<1>  | IEC3<1>      | IPC12<6:4>  |

| MI2C2 – I2C2 Master Event                     | 58     | 50         | 0x000078          | IFS3<2>  | IEC3<2>      | IPC12<10:8> |

| Reserved                                      | 59-64  | 51-56      | 0x00007A-0x000084 | _        | _            | _           |

| PSEM – PWM Special Event Match <sup>(2)</sup> | 65     | 57         | 0x000086          | IFS3<9>  | IEC3<9>      | IPC14<6:4>  |

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

<sup>2:</sup> This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

#### REGISTER 8-1: DMAXCON: DMA CHANNEL x CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|--------|-------|-------|-------|-------|-----|-----|-------|

| CHEN   | SIZE  | DIR   | HALF  | NULLW | _   | _   | _     |

| bit 15 |       |       |       |       |     |     | bit 8 |

| U-0   | U-0 | R/W-0  | R/W-0  | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----|--------|--------|-----|-----|-------|-------|

| _     | _   | AMODE1 | AMODE0 | _   | _   | MODE1 | MODE0 |

| bit 7 |     |        |        |     |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CHEN: DMA Channel Enable bit

1 = Channel is enabled0 = Channel is disabled

bit 14 SIZE: DMA Data Transfer Size bit

1 = Byte0 = Word

bit 13 DIR: DMA Transfer Direction bit (source/destination bus select)

1 = Reads from RAM address, writes to peripheral address

0 = Reads from peripheral address, writes to RAM address

bit 12 HALF: DMA Block Transfer Interrupt Select bit

1 = Initiates interrupt when half of the data has been moved

0 = Initiates interrupt when all of the data has been moved

bit 11 NULLW: Null Data Peripheral Write Mode Select bit

1 = Null data write to peripheral in addition to RAM write (DIR bit must also be clear)

0 = Normal operation

bit 10-6 Unimplemented: Read as '0'

bit 5-4 AMODE<1:0>: DMA Channel Addressing Mode Select bits

11 = Reserved

10 = Peripheral Indirect Addressing mode

01 = Register Indirect without Post-Increment mode

00 = Register Indirect with Post-Increment mode

bit 3-2 **Unimplemented:** Read as '0'

bit 1-0 MODE<1:0>: DMA Channel Operating Mode Select bits

11 = One-Shot, Ping-Pong modes are enabled (one block transfer from/to each DMA buffer)

10 = Continuous, Ping-Pong modes are enabled

01 = One-Shot, Ping-Pong modes are disabled

00 = Continuous, Ping-Pong modes are disabled

# REGISTER 8-3: DMAXSTAH: DMA CHANNEL x START ADDRESS REGISTER A (HIGH)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |  |

|-------|------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|--|

|       | STA<23:16> |       |       |       |       |       |       |  |  |  |  |  |  |

| bit 7 |            |       |       |       |       |       | bit 0 |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | STA<  | 15:8> |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | STA<  | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **STA<15:0>:** Primary Start Address bits (source or destination)

## REGISTER 8-5: DMAXSTBH: DMA CHANNEL x START ADDRESS REGISTER B (HIGH)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | STB<  | 23:16> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **STB<23:16>:** Secondary Start Address bits (source or destination)

# REGISTER 8-6: DMAXSTBL: DMA CHANNEL x START ADDRESS REGISTER B (LOW)

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | STB<  | 15:8> |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | STB   | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

# REGISTER 8-7: DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | PAD<  | :15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | PAD•  | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

# REGISTER 8-8: DMAXCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|----------------------|-------|-------|

| _      | _   |       |       | CNT<  | 13:8> <sup>(2)</sup> |       |       |

| bit 15 |     |       |       |       |                      |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------------------|-------|-------|-------|

|       |       |       | CNT<  | 7:0> <sup>(2)</sup> |       |       |       |

| bit 7 |       |       |       |                     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: The number of DMA transfers = CNT<13:0> + 1.

#### REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R-0    | R-0    | R-0    | R-0    |

|-------|-----|-----|-----|--------|--------|--------|--------|

| _     | _   | _   | _   | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0 |

| bit 7 |     |     |     |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as '0'

bit 3 PWCOL3: DMA Channel 3 Peripheral Write Collision Flag bit

1 = Write collision is detected0 = No write collision is detected

bit 2 PWCOL2: DMA Channel 2 Peripheral Write Collision Flag bit

1 = Write collision is detected0 = No write collision is detected

bit 1 PWCOL1: DMA Channel 1 Peripheral Write Collision Flag bit

1 = Write collision is detected0 = No write collision is detected

bit 0 PWCOL0: DMA Channel 0 Peripheral Write Collision Flag bit

1 = Write collision is detected0 = No write collision is detected

#### **TIMER2/3 AND TIMER4/5** 13.0

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

> 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- · Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- · Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- · Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- · ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

For 32-bit operation, T3CON and T5CON

control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

#### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLTEN7 | FLTEN6 | FLTEN5 | FLTEN4 | FLTEN3 | FLTEN2 | FLTEN1 | FLTEN0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

x = Bit is unknown-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 15-0 FLTEN<15:0>: Enable Filter n to Accept Messages bits

> 1 = Enables Filter n 0 = Disables Filter n

#### REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0  | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-----------|-------|-------|-------|-------|

|        | F3BP< | <3:0> | F2BP<3:0> |       |       |       |       |

| bit 15 |       |       |           |       |       |       | bit 8 |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| F1BP<3:0> |       |       |       |       | F0BP  | <3:0> |       |

| bit 7     |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n = Value at POR x = Bit is unknown

bit 15-12 F3BP<3:0>: RX Buffer Mask for Filter 3 bits

1111 = Filter hits received in RX FIFO buffer

1110 = Filter hits received in RX Buffer 14

0001 = Filter hits received in RX Buffer 1 0000 = Filter hits received in RX Buffer 0

F2BP<3:0>: RX Buffer Mask for Filter 2 bits (same values as bits<15:12>)

bit 11-8 bit 7-4 F1BP<3:0>: RX Buffer Mask for Filter 1 bits (same values as bits<15:12>)

bit 3-0 F0BP<3:0>: RX Buffer Mask for Filter 0 bits (same values as bits<15:12>)

#### REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

**Legend:** C = Writable bit, but only '0' can be written to clear the bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **RXOVF<15:0>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxrXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

**Legend:** C = Writable bit, but only '0' can be written to clear the bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## bit 15-0 **RXOVF<31:16>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### 30.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>    | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\geq 3.0V^{(3)}$     | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to +3.6V        |

| Maximum current out of Vss pin                                                    | 300 mA               |

| Maximum current into VDD pin <sup>(2)</sup>                                       | 300 mA               |

| Maximum current sunk/sourced by any 4x I/O pin                                    | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                    | 25 mA                |

| Maximum current sunk by all ports <sup>(2,4)</sup>                                | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- **4:** Exceptions are: dsPIC33EPXXXGP502, dsPIC33EPXXXMC202/502 and PIC24EPXXXGP/MC202 devices, which have a maximum sink/source capability of 130 mA.

# 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X AC characteristics and timing parameters.

TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V                  |  |  |  |  |

|--------------------|--------------------------------------------------------------|--|--|--|--|

|                    | (unless otherwise stated)                                    |  |  |  |  |

| AC CHARACTERISTICS | Operating temperature -40°C ≤ Ta ≤ +85°C for Industrial      |  |  |  |  |

| AC CHARACTERISTICS | -40°C ≤ Ta ≤ +125°C for Extended                             |  |  |  |  |

|                    | Operating voltage VDD range as described in Section 30.1 "DC |  |  |  |  |

|                    | Characteristics".                                            |  |  |  |  |

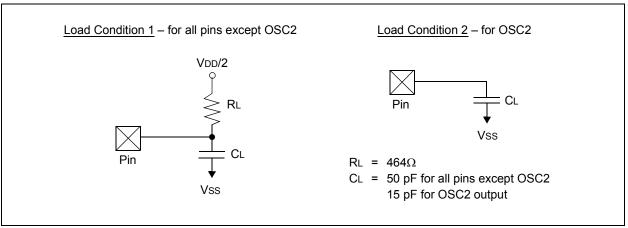

#### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                    |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | _    | 15   | pF    | In XT and HS modes, when external clock is used to drive OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | _    | _    | 50   | pF    | EC mode                                                       |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                     |

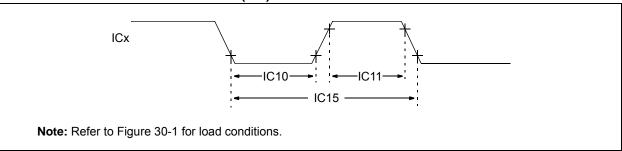

# FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | STICS                          | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |       |                                  |                                  |  |

|--------------------|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|----------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                             | Max. | Units | Conditions                       |                                  |  |

| IC10               | TccL   | ICx Input Low Time             | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                   | _    | ns    | Must also meet<br>Parameter IC15 |                                  |  |

| IC11               | TccH   | ICx Input High Time            | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                   | _    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |  |

| IC15               | TccP   | ICx Input Period               | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50                                                                                                                                                                                                    | _    | ns    |                                  |                                  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

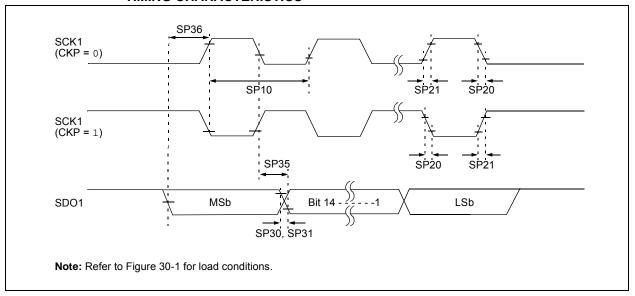

FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHA | AC CHARACTERISTICS    |                                           |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |       |                             |  |

|--------|-----------------------|-------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>             | Min. | Typ. <sup>(2)</sup>                                                                                                                                                                                                                              | Max. | Units | Conditions                  |  |

| SP10   | FscP                  | Maximum SCK1 Frequency                    | _    | _                                                                                                                                                                                                                                                | 15   | MHz   | (Note 3)                    |  |

| SP20   | TscF                  | SCK1 Output Fall Time                     | _    | _                                                                                                                                                                                                                                                | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP21   | TscR                  | SCK1 Output Rise Time                     | _    | _                                                                                                                                                                                                                                                | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                | _    |                                                                                                                                                                                                                                                  | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                | _    | _                                                                                                                                                                                                                                                | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after SCK1 Edge    | _    | 6                                                                                                                                                                                                                                                | 20   | ns    |                             |  |

| SP36   | TdiV2scH,<br>TdiV2scL | SDO1 Data Output Setup to First SCK1 Edge | 30   | _                                                                                                                                                                                                                                                | _    | ns    |                             |  |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 3: The minimum clock period for SCK1 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

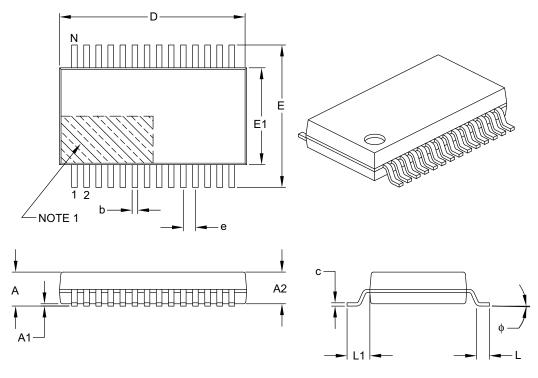

# 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     | MILLIMETERS |          |       |  |

|--------------------------|-----------|-------------|----------|-------|--|

| Dimension                | on Limits | MIN         | NOM      | MAX   |  |

| Number of Pins           | N         |             | 28       |       |  |

| Pitch                    | е         |             | 0.65 BSC |       |  |

| Overall Height           | Α         | _           | -        | 2.00  |  |

| Molded Package Thickness | A2        | 1.65        | 1.75     | 1.85  |  |

| Standoff                 | A1        | 0.05        | -        | _     |  |

| Overall Width            | E         | 7.40        | 7.80     | 8.20  |  |

| Molded Package Width     | E1        | 5.00        | 5.30     | 5.60  |  |

| Overall Length           | D         | 9.90        | 10.20    | 10.50 |  |

| Foot Length              | L         | 0.55        | 0.75     | 0.95  |  |

| Footprint                | L1        |             | 1.25 REF |       |  |

| Lead Thickness           | С         | 0.09        | _        | 0.25  |  |

| Foot Angle               | ф         | 0°          | 4°       | 8°    |  |

| Lead Width               | b         | 0.22        | _        | 0.38  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

| dsPIC33EPXXXGP50 | X, dsPIC33EPXXXMC | 20X/50X AND PIC2 | 4EPXXXGP/MC20X |  |

|------------------|-------------------|------------------|----------------|--|

| NOTES:           |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |

|                  |                   |                  |                |  |