Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

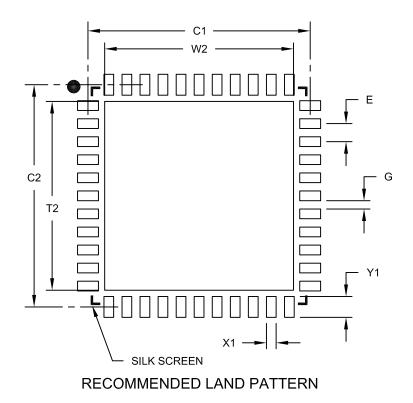

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc506-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

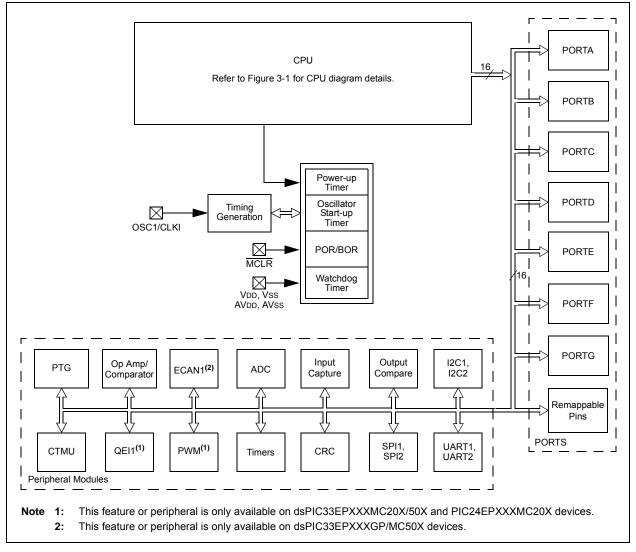

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X BLOCK DIAGRAM

#### TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | _      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | _      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | —      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

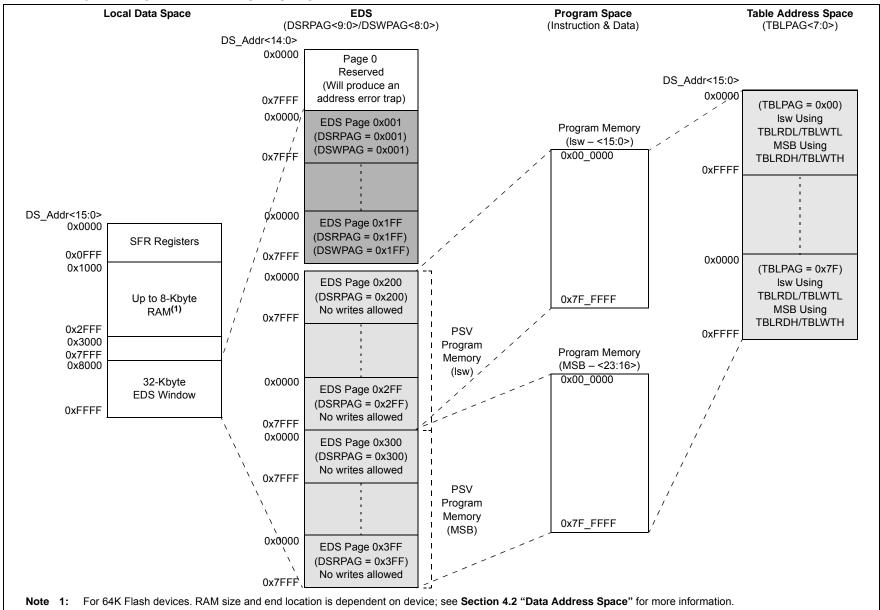

#### EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                                  | U-0                                                                                                                        | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |  |  |  |  |  |  |

|---------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|--|--|--|--|--|--|

| TRAPF         | R IOPUWR                               | —                                                                                                                          | _             | VREGSF                | —                 | CM               | VREGS         |  |  |  |  |  |  |

| bit 15        |                                        |                                                                                                                            |               |                       |                   |                  | bit 8         |  |  |  |  |  |  |

|               |                                        | DANIO                                                                                                                      | DAMO          | DAMA                  | DAMO              |                  |               |  |  |  |  |  |  |

| R/W-0         |                                        | R/W-0                                                                                                                      | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |  |  |  |  |  |  |

| EXTR<br>bit 7 | SWR                                    | SWDTEN <sup>(2)</sup>                                                                                                      | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |  |  |  |  |  |  |

|               |                                        |                                                                                                                            |               |                       |                   |                  | bit (         |  |  |  |  |  |  |

| Legend:       |                                        |                                                                                                                            |               |                       |                   |                  |               |  |  |  |  |  |  |

| R = Reada     | able bit                               | W = Writable I                                                                                                             | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |  |  |  |  |  |  |

| -n = Value    | at POR                                 | '1' = Bit is set                                                                                                           |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |  |  |  |  |  |  |

|               |                                        |                                                                                                                            |               |                       |                   |                  |               |  |  |  |  |  |  |

| bit 15        | •                                      | TRAPR: Trap Reset Flag bit                                                                                                 |               |                       |                   |                  |               |  |  |  |  |  |  |

|               |                                        | <ol> <li>A Trap Conflict Reset has occurred</li> <li>A Trap Conflict Reset has not occurred</li> </ol>                     |               |                       |                   |                  |               |  |  |  |  |  |  |

| bit 14        | •                                      | 0 = A Trap Conflict Reset has not occurred<br>IOPUWR: Illegal Opcode or Uninitialized W Access Reset Flag bit              |               |                       |                   |                  |               |  |  |  |  |  |  |

|               |                                        | 1 = An illegal opcode detection, an illegal address mode or Uninitialized W register used as ar                            |               |                       |                   |                  |               |  |  |  |  |  |  |

|               |                                        | Pointer caused                                                                                                             |               |                       |                   |                  |               |  |  |  |  |  |  |

|               | -                                      | l opcode or Uni                                                                                                            |               | egister Reset h       | as not occurred   | d                |               |  |  |  |  |  |  |

| bit 13-12     | -                                      | ted: Read as '                                                                                                             |               |                       | . 1.9             |                  |               |  |  |  |  |  |  |

| bit 11        |                                        | VREGSF: Flash Voltage Regulator Standby During Sleep bit<br>1 = Flash voltage regulator is active during Sleep             |               |                       |                   |                  |               |  |  |  |  |  |  |

|               |                                        | ltage regulator (                                                                                                          |               | •                     | ing Sleep         |                  |               |  |  |  |  |  |  |

| bit 10        |                                        | ted: Read as '                                                                                                             | -             | ,,                    | 5                 |                  |               |  |  |  |  |  |  |

| bit 9         | CM: Configur                           | CM: Configuration Mismatch Flag bit                                                                                        |               |                       |                   |                  |               |  |  |  |  |  |  |

|               | 1 = A Configu                          | uration Mismatc<br>uration Mismatc                                                                                         | h Reset has   |                       |                   |                  |               |  |  |  |  |  |  |

| bit 8         | VREGS: Volta                           | age Regulator S                                                                                                            | Standby Durir | ng Sleep bit          |                   |                  |               |  |  |  |  |  |  |

|               | •                                      | egulator is active<br>egulator goes in                                                                                     | •             | •                     | еер               |                  |               |  |  |  |  |  |  |

| bit 7         | EXTR: Extern                           | <ul> <li>0 = Voltage regulator goes into Standby mode during Sleep</li> <li>EXTR: External Reset (MCLR) Pin bit</li> </ul> |               |                       |                   |                  |               |  |  |  |  |  |  |

|               |                                        | Clear (pin) Res<br>Clear (pin) Res                                                                                         |               |                       |                   |                  |               |  |  |  |  |  |  |

| bit 6         | SWR: Softwa                            | re RESET (Instr                                                                                                            | uction) Flag  | bit                   |                   |                  |               |  |  |  |  |  |  |

|               |                                        | instruction has instruction has                                                                                            |               |                       |                   |                  |               |  |  |  |  |  |  |

| bit 5         | SWDTEN: So                             | oftware Enable/                                                                                                            | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |  |  |  |  |  |  |

|               | 1 = WDT is e<br>0 = WDT is di          |                                                                                                                            |               |                       |                   |                  |               |  |  |  |  |  |  |

| bit 4         | WDTO: Watc                             | hdog Timer Tim                                                                                                             | e-out Flag bi | it                    |                   |                  |               |  |  |  |  |  |  |

|               |                                        | e-out has occur<br>e-out has not oc                                                                                        |               |                       |                   |                  |               |  |  |  |  |  |  |

| Note 1:       | All of the Reset sta cause a device Re |                                                                                                                            | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |  |  |  |  |  |  |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir  | onfiguration bit i                                                                                                         | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |  |  |  |  |  |  |

## REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| U-0               | U-0                                                                                          | U-0                                                                                                                                                                     | U-0                                                                             | R-0               | R-0              | R-0                | R-0     |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------|------------------|--------------------|---------|--|--|--|--|--|

|                   | —                                                                                            |                                                                                                                                                                         |                                                                                 | ILR3              | ILR2             | ILR1               | ILR0    |  |  |  |  |  |

| bit 15            |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                    | bit 8   |  |  |  |  |  |

| R-0               | R-0                                                                                          | R-0                                                                                                                                                                     | R-0                                                                             | R-0               | R-0              | R-0                | R-0     |  |  |  |  |  |

| VECNUM7           | VECNUM6                                                                                      | VECNUM5                                                                                                                                                                 | VECNUM4                                                                         | VECNUM3           | VECNUM2          | VECNUM1            | VECNUM0 |  |  |  |  |  |

| bit 7             |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                    | bit C   |  |  |  |  |  |

| Legend:           |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                    |         |  |  |  |  |  |

| R = Readable      | bit                                                                                          | W = Writable                                                                                                                                                            | bit                                                                             | U = Unimplen      | nented bit, read | as '0'             |         |  |  |  |  |  |

| -n = Value at POR |                                                                                              | '1' = Bit is set                                                                                                                                                        |                                                                                 | '0' = Bit is clea | ared             | x = Bit is unknown |         |  |  |  |  |  |

| bit 15-12         | Unimplemen                                                                                   | ted: Read as '                                                                                                                                                          | 0'                                                                              |                   |                  |                    |         |  |  |  |  |  |

| bit 11-8          | ILR<3:0>: New CPU Interrupt Priority Level bits                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                    |         |  |  |  |  |  |

|                   | 1111 = CPU Interrupt Priority Level is 15                                                    |                                                                                                                                                                         |                                                                                 |                   |                  |                    |         |  |  |  |  |  |

|                   |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                    |         |  |  |  |  |  |

|                   | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                    |         |  |  |  |  |  |

|                   | 0001 = CPU Interrupt Priority Level is 1<br>0000 = CPU Interrupt Priority Level is 0         |                                                                                                                                                                         |                                                                                 |                   |                  |                    |         |  |  |  |  |  |

| bit 7-0           | VECNUM<7:0>: Vector Number of Pending Interrupt bits                                         |                                                                                                                                                                         |                                                                                 |                   |                  |                    |         |  |  |  |  |  |

|                   | 11111111 = 255, Reserved; do not use                                                         |                                                                                                                                                                         |                                                                                 |                   |                  |                    |         |  |  |  |  |  |

|                   | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                    |         |  |  |  |  |  |

|                   | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                    |         |  |  |  |  |  |

|                   | 00001000 = 8<br>00000111 = 7<br>00000110 = 8<br>00000101 = 8<br>00000100 = 7<br>00000011 = 3 | 9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d<br>6, Generic soft<br>5, DMAC error<br>4, Math error tr<br>3, Stack error t<br>2, Generic hard<br>1, Address erro | rnal Interrupt C<br>o not use<br>error trap<br>trap<br>rap<br>d trap<br>or trap | )                 |                  |                    |         |  |  |  |  |  |

#### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

#### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

#### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

#### 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

#### **11.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Change Noti-      |

|-------|----------------------------------------------|

|       | fication pins should always be disabled      |

|       | when the port pin is configured as a digital |

|       | output.                                      |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, WO | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

#### 11.7 **Peripheral Pin Select Registers**

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | _     | _     | —     |

| bit 7  |       | •     |       | •          |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC2R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| ·                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 8                                                                                                                                                                                                                                                                                                                                                                                               |  |

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC1R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit C                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| e bit                        | W = Writable b                                                                                                                                                         | it                                                                                                                                                                                                                                                                                                                                       | U = Unimplem                                                                                                                                                                                             | nented bit, rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| POR                          | '1' = Bit is set                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                        | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| •                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | nbers)                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                              |                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Unimplemer                   | nted: Read as '0                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |