Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Decalis                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc506t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                                     |

|-------------------------------|-------------|----------------|---------|-------------------------------------------------------------------------------------------------|

| C1IN1-                        | I           | Analog         | No      | Op Amp/Comparator 1 Negative Input 1.                                                           |

| C1IN2-                        | I           | Analog         | No      | Comparator 1 Negative Input 2.                                                                  |

| C1IN1+                        | I           | Analog         | No      | Op Amp/Comparator 1 Positive Input 1.                                                           |

| OA1OUT                        | 0           | Analog         | No      | Op Amp 1 output.                                                                                |

| C1OUT                         | 0           | —              | Yes     | Comparator 1 output.                                                                            |

| C2IN1-                        | I           | Analog         | No      | Op Amp/Comparator 2 Negative Input 1.                                                           |

| C2IN2-                        | I           | Analog         | No      | Comparator 2 Negative Input 2.                                                                  |

| C2IN1+                        | I           | Analog         | No      | Op Amp/Comparator 2 Positive Input 1.                                                           |

| OA2OUT                        | 0           | Analog         | No      | Op Amp 2 output.                                                                                |

| C2OUT                         | 0           |                | Yes     | Comparator 2 output.                                                                            |

| C3IN1-                        | I           | Analog         | No      | Op Amp/Comparator 3 Negative Input 1.                                                           |

| C3IN2-                        | I           | Analog         | No      | Comparator 3 Negative Input 2.                                                                  |

| C3IN1+                        | I           | Analog         | No      | Op Amp/Comparator 3 Positive Input 1.                                                           |

| OA3OUT                        | 0           | Analog         | No      | Op Amp 3 output.                                                                                |

| C3OUT                         | 0           |                | Yes     | Comparator 3 output.                                                                            |

| C4IN1-                        | I.          | Analog         | No      | Comparator 4 Negative Input 1.                                                                  |

| C4IN1+                        | I.          | Analog         | No      | Comparator 4 Positive Input 1.                                                                  |

| C4OUT                         | 0           |                | Yes     | Comparator 4 output.                                                                            |

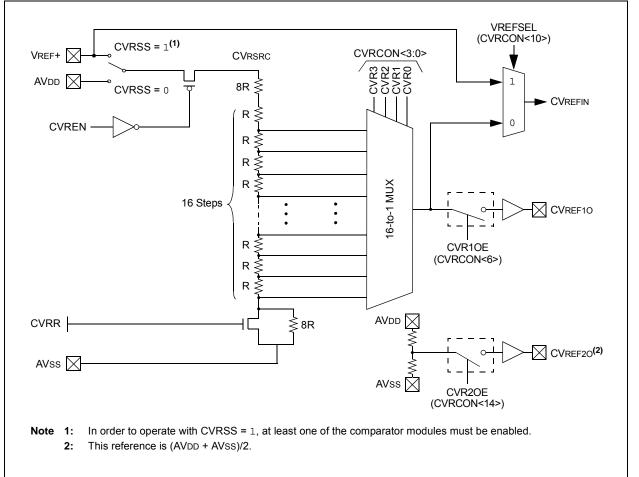

| CVREF10                       | 0           | Analog         | No      | Op amp/comparator voltage reference output.                                                     |

| CVREF20                       | 0           | Analog         | No      | Op amp/comparator voltage reference divided by 2 output.                                        |

| PGED1                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.                                 |

| PGEC1                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1.                              |

| PGED2                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.                                 |

| PGEC2                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2.                              |

| PGED3                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.                                 |

| PGEC3                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 3.                              |

| MCLR                          | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device.                      |

| AVDD                          | Р           | Р              | No      | Positive supply for analog modules. This pin must be connected at all times.                    |

| AVss                          | Р           | Р              | No      | Ground reference for analog modules. This pin must be connected at all times.                   |

| Vdd                           | Р           |                | No      | Positive supply for peripheral logic and I/O pins.                                              |

| VCAP                          | Р           |                | No      | CPU logic filter capacitor connection.                                                          |

| Vss                           | Р           |                | No      | Ground reference for logic and I/O pins.                                                        |

| VREF+                         | 1           | Analog         | No      | Analog voltage reference (high) input.                                                          |

| VREF-                         | Ι           | Analog         | No      | Analog voltage reference (low) input.                                                           |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI | or output     Analog = Analog input     P = Power       MOS levels     O = Output     I = Input |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

## 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

#### 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

# 9.3 Oscillator Control Registers

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0            | R-0                                                                | R-0                                  | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                |

|----------------|--------------------------------------------------------------------|--------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------|

| _              | COSC2                                                              | COSC1                                | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |

| bit 15         |                                                                    |                                      |                                    |                                    |                                    |                      | bit 8                |

| R/W-0          | R/W-0                                                              | R-0                                  | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                |

| CLKLOC         | CK IOLOCK                                                          | LOCK                                 |                                    | CF <sup>(3)</sup>                  |                                    |                      | OSWEN                |

| bit 7          |                                                                    |                                      |                                    |                                    |                                    |                      | bit (                |

| Legend:        |                                                                    | y = Value set                        | from Configur                      | ation bits on F                    | POR                                |                      |                      |

| R = Reada      | able bit                                                           | W = Writable                         | -                                  |                                    | mented bit, read                   | l as '0'             |                      |

| -n = Value     | at POR                                                             | '1' = Bit is se                      | t                                  | '0' = Bit is cle                   | eared                              | x = Bit is unkr      | nown                 |

| hit 1 <i>5</i> | Unimplemen                                                         | ted. Dood oo                         | 0'                                 |                                    |                                    |                      |                      |

| bit 15         | -                                                                  | ted: Read as                         |                                    |                                    |                                    |                      |                      |

| bit 14-12      |                                                                    | Current Oscill                       |                                    |                                    | ()                                 |                      |                      |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F   |                                    |                                    |                                    |                      |                      |

|                |                                                                    | ower RC Oscil                        |                                    |                                    |                                    |                      |                      |

|                | 100 = Reserv                                                       |                                      | ()                                 |                                    |                                    |                      |                      |

|                |                                                                    | y Oscillator (X                      |                                    | h PLL                              |                                    |                      |                      |

|                |                                                                    | y Oscillator (X                      |                                    |                                    |                                    |                      |                      |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F   |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |

| bit 11         |                                                                    | ted: Read as                         | ,                                  |                                    |                                    |                      |                      |

| bit 10-8       | -8 NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup>         |                                      |                                    |                                    |                                    |                      |                      |

|                | 111 = Fast R                                                       | C Oscillator (F                      | RC) with Divid                     | le-by-n                            |                                    |                      |                      |

|                |                                                                    | C Oscillator (F                      |                                    | le-by-16                           |                                    |                      |                      |

|                |                                                                    | ower RC Oscil                        | ator (LPRC)                        |                                    |                                    |                      |                      |

|                | 100 = Reserv                                                       | /ed<br>y Oscillator (X               |                                    |                                    |                                    |                      |                      |

|                |                                                                    | y Oscillator (X                      |                                    | IFLL                               |                                    |                      |                      |

|                |                                                                    | C Oscillator (F                      |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |

|                |                                                                    | C Oscillator (F                      |                                    | ,                                  | ,                                  |                      |                      |

| bit 7          |                                                                    | Clock Lock Ena                       |                                    |                                    |                                    |                      |                      |

|                |                                                                    |                                      |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and       |

|                |                                                                    | figurations may<br>d PLL selectio    |                                    | ked, configurat                    | ions may be mo                     | odified              |                      |

| bit 6          |                                                                    | Lock Enable b                        |                                    | -                                  | -                                  |                      |                      |

|                | 1 = I/O lock is                                                    | s active                             |                                    |                                    |                                    |                      |                      |

|                | 0 = I/O lock is                                                    | s not active                         |                                    |                                    |                                    |                      |                      |

| bit 5          | LOCK: PLL L                                                        | ock Status bit                       | (read-only)                        |                                    |                                    |                      |                      |

|                |                                                                    | s that PLL is in<br>s that PLL is ou |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                      |

| Note 1:        | Writes to this regis                                               |                                      |                                    |                                    |                                    |                      | ʻdsPIC33/            |

| 2:             | Direct clock switch<br>This applies to cloo<br>mode as a transitio | es between ar<br>ck switches in      | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                      |

| 0              | This bit should only                                               |                                      |                                    |                                    |                                    |                      |                      |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

### REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

#### REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      | —     | —     | _     | _          | _     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|        |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          |                                                                                                                                         |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

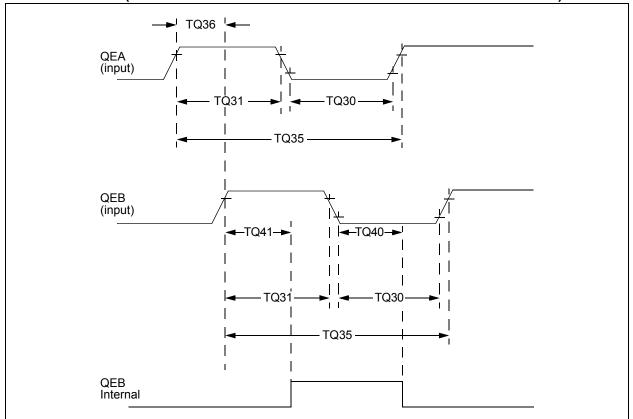

## 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

#### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

# 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

#### 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0                          | U-0                                  | U-0                                                                             | U-0            | U-0          | U-0              | U-0             | U-0   |  |  |  |

|------------------------------|--------------------------------------|---------------------------------------------------------------------------------|----------------|--------------|------------------|-----------------|-------|--|--|--|

| _                            | —                                    | —                                                                               |                | —            | —                | —               | _     |  |  |  |

| bit 15                       |                                      |                                                                                 |                |              |                  |                 | bit   |  |  |  |

|                              |                                      |                                                                                 |                |              |                  |                 |       |  |  |  |

| R/W-0                        | R/W-0                                | R/W-0                                                                           | U-0            | R/W-0        | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| IVRIE                        | WAKIE                                | ERRIE                                                                           | —              | FIFOIE       | RBOVIE           | RBIE            | TBIE  |  |  |  |

| bit 7                        |                                      |                                                                                 |                |              |                  |                 | bit   |  |  |  |

|                              |                                      |                                                                                 |                |              |                  |                 |       |  |  |  |

| <b>Legend:</b><br>R = Readab | la hit                               | W = Writable b                                                                  | .it            |              | montod bit rook  | l oo 'O'        |       |  |  |  |

| n = Value a                  |                                      | '1' = Bit is set                                                                | אנ             | 0 = Onimpler | mented bit, read | x = Bit is unkr |       |  |  |  |

|                              | IL POR                               | I = DILIS SEL                                                                   |                |              | areu             |                 | IOWI  |  |  |  |

| bit 15-8                     | Unimplemen                           | ted: Read as '0                                                                 | ,              |              |                  |                 |       |  |  |  |

| bit 7                        | -                                    |                                                                                 |                | bit          |                  |                 |       |  |  |  |

|                              |                                      | IVRIE: Invalid Message Interrupt Enable bit<br>1 = Interrupt request is enabled |                |              |                  |                 |       |  |  |  |

|                              |                                      | request is not er                                                               |                |              |                  |                 |       |  |  |  |

| bit 6                        | WAKIE: Bus                           | WAKIE: Bus Wake-up Activity Interrupt Enable bit                                |                |              |                  |                 |       |  |  |  |

|                              |                                      | 1 = Interrupt request is enabled                                                |                |              |                  |                 |       |  |  |  |

|                              |                                      | request is not er                                                               |                |              |                  |                 |       |  |  |  |

| bit 5                        |                                      | Interrupt Enabl                                                                 |                |              |                  |                 |       |  |  |  |

|                              |                                      | request is enabl<br>request is not er                                           |                |              |                  |                 |       |  |  |  |

| bit 4                        |                                      | ted: Read as '0                                                                 |                |              |                  |                 |       |  |  |  |

| bit 3                        | -                                    | Almost Full Int                                                                 |                | o hit        |                  |                 |       |  |  |  |

| DIL J                        |                                      |                                                                                 | •              | ebit         |                  |                 |       |  |  |  |

|                              |                                      | 1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled        |                |              |                  |                 |       |  |  |  |

| bit 2                        | <b>RBOVIE:</b> RX                    | Buffer Overflow                                                                 | / Interrupt Er | nable bit    |                  |                 |       |  |  |  |

|                              | 1 = Interrupt                        | 1 = Interrupt request is enabled                                                |                |              |                  |                 |       |  |  |  |

|                              | 0 = Interrupt i                      | request is not er                                                               | nabled         |              |                  |                 |       |  |  |  |

| bit 1                        |                                      | ffer Interrupt En                                                               |                |              |                  |                 |       |  |  |  |

|                              |                                      | equest is enabl                                                                 |                |              |                  |                 |       |  |  |  |

|                              |                                      | equiest is not er                                                               | nabled         |              |                  |                 |       |  |  |  |

|                              | 0 = Interrupt request is not enabled |                                                                                 |                |              |                  |                 |       |  |  |  |

| bit 0                        | TBIE: TX Buf                         | fer Interrupt Ena<br>request is enabl                                           | able bit       |              |                  |                 |       |  |  |  |

#### REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER

| U-0          | R/W-x                                                                | U-0                           | U-0              | U-0              | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

|--------------|----------------------------------------------------------------------|-------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| —            | WAKFIL                                                               |                               | —                |                  | SEG2PH2          | SEG2PH1         | SEG2PH0 |  |  |  |  |

| bit 15       |                                                                      |                               |                  |                  |                  |                 | bit     |  |  |  |  |

|              |                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

| R/W-x        | R/W-x                                                                | R/W-x                         | R/W-x            | R/W-x            | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

| SEG2PHTS     | S SAM                                                                | SEG1PH2                       | SEG1PH1          | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |  |  |  |  |

| bit 7        |                                                                      |                               |                  |                  |                  |                 | bit     |  |  |  |  |

| Legend:      |                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

| R = Readab   | le bit                                                               | W = Writable                  | bit              | U = Unimpler     | nented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value a |                                                                      | '1' = Bit is set              |                  | '0' = Bit is cle |                  | x = Bit is unkr | nown    |  |  |  |  |

|              |                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

| bit 15       | Unimplemen                                                           | nted: Read as '               | 0'               |                  |                  |                 |         |  |  |  |  |

| bit 14       | WAKFIL: Sel                                                          | lect CAN Bus L                | ine Filter for V | Vake-up bit      |                  |                 |         |  |  |  |  |

|              |                                                                      | N bus line filter             |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                      | line filter is not            |                  | e-up             |                  |                 |         |  |  |  |  |

| bit 13-11    | -                                                                    | nted: Read as '               |                  |                  |                  |                 |         |  |  |  |  |

| bit 10-8     | SEG2PH<2:0>: Phase Segment 2 bits                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 111 = Length is 8 x TQ                                               |                               |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 000 = Length                                                         | n is 1 x To                   |                  |                  |                  |                 |         |  |  |  |  |

| bit 7        | -                                                                    |                               | nt 2 Time Sele   | ct bit           |                  |                 |         |  |  |  |  |

|              | SEG2PHTS: Phase Segment 2 Time Select bit<br>1 = Freely programmable |                               |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                      | n of SEG1PHx I                | bits or Informa  | tion Processin   | g Time (IPT), w  | hichever is gre | ater    |  |  |  |  |

| bit 6        | SAM: Sample of the CAN Bus Line bit                                  |                               |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                      | s sampled threes sampled once |                  |                  |                  |                 |         |  |  |  |  |

| bit 5-3      | SEG1PH<2:0                                                           | <b>0&gt;:</b> Phase Segr      | nent 1 bits      |                  |                  |                 |         |  |  |  |  |

|              | 111 = Length is 8 x Tq                                               |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    | •                             |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 000 = Length                                                         |                               |                  |                  |                  |                 |         |  |  |  |  |

| bit 2-0      |                                                                      | >: Propagation                | Time Segmen      | t bits           |                  |                 |         |  |  |  |  |

|              | 111 = Length                                                         | IIS8XIQ                       |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

## REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

## REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |                                         |       |                                    |       |        |       |

|------------------------------------|-------|-----------------------------------------|-------|------------------------------------|-------|--------|-------|

|                                    | R/W-0 | R/W-0                                   | R/W-0 | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |

|                                    | F7BF  | °<3:0>                                  |       |                                    | F6BF  | P<3:0> |       |

| bit 15                             |       |                                         |       |                                    |       |        | bit 8 |

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0 | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |

|                                    | F5BF  | °<3:0>                                  |       |                                    | F4BF  | P<3:0> |       |

| bit 7                              |       |                                         |       |                                    |       |        | bit 0 |

| Legend:                            |       |                                         |       |                                    |       |        |       |

| R = Readable bi                    | t     | W = Writable                            | bit   | U = Unimplemented bit, read as '0' |       |        |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknowr |       | nown                               |       |        |       |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0   | R/W-0 |  |

|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|----------------|---------|-------|--|

|               | F11BP<3:0>                                         |                                                                                               |                                                |                                         | F10B           | SP<3:0> |       |  |

| bit 15        |                                                    |                                                                                               |                                                |                                         |                |         | bit 8 |  |

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0   | R/W-0 |  |

|               | F9BP<3:0>                                          |                                                                                               |                                                |                                         | F8B            | P<3:0>  |       |  |

| bit 7         |                                                    |                                                                                               |                                                |                                         |                |         | bit 0 |  |

| Legend:       |                                                    |                                                                                               |                                                |                                         |                |         |       |  |

| R = Readabl   | le bit                                             | W = Writable                                                                                  | bit                                            | U = Unimplemented bit, read as '0'      |                |         |       |  |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                              |                                                | '0' = Bit is cleared x = Bit is unknown |                |         | nown  |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | RX Buffer Mar<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer<br>4                              |                |         |       |  |

| bit 11-8      | F10BP<3:0>                                         | : RX Buffer Ma                                                                                | sk for Filter 1                                | 0 bits (same val                        | ues as bits<1  | 5:12>)  |       |  |

| bit 7-4       | F9BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 9 b                               | oits (same value                        | s as bits<15:1 | 2>)     |       |  |

| bit 3-0       | F8BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 8 k                               | oits (same value                        | s as bits<15:1 | 2>)     |       |  |

|               |                                                    |                                                                                               |                                                |                                         |                |         |       |  |

© 2011-2013 Microchip Technology Inc.

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                        | R/W-0                                                                                                               | R/W-0                                                                                                                                           | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                     | R/W-0                        | R/W-0  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------|--------|

| F15MSK<1:0>                                  |                                                                                                                     | F14MS                                                                                                                                           | F14MSK<1:0>                                                                                                                                          |                                                                                                                           | SK<1:0>                                                                   | F12MS                        | K<1:0> |

| bit 15                                       |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              | bit 8  |

| R/W-0                                        | R/W-0                                                                                                               | R/W-0                                                                                                                                           | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                     | R/W-0                        | R/W-0  |

|                                              | 1SK<1:0>                                                                                                            | F10MS                                                                                                                                           |                                                                                                                                                      |                                                                                                                           | K<1:0>                                                                    |                              | K<1:0> |

| bit 7                                        |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              | bit C  |

|                                              |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| Legend:                                      |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| R = Readabl                                  | le bit                                                                                                              | W = Writable                                                                                                                                    | bit                                                                                                                                                  | U = Unimplem                                                                                                              | nented bit, read                                                          | l as '0'                     |        |

| -n = Value at                                | t POR                                                                                                               | '1' = Bit is set                                                                                                                                |                                                                                                                                                      | '0' = Bit is cleared x                                                                                                    |                                                                           | x = Bit is unkr              | nown   |

|                                              |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

|                                              |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| bit 15-14                                    | F15MSK<1:                                                                                                           | 0>: Mask Sourc                                                                                                                                  | e for Filter 15                                                                                                                                      | bits                                                                                                                      |                                                                           |                              |        |

| bit 15-14                                    | 11 = Reserv                                                                                                         | ed                                                                                                                                              |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| bit 15-14                                    | 11 = Reserv<br>10 = Accepta                                                                                         | ed<br>ance Mask 2 reg                                                                                                                           | gisters contair                                                                                                                                      | n mask                                                                                                                    |                                                                           |                              |        |

| bit 15-14                                    | 11 = Reserv<br>10 = Accepta<br>01 = Accepta                                                                         | ed                                                                                                                                              | gisters contair<br>gisters contair                                                                                                                   | n mask<br>n mask                                                                                                          |                                                                           |                              |        |

| bit 15-14<br>bit 13-12                       | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                         | ed<br>ance Mask 2 reg<br>ance Mask 1 reg                                                                                                        | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                | ies as bits<15∷                                                           | 14>)                         |        |

|                                              | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:                                            | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                                                     | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14                                                          | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu                                                                   |                                                                           |                              |        |

| bit 13-12                                    | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0                             | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc                                                         | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu                                                          | les as bits<15∷                                                           | 14>)                         |        |

| bit 13-12<br>bit 11-10                       | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:                  | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc                             | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu                                       | ies as bits<15:<br>ies as bits<15:                                        | 14>)<br>14>)                 |        |