Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp502-h-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

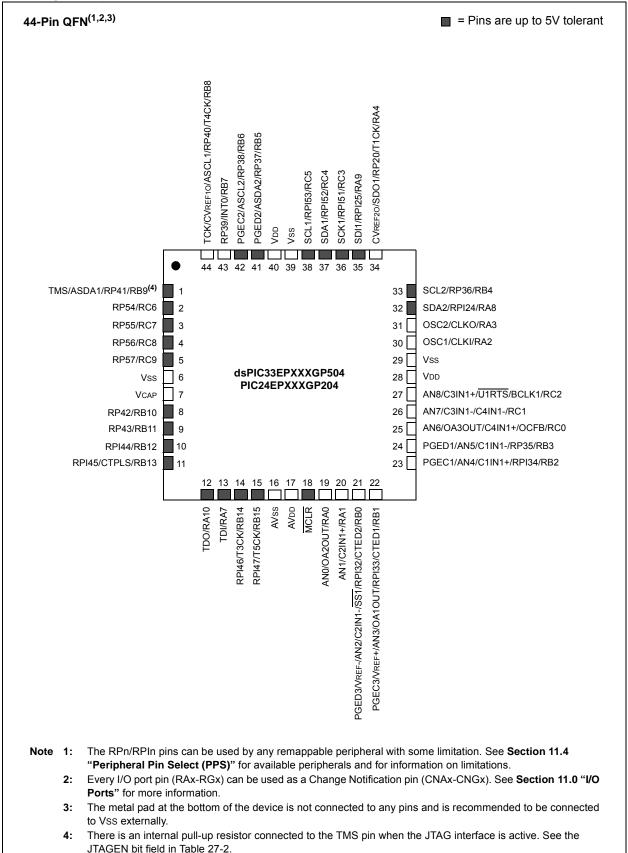

## **Pin Diagrams (Continued)**

| R/W-0                 | R/W-0                                                                  | R/W-0                                                | R/W-0                                         | R/W-0                              | U-0              | U-0             | U-0            |  |

|-----------------------|------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------|------------------------------------|------------------|-----------------|----------------|--|

| CHEN                  | SIZE                                                                   | DIR                                                  | HALF                                          | NULLW                              |                  |                 |                |  |

| bit 15                |                                                                        |                                                      |                                               |                                    |                  |                 | bit            |  |

| U-0                   | U-0                                                                    | R/W-0                                                | R/W-0                                         | U-0                                | U-0              | R/W-0           | R/W-0          |  |

|                       | 0-0                                                                    | AMODE1                                               | AMODE0                                        | 0-0                                | 0-0              | MODE1           | MODE0          |  |

| bit 7                 |                                                                        | AWODET                                               | 7 WIODE0                                      |                                    |                  | MODET           | bit            |  |

| Lovende               |                                                                        |                                                      |                                               |                                    |                  |                 |                |  |

| Legend:<br>R = Readab | lo hit                                                                 | M - Mritabla                                         | hit.                                          |                                    | monted bit rec   | ud aa '0'       |                |  |

|                       |                                                                        | W = Writable                                         |                                               | -                                  | mented bit, rea  |                 |                |  |

| -n = Value a          | IT POR                                                                 | '1' = Bit is set                                     |                                               | '0' = Bit is cle                   | ared             | x = Bit is unkr | Bit is unknown |  |

| bit 15                | CHEN: DMA                                                              | Channel Enabl                                        | e bit                                         |                                    |                  |                 |                |  |

|                       | 1 = Channel<br>0 = Channel                                             |                                                      |                                               |                                    |                  |                 |                |  |

| bit 14                |                                                                        | ata Transfer S                                       | ze hit                                        |                                    |                  |                 |                |  |

|                       | 1 = Byte                                                               |                                                      |                                               |                                    |                  |                 |                |  |

|                       | 0 = Word                                                               |                                                      |                                               |                                    |                  |                 |                |  |

| bit 13                | <b>DIR:</b> DMA Transfer Direction bit (source/destination bus select) |                                                      |                                               |                                    |                  |                 |                |  |

|                       |                                                                        | om RAM addre<br>om peripheral a                      |                                               |                                    |                  |                 |                |  |

| bit 12                |                                                                        | Block Transfer                                       |                                               |                                    |                  |                 |                |  |

|                       | 1 = Initiates i                                                        | nterrupt when                                        | half of the data                              | a has been mo                      |                  |                 |                |  |

| bit 11                |                                                                        | Data Periphera                                       |                                               |                                    |                  |                 |                |  |

|                       |                                                                        | write to periph                                      |                                               |                                    | e (DIR bit must  | also be clear)  |                |  |

| bit 10-6              | Unimplemen                                                             | ted: Read as '                                       | 0'                                            |                                    |                  |                 |                |  |

| bit 5-4               | AMODE<1:0                                                              | -: DMA Chann                                         | el Addressing                                 | Mode Select b                      | oits             |                 |                |  |

|                       | 11 = Reserve<br>10 = Periphe<br>01 = Register                          |                                                      | ressing mode<br>ut Post-Increm                | nent mode                          |                  |                 |                |  |

| bit 3-2               | Unimplemen                                                             | ted: Read as '                                       | 0'                                            |                                    |                  |                 |                |  |

| bit 1-0               | -                                                                      | DMA Channel                                          |                                               | de Select bits                     |                  |                 |                |  |

|                       | 11 = One-Sho<br>10 = Continue                                          | ot, Ping-Pong r<br>ous, Ping-Pong<br>ot, Ping-Pong r | nodes are ena<br>modes are e<br>nodes are dis | abled (one bloc<br>nabled<br>abled | ck transfer fror | n/to each DMA t | ouffer)        |  |

## REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

## REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0 | U-0             | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|-----------------|-------|--------------|------------------|--------|-------|

| —              | —   | —               | —     | —            | —                | -      | —     |

| bit 15         |     |                 |       |              |                  |        | bit 8 |

|                |     |                 |       |              |                  |        |       |

| R-0            | R-0 | R-0             | R-0   | R-0          | R-0              | R-0    | R-0   |

|                |     |                 | DSADR | <23:16>      |                  |        |       |

| bit 7          |     |                 |       |              |                  |        | bit 0 |

|                |     |                 |       |              |                  |        |       |

| Legend:        |     |                 |       |              |                  |        |       |

| R = Readable b | it  | W = Writable bi | t     | U = Unimpler | nented bit, read | as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0              | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0             | R-0   |

|------------------|-----|------------------|------|----------------------|-------------|-----------------|-------|

|                  |     |                  | DSAD | DR<15:8>             |             |                 |       |

| bit 15           |     |                  |      |                      |             |                 | bit 8 |

|                  |     |                  |      |                      |             |                 |       |

| R-0              | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0             | R-0   |

|                  |     |                  | DSA  | DR<7:0>              |             |                 |       |

| bit 7            |     |                  |      |                      |             |                 | bit 0 |

|                  |     |                  |      |                      |             |                 |       |

| Legend:          |     |                  |      |                      |             |                 |       |

| R = Readable b   | it  | W = Writable bit |      | U = Unimplemen       | ted bit, re | ad as '0'       |       |

| -n = Value at PC | OR  | '1' = Bit is set |      | '0' = Bit is cleared | d           | x = Bit is unkn | own   |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

| U-0                                                                                                       | U-0                                                                                             | U-0               | U-0           | U-0                                     | U-0              | U-0    | U-0    |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------|---------------|-----------------------------------------|------------------|--------|--------|

| —                                                                                                         | —                                                                                               | —                 | —             | —                                       | —                | —      | —      |

| bit 15                                                                                                    |                                                                                                 |                   |               |                                         |                  |        | bit 8  |

|                                                                                                           |                                                                                                 |                   |               |                                         |                  |        |        |

| U-0                                                                                                       | U-0                                                                                             | U-0               | U-0           | R-0                                     | R-0              | R-0    | R-0    |

|                                                                                                           |                                                                                                 | <u> </u>          | _             | PWCOL3                                  | PWCOL2           | PWCOL1 | PWCOL0 |

| bit 7                                                                                                     |                                                                                                 |                   |               |                                         |                  |        | bit 0  |

|                                                                                                           |                                                                                                 |                   |               |                                         |                  |        |        |

| Legend:                                                                                                   |                                                                                                 |                   |               |                                         |                  |        |        |

| R = Readab                                                                                                | le bit                                                                                          | W = Writable      | bit           | U = Unimpler                            | mented bit, read | as '0' |        |

| -n = Value a                                                                                              | t POR                                                                                           | '1' = Bit is set  |               | '0' = Bit is cleared x = Bit is unknown |                  |        | nown   |

|                                                                                                           |                                                                                                 |                   |               |                                         |                  |        |        |

| bit 15-4                                                                                                  | Unimplemen                                                                                      | ted: Read as '    | 0'            |                                         |                  |        |        |

| bit 3                                                                                                     | PWCOL3: DI                                                                                      | MA Channel 3 F    | Peripheral Wi | rite Collision Fla                      | ag bit           |        |        |

|                                                                                                           |                                                                                                 | lision is detecte |               |                                         |                  |        |        |

|                                                                                                           |                                                                                                 | collision is dete |               |                                         |                  |        |        |

| bit 2                                                                                                     |                                                                                                 |                   | •             | rite Collision Fla                      | ag bit           |        |        |

|                                                                                                           | <ul> <li>1 = Write collision is detected</li> <li>0 = No write collision is detected</li> </ul> |                   |               |                                         |                  |        |        |

| bit 1                                                                                                     |                                                                                                 |                   |               |                                         |                  |        |        |

| bit 1 <b>PWCOL1:</b> DMA Channel 1 Peripheral Write Collision Flag bit<br>1 = Write collision is detected |                                                                                                 |                   |               |                                         |                  |        |        |

|                                                                                                           | 0 =  No write collision is detected                                                             |                   |               |                                         |                  |        |        |

| bit 0                                                                                                     | PWCOL0: DI                                                                                      | MA Channel 0 F    | Peripheral Wi | rite Collision Fla                      | ag bit           |        |        |

|                                                                                                           |                                                                                                 | lision is detecte | •             | -                                       | <b>č</b>         |        |        |

|                                                                                                           | 0 = No write                                                                                    | collision is dete | ected         |                                         |                  |        |        |

|                                                                                                           |                                                                                                 |                   |               |                                         |                  |        |        |

## REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

## TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

## 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

## 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

## 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

## 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

## 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

## REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|------------------|----------------------------------------------------------|-------|-------------------|-----------------|-----------------|-------|

|              |                  |                                                          |       | DTCMP3R<6:0       | )>              |                 |       |

| bit 15       |                  |                                                          |       |                   |                 |                 | bit 8 |

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| 0-0          | R/W-0            | R/W-0                                                    | -     | DTCMP2R<6:0       |                 | R/W-0           | R/W-U |

| bit 7        |                  |                                                          |       |                   | 17              |                 | bit 0 |

| bit i        |                  |                                                          |       |                   |                 |                 | bit 0 |

| Legend:      |                  |                                                          |       |                   |                 |                 |       |

| R = Readab   | ole bit          | W = Writable                                             | bit   | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR           | '1' = Bit is set                                         |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |                  |                                                          |       |                   |                 |                 |       |

|              |                  | nput tied to CMI                                         |       |                   |                 |                 |       |

| bit 7        | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |       |                   |                 |                 |       |

| R/W-0              | U-0                  | R/W-0                 | U-0                   | U-0 | U-0 | U-0                  | U-0   |

|--------------------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| TON <sup>(1)</sup> | —                    | TSIDL <sup>(2)</sup>  | —                     | —   | —   | —                    | —     |

| bit 15             |                      |                       |                       |     |     |                      | bit 8 |

|                    |                      |                       |                       |     |     |                      |       |

| U-0                | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

| —                  | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> |     | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7              |                      |                       |                       |     |     |                      | bit 0 |

|                    |                      |                       |                       |     |     |                      |       |

## REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| Legend:      |                        |                                                                               |                                         |                                   |

|--------------|------------------------|-------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|

| R = Readal   | ole bit                | W = Writable bit                                                              | U = Unimplemented bit                   | , read as '0'                     |

| -n = Value a | at POR                 | '1' = Bit is set                                                              | '0' = Bit is cleared                    | x = Bit is unknown                |

| bit 15       | TON: Tin               | nery On bit <sup>(1)</sup>                                                    |                                         |                                   |

|              |                        | s 16-bit Timery<br>s 16-bit Timery                                            |                                         |                                   |

| bit 14       | •                      | mented: Read as '0'                                                           |                                         |                                   |

| bit 13       | -                      | imery Stop in Idle Mode bit <sup>(2</sup>                                     | 2)                                      |                                   |

|              |                        | ontinues module operation winues module operation in Id                       | hen device enters Idle mode<br>lle mode |                                   |

| bit 12-7     | Unimple                | mented: Read as '0'                                                           |                                         |                                   |

| bit 6        | TGATE:                 | Timery Gated Time Accumu                                                      | lation Enable bit <sup>(1)</sup>        |                                   |

|              | When TC<br>This bit is | <u>CS = 1:</u><br>s ignored.                                                  |                                         |                                   |

|              |                        | <u>CS = 0:</u><br>d time accumulation is enab<br>d time accumulation is disab |                                         |                                   |

| bit 5-4      | TCKPS<                 | 1:0>: Timery Input Clock Pre                                                  | escale Select bits <sup>(1)</sup>       |                                   |

|              | 11 <b>= 1:2</b> 5      |                                                                               |                                         |                                   |

|              | 10 = 1:64<br>01 = 1:8  | 1                                                                             |                                         |                                   |

|              | 01 = 1.8               |                                                                               |                                         |                                   |

| bit 3-2      | Unimple                | mented: Read as '0'                                                           |                                         |                                   |

| bit 1        | -                      | nery Clock Source Select bit                                                  | (1,3)                                   |                                   |

|              |                        | nal clock is from pin, TyCK (<br>nal clock (FP)                               | (on the rising edge)                    |                                   |

| bit 0        | Unimple                | mented: Read as '0'                                                           |                                         |                                   |

|              |                        | peration is enabled (T2CON<br>set through TxCON.                              | <3> = 1), these bits have no e          | ffect on Timery operation; all ti |

|              |                        |                                                                               |                                         |                                   |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

## 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0                          | U-0                                                                        | U-0                                                                                                                        | U-0                                                              | U-0                  | U-0                       | R/W-0              | R/W-0   |

|--------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------|---------------------------|--------------------|---------|

| CHPCLKEN                       | —                                                                          | —                                                                                                                          | —                                                                | —                    | —                         | CHOPC              | LK<9:8> |

| bit 15                         |                                                                            |                                                                                                                            |                                                                  |                      |                           |                    | bit 8   |

|                                |                                                                            |                                                                                                                            |                                                                  |                      |                           |                    |         |

| R/W-0                          | R/W-0                                                                      | R/W-0                                                                                                                      | R/W-0                                                            | R/W-0                | R/W-0                     | R/W-0              | R/W-0   |

|                                |                                                                            |                                                                                                                            | CHOPC                                                            | LK<7:0>              |                           |                    |         |

| bit 7                          |                                                                            |                                                                                                                            |                                                                  |                      |                           |                    | bit 0   |

|                                |                                                                            |                                                                                                                            |                                                                  |                      |                           |                    |         |

| Legend:                        |                                                                            |                                                                                                                            |                                                                  |                      |                           |                    |         |

| R = Readable I                 | bit                                                                        | W = Writable                                                                                                               | bit                                                              | U = Unimplei         | mented bit, read          | as '0'             |         |

| -n = Value at P                | OR                                                                         | '1' = Bit is set                                                                                                           |                                                                  | '0' = Bit is cleared |                           | x = Bit is unknown |         |

| bit 15<br>bit 14-10<br>bit 9-0 | 1 = Chop clos<br>0 = Chop clos<br>Unimplemen<br>CHOPCLK<9<br>The frequence | Enable Chop<br>ck generator is<br>ck generator is<br>ted: Read as '<br>9:0>: Chop Clo<br>y of the chop c<br>ncy = (FP/PCL) | enabled<br>disabled<br>0'<br>ck Divider bits<br>lock signal is g | given by the fo      | ollowing expressi<br>+ 1) | on:                |         |

## REGISTER 16-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

## REGISTER 16-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|-------|----------------|-------|-----------------------------------------|-------|-------|-------|--|

|                                    |       |                | MDC   | <15:8>                                  |       |       |       |  |

| bit 15                             |       |                |       |                                         |       |       | bit 8 |  |

|                                    |       |                |       |                                         |       |       |       |  |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |       |                | MD    | C<7:0>                                  |       |       |       |  |

| bit 7                              |       |                |       |                                         |       |       | bit 0 |  |

|                                    |       |                |       |                                         |       |       |       |  |

| Legend:                            |       |                |       |                                         |       |       |       |  |

| R = Readable                       | bit   | W = Writable b | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cleared x = Bit is unknowr |       |       |       |  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

## REGISTER 21-22: CxRXFUL1: ECANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Writable bit, but on | ly '0' can be written to clear t | he bit             |

|-------------------|--------------------------|----------------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit            | , read as '0'      |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared             | x = Bit is unknown |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

## REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only ( | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|------------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit             | U = Unimplemented bit, re-                                     | ad as '0'          |  |  |  |  |

| -n = Value at POR | '1' = Bit is set             | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 **RXFUL<31:16>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

## 23.4 ADC Control Registers

## REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0         | U-0                                | R/W-0                               | R/W-0            | U-0               | R/W-0            | R/W-0                               | R/W-0               |  |  |

|---------------|------------------------------------|-------------------------------------|------------------|-------------------|------------------|-------------------------------------|---------------------|--|--|

| ADON          | —                                  | ADSIDL                              | ADDMABM          |                   | AD12B            | FORM1                               | FORM0               |  |  |

| bit 15        | •                                  |                                     |                  |                   |                  |                                     | bit 8               |  |  |

| R/W-0         | R/W-0                              | R/W-0                               | R/W-0            | R/W-0             | R/W-0            | R/W-0, HC, HS                       | R/C-0. HC. HS       |  |  |

| SSRC2         | SSRC1                              | SSRC0                               | SSRCG            | SIMSAM            | ASAM             | SAMP                                | DONE <sup>(3)</sup> |  |  |

| bit 7         |                                    |                                     |                  |                   |                  |                                     | bit (               |  |  |

| Legend:       |                                    | HC - Hardwar                        | e Clearable bit  | HS - Hardwa       | re Settable bit  | C = Clearable bi                    | +                   |  |  |

| R = Readable  | a hit                              | W = Writable b                      |                  |                   | nented bit, read |                                     | L                   |  |  |

| -n = Value at |                                    | '1' = Bit is set                    | nt -             | '0' = Bit is clea |                  | x = Bit is unknov                   | vp.                 |  |  |

|               | FUR                                | I - DILIS SEL                       |                  |                   | aieu             |                                     |                     |  |  |

| bit 15        | ADON: ADO                          | C1 Operating M                      | ode bit          |                   |                  |                                     |                     |  |  |

|               | 1 = ADC mo<br>0 = ADC is 0         | odule is operatir<br>off            | ng               |                   |                  |                                     |                     |  |  |

| bit 14        | Unimplemented: Read as '0'         |                                     |                  |                   |                  |                                     |                     |  |  |

| bit 13        | ADSIDL: ADC1 Stop in Idle Mode bit |                                     |                  |                   |                  |                                     |                     |  |  |

|               | 1 = Disconti                       | nues module oj                      | peration when o  | device enters     | ldle mode        |                                     |                     |  |  |

|               | 0 = Continu                        | es module oper                      | ation in Idle mo | ode               |                  |                                     |                     |  |  |

| bit 12        |                                    | : DMA Buffer B                      |                  |                   |                  |                                     |                     |  |  |

|               |                                    |                                     |                  |                   |                  | rovides an addre                    | ess to the DM       |  |  |

|               |                                    |                                     |                  |                   |                  | nd-alone buffer<br>des a Scatter/Ga | ther address t      |  |  |

|               |                                    |                                     |                  |                   |                  | size of the DMA b                   |                     |  |  |

| bit 11        |                                    | nted: Read as                       |                  |                   |                  |                                     |                     |  |  |

| bit 10        | AD12B: AD                          | C1 10-Bit or 12                     | -Bit Operation I | Mode bit          |                  |                                     |                     |  |  |

|               |                                    | -channel ADC                        | -                |                   |                  |                                     |                     |  |  |

|               | 0 = 10-bit, 4                      | -channel ADC                        | operation        |                   |                  |                                     |                     |  |  |

| bit 9-8       | FORM<1:0>                          | Data Output I                       | Format bits      |                   |                  |                                     |                     |  |  |

|               | For 10-Bit C                       |                                     |                  |                   |                  |                                     |                     |  |  |

|               |                                    | l fractional (Dou<br>nal (Dou⊤ = dd |                  |                   | 0, where s = .I  | NOT.d<9>)                           |                     |  |  |

|               |                                    | l integer (DOUT                     |                  |                   | where $s = .NC$  | (<9>)                               |                     |  |  |

|               |                                    | r (Dout = 0000                      |                  |                   |                  |                                     |                     |  |  |

|               | For 12-Bit C                       | peration:                           |                  |                   |                  |                                     |                     |  |  |

|               | •                                  | fractional (Dou                     |                  |                   | 0, where s = .I  | NOT.d<11>)                          |                     |  |  |

|               |                                    |                                     |                  |                   |                  |                                     |                     |  |  |

|               |                                    | nal (Dout = dd<br>I integer (Dout   |                  |                   |                  | (<11>)                              |                     |  |  |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 3: Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

## REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage

- 0 = VIN+ input connects to C4IN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits<sup>(1)</sup>

- 11 = VIN- input of comparator connects to OA3/AN6

- 10 = VIN- input of comparator connects to OA2/AN0

- 01 = VIN- input of comparator connects to OA1/AN3

- 00 = VIN- input of comparator connects to C4IN1-

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                            | Description                                 | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------------------------------|---------------------------------------------|---------------|-------------------------------|--------------------------|

| 25                 | DAW                  | DAW    | Wn                                         | Wn = decimal adjust Wn                      | 1             | 1                             | С                        |

| 26                 | DEC                  | DEC    | f                                          | f = f - 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC    | f,WREG                                     | WREG = f – 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC    | Ws,Wd                                      | Wd = Ws - 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 27                 | DEC2                 | DEC2   | f                                          | f = f - 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC2   | f,WREG                                     | WREG = f – 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC2   | Ws,Wd                                      | Wd = Ws - 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 28                 | DISI                 | DISI   | #lit14                                     | Disable Interrupts for k instruction cycles | 1             | 1                             | None                     |

| 29                 | DIV                  | DIV.S  | Wm,Wn                                      | Signed 16/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.SD | Wm,Wn                                      | Signed 32/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.U  | Wm,Wn                                      | Unsigned 16/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.UD | Wm,Wn                                      | Unsigned 32/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

| 30                 | DIVF                 | DIVF   | Wm , Wn <sup>(1)</sup>                     | Signed 16/16-bit Fractional Divide          | 1             | 18                            | N,Z,C,OV                 |

| 31                 | DO                   | DO     | #lit15,Expr <sup>(1)</sup>                 | Do code to PC + Expr, lit15 + 1 times       | 2             | 2                             | None                     |

|                    |                      | DO     | Wn, Expr(1)                                | Do code to PC + Expr, (Wn) + 1 times        | 2             | 2                             | None                     |

| 32                 | ED                   | ED     | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>         | Euclidean Distance (no accumulate)          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 33                 | EDAC                 | EDAC   | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>         | Euclidean Distance                          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 34                 | EXCH                 | EXCH   | Wns,Wnd                                    | Swap Wns with Wnd                           | 1             | 1                             | None                     |

| 35                 | FBCL                 | FBCL   | Ws,Wnd                                     | Find Bit Change from Left (MSb) Side        | 1             | 1                             | С                        |

| 36                 | FF1L                 | FF1L   | Ws,Wnd                                     | Find First One from Left (MSb) Side         | 1             | 1                             | С                        |

| 37                 | FF1R                 | FF1R   | Ws,Wnd                                     | Find First One from Right (LSb) Side        | 1             | 1                             | С                        |

| 38                 | GOTO                 | GOTO   | Expr                                       | Go to address                               | 2             | 4                             | None                     |

|                    |                      | GOTO   | Wn                                         | Go to indirect                              | 1             | 4                             | None                     |

|                    |                      | GOTO.L | Wn                                         | Go to indirect (long address)               | 1             | 4                             | None                     |

| 39                 | INC                  | INC    | f                                          | f = f + 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC    | f,WREG                                     | WREG = f + 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC    | Ws,Wd                                      | Wd = Ws + 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 40                 | INC2                 | INC2   | f                                          | f = f + 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC2   | f,WREG                                     | WREG = f + 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC2   | Ws,Wd                                      | Wd = Ws + 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 41                 | IOR                  | IOR    | f                                          | f = f .IOR. WREG                            | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | f,WREG                                     | WREG = f .IOR. WREG                         | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | #lit10,Wn                                  | Wd = lit10 .IOR. Wd                         | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | Wb,Ws,Wd                                   | Wd = Wb .IOR. Ws                            | 1             | 1                             | N,Z                      |

|                    |                      | IOR    | Wb,#lit5,Wd                                | Wd = Wb .IOR. lit5                          | 1             | 1                             | N,Z                      |

| 42                 | LAC                  | LAC    | Wso,#Slit4,Acc                             | Load Accumulator                            | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 43                 | LNK                  | LNK    | #lit14                                     | Link Frame Pointer                          | 1             | 1                             | SFA                      |

| 44                 | LSR                  | LSR    | f                                          | f = Logical Right Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR    | f,WREG                                     | WREG = Logical Right Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR    | Ws,Wd                                      | Wd = Logical Right Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR    | Wb,Wns,Wnd                                 | Wnd = Logical Right Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | LSR    | Wb,#lit5,Wnd                               | Wnd = Logical Right Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 45                 | MAC                  | MAC    | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd,AWB <sup>(1)</sup> | Multiply and Accumulate                     | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MAC    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>     | Square and Accumulate                       | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

## TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

## 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

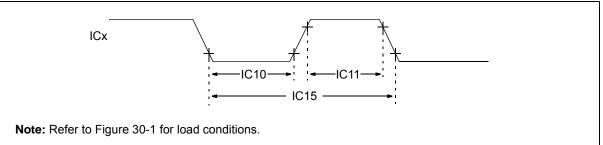

## FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

## TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHA        | RACTERI | STICS                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                  |                                  |  |

|---------------|---------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|----------------------------------|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                  | Max. | Units | Conditions                       |                                  |  |

| IC10          | TccL    | ICx Input Low Time             | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                        |      | ns    | Must also meet<br>Parameter IC15 |                                  |  |

| IC11          | ТссН    | ICx Input High Time            | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                        | —    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |  |

| IC15          | TccP    | ICx Input Period               | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50                                                                                                                                                                                                                                         | _    | ns    | (1, 4, 16)                       |                                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

| AC CHARAG            | CTERISTICS                               |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | it/Receive Transmit/Receive                           |     | СКР | SMP |  |

| 15 MHz               | Table 30-33                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                | _                                        | Table 30-34                                 | —                                                     | 1   | 0,1 | 1   |  |

| 9 MHz                | —                                        | Table 30-35                                 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 30-36                                           | 1   | 0   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 30-37                                           | 1   | 1   | 0   |  |

| 15 MHz               | _                                        | —                                           | Table 30-38                                           | 0   | 1   | 0   |  |

| 11 MHz               | _                                        | —                                           | Table 30-39                                           | 0   | 0   | 0   |  |

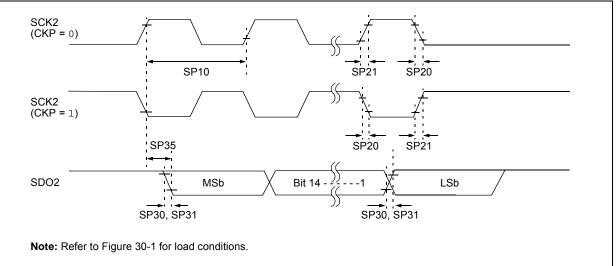

## TABLE 30-33: SPI2 MAXIMUM DATA/CLOCK RATE SUMMARY

## FIGURE 30-14: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

# TABLE 30-37:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |                          |       |                                |  |

|--------------------|-----------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|-------|--------------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max.                     | Units | Conditions                     |  |

| SP70               | FscP                  | Maximum SCK2 Input<br>Frequency                 | -                                                                                                                                                                                                                                                                                       | -                   | Lesser<br>of FP<br>or 15 | MHz   | (Note 3)                       |  |

| SP72               | TscF                  | SCK2 Input Fall Time                            | _                                                                                                                                                                                                                                                                                       | -                   |                          | ns    | See Parameter DO32<br>(Note 4) |  |

| SP73               | TscR                  | SCK2 Input Rise Time                            | —                                                                                                                                                                                                                                                                                       |                     |                          | ns    | See Parameter DO31 (Note 4)    |  |