#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp502-h-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

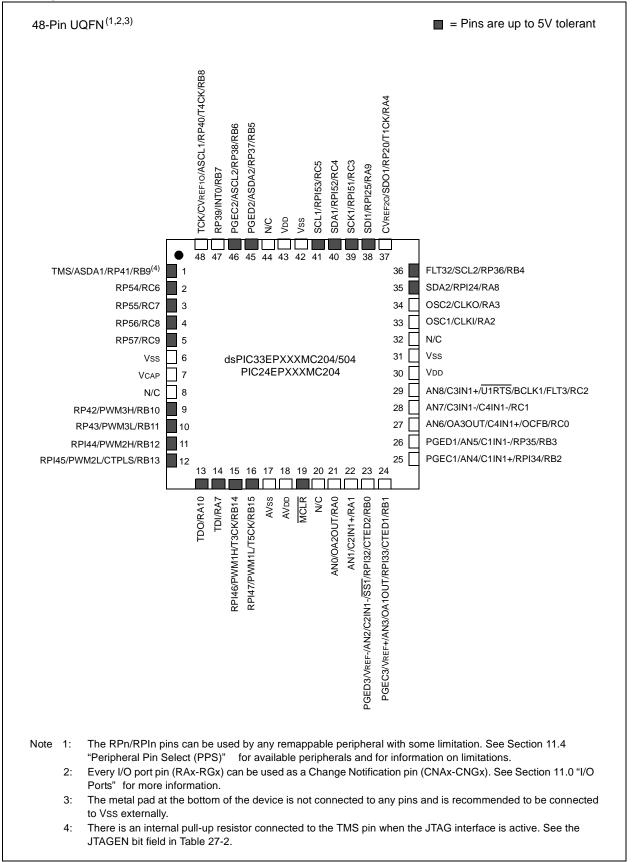

### Pin Diagrams (Continued)

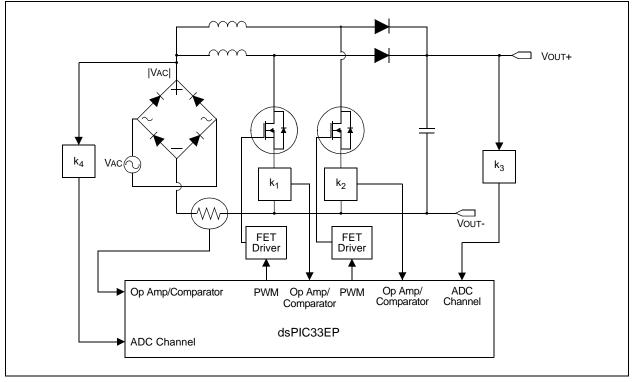

#### FIGURE 2-7: **INTERLEAVED PFC**

Phase Terminal Voltage Feedback

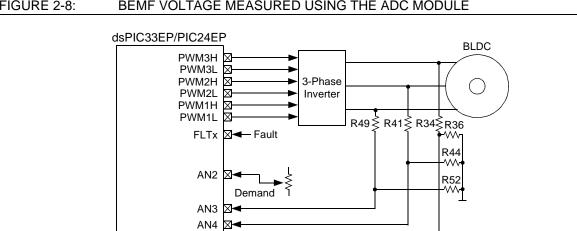

#### FIGURE 2-8: BEMF VOLTAGE MEASURED USING THE ADC MODULE

AN5 🖂

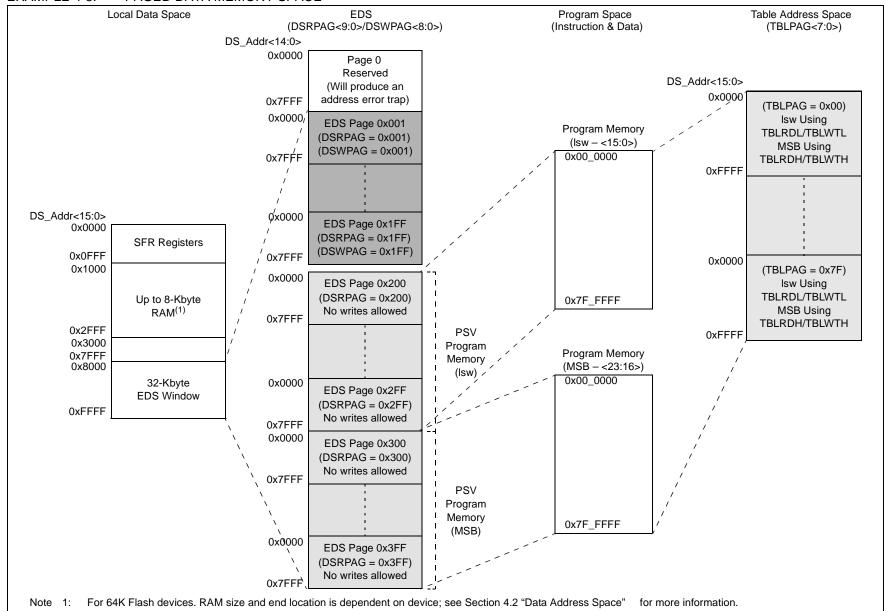

#### EXAMPLE 4-3: PAGED DATA MEMORY SPACE

| R/W-0      | R/W-0                                                                                                                                                      | R/W-0                                                              | R/W-0                  | R/W-0                   | R/W-0                 | R/W-0                | R/W-0                |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------|-------------------------|-----------------------|----------------------|----------------------|--|--|

| NSTDIS     | OVAERR <sup>(1)</sup>                                                                                                                                      | OVBERR <sup>(1)</sup>                                              | COVAERR <sup>(1)</sup> | COVBERR <sup>(1)</sup>  | OVATE <sup>(1)</sup>  | OVBTE <sup>(1)</sup> | COVTE <sup>(1)</sup> |  |  |

| bit 15     |                                                                                                                                                            |                                                                    |                        |                         |                       |                      | bit                  |  |  |

|            |                                                                                                                                                            |                                                                    |                        |                         |                       |                      |                      |  |  |

| R/W-0      | R/W-0                                                                                                                                                      | R/W-0                                                              | R/W-0                  | R/W-0                   | R/W-0                 | R/W-0                | U-0                  |  |  |

| SFTACER    | R <sup>(1)</sup> DIV0ERR                                                                                                                                   | DMACERR                                                            | MATHERR                | ADDRERR                 | STKERR                | OSCFAIL              |                      |  |  |

| bit 7      |                                                                                                                                                            |                                                                    |                        |                         |                       |                      | bit                  |  |  |

| Legend:    |                                                                                                                                                            |                                                                    |                        |                         |                       |                      |                      |  |  |

| R = Reada  | ble bit                                                                                                                                                    | W = Writable                                                       | bit                    | U = Unimpleme           | ented bit, read       | as '0'               |                      |  |  |

| -n = Value | at POR                                                                                                                                                     | '1' = Bit is set                                                   |                        | '0' = Bit is clear      | ed                    | x = Bit is unk       | nown                 |  |  |

| bit 15     |                                                                                                                                                            | torrupt Nonting                                                    | Diachla hit            |                         |                       |                      |                      |  |  |

| bit 15     |                                                                                                                                                            | terrupt Nesting<br>t nesting is disa                               |                        |                         |                       |                      |                      |  |  |

|            |                                                                                                                                                            | t nesting is ena                                                   |                        |                         |                       |                      |                      |  |  |

| bit 14     | OVAERR: A                                                                                                                                                  | Accumulator A C                                                    | Overflow Trap F        | lag bit <sup>(1)</sup>  |                       |                      |                      |  |  |

|            |                                                                                                                                                            | s caused by ov                                                     |                        |                         |                       |                      |                      |  |  |

|            | =                                                                                                                                                          | s not caused by                                                    |                        |                         |                       |                      |                      |  |  |

| bit 13     |                                                                                                                                                            | OVBERR: Accumulator B Overflow Trap Flag bit <sup>(1)</sup>        |                        |                         |                       |                      |                      |  |  |

|            | 1 = Trap was caused by overflow of Accumulator B                                                                                                           |                                                                    |                        |                         |                       |                      |                      |  |  |

| bit 12     | <ul> <li>0 = Trap was not caused by overflow of Accumulator B</li> <li>COVAERR: Accumulator A Catastrophic Overflow Trap Flag bit<sup>(1)</sup></li> </ul> |                                                                    |                        |                         |                       |                      |                      |  |  |

| JIL IZ     | 1 = Trap was caused by catastrophic overflow of Accumulator A                                                                                              |                                                                    |                        |                         |                       |                      |                      |  |  |

|            | 1 = Trap was caused by catastrophic overflow of Accumulator A<br>0 = Trap was not caused by catastrophic overflow of Accumulator A                         |                                                                    |                        |                         |                       |                      |                      |  |  |

| bit 11     | COVBERR:                                                                                                                                                   | Accumulator E                                                      | Catastrophic           | Overflow Trap Fl        | ag bit <sup>(1)</sup> |                      |                      |  |  |

|            |                                                                                                                                                            |                                                                    |                        | flow of Accumula        |                       |                      |                      |  |  |

| bit 10     | OVATE: Acc                                                                                                                                                 | cumulator A Ov                                                     | erflow Trap En         | able bit <sup>(1)</sup> |                       |                      |                      |  |  |

|            | 1 = Trap ove<br>0 = Trap is o                                                                                                                              | erflow of Accum<br>disabled                                        | nulator A              |                         |                       |                      |                      |  |  |

| bit 9      | OVBTE: Ac                                                                                                                                                  | cumulator B Ov                                                     | erflow Trap En         | able bit <sup>(1)</sup> |                       |                      |                      |  |  |

|            |                                                                                                                                                            | erflow of Accum                                                    | nulator B              |                         |                       |                      |                      |  |  |

|            | 0 = Trap is o                                                                                                                                              |                                                                    |                        | (1)                     |                       |                      |                      |  |  |

| bit 8      |                                                                                                                                                            | tastrophic Over                                                    | •                      |                         |                       |                      |                      |  |  |

|            | <ul> <li>1 = Trap on catastrophic overflow of Accumulator A or B is enabled</li> <li>0 = Trap is disabled</li> </ul>                                       |                                                                    |                        |                         |                       |                      |                      |  |  |

| bit 7      | SFTACERR: Shift Accumulator Error Status bit <sup>(1)</sup>                                                                                                |                                                                    |                        |                         |                       |                      |                      |  |  |

|            | 1 = Math error trap was caused by an invalid accumulator shift                                                                                             |                                                                    |                        |                         |                       |                      |                      |  |  |

|            |                                                                                                                                                            | 0 = Math error trap was not caused by an invalid accumulator shift |                        |                         |                       |                      |                      |  |  |

| bit 6      | DIV0ERR: Divide-by-Zero Error Status bit                                                                                                                   |                                                                    |                        |                         |                       |                      |                      |  |  |

|            |                                                                                                                                                            | ror trap was cau<br>ror trap was not                               |                        |                         |                       |                      |                      |  |  |

| bit 5      |                                                                                                                                                            | -                                                                  | -                      |                         |                       |                      |                      |  |  |

|            | DMACERR: DMAC Trap Flag bit<br>1 = DMAC trap has occurred                                                                                                  |                                                                    |                        |                         |                       |                      |                      |  |  |

|            |                                                                                                                                                            | rup nuo oooune                                                     |                        |                         |                       |                      |                      |  |  |

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0          | U-0                                                                                                                         | R/W-0                               | R/W-0 | R/W-0                    | R/W-0           | R/W-0           | R/W-0 |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------|--------------------------|-----------------|-----------------|-------|--|--|

|              | _                                                                                                                           |                                     |       | RP57                     | ′R<5:0>         |                 |       |  |  |

| bit 15       | ·                                                                                                                           |                                     |       |                          |                 |                 | bit 8 |  |  |

|              |                                                                                                                             |                                     | DAMA  | DAMA                     | D M / O         | DAMA            | DAMA  |  |  |

| U-0          | U-0                                                                                                                         | R/W-0                               | R/W-0 | R/W-0                    | R/W-0           | R/W-0           | R/W-0 |  |  |

|              | —                                                                                                                           |                                     |       | RP56                     | R<5:0>          |                 |       |  |  |

| bit 7        |                                                                                                                             |                                     |       |                          |                 |                 | bit 0 |  |  |

|              |                                                                                                                             |                                     |       |                          |                 |                 |       |  |  |

| Legend:      |                                                                                                                             |                                     |       |                          |                 |                 |       |  |  |

| R = Readab   | le bit                                                                                                                      | W = Writable                        | bit   | U = Unimpler             | nented bit, rea | d as '0'        |       |  |  |

| -n = Value a | t POR                                                                                                                       | '1' = Bit is set                    |       | '0' = Bit is cle         | ared            | x = Bit is unkr | nown  |  |  |

| bit 15-14    | Unimplement                                                                                                                 | ed: Read as '                       | 0'    |                          |                 |                 |       |  |  |

| bit 13-8     |                                                                                                                             | : Peripheral Ou<br>-3 for periphera | •     | is Assigned to<br>nbers) | RP57 Output I   | Pin bits        |       |  |  |

| bit 7-6      | Unimplement                                                                                                                 | Unimplemented: Read as '0'          |       |                          |                 |                 |       |  |  |

| bit 5-0      | RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits (see Table 11-3 for peripheral function numbers) |                                     |       |                          |                 |                 |       |  |  |

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   |     |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP97R<5:0>: Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

### 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70330) in the "*dsPIC33/ PIC24 Family Reference Manual*', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

- 3: There are minimum bit rates of approximately FCY/512. As a result, high processor speeds may not support 100 Kbit/second operation. See timing specifications, IM10 and IM11, and the "Baud Rate Generator" in the "dsPIC33/PIC24 Family Reference Manual".

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two Inter-Integrated Circuit (I<sup>2</sup>C) modules: I2C1 and I2C2.

The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

The  $I^2C$  module has a 2-pin interface:

- The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7 and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

- Intelligent Platform Management Interface (IPMI)

support

- System Management Bus (SMBus) support

### 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I <sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

#### REGISTER 20-1: UxMODE: UART x MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

| Note 1: | Refer to the "UART" (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                                      |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

### 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details. The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier) acceptance filters

- Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

#### REGISTER 21-22: CxRXFUL1: ECANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Writable bit, but only 'C | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |

|-------------------|-------------------------------|----------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit              | U = Unimplemented bit, rea                                     | d as '0'           |  |  |  |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |

bit 15-0 RXFUL<15:0>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  | •       |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only ' | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |

|-------------------|------------------------------|----------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit             | U = Unimplemented bit, re                                      | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set             | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |

bit 15-0 RXFUL<31:16>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### BUFFER 21-7: ECAN <sup>™</sup> MESSAGE BUFFER WORD 6

| R/W-x           | R/W-x | R/W-x                                           | R/W-x                                             | R/W-x           | R/W-x | R/W-x | R/W-x |

|-----------------|-------|-------------------------------------------------|---------------------------------------------------|-----------------|-------|-------|-------|

|                 |       |                                                 | B                                                 | yte 7           |       |       |       |

| bit 15          |       |                                                 |                                                   |                 |       |       | bit 8 |

| R/W-x           | R/W-x | R/W-x                                           | R/W-x                                             | R/W-x           | R/W-x | R/W-x | R/W-x |

|                 |       |                                                 | B                                                 | yte 6           |       |       |       |

| bit 7           |       |                                                 |                                                   |                 |       |       | bit 0 |

| Legend:         |       |                                                 |                                                   |                 |       |       |       |

| R = Readable I  | oit   | W = Writable                                    | = Writable bit U = Unimplemented bit, read as '0' |                 |       |       |       |

| -n = Value at P | OR    | R '1' = Bit is set '0' = Bit is cleared $x = B$ |                                                   | x = Bit is unkr | nown  |       |       |

bit 15-8 Byte 7<15:8>: ECAN Message Byte 7 bits

bit 7-0 Byte 6<7:0>: ECAN Message Byte 6 bits

#### BUFFER 21-8: ECAN<sup>™</sup> MESSAGE BUFFER WORD 7

| U-0    | U-0 | U-0 | R/W-x                  | R/W-x                  | R/W-x                  | R/W-x                  | R/W-x                  |

|--------|-----|-----|------------------------|------------------------|------------------------|------------------------|------------------------|

| —      | —   | —   | FILHIT4 <sup>(1)</sup> | FILHIT3 <sup>(1)</sup> | FILHIT2 <sup>(1)</sup> | FILHIT1 <sup>(1)</sup> | FILHIT0 <sup>(1)</sup> |

| bit 15 |     |     |                        |                        |                        |                        | bit 8                  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | —   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                     |

|-----------|----------------------------------------------------------------|

| bit 12-8  | FILHIT<4:0>: Filter Hit Code bits <sup>(1)</sup>               |

|           | Encodes number of filter that resulted in writing this buffer. |

| bit 7-0   | Unimplemented: Read as '0'                                     |

Note 1: Only written by module for receive buffers, unused for transmit buffers.

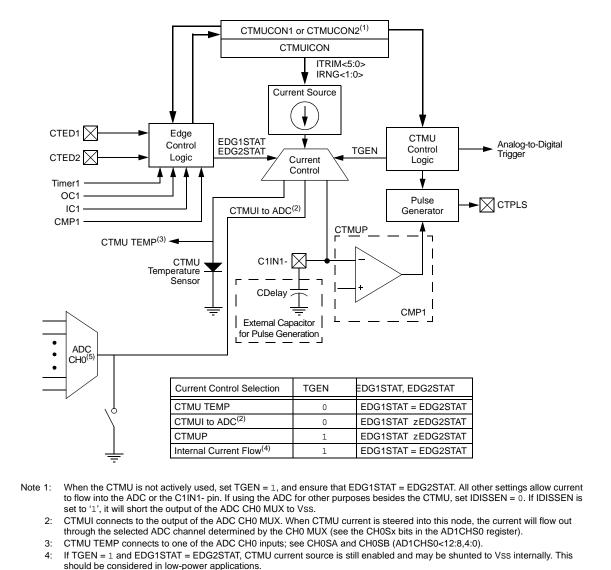

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

### 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER <sup>(1)</sup>

| R/W-0   | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------|--------|----------|-------|-------|-------|

|         |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15  |       |       |        |          |       |       | bit 8 |

|         |       |       |        |          |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | PTGC1L | _IM<7:0> |       |       |       |

| bit 7   |       |       |        |          |       |       | bit 0 |

|         |       |       |        |          |       |       |       |

| Legend: |       |       |        |          |       |       |       |

| _ogo              |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 PTGC1LIM<15:0>: PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

Note 1: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER (1)

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGHOL | _D<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------------|-------|-------|-------|-------|-------|-------|-------|

| PTGHOLD<7:0> |       |       |       |       |       |       |       |

| bit 7        |       |       |       |       |       | bit 0 |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 PTGHOLD<15:0>: PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

Note 1: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

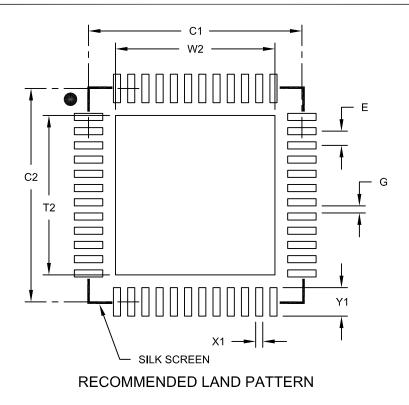

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units | Ν    | <b>ILLIMETER</b> | S    |

|----------------------------|-------|------|------------------|------|

| Dimension Limits           |       | MIN  | NOM              | MAX  |

| Contact Pitch              | E     |      | 0.40 BSC         |      |

| Optional Center Pad Width  | W2    |      |                  | 4.45 |

| Optional Center Pad Length | T2    |      |                  | 4.45 |

| Contact Pad Spacing        | C1    |      | 6.00             |      |

| Contact Pad Spacing        | C2    |      | 6.00             |      |

| Contact Pad Width (X28)    | X1    |      |                  | 0.20 |

| Contact Pad Length (X28)   | Y1    |      |                  | 0.80 |

| Distance Between Pads      | G     | 0.20 |                  |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A

### APPENDIX A: REVISION HISTORY

### Revision A (April 2011)

This is the initial released version of the document.

### Revision B (July 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-1.

### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                                                     | Update Description                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Digital Signal Controllers<br>and Microcontrollers" | Changed all pin diagrams references of VLAP to TLA.                                                                                                                                                                                                                                                                     |

| Section 4.0 "Memory<br>Organization"                                             | Updated the All Resets values for CLKDIV and PLLFBD in the System Control Register Map (see Table 4-35).                                                                                                                                                                                                                |

| Section 5.0 "Flash Program<br>Memory"                                            | Updated "one word" to "two words" in the first paragraph of Section 5.2 "RTSP Operation".                                                                                                                                                                                                                               |

| Section 9.0 "Oscillator<br>Configuration"                                        | Updated the PLL Block Diagram (see Figure 9-2).<br>Updated the Oscillator Mode, Fast RC Oscillator (FRC) with divide-by-N and PLL<br>(FRCPLL), by changing (FRCDIVN + PLL) to (FRCPLL).                                                                                                                                 |

|                                                                                  | Changed (FRCDIVN + PLL) to (FRCPLL) for COSC<2:0> = 001 and NOSC<2:0> = 001 in the Oscillator Control Register (see Register 9-1).                                                                                                                                                                                      |

|                                                                                  | Changed the POR value from 0 to 1 for the DOZE<1:0> bits, from 1 to 0 for the FRCDIV<0> bit, and from 0 to 1 for the PLLPOST<0> bit; Updated the default definitions for the DOZE<2:0> and FRCDIV<2:0> bits and updated all bit definitions for the PLLPOST<1:0> bits in the Clock Divisor Register (see Register 9-2). |

|                                                                                  | Changed the POR value from 0 to 1 for the PLLDIV<5:4> bits and updated the default definitions for all PLLDIV<8:0> bits in the PLL Feedback Division Register (see Register 9-2).                                                                                                                                       |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                            | Updated the bit definitions for the IRNG<1:0> bits in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                            |

| Section 25.0 "Op amp/<br>Comparator Module"                                      | Updated the voltage reference block diagrams (see Figure 25-1 and Figure 25-2).                                                                                                                                                                                                                                         |

| Section Name                                 | Update Description                                                                                                                                                       |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 30.0 "Electrical<br>Characteristics" | Removed Voltage on VCAP with respect to Vss and added Note 5 in Absolute Maximum Ratings <sup>(1)</sup> .                                                                |

|                                              | Removed Parameter DC18 (VCORE) and Note 3 from the DC Temperature and Voltage Specifications (see Table 30-4).                                                           |

|                                              | Updated Note 1 in the DC Characteristics: Operating Current (IDD) (see Table 30-6).                                                                                      |

|                                              | Updated Note 1 in the DC Characteristics: Idle Current (IIDLE) (see Table 30-7).                                                                                         |

|                                              | Changed the Typical values for Parameters DC60a-DC60d and updated Note 1 in the DC Characteristics: Power-down Current (IPD) (see Table 30-8).                           |

|                                              | Updated Note 1 in the DC Characteristics: Doze Current (IDOZE) (see Table 30-9).                                                                                         |

|                                              | Updated Note 2 in the Electrical Characteristics: BOR (see Table 30-12).                                                                                                 |

|                                              | Updated Parameters CM20 and CM31, and added Parameters CM44 and CM45 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                  |

|                                              | Added the Op amp/Comparator Reference Voltage Settling Time Specifications (see Table 30-15).                                                                            |

|                                              | Added Op amp/Comparator Voltage Reference DC Specifications (see Table 30-16).                                                                                           |

|                                              | Updated Internal FRC Accuracy Parameter F20a (see Table 30-21).                                                                                                          |

|                                              | Updated the Typical value and Units for Parameter CTMUI1, and added Parameters CTMUI4, CTMUFV1, and CTMUFV2 to the CTMU Current Source Specifications (see Table 30-55). |

| Section 31.0 "Packaging<br>Information"      | Updated packages by replacing references of VLAP with TLA.                                                                                                               |

| "Product Identification<br>System"           | Changed VLAP to TLA.                                                                                                                                                     |

| ECAN Module                |          |

|----------------------------|----------|

| Control Registers          |          |

| Modes of Operation         |          |

| Overview                   |          |

| Resources                  |          |

| Electrical Characteristics | 401      |

| AC                         | 413, 471 |

| Enhanced CAN (ECAN) Module |          |

| Equations                  |          |

| Device Operating Frequency | 154      |

| FPLLO Calculation          |          |

| Fvco Calculation           | 154      |

| Errata                     | 23       |

|                            |          |

### F

| Filter Capacitor (CEFC) Specifications | 403 |

|----------------------------------------|-----|

| Flash Program Memory                   |     |

| Control Registers                      | 120 |

| Programming Operations                 | 120 |

| Resources                              | 120 |

| RTSP Operation                         | 120 |

| Table Instructions                     | 119 |

| Flexible Configuration                 |     |

### G

| Guidelines for Getting Started                |    |

|-----------------------------------------------|----|

| Application Examples                          |    |

| Basic Connection Requirements                 |    |

| CPU Logic Filter Capacitor Connection (VCAP). | 30 |

| Decoupling Capacitors                         |    |

| External Oscillator Pins                      |    |

| ICSP Pins                                     |    |

| Master Clear (MCLR) Pin                       | 30 |

| Oscillator Value Conditions on Start-up       |    |

| Unused I/Os                                   | 32 |

|                                               |    |

#### Н

### I

| •                                    |          |

|--------------------------------------|----------|

| I/O Ports                            | 173      |

| Helpful Tips                         |          |

| Parallel I/O (PIO)                   |          |

| Resources                            |          |

| Write/Read Timing                    |          |

| In-Circuit Debugger                  |          |

| In-Circuit Emulation                 |          |

| In-Circuit Serial Programming (ICSP) | 379, 386 |

| Input Capture                        | 213      |

| Control Registers                    | 215      |

| Resources                            | 214      |

| Input Change Notification (ICN)      | 174      |

| Instruction Addressing Modes         | 112      |

| File Register Instructions           | 112      |

| Fundamental Modes Supported          | 112      |

| MAC Instructions                     | 113      |

| MCU Instructions                     | 112      |

| Move and Accumulator Instructions    | 113      |

| Other Instructions                   | 113      |

| Instruction Set                             |

|---------------------------------------------|

| Overview                                    |

| Summary                                     |

| Symbols Used in Opcode Descriptions         |

| Inter-Integrated Circuit (I <sup>2</sup> C) |

| Control Registers 276                       |

| Resources 275                               |

| Internal RC Oscillator                      |

| Use with WDT 385                            |

| Internet Address 524                        |

| Interrupt Controller                        |

| Control and Status Registers 131            |

| INTCON1 131                                 |

| INTCON2 131                                 |

| INTCON3 131                                 |

| INTCON4 131                                 |

| INTTREG 131                                 |

| Interrupt Vector Details 129                |

| Interrupt Vector Table (IVT) 127            |

| Reset Sequence 127                          |

| Resources 131                               |

| J                                           |

| JTAG Boundary Scan Interface | . 379 |

|------------------------------|-------|

| JTAG Interface               | . 386 |

### М

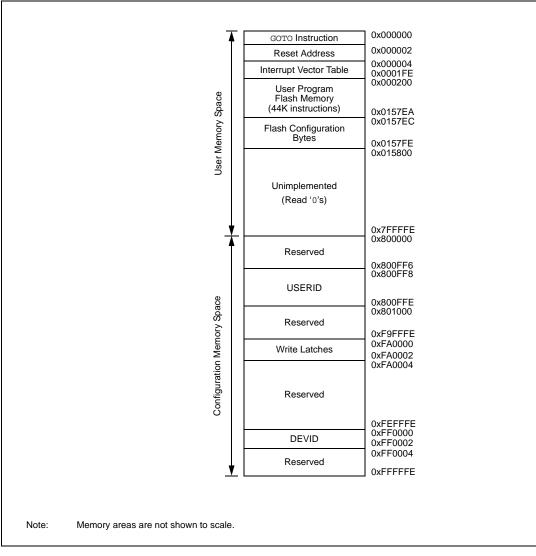

| Memory Maps                               |     |

|-------------------------------------------|-----|

| Extended Data Space                       | 109 |

| Memory Organization                       | 45  |

| Resources                                 | 62  |

| Microchip Internet Web Site               | 524 |

| Modulo Addressing                         | 114 |

| Applicability                             | 115 |

| Operation Example                         | 114 |

| Start and End Address                     | 114 |

| W Address Register Selection              | 114 |

| MPLAB Assembler, Linker, Librarian        | 398 |

| MPLAB ICD 3 In-Circuit Debugger           | 399 |

| MPLAB PM3 Device Programmer               | 399 |

| MPLAB REAL ICE In-Circuit Emulator System | 399 |

| MPLAB X Integrated Development            |     |

| Environment Software                      | 397 |

| MPLAB X SIM Software Simulator            | 399 |

| MPLIB Object Librarian                    | 398 |

| MPLINK Object Linker                      | 398 |

#

| Op Amp                     |     |

|----------------------------|-----|

| Application Considerations | 358 |

| Configuration A            | 358 |

| Configuration B            | 359 |

| Op Amp/Comparator          | 355 |

| Control Registers          | 360 |

| Resources                  | 359 |

| Open-Drain Configuration   | 174 |

| Oscillator                 |     |

| Control Registers          | 156 |

| Resources                  | 155 |

| Output Compare             |     |

| Control Registers          | 221 |

| Resources                  | 220 |

|                            |     |