Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp502-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4         | -16:  | QEI1   | REGR               |          | P FOR d    | SPIC33E                                                         | PXXXMO   | 20X/50)  | ( AND PI    | C24EP) |        | 20X DE     | VICES O  | NLY    | 1      |        |        | r             |

|-----------------|-------|--------|--------------------|----------|------------|-----------------------------------------------------------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| File Name       | Addr. | Bit 15 | Bit 14             | Bit 13   | Bit 12     | Bit 11                                                          | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON         | 01C0  | QEIEN  | —                  | QEISIDL  |            | PIMOD<2:0>                                                      |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI1IOC         | 01C2  | QCAPEN | FLTREN             |          | QFDIV<2:0> | V<2:0> OUTFNC<1:0> SWPAB HOMPOL IDXPOL QEBPOL QEAPOL HOME INDEX |          |          |             | QEB    | QEA    | 000x       |          |        |        |        |        |               |

| <b>QEI1STAT</b> | 01C4  | _      | _                  | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ                                                        | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL        | 01C6  |        |                    |          |            |                                                                 |          |          | POSCNT<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| POS1CNTH        | 01C8  |        | POSCNT<31:16> 000  |          |            |                                                                 |          |          |             |        |        | 0000       |          |        |        |        |        |               |

| POS1HLD         | 01CA  |        | POSHLD<15:0> 0000  |          |            |                                                                 |          |          |             |        |        |            |          |        |        |        |        |               |

| VEL1CNT         | 01CC  |        | VELCNT<15:0> 0000  |          |            |                                                                 |          |          |             |        |        |            |          |        |        |        |        |               |

| INT1TMRL        | 01CE  |        | INTTMR<15:0> 0000  |          |            |                                                                 |          |          |             |        |        |            |          |        |        |        |        |               |

| INT1TMRH        | 01D0  |        | INTTMR<31:16> 0000 |          |            |                                                                 |          |          |             |        |        | 0000       |          |        |        |        |        |               |

| INT1HLDL        | 01D2  |        |                    |          |            |                                                                 |          |          | INTHLD<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDH        | 01D4  |        |                    |          |            |                                                                 |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL       | 01D6  |        |                    |          |            |                                                                 |          |          | INDXCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH       | 01D8  |        |                    |          |            |                                                                 |          |          | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD        | 01DA  |        |                    |          |            |                                                                 |          |          | INDXHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL        | 01DC  |        |                    |          |            |                                                                 |          |          | QEIGEC<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1ICL</b>  | 01DC  |        |                    |          |            |                                                                 |          |          | QEIIC<15:0  | >      |        |            |          |        |        |        |        | 0000          |

| QEI1GECH        | 01DE  |        |                    |          |            |                                                                 |          |          | QEIGEC<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| QEI1ICH         | 01DE  |        |                    |          |            |                                                                 |          |          | QEIIC<31:16 | š>     |        |            |          |        |        |        |        | 0000          |

| QEI1LECL        | 01E0  |        |                    |          |            |                                                                 |          |          | QEILEC<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1LECH</b> | 01E2  |        |                    |          |            |                                                                 |          |          | QEILEC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 3 SPI1MD: SPI1 Module Disable bit 1 = SPI1 module is disabled

- 0 = SPI1 module is enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: ECAN1 Module Disable bit<sup>(2)</sup> 1 = ECAN1 module is disabled 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit 1 = ADC1 module is disabled 0 = ADC1 module is enabled

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

## REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|-----------------|-------|

| —            |                           |                                                                                                    |                            | QEB1R<6:0>        |                 |                 |       |

| bit 15       |                           |                                                                                                    |                            |                   |                 |                 | bit 8 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |                           |                                                                                                    |                            | QEA1R<6:0>        |                 |                 |       |

| bit 7        |                           |                                                                                                    |                            |                   |                 |                 | bit 0 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| Legend:      |                           |                                                                                                    |                            |                   |                 |                 |       |

| R = Readat   | ole bit                   | W = Writable                                                                                       | bit                        | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR                    | '1' = Bit is set                                                                                   |                            | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 1111001 =                 | 1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss                    | 121<br>P1                  |                   |                 |                 |       |

| bit 7        | Unimpleme                 | nted: Read as '                                                                                    | 0'                         |                   |                 |                 |       |

| bit 6-0      | (see Table 1<br>1111001 = | >: Assign A (QE<br>1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss | selection nun<br>121<br>P1 |                   | n Pin bits      |                 |       |

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | R/W-0                                                                    | R/W-0                                                                                                    | R/W-0                           | U-0               | U-0              | U-0                    | R/W-0        |  |  |

|------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------|-------------------|------------------|------------------------|--------------|--|--|

| FLTMD      | FLTOUT                                                                   | FLTTRIEN                                                                                                 | OCINV                           | —                 | _                | —                      | OC32         |  |  |

| bit 15     | ·                                                                        |                                                                                                          |                                 |                   | ·                |                        | bit          |  |  |

|            |                                                                          |                                                                                                          |                                 |                   |                  |                        |              |  |  |

| R/W-0      | R/W-0, HS                                                                | R/W-0                                                                                                    | R/W-0                           | R/W-1             | R/W-1            | R/W-0                  | R/W-0        |  |  |

| OCTRIG     | G TRIGSTAT                                                               | OCTRIS                                                                                                   | SYNCSEL4                        | SYNCSEL3          | SYNCSEL2         | SYNCSEL1               | SYNCSEL      |  |  |

| bit 7      |                                                                          |                                                                                                          |                                 |                   |                  |                        | bit          |  |  |

| Legend:    |                                                                          | HS = Hardwa                                                                                              | re Settable bit                 |                   |                  |                        |              |  |  |

| R = Reada  | able bit                                                                 | W = Writable                                                                                             | bit                             | U = Unimplem      | nented bit, read | l as '0'               |              |  |  |

| -n = Value | at POR                                                                   | '1' = Bit is set                                                                                         |                                 | '0' = Bit is clea | ared             | x = Bit is unkn        | iown         |  |  |

|            |                                                                          |                                                                                                          |                                 |                   |                  |                        |              |  |  |

| bit 15     | 1 = Fault mo<br>cleared i                                                | t Mode Select b<br>ode is maintain<br>n software and                                                     | ed until the Fa<br>a new PWM pe | eriod starts      |                  |                        |              |  |  |

|            |                                                                          | de is maintaine                                                                                          | d until the Faul                | t source is rem   | loved and a ne   | w PWM period           | starts       |  |  |

| bit 14     | FLTOUT: Fau                                                              |                                                                                                          | . –                             |                   |                  |                        |              |  |  |

|            |                                                                          | tput is driven hi<br>tput is driven lo                                                                   |                                 |                   |                  |                        |              |  |  |

| bit 13     |                                                                          | <ul> <li>PWM output is driven low on a Fault</li> <li>FLTTRIEN: Fault Output State Select bit</li> </ul> |                                 |                   |                  |                        |              |  |  |

|            |                                                                          | 1 = OCx pin is tri-stated on a Fault condition                                                           |                                 |                   |                  |                        |              |  |  |

|            | •                                                                        | I/O state is defi                                                                                        |                                 |                   | ault condition   |                        |              |  |  |

| bit 12     | OCINV: Outp                                                              | ut Compare x I                                                                                           | nvert bit                       |                   |                  |                        |              |  |  |

|            |                                                                          | out is inverted<br>out is not invert                                                                     | ed                              |                   |                  |                        |              |  |  |

| bit 11-9   | Unimplemen                                                               | ted: Read as '                                                                                           | כי                              |                   |                  |                        |              |  |  |

| bit 8      | OC32: Casca                                                              | ide Two OCx M                                                                                            | odules Enable                   | bit (32-bit oper  | ration)          |                        |              |  |  |

|            |                                                                          | module operate module operate                                                                            |                                 |                   |                  |                        |              |  |  |

| bit 7      |                                                                          | tput Compare x                                                                                           |                                 | Select bit        |                  |                        |              |  |  |

|            |                                                                          | OCx from the s                                                                                           |                                 |                   | CSELx bits       |                        |              |  |  |

|            |                                                                          | nizes OCx with                                                                                           |                                 |                   |                  | S                      |              |  |  |

| bit 6      | TRIGSTAT: T                                                              | imer Trigger St                                                                                          | atus bit                        |                   |                  |                        |              |  |  |

|            |                                                                          | urce has been <sup>.</sup><br>urce has not be                                                            |                                 |                   | d clear          |                        |              |  |  |

| bit 5      |                                                                          | put Compare x                                                                                            |                                 | •                 |                  |                        |              |  |  |

|            | 1 = OCx is tr                                                            | • •                                                                                                      | ·                               |                   |                  |                        |              |  |  |

|            | 0 = Output C                                                             | ompare x mod                                                                                             | ule drives the C                | OCx pin           |                  |                        |              |  |  |

| Note 1:    | Do not use the O                                                         | Cx module as i                                                                                           | ts own Svnchro                  | nization or Tric  | aaer source.     |                        |              |  |  |

|            | When the OCy m                                                           |                                                                                                          | -                               |                   |                  | module uses t          | he OCv       |  |  |

|            | module as a Trigg                                                        |                                                                                                          |                                 |                   |                  |                        |              |  |  |

| 3:         | Each Output Con<br><b>"Peripheral Trig</b><br>PTGO0 = OC1<br>PTGO1 = OC2 |                                                                                                          |                                 |                   |                  | n source. See <b>S</b> | Section 24.0 |  |  |

|            | PTGO2 = OC3 $PTGO3 = OC4$                                                |                                                                                                          |                                 |                   |                  |                        |              |  |  |

## REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

### REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

- bit 7-3 FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator # bits 11111 = Fault 32 (default) 11110 = Reserved . . 01100 = Reserved 01011 = Comparator 4 01010 = Op Amp/Comparator 3

- 01001 = Op Amp/Comparator 2

- 01000 = Op Amp/Comparator 1

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = Reserved

- 00011 = Fault 4

- 00010 = Fault 3

- 00001 = Fault 2 00000 = Fault 1

- bit 2 ELTROL Fault Delarity for DWM Concrete

## bit 2 **FLTPOL:** Fault Polarity for PWM Generator # bit<sup>(2)</sup>

- 1 = The selected Fault source is active-low

- 0 = The selected Fault source is active-high

- bit 1-0 FLTMOD<1:0>: Fault Mode for PWM Generator # bits

- 11 = Fault input is disabled

- 10 = Reserved

- 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

- 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

- **Note 1:** If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

- **2:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| U-0                                                                                  | U-0                                                                                                                                                                                                                                              | U-0                                                                                                                 | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|--|--|

|                                                                                      | —                                                                                                                                                                                                                                                | _                                                                                                                   | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |  |  |

| bit 15                                                                               |                                                                                                                                                                                                                                                  | •                                                                                                                   |                                       | •                    | •                    | •                    | bit                  |  |  |  |  |  |

| R/W-0                                                                                | R/W-0                                                                                                                                                                                                                                            | R/W-0                                                                                                               | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |  |

| SSEN <sup>(2)</sup>                                                                  | CKP                                                                                                                                                                                                                                              | MSTEN                                                                                                               | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |  |  |

| bit 7                                                                                | CKF                                                                                                                                                                                                                                              | WISTEN                                                                                                              | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |  |  |  |  |  |

|                                                                                      |                                                                                                                                                                                                                                                  |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

| Legend:                                                                              |                                                                                                                                                                                                                                                  |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

| R = Readabl                                                                          | le bit                                                                                                                                                                                                                                           | W = Writable                                                                                                        | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |  |  |  |  |  |

| -n = Value at                                                                        | t POR                                                                                                                                                                                                                                            | '1' = Bit is se                                                                                                     | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |  |  |  |  |  |

|                                                                                      |                                                                                                                                                                                                                                                  |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

| bit 15-13                                                                            | Unimplemen                                                                                                                                                                                                                                       | ted: Read as                                                                                                        | 0'                                    |                      |                      |                      |                      |  |  |  |  |  |

| bit 12                                                                               |                                                                                                                                                                                                                                                  |                                                                                                                     | bit (SPIx Mas                         | -                    | ()                   |                      |                      |  |  |  |  |  |

|                                                                                      |                                                                                                                                                                                                                                                  |                                                                                                                     | sabled, pin fun                       | ctions as I/O        |                      |                      |                      |  |  |  |  |  |

| 0 = Internal SPIx clock is enabled         bit 11       DISSDO: Disable SDOx Pin bit |                                                                                                                                                                                                                                                  |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

|                                                                                      |                                                                                                                                                                                                                                                  |                                                                                                                     | / the module; p                       | oin functions as     | s I/O                |                      |                      |  |  |  |  |  |

|                                                                                      |                                                                                                                                                                                                                                                  | is controlled b                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

| bit 10                                                                               | MODE16: Wo                                                                                                                                                                                                                                       | MODE16: Word/Byte Communication Select bit                                                                          |                                       |                      |                      |                      |                      |  |  |  |  |  |

|                                                                                      |                                                                                                                                                                                                                                                  | <ul> <li>1 = Communication is word-wide (16 bits)</li> <li>0 = Communication is byte-wide (8 bits)</li> </ul>       |                                       |                      |                      |                      |                      |  |  |  |  |  |

|                                                                                      |                                                                                                                                                                                                                                                  | •                                                                                                                   | . ,                                   |                      |                      |                      |                      |  |  |  |  |  |

| bit 9                                                                                |                                                                                                                                                                                                                                                  | ata Input Sam                                                                                                       | ole Phase bit                         |                      |                      |                      |                      |  |  |  |  |  |

|                                                                                      | Master mode                                                                                                                                                                                                                                      | -                                                                                                                   | end of data o                         | utout time           |                      |                      |                      |  |  |  |  |  |

|                                                                                      |                                                                                                                                                                                                                                                  |                                                                                                                     | middle of data                        |                      |                      |                      |                      |  |  |  |  |  |

|                                                                                      | Slave mode:                                                                                                                                                                                                                                      |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

|                                                                                      | SMP must be cleared when SPIx is used in Slave mode.                                                                                                                                                                                             |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

| bit 8                                                                                |                                                                                                                                                                                                                                                  | CKE: SPIx Clock Edge Select bit <sup>(1)</sup>                                                                      |                                       |                      |                      |                      |                      |  |  |  |  |  |

|                                                                                      | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)</li> </ul> |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

| bit 7                                                                                |                                                                                                                                                                                                                                                  |                                                                                                                     |                                       |                      |                      | ve clock state (I    |                      |  |  |  |  |  |

|                                                                                      |                                                                                                                                                                                                                                                  | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(2)</sup><br>1 = $\overline{SSx}$ pin is used for Slave mode |                                       |                      |                      |                      |                      |  |  |  |  |  |

|                                                                                      | $1 = \frac{35x}{55x}$ pin is used for Slave mode<br>0 = SSx pin is not used by the module; pin is controlled by port function                                                                                                                    |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

| bit 6                                                                                | CKP: Clock F                                                                                                                                                                                                                                     | Polarity Select                                                                                                     | bit                                   |                      |                      |                      |                      |  |  |  |  |  |

|                                                                                      |                                                                                                                                                                                                                                                  |                                                                                                                     | nigh level; activ<br>ow level; active |                      |                      |                      |                      |  |  |  |  |  |

| bit 5                                                                                | MSTEN: Master Mode Enable bit                                                                                                                                                                                                                    |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

|                                                                                      | 1 = Master m<br>0 = Slave mo                                                                                                                                                                                                                     |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

| Note 1: T                                                                            | he CKE bit is not                                                                                                                                                                                                                                | used in Frame                                                                                                       | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |  |  |  |  |  |

|                                                                                      | his bit must be cl                                                                                                                                                                                                                               |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

| <b>0</b>                                                                             |                                                                                                                                                                                                                                                  |                                                                                                                     |                                       |                      |                      |                      |                      |  |  |  |  |  |

## REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

NOTES:

## REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

| bit 1 | BUFM: Buffer Fill Mode Select bit                                                                                                                                                                                               |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | <ul> <li>1 = Starts the buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on next interrupt</li> <li>0 = Always starts filling the buffer from the start address.</li> </ul> |  |  |  |  |  |  |

| bit 0 | ALTS: Alternate Input Sample Mode Select bit                                                                                                                                                                                    |  |  |  |  |  |  |

1 = Uses channel input selects for Sample MUXA on first sample and Sample MUXB on next sample 0 = Always uses channel input selects for Sample MUXA

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|              | R/W-0         | U-0                                | U-0                         | U-0             | R/W-0                                | R/W-0                | R/W-0                |  |  |  |  |

|--------------|---------------|------------------------------------|-----------------------------|-----------------|--------------------------------------|----------------------|----------------------|--|--|--|--|

| CSS31        | CSS30         | —                                  | —                           | _               | CSS26 <sup>(2)</sup>                 | CSS25 <sup>(2)</sup> | CSS24 <sup>(2)</sup> |  |  |  |  |

| bit 15       | - 1           |                                    |                             |                 |                                      |                      | bit 8                |  |  |  |  |

|              |               |                                    |                             |                 |                                      |                      |                      |  |  |  |  |

| U-0          | U-0           | U-0                                | U-0                         | U-0             | U-0                                  | U-0                  | U-0                  |  |  |  |  |

| _            |               | _                                  | _                           | _               |                                      | _                    |                      |  |  |  |  |

| bit 7        |               |                                    |                             |                 |                                      |                      | bit (                |  |  |  |  |

|              |               |                                    |                             |                 |                                      |                      |                      |  |  |  |  |

| Legend:      |               |                                    |                             |                 |                                      |                      |                      |  |  |  |  |

| R = Readab   | le bit        | W = Writable                       | bit                         | U = Unimple     | emented bit, read                    | d as '0'             |                      |  |  |  |  |

| -n = Value a | t POR         | '1' = Bit is set                   |                             | '0' = Bit is cl | eared                                | x = Bit is unk       | nown                 |  |  |  |  |

|              |               |                                    |                             |                 |                                      |                      |                      |  |  |  |  |

| bit 15       |               | 1 Input Scan S                     |                             |                 |                                      |                      |                      |  |  |  |  |

|              |               |                                    |                             |                 | input scan (Ope                      |                      |                      |  |  |  |  |

|              | •             | •                                  |                             | surement for ir | nput scan (Open                      | )                    |                      |  |  |  |  |

| bit 14       |               | 1 Input Scan S                     |                             |                 |                                      |                      |                      |  |  |  |  |

|              |               |                                    |                             |                 | or input scan (CT<br>input scan (CTN |                      |                      |  |  |  |  |

| bit 13-11    | Unimplemen    | ted: Read as '                     | 0'                          |                 |                                      |                      |                      |  |  |  |  |

| bit 10       | CSS26: ADC    | 1 Input Scan S                     | election bit <sup>(2)</sup> |                 |                                      |                      |                      |  |  |  |  |

|              | 1 = Selects C | )<br>A3/AN6 for inp                | ut scan                     |                 |                                      |                      |                      |  |  |  |  |

|              | 0 = Skips OA  | 3/AN6 for input                    | scan                        |                 |                                      |                      |                      |  |  |  |  |

| bit 9        | CSS25: ADC    | 1 Input Scan S                     | election bit <sup>(2)</sup> |                 |                                      |                      |                      |  |  |  |  |

|              | 1 = Selects C | 1 = Selects OA2/AN0 for input scan |                             |                 |                                      |                      |                      |  |  |  |  |

|              | 0 = Skips OA  | 2/AN0 for input                    | scan                        |                 |                                      |                      |                      |  |  |  |  |

| bit 8        | CSS24: ADC    | 1 Input Scan S                     | election bit <sup>(2)</sup> |                 |                                      |                      |                      |  |  |  |  |

|              |               | 0A1/AN3 for inp                    |                             |                 |                                      |                      |                      |  |  |  |  |

|              | 0 = Skips OA  | 1/AN3 for input                    | scan                        |                 |                                      |                      |                      |  |  |  |  |

|              |               |                                    |                             |                 |                                      |                      |                      |  |  |  |  |

## REGISTER 23-7: AD1CSSH: ADC1 INPUT SCAN SELECT REGISTER HIGH<sup>(1)</sup>

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                          |

|---------|------------------------|-------------|-------------------------------------------------------------|

|         | PTGWHI(1)              | 0000        | PWM Special Event Trigger. <sup>(3)</sup>                   |

|         | or (1)                 | 0001        | PWM master time base synchronization output. <sup>(3)</sup> |

|         | PTGWLO(1)              | 0010        | PWM1 interrupt. <sup>(3)</sup>                              |

|         |                        | 0011        | PWM2 interrupt. <sup>(3)</sup>                              |

|         |                        | 0100        | PWM3 interrupt. <sup>(3)</sup>                              |

|         |                        | 0101        | Reserved.                                                   |

|         |                        | 0110        | Reserved.                                                   |

|         |                        | 0111        | OC1 Trigger event.                                          |

|         |                        | 1000        | OC2 Trigger event.                                          |

|         |                        | 1001        | IC1 Trigger event.                                          |

|         |                        | 1010        | CMP1 Trigger event.                                         |

|         |                        | 1011        | CMP2 Trigger event.                                         |

|         |                        | 1100        | CMP3 Trigger event.                                         |

|         |                        | 1101        | CMP4 Trigger event.                                         |

|         |                        | 1110        | ADC conversion done interrupt.                              |

|         |                        | 1111        | INT2 external interrupt.                                    |

|         | PTGIRQ(1)              | 0000        | Generate PTG Interrupt 0.                                   |

|         |                        | 0001        | Generate PTG Interrupt 1.                                   |

|         |                        | 0010        | Generate PTG Interrupt 2.                                   |

|         |                        | 0011        | Generate PTG Interrupt 3.                                   |

|         |                        | 0100        | Reserved.                                                   |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         | (2)                    | 1111        | Reserved.                                                   |

|         | PTGTRIG <sup>(2)</sup> | 00000       | PTGO0.                                                      |

|         |                        | 00001       | PTGO1.                                                      |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         |                        | 11110       | PTGO30.                                                     |

|         |                        | 11111       | PTGO31.                                                     |

TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed, or an SFR register is read. In these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157). For more information on instructions that take more than one instruction cycle to execute, refer to **"CPU"** (DS70359) in the *"dsPIC33/PIC24 Family Reference Manual"*, particularly the **"Instruction Flow Types"** section.

| Field               | Description                                                                          |

|---------------------|--------------------------------------------------------------------------------------|

| #text               | Means literal defined by "text"                                                      |

| (text)              | Means "content of text"                                                              |

| [text]              | Means "the location addressed by text"                                               |

| {}                  | Optional field or operation                                                          |

| $a \in \{b, c, d\}$ | a is selected from the set of values b, c, d                                         |

| <n:m></n:m>         | Register bit field                                                                   |

| .b                  | Byte mode selection                                                                  |

| .d                  | Double-Word mode selection                                                           |

| .S                  | Shadow register select                                                               |

| .w                  | Word mode selection (default)                                                        |

| Acc                 | One of two accumulators {A, B}                                                       |

| AWB                 | Accumulator write back destination address register ∈ {W13, [W13]+ = 2}              |

| bit4                | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z     | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr                | Absolute address, label or expression (resolved by the linker)                       |

| f                   | File register address ∈ {0x00000x1FFF}                                               |

| lit1                | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4                | 4-bit unsigned literal ∈ {015}                                                       |

| lit5                | 5-bit unsigned literal ∈ {031}                                                       |

| lit8                | 8-bit unsigned literal ∈ {0255}                                                      |

| lit10               | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |

| lit14               | 14-bit unsigned literal ∈ {016384}                                                   |

| lit16               | 16-bit unsigned literal ∈ {065535}                                                   |

| lit23               | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |

| None                | Field does not require an entry, can be blank                                        |

| OA, OB, SA, SB      | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |

| PC                  | Program Counter                                                                      |

| Slit10              | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16              | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6               | 6-bit signed literal ∈ {-1616}                                                       |

| Wb                  | Base W register ∈ {W0W15}                                                            |

| Wd                  | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo                 | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

### TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACT       | ERISTICS                  |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |        |      |           |  |  |

|------------------|---------------------------|------|------------------------------------------------------|--------|------|-----------|--|--|

| Parameter<br>No. | Тур.                      | Max. | Units Conditions                                     |        |      |           |  |  |

| Operating Cur    | rent (IDD) <sup>(1)</sup> |      |                                                      |        |      |           |  |  |

| DC20d            | 9                         | 15   | mA                                                   | -40°C  |      |           |  |  |

| DC20a            | 9                         | 15   | mA                                                   | +25°C  | 3.3V | 10 MIPS   |  |  |

| DC20b            | 9                         | 15   | mA                                                   | +85°C  | 3.3V |           |  |  |

| DC20c            | 9                         | 15   | mA                                                   | +125°C |      |           |  |  |

| DC22d            | 16                        | 25   | mA                                                   | -40°C  |      |           |  |  |

| DC22a            | 16                        | 25   | mA                                                   | +25°C  | 3.3V | 20 MIPS   |  |  |

| DC22b            | 16                        | 25   | mA                                                   | +85°C  | 3.3V | 20 1011-5 |  |  |

| DC22c            | 16                        | 25   | mA                                                   | +125°C |      |           |  |  |

| DC24d            | 27                        | 40   | mA                                                   | -40°C  |      |           |  |  |

| DC24a            | 27                        | 40   | mA                                                   | +25°C  | 3.3V | 40 MIPS   |  |  |

| DC24b            | 27                        | 40   | mA                                                   | +85°C  | 3.3V | 40 1011-5 |  |  |

| DC24c            | 27                        | 40   | mA                                                   | +125°C |      |           |  |  |

| DC25d            | 36                        | 55   | mA                                                   | -40°C  |      |           |  |  |

| DC25a            | 36                        | 55   | mA                                                   | +25°C  | 3.3V | 60 MIPS   |  |  |

| DC25b            | 36                        | 55   | mA                                                   | +85°C  | 3.3V | OU IVIIPS |  |  |

| DC25c            | 36                        | 55   | mA                                                   | +125°C | 7    |           |  |  |

| DC26d            | 41                        | 60   | mA                                                   | -40°C  |      |           |  |  |

| DC26a            | 41                        | 60   | mA                                                   | +25°C  | 3.3V | 70 MIPS   |  |  |

| DC26b            | 41                        | 60   | mA                                                   | +85°C  |      |           |  |  |

#### TABLE 30-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) {NOP(); } statement

- · JTAG is disabled

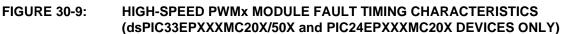

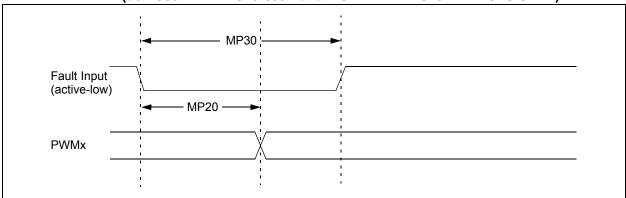

## FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

## TABLE 30-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                    |  |

|--------------------|--------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max. | Units | Conditions         |  |

| MP10               | TFPWM  | PWMx Output Fall Time               |                                                                                                                                                                                                                                                                                         | —    | _    | ns    | See Parameter DO32 |  |

| MP11               | TRPWM  | PWMx Output Rise Time               | _                                                                                                                                                                                                                                                                                       | —    | _    | ns    | See Parameter DO31 |  |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                                                                                                                                                                                                                                                                                       | _    | 15   | ns    |                    |  |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                                                                                                                                                                                                                                                                                      | _    | _    | ns    |                    |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

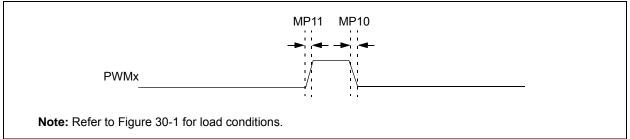

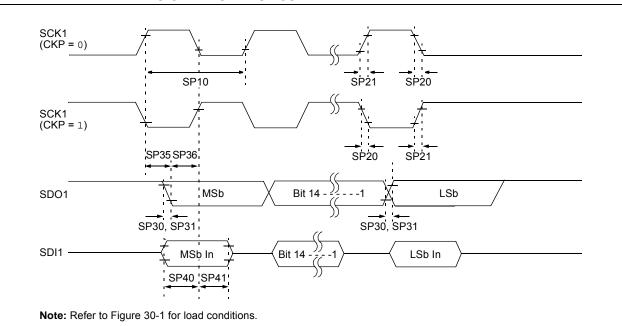

### FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

## TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHA | RACTERIST             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                                                |   |    |     |                                |  |

|--------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---|----|-----|--------------------------------|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                       | Min. Typ. <sup>(2)</sup> Max. Units Conditions |   |    |     |                                |  |

| SP10   | FscP                  | Maximum SCK1 Frequency                                                                                                                                                                                                                                                              | —                                              |   | 15 | MHz | (Note 3)                       |  |

| SP20   | TscF                  | SCK1 Output Fall Time                                                                                                                                                                                                                                                               | -                                              | - | _  | ns  | See Parameter DO32<br>(Note 4) |  |

| SP21   | TscR                  | SCK1 Output Rise Time                                                                                                                                                                                                                                                               | —                                              | — | _  | ns  | See Parameter DO31 (Note 4)    |  |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                                                                                                                                                                                                                                                          | -                                              | - | _  | ns  | See Parameter DO32<br>(Note 4) |  |