Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp502t-i-mm |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

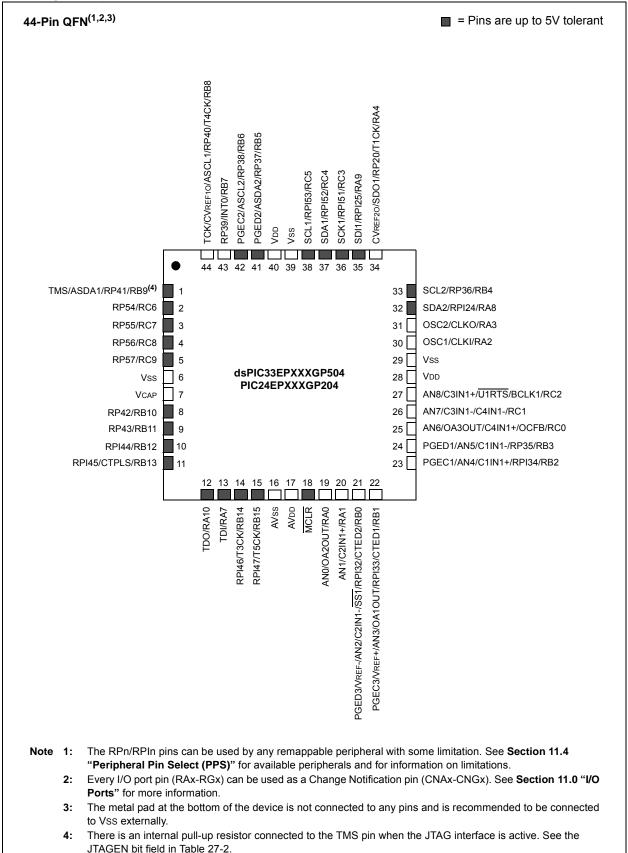

#### **Pin Diagrams (Continued)**

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVSS pins must be connected, independent of the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ .

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

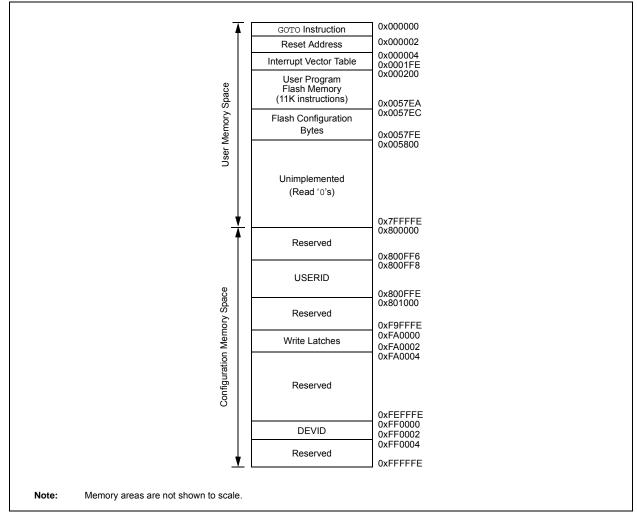

#### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

#### 4.2.5 X AND Y DATA SPACES

# The dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXXGP/MC20X devices.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

#### 4.3 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 4.3.1 KEY RESOURCES

- "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

#### 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|--------|-------|-------|--------|---------------------|-----|-------|-------|

| VAR    | —     | US1   | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15 |       | •     |        |                     |     |       | bit 8 |

|        |       |       |        |                     |     |       |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7  |       | •     |        |                     |     |       | bit 0 |

|        |       |       |        |                     |     |       |       |

|        |       |       |        |                     |     |       |       |

# **REGISTER 7-2:** CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                      |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared | x = Bit is unknown |

bit

| VAR: Variable Exception Processing Latency Control                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>1 = Variable exception processing is enabled</li> </ol>                                                              |

| 0 = Fixed exception processing is enabled                                                                                     |

| IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                                |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

|                                                                                                                               |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| R/W-1        | R/W-0                                                                                                                            | R/W-0                                                    | U-0          | U-0              | U-0              | U-0             | U-0    |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|------------------|------------------|-----------------|--------|--|--|--|--|--|

| GIE          | DISI                                                                                                                             | SWTRAP                                                   |              |                  |                  | _               |        |  |  |  |  |  |

| bit 15       |                                                                                                                                  |                                                          |              |                  |                  |                 | bit 8  |  |  |  |  |  |

|              |                                                                                                                                  |                                                          |              |                  |                  |                 |        |  |  |  |  |  |

| U-0          | U-0                                                                                                                              | U-0                                                      | U-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

|              | —                                                                                                                                |                                                          |              |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |  |  |

| bit 7        |                                                                                                                                  |                                                          |              |                  |                  |                 | bit C  |  |  |  |  |  |

| Legend:      |                                                                                                                                  |                                                          |              |                  |                  |                 |        |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                           | W = Writable                                             | bit          | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |  |  |

| -n = Value a |                                                                                                                                  | '1' = Bit is set                                         |              | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |  |  |  |  |

|              |                                                                                                                                  |                                                          |              |                  |                  |                 |        |  |  |  |  |  |

| bit 15       | GIE: Global                                                                                                                      | GIE: Global Interrupt Enable bit                         |              |                  |                  |                 |        |  |  |  |  |  |

|              | 1 = Interrupts and associated IE bits are enabled                                                                                |                                                          |              |                  |                  |                 |        |  |  |  |  |  |

|              |                                                                                                                                  | 0 = Interrupts are disabled, but traps are still enabled |              |                  |                  |                 |        |  |  |  |  |  |

| bit 14       | DISI: DISI Instruction Status bit                                                                                                |                                                          |              |                  |                  |                 |        |  |  |  |  |  |

|              |                                                                                                                                  | struction is active<br>struction is not a                | -            |                  |                  |                 |        |  |  |  |  |  |

| bit 13       | SWTRAP: Software Trap Status bit                                                                                                 |                                                          |              |                  |                  |                 |        |  |  |  |  |  |

|              |                                                                                                                                  | e trap is enabled<br>e trap is disabled                  |              |                  |                  |                 |        |  |  |  |  |  |

| bit 12-3     | Unimpleme                                                                                                                        | nted: Read as '                                          | 0'           |                  |                  |                 |        |  |  |  |  |  |

| bit 2        | INT2EP: Ext                                                                                                                      | ternal Interrupt 2                                       | 2 Edge Detec | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |

|              |                                                                                                                                  | on negative edg                                          |              |                  |                  |                 |        |  |  |  |  |  |

| bit 1        | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit                                                                     |                                                          |              |                  |                  |                 |        |  |  |  |  |  |

|              |                                                                                                                                  | on negative edg                                          |              |                  |                  |                 |        |  |  |  |  |  |

| bit 0        | INTOEP: Ext                                                                                                                      | ternal Interrupt C                                       | Edge Detec   | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |

|              | INTOEP: External Interrupt 0 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge<br>0 = Interrupt on positive edge |                                                          |              |                  |                  |                 |        |  |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **"Oscillator"** (DS70580) in the *"dsPIC33/ PIC24 Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                             | R/W-0           | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| ROON          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ROSSLP                                                            | ROSEL           | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                   |                 |                       |                       | •                     | bit                   |  |  |  |

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U-0                                                               | U-0             | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |

|               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                 |                 | _                     |                       | _                     |                       |  |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                   |                 |                       |                       |                       | bit                   |  |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                   |                 |                       |                       |                       |                       |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable                                                      | bit             | U = Unimpler          | nented bit, read      | l as '0'              |                       |  |  |  |

| -n = Value at |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | '1' = Bit is set                                                  |                 | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |  |  |  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as ' | out is disabled |                       | .K pin <sup>(2)</sup> |                       |                       |  |  |  |

| bit 13        | <b>ROSSLP:</b> Reference Oscillator Run in Sleep bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                   |                 |                       |                       |                       |                       |  |  |  |

|               | 1 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e oscillator out<br>e oscillator out                              | out continues   | to run in Sleep       |                       |                       |                       |  |  |  |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | erence Oscillato<br>crystal is used<br>lock is used as            | as the refere   | nce clock             |                       |                       |                       |  |  |  |

| bit 11-8      | 0 = System clock is used as the reference clock<br><b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divider bits <sup>(1)</sup><br>1111 = Reference clock divided by 32,768<br>1110 = Reference clock divided by 16,384<br>1101 = Reference clock divided by 8,192<br>1100 = Reference clock divided by 4,096<br>1011 = Reference clock divided by 2,048<br>1010 = Reference clock divided by 1,024<br>1001 = Reference clock divided by 512<br>1000 = Reference clock divided by 256<br>0111 = Reference clock divided by 128<br>0110 = Reference clock divided by 4<br>0101 = Reference clock divided by 4<br>0101 = Reference clock divided by 32<br>0100 = Reference clock divided by 32<br>0100 = Reference clock divided by 4<br>0011 = Reference clock divided by 4 |                                                                   |                 |                       |                       |                       |                       |  |  |  |

|               | 0000 = Refer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ence clock                                                        | -               |                       |                       |                       |                       |  |  |  |

#### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

NOTES:

#### 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0         | R/W-0                                                                                                                                                                  | R/W-0                                                                                                     | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| QCAPEN        | FLTREN                                                                                                                                                                 | QFDIV2                                                                                                    | QFDIV1            | QFDIV0            | OUTFNC1          | OUTFNC0         | SWPAB |  |  |  |  |

| bit 15        | ·                                                                                                                                                                      | ·                                                                                                         |                   |                   |                  |                 | bit 8 |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                                  | R/W-0                                                                                                     | R/W-0             | R-x               | R-x              | R-x             | R-x   |  |  |  |  |

| HOMPOL        | IDXPOL                                                                                                                                                                 | QEBPOL                                                                                                    | QEAPOL            | HOME              | INDEX            | QEB             | QEA   |  |  |  |  |

| bit 7         |                                                                                                                                                                        |                                                                                                           |                   | TIOME             | INDEX            | QLD             | bit ( |  |  |  |  |

| Legend:       |                                                                                                                                                                        |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                                  | W = Writable                                                                                              | bit               | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value at |                                                                                                                                                                        | '1' = Bit is set                                                                                          |                   | '0' = Bit is cle  |                  | x = Bit is unkn | own   |  |  |  |  |

|               |                                                                                                                                                                        |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

| bit 15        | QCAPEN: Q                                                                                                                                                              | EI Position Cou                                                                                           | nter Input Cap    | ture Enable bit   |                  |                 |       |  |  |  |  |

|               |                                                                                                                                                                        | tch event trigge                                                                                          |                   |                   |                  |                 |       |  |  |  |  |

|               |                                                                                                                                                                        | tch event does                                                                                            |                   | -                 |                  |                 |       |  |  |  |  |

| bit 14        |                                                                                                                                                                        | Ax/QEBx/INDX                                                                                              | •                 | tal Filter Enable | e dit            |                 |       |  |  |  |  |

|               |                                                                                                                                                                        | digital filter is e<br>digital filter is d                                                                |                   | sed)              |                  |                 |       |  |  |  |  |

| bit 13-11     | <ul> <li>0 = Input pin digital filter is disabled (bypassed)</li> <li>QFDIV&lt;2:0&gt;: QEAx/QEBx/INDXx/HOMEx Digital Input Filter Clock Divide Select bits</li> </ul> |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 111 = 1:128 clock divide                                                                                                                                               |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 110 = 1.64 clock divide                                                                                                                                                |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 101 = 1:32 clock divide                                                                                                                                                |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 100 = 1:16 clock divide                                                                                                                                                |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 011 = 1:8  clock divide                                                                                                                                                |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 010 = 1:4 clock divide<br>001 = 1:2 clock divide                                                                                                                       |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 000 = 1:1 clo                                                                                                                                                          |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

| bit 10-9      | OUTFNC<1:0>: QEI Module Output Function Mode Select bits                                                                                                               |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 11 = The CTNCMPx pin goes high when QEI1LEC $\geq$ POS1CNT $\geq$ QEI1GEC                                                                                              |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 10 = The CTNCMPx pin goes high when POS1CNT ≤ QEI1LEC                                                                                                                  |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 01 = The CTNCMPx pin goes high when POS1CNT ≥ QEI1GEC<br>00 = Output is disabled                                                                                       |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

| L:1 0         | •                                                                                                                                                                      |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

| bit 8         | SWPAB: Swap QEA and QEB Inputs bit                                                                                                                                     |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | <ol> <li>1 = QEAx and QEBx are swapped prior to quadrature decoder logic</li> <li>0 = QEAx and QEBx are not swapped</li> </ol>                                         |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

| bit 7         | HOMPOL: H                                                                                                                                                              | OMEx Input Po                                                                                             | larity Select bit |                   |                  |                 |       |  |  |  |  |

|               | 1 = Input is in                                                                                                                                                        |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

| bit 6         | 0 = Input is n                                                                                                                                                         |                                                                                                           | ty Soloot bit     |                   |                  |                 |       |  |  |  |  |

|               | IDXPOL: INDXx Input Polarity Select bit                                                                                                                                |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | <ul> <li>1 = Input is inverted</li> <li>0 = Input is not inverted</li> </ul>                                                                                           |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

| bit 5         | <b>QEBPOL:</b> QEBx Input Polarity Select bit                                                                                                                          |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 1 = Input is inverted                                                                                                                                                  |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 0 = Input is not inverted                                                                                                                                              |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

| bit 4         | QEAPOL: Q                                                                                                                                                              | EAx Input Polar                                                                                           | ity Select bit    |                   |                  |                 |       |  |  |  |  |

|               | 1 = Input is i                                                                                                                                                         |                                                                                                           |                   |                   |                  |                 |       |  |  |  |  |

|               | 0 = Input is r                                                                                                                                                         | not inverted                                                                                              |                   |                   |                  |                 |       |  |  |  |  |

| bit 3         | HOME: Statu                                                                                                                                                            | <ul> <li>Input is not inverted</li> <li>HOME: Status of HOMEx Input Pin After Polarity Control</li> </ul> |                   |                   |                  |                 |       |  |  |  |  |

| DIL 3         | <b>HOME</b> . Statu                                                                                                                                                    |                                                                                                           | out Pin Alter Po  | bianty Control    |                  |                 |       |  |  |  |  |

| DIL 3         | 1 = Pin is at<br>0 = Pin is at                                                                                                                                         | logic '1'                                                                                                 | out Pin Aiter Po  | bianty Control    |                  |                 |       |  |  |  |  |

# REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER

| R-0                                                                  | R-0              | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                                              |

|----------------------------------------------------------------------|------------------|------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                      |                  | TERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                                                  |

|                                                                      |                  |                              |                                                    |                                                                                                |                                                                                           | bit 8                                                                                                                                            |

|                                                                      |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                                                  |

| R-0                                                                  | R-0              | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                                              |

|                                                                      |                  | RERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                                                  |

|                                                                      |                  |                              |                                                    |                                                                                                |                                                                                           | bit 0                                                                                                                                            |

|                                                                      |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                                                  |

|                                                                      |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                                                  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                                                  |

| OR                                                                   | '1' = Bit is set |                              | '0' = Bit is cleared x = Bit is unknow             |                                                                                                |                                                                                           |                                                                                                                                                  |

|                                                                      | R-0              | R-0 R-0<br>it W = Writable b | TERR<br>R-0 R-0 R-0<br>RERR<br>it W = Writable bit | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT<7:0> | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT | TERRCNT<7:0>           R-0         R-0         R-0         R-0           RERRCNT<7:0>         Revenue         U = Unimplemented bit, read as '0' |

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

| bit 7-6 | SJW<1:0>: Synchronization Jump Width bits    |

|---------|----------------------------------------------|

|         | 11 = Length is 4 x TQ                        |

|         | $10 = \text{Length is } 3 \times \text{Tq}$  |

|         | $01 = \text{Length is } 2 \times \text{T} Q$ |

|         | $00 = \text{Length is } 1 \times \text{Tq}$  |

```

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

```

```

11 1111 = TQ = 2 x 64 x 1/FCAN

```

•

- 00 0010 = TQ = 2 x 3 x 1/FCAN 00 0001 = TQ = 2 x 2 x 1/FCAN

- 00 0000 = Tq = 2 x 1 x 1/FCAN

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-x         | R/W-x                                                                         | R/W-x                                           | R/W-x         | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |  |

|---------------|-------------------------------------------------------------------------------|-------------------------------------------------|---------------|------------------------------------|-------|--------------------|-------|--|--|--|--|

| EID5          | EID4                                                                          | EID3                                            | EID2          | EID1                               | EID0  | RTR                | RB1   |  |  |  |  |

| bit 15        |                                                                               |                                                 |               |                                    |       |                    | bit 8 |  |  |  |  |

|               |                                                                               |                                                 |               |                                    |       |                    |       |  |  |  |  |

| U-x           | U-x                                                                           | U-x                                             | R/W-x         | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |  |

| —             | —                                                                             | _                                               | RB0           | DLC3                               | DLC2  | DLC1               | DLC0  |  |  |  |  |

| bit 7         |                                                                               |                                                 |               |                                    |       |                    | bit 0 |  |  |  |  |

| Lonondi       |                                                                               |                                                 |               |                                    |       |                    |       |  |  |  |  |

| Legend:       | l. h.:.                                                                       |                                                 | L.11          |                                    |       | -l (O)             |       |  |  |  |  |

| R = Readab    |                                                                               | W = Writable                                    |               | U = Unimplemented bit, read as '0' |       |                    |       |  |  |  |  |

| -n = Value a  | t POR                                                                         | '1' = Bit is set                                |               | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |  |  |  |

|               |                                                                               |                                                 |               |                                    |       |                    |       |  |  |  |  |

| bit 15-10     | EID<5:0>: E                                                                   | xtended Identifi                                | er bits       |                                    |       |                    |       |  |  |  |  |

| bit 9         | RTR: Remot                                                                    | RTR: Remote Transmission Request bit            |               |                                    |       |                    |       |  |  |  |  |

|               | When IDE = 1:                                                                 |                                                 |               |                                    |       |                    |       |  |  |  |  |

|               | •                                                                             | 1 = Message will request remote transmission    |               |                                    |       |                    |       |  |  |  |  |

|               |                                                                               | 0 = Normal message                              |               |                                    |       |                    |       |  |  |  |  |

|               |                                                                               | <u>When IDE = 0:</u><br>The RTR bit is ignored. |               |                                    |       |                    |       |  |  |  |  |

| <b>h</b> :+ 0 |                                                                               |                                                 |               |                                    |       |                    |       |  |  |  |  |

| bit 8         | <b>RB1:</b> Reserved Bit 1<br>User must set this bit to '0' per CAN protocol. |                                                 |               |                                    |       |                    |       |  |  |  |  |

|               |                                                                               |                                                 | -             | 0001.                              |       |                    |       |  |  |  |  |

| bit 7-5       | •                                                                             | nted: Read as '                                 | 0             |                                    |       |                    |       |  |  |  |  |

| bit 4         | RB0: Reserv                                                                   |                                                 | <b></b>       |                                    |       |                    |       |  |  |  |  |

|               | User must se                                                                  | et this bit to '0' p                            | per CAN proto | ocol.                              |       |                    |       |  |  |  |  |

| hit 2 0       |                                                                               | DIC 22:00 + Data Langth Cada hita               |               |                                    |       |                    |       |  |  |  |  |

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

#### BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x                | R/W-x | R/W-x            | R/W-x            | R/W-x                              | R/W-x                | R/W-x | R/W-x              |  |

|----------------------|-------|------------------|------------------|------------------------------------|----------------------|-------|--------------------|--|

|                      |       |                  | Ву               | /te 1                              |                      |       |                    |  |

| bit 15               |       |                  |                  |                                    |                      |       | bit 8              |  |

| R/W-x                | R/W-x | R/W-x            | R/W-x            | R/W-x                              | R/W-x                | R/W-x | R/W-x              |  |