Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp504-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

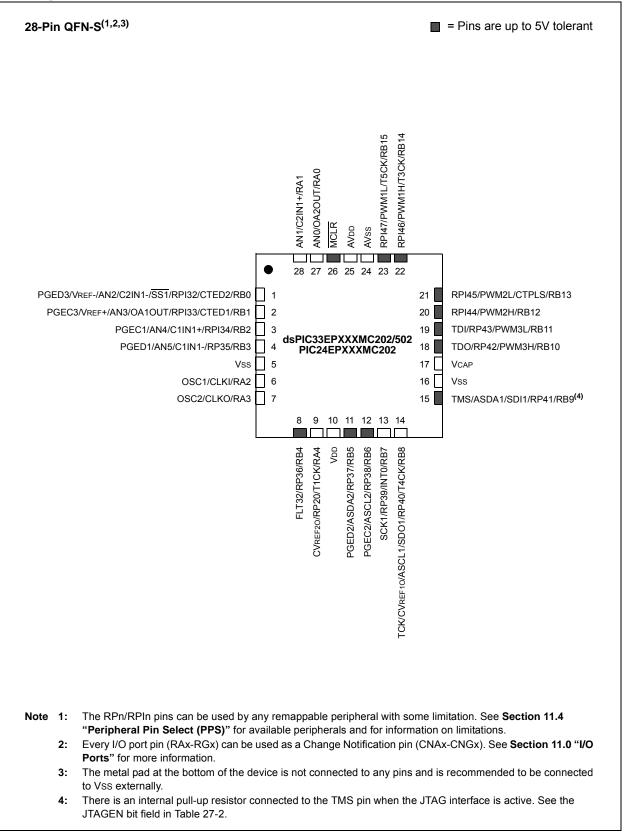

## Pin Diagrams (Continued)

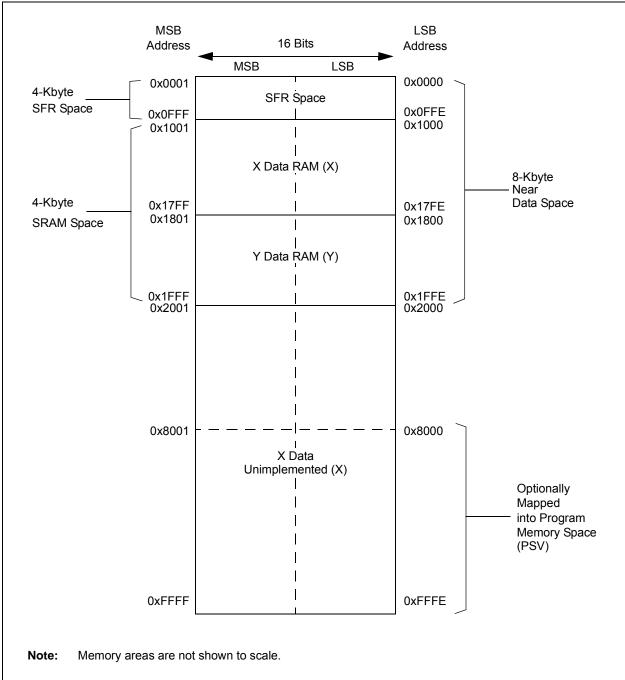

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

## TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

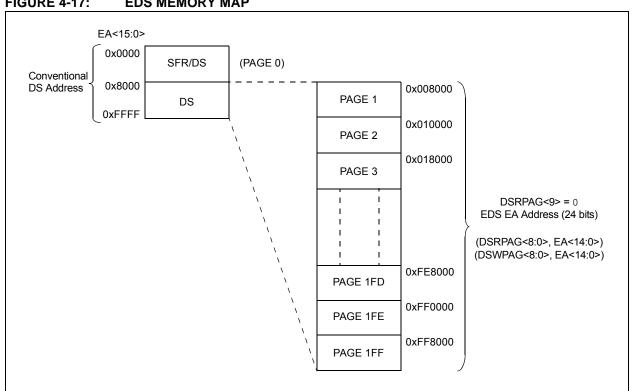

### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

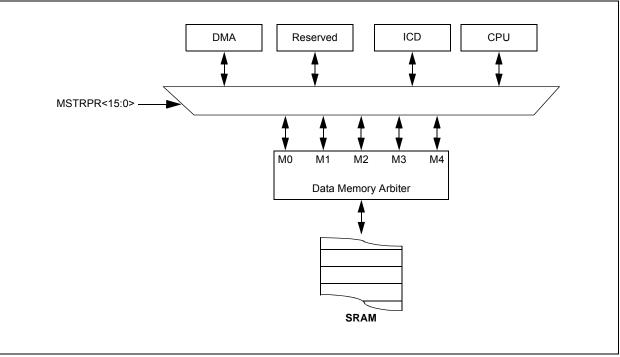

## 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

## FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

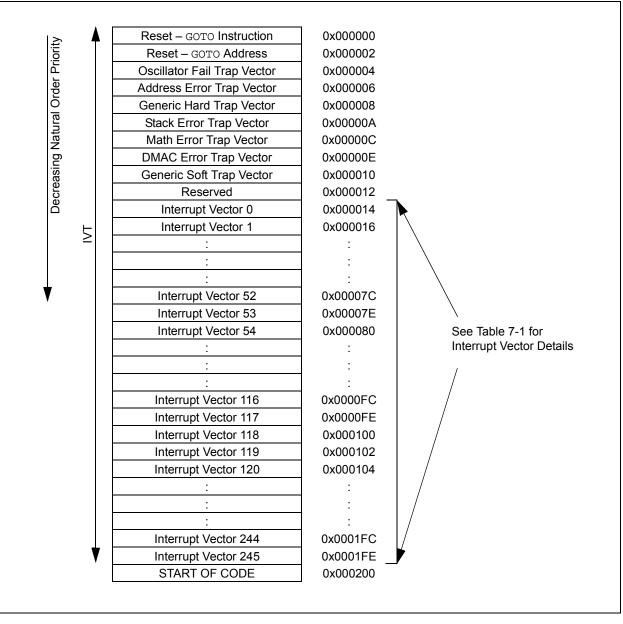

### FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

|                                                     | Vector  | IRQ        |                   | Inte     | errupt Bit L | ocation      |

|-----------------------------------------------------|---------|------------|-------------------|----------|--------------|--------------|

| Interrupt Source                                    | #       | #          | IVT Address       | Flag     | Enable       | Priority     |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _        | _            | _            |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —        | _            | —            |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —        | _            | —            |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —        | _            | —            |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14> | IEC5<14>     | IPC23<10:8>  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15> | IEC5<15>     | IPC23<14:12> |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>  | IEC6<0>      | IPC24<2:0>   |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —        | _            | —            |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14> | IEC8<14>     | IPC35<10:8>  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15> | IEC8<15>     | IPC35<14:12> |

| Reserved                                            | 152     | 144        | 0x000134          | —        | —            | _            |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>  | IEC9<1>      | IPC36<6:4>   |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>  | IEC9<2>      | IPC36<10:8>  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>  | IEC9<3>      | IPC36<14:12> |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>  | IEC9<4>      | IPC37<2:0>   |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>  | IEC9<5>      | IPC37<6:4>   |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>  | IEC9<6>      | IPC37<10:8>  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —        | —            | _            |

|                                                     | Lowe    | est Natura | I Order Priority  |          |              |              |

## TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —            |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15       |              |                                                          |               |                   |                 |                 | bit 8 |

|              |              |                                                          |               |                   |                 |                 |       |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7        |              |                                                          |               |                   |                 |                 | bit C |

|              |              |                                                          |               |                   |                 |                 |       |

| Legend:      |              |                                                          |               |                   |                 |                 |       |

| R = Readab   | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0      | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

## REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

## 13.2 Timer Control Registers

| R/W-0         | U-0                                                                               | R/W-0                              | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------|------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| TON           |                                                                                   | TSIDL                              | —              | _                |                 |                 | _     |  |  |  |  |  |

| bit 15        |                                                                                   |                                    |                |                  |                 |                 | bit 8 |  |  |  |  |  |

|               |                                                                                   |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| U-0           | R/W-0                                                                             | R/W-0                              | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |  |  |

| _             | TGATE                                                                             | TCKPS1                             | TCKPS0         | T32              | _               | TCS             | _     |  |  |  |  |  |

| bit 7         |                                                                                   |                                    |                |                  |                 |                 | bit ( |  |  |  |  |  |

| <u> </u>      |                                                                                   |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| Legend:       | - 1-:4                                                                            |                                    |                | II II.           |                 |                 |       |  |  |  |  |  |

| R = Readable  |                                                                                   | W = Writable                       |                | -                | nented bit, rea |                 |       |  |  |  |  |  |

| -n = Value at | PUR                                                                               | '1' = Bit is set                   |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15        | TON: Timerx                                                                       | On hit                             |                |                  |                 |                 |       |  |  |  |  |  |

|               | When T32 = 2                                                                      |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = Starts 32-                                                                    | bit Timerx/y                       |                |                  |                 |                 |       |  |  |  |  |  |

|               | 0 = Stops 32-                                                                     |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | <u>When T32 = 0</u><br>1 = Starts 16-                                             |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 0 = Stops 16-                                                                     |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| bit 14        | Unimplemen                                                                        | Unimplemented: Read as '0'         |                |                  |                 |                 |       |  |  |  |  |  |

| bit 13        | TSIDL: Timer                                                                      | x Stop in Idle M                   | lode bit       |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                   | ues module op                      |                |                  | dle mode        |                 |       |  |  |  |  |  |

|               |                                                                                   | s module opera                     |                | ode              |                 |                 |       |  |  |  |  |  |

| bit 12-7      | -                                                                                 | ted: Read as '                     |                |                  |                 |                 |       |  |  |  |  |  |

| bit 6         |                                                                                   | erx Gated Time                     | Accumulation   | Enable bit       |                 |                 |       |  |  |  |  |  |

|               | When TCS =<br>This bit is igno                                                    |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | When TCS = 0:                                                                     |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = Gated time accumulation is enabled<br>0 = Gated time accumulation is disabled |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                   |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| bit 5-4       |                                                                                   | : Timerx Input                     | Clock Prescal  | e Select bits    |                 |                 |       |  |  |  |  |  |

|               | 11 = 1:256<br>10 = 1:64                                                           |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 01 = 1:8                                                                          |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 00 = 1:1                                                                          |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| bit 3         | T32: 32-Bit Ti                                                                    | mer Mode Sele                      | ect bit        |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                   | nd Timery form<br>nd Timery act as |                |                  |                 |                 |       |  |  |  |  |  |

| bit 2         | Unimplemen                                                                        | ted: Read as '                     | )'             |                  |                 |                 |       |  |  |  |  |  |

| bit 1         | TCS: Timerx                                                                       | Clock Source S                     | elect bit      |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl                                                 | clock is from pir<br>lock (FP)     | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |  |  |  |

| bit 0         | Unimplomon                                                                        | ted: Read as '                     | ı'             |                  |                 |                 |       |  |  |  |  |  |

## REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-----------------|----------|-------|

| —               | —     |                  |       | DTR)                                    | <13:8>          |          |       |

| bit 15          |       |                  |       |                                         |                 |          | bit 8 |

|                 |       |                  |       |                                         |                 |          |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|                 |       |                  | DTR   | x<7:0>                                  |                 |          |       |

| bit 7           |       |                  |       |                                         |                 |          | bit 0 |

|                 |       |                  |       |                                         |                 |          |       |

| Legend:         |       |                  |       |                                         |                 |          |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimpler                            | nented bit, rea | d as '0' |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                 |          |       |

## REGISTER 16-10: DTRx: PWMx DEAD-TIME REGISTER

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0                               | U-0   | R/W-0            | R/W-0 | R/W-0                              | R/W-0   | R/W-0                                   | R/W-0 |  |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|---------|-----------------------------------------|-------|--|--|

| —                                 | _     |                  |       | ALTDTR                             | x<13:8> |                                         |       |  |  |

| bit 15                            |       |                  |       |                                    |         |                                         | bit 8 |  |  |

|                                   |       |                  |       |                                    |         |                                         |       |  |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0   | R/W-0                                   | R/W-0 |  |  |

|                                   |       |                  | ALTDT | Rx<7:0>                            |         |                                         |       |  |  |

| bit 7                             |       |                  |       |                                    |         |                                         | bit 0 |  |  |

| Legend:                           |       |                  |       |                                    |         |                                         |       |  |  |

| R = Readable bit W = Writable bit |       |                  | oit   | U = Unimplemented bit, read as '0' |         |                                         |       |  |  |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is clea                  | red     | '0' = Bit is cleared x = Bit is unknown |       |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0                  | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|------------------------|-------|

|                 |       |                  | INDXH | LD<15:8>         |                 |                        |       |

| bit 15          |       |                  |       |                  |                 |                        | bit 8 |

|                 |       |                  |       |                  |                 |                        |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0                  | R/W-0 |

|                 |       |                  | INDXF | ILD<7:0>         |                 |                        |       |

| bit 7           |       |                  |       |                  |                 |                        | bit 0 |

| Legend:         |       |                  |       |                  |                 |                        |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | ad as '0'              |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | red x = Bit is unknown |       |

## REGISTER 17-10: INDX1HLD: INDEX COUNTER 1 HOLD REGISTER

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDX1CNTH bits

## REGISTER 17-11: QEI1ICH: QEI1 INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0                             | R/W-0            | R/W-0                            | R/W-0                                   | R/W-0                                                                                 | R/W-0                                                                                             | R/W-0                                                 |  |  |  |

|-----------------------------------|------------------|----------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

|                                   |                  | QEIIC                            | <31:24>                                 |                                                                                       |                                                                                                   |                                                       |  |  |  |

|                                   |                  |                                  |                                         |                                                                                       |                                                                                                   | bit 8                                                 |  |  |  |

|                                   |                  |                                  |                                         |                                                                                       |                                                                                                   |                                                       |  |  |  |

| R/W-0                             | R/W-0            | R/W-0                            | R/W-0                                   | R/W-0                                                                                 | R/W-0                                                                                             | R/W-0                                                 |  |  |  |

|                                   |                  | QEIIC                            | <23:16>                                 |                                                                                       |                                                                                                   |                                                       |  |  |  |

|                                   |                  |                                  |                                         |                                                                                       |                                                                                                   | bit 0                                                 |  |  |  |

|                                   |                  |                                  |                                         |                                                                                       |                                                                                                   |                                                       |  |  |  |

|                                   |                  |                                  |                                         |                                                                                       |                                                                                                   |                                                       |  |  |  |

| R = Readable bit W = Writable bit |                  |                                  |                                         | U = Unimplemented bit, read as '0'                                                    |                                                                                                   |                                                       |  |  |  |

| OR                                | '1' = Bit is set |                                  | '0' = Bit is cleared x = Bit is unknown |                                                                                       |                                                                                                   | nown                                                  |  |  |  |

|                                   | R/W-0            | R/W-0 R/W-0<br>it W = Writable I | QEIIC<br>R/W-0 R/W-0 QEIIC<br>QEIIC     | QEIIC<31:24><br>R/W-0 R/W-0 R/W-0<br>QEIIC<23:16><br>it W = Writable bit U = Unimplen | QEIIC<31:24>   R/W-0 R/W-0 R/W-0   QEIIC<23:16>   it W = Writable bit U = Unimplemented bit, real | QEIIC<31:24>   R/W-0 R/W-0 R/W-0 R/W-0   QEIIC<23:16> |  |  |  |

bit 15-0 **QEIIC<31:16>:** High Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

#### REGISTER 17-12: QEI1ICL: QEI1 INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0             | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------------|-------|-------|-------------------|------------------------------------|-------|-------|-------|--|--|

|                                    |       |       | QEII              | C<15:8>                            |       |       |       |  |  |

| bit 15                             |       |       |                   |                                    |       |       | bit 8 |  |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0             | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                    |       |       | QEI               | C<7:0>                             |       |       |       |  |  |

| bit 7                              |       |       |                   |                                    |       |       | bit C |  |  |

| Legend:                            |       |       |                   |                                    |       |       |       |  |  |

| R = Readable bit W = Writable bit  |       |       | bit               | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is clea | x = Bit is unknown                 |       |       |       |  |  |

bit 15-0 **QEIIC<15:0>:** Low Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

## 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                       | U-0              | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |

|---------------|---------------------------|------------------|---------------|------------------|------------------|-----------------|-------|

|               | —                         |                  | SID10         | SID9             | SID8             | SID7            | SID6  |

| bit 15        |                           |                  |               |                  |                  |                 | bit 8 |

| R/W-x         | R/W-x                     | R/W-x            | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |

| SID5          | SID4                      | SID3             | SID2          | SID1             | SID0             | SRR             | IDE   |

| bit 7         |                           | •                |               |                  |                  |                 | bit 0 |

| Legend:       |                           |                  |               |                  |                  |                 |       |

| R = Readabl   | e bit                     | W = Writable     | bit           | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value at | POR                       | '1' = Bit is set |               | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|               |                           |                  |               |                  |                  |                 |       |

| bit 15-13     | Unimplemen                | ted: Read as '   | כי            |                  |                  |                 |       |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S | tandard Identifi | ier bits      |                  |                  |                 |       |

| bit 1         | SRR: Substitu             | ute Remote Re    | quest bit     |                  |                  |                 |       |

|               | When IDE =                | ):               |               |                  |                  |                 |       |

|               | 1 = Message               | will request rer | note transmis | ssion            |                  |                 |       |

|               | 0 = Normal m              | lessage          |               |                  |                  |                 |       |

|               | When IDE = 1              | L:               |               |                  |                  |                 |       |

|               | The SRR bit r             | must be set to ' | 1'.           |                  |                  |                 |       |

| bit 0         | IDE: Extende              | d Identifier bit |               |                  |                  |                 |       |

|               | 1 = Message               | will transmit Ex | tended Ident  | ifier            |                  |                 |       |

|               |                           | will transmit St |               |                  |                  |                 |       |

|               |                           |                  |               |                  |                  |                 |       |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0               | U-0   | U-0              | U-0   | R/W-x                              | R/W-x | R/W-x              | R/W-x |

|-------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|

| —                 | —     | —                |       | EID17                              | EID16 | EID15              | EID14 |

| bit 15            |       |                  |       |                                    |       |                    | bit 8 |

|                   |       |                  |       |                                    |       |                    |       |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |

| EID13             | EID12 | EID11            | EID10 | EID9                               | EID8  | EID7               | EID6  |

| bit 7             |       |                  |       |                                    |       |                    | bit 0 |

|                   |       |                  |       |                                    |       |                    |       |

| Legend:           |       |                  |       |                                    |       |                    |       |

| R = Readable      | bit   | W = Writable bit |       | U = Unimplemented bit, read as '0' |       |                    |       |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |

| L                 |       |                  |       |                                    |       |                    |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

| REGISTER 24-6: | PTGSDLIM: PTG STEP DELAY LIMIT REGISTER <sup>(1,2)</sup> |

|----------------|----------------------------------------------------------|

|                |                                                          |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|

|                                   |       |                  | PTGSD | LIM<15:8>                          |       |                 |       |  |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |  |

|                                   |       |                  |       |                                    |       |                 |       |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|                                   |       |                  | PTGSE | )LIM<7:0>                          |       |                 |       |  |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |  |

|                                   |       |                  |       |                                    |       |                 |       |  |

| Legend:                           |       |                  |       |                                    |       |                 |       |  |

| R = Readable bit W = Writable bit |       |                  |       | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |  |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

**Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|-----------------------------------|-------|-------|-------|------------------------------------|-------|-----------------|-------|--|

|                                   |       |       | PTGC0 | LIM<15:8>                          |       |                 |       |  |

| bit 15                            |       |       |       |                                    |       |                 | bit 8 |  |

|                                   |       |       |       |                                    |       |                 |       |  |

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|                                   |       |       | PTGC  | )LIM<7:0>                          |       |                 |       |  |

| bit 7                             |       |       |       |                                    |       |                 | bit 0 |  |

|                                   |       |       |       |                                    |       |                 |       |  |

| Legend:                           |       |       |       |                                    |       |                 |       |  |

| R = Readable bit W = Writable bit |       |       | it    | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at POR '1' = Bit is    |       |       |       | '0' = Bit is clea                  | ared  | x = Bit is unki | nown  |  |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

| U-0          | U-0                           | U-0                | U-0              | U-0              | U-0              | U-0            | U-0    |  |  |  |  |

|--------------|-------------------------------|--------------------|------------------|------------------|------------------|----------------|--------|--|--|--|--|

|              | —                             | —                  | _                | —                |                  | —              | _      |  |  |  |  |

| bit 15       |                               |                    |                  |                  |                  |                | bit    |  |  |  |  |

|              |                               |                    |                  |                  |                  |                |        |  |  |  |  |

| U-0          | R/W-0                         | R/W-0              | R/W-0            | R/W-0            | R/W-0            | R/W-0          | R/W-0  |  |  |  |  |

|              | CFSEL2                        | CFSEL1             | CFSEL0           | CFLTREN          | CFDIV2           | CFDIV1         | CFDIV0 |  |  |  |  |

| bit 7        |                               |                    |                  |                  |                  |                | bit    |  |  |  |  |

| Legend:      |                               |                    |                  |                  |                  |                |        |  |  |  |  |

| R = Readab   | le bit                        | W = Writable       | bit              | U = Unimpler     | mented bit, read | as '0'         |        |  |  |  |  |

| -n = Value a |                               | '1' = Bit is set   |                  | '0' = Bit is cle |                  | x = Bit is unk | nown   |  |  |  |  |

|              |                               |                    |                  |                  |                  |                | -      |  |  |  |  |

| bit 15-7     | Unimplemen                    | ted: Read as       | ʻ0'              |                  |                  |                |        |  |  |  |  |

| oit 6-4      | CFSEL<2:0>                    | : Comparator       | Filter Input Clo | ock Select bits  |                  |                |        |  |  |  |  |

|              | 111 = T5CLK                   |                    | ·                |                  |                  |                |        |  |  |  |  |

|              | 110 = T4CLK                   |                    |                  |                  |                  |                |        |  |  |  |  |

|              | 101 = T3CLK                   | ( <sup>(1)</sup>   |                  |                  |                  |                |        |  |  |  |  |

|              | 100 = T2CLK                   | <mark>(</mark> (2) |                  |                  |                  |                |        |  |  |  |  |

|              |                               | 011 = Reserved     |                  |                  |                  |                |        |  |  |  |  |

|              | 010 = SYNC                    | 01 <sup>(3)</sup>  |                  |                  |                  |                |        |  |  |  |  |

|              | 001 = Fosc <sup>(4</sup>      | 1)                 |                  |                  |                  |                |        |  |  |  |  |

|              | 000 = FP <sup>(4)</sup>       |                    |                  |                  |                  |                |        |  |  |  |  |

| bit 3        |                               | comparator Filt    | er Enable bit    |                  |                  |                |        |  |  |  |  |

|              | 1 = Digital filter is enabled |                    |                  |                  |                  |                |        |  |  |  |  |

|              | •                             | er is disabled     |                  |                  |                  |                |        |  |  |  |  |

| bit 2-0      | CFDIV<2:0>:                   | : Comparator F     | ilter Clock Div  | vide Select bits |                  |                |        |  |  |  |  |

|              | 111 = Clock                   | Divide 1:128       |                  |                  |                  |                |        |  |  |  |  |

|              | 110 = Clock                   | Divide 1:64        |                  |                  |                  |                |        |  |  |  |  |

|              | 101 = Clock                   | Divide 1:32        |                  |                  |                  |                |        |  |  |  |  |

|              | 100 = Clock                   | Divide 1:16        |                  |                  |                  |                |        |  |  |  |  |

|              | 011 = Clock                   |                    |                  |                  |                  |                |        |  |  |  |  |

|              | 010 = Clock                   |                    |                  |                  |                  |                |        |  |  |  |  |

|              | 001 = Clock                   |                    |                  |                  |                  |                |        |  |  |  |  |

|              | 000 = Clock                   | Divide 1:1         |                  |                  |                  |                |        |  |  |  |  |

| Note 1: S    | See the Type C Ti             | mer Block Diag     | gram (Figure 1   | 3-2).            |                  |                |        |  |  |  |  |

|              | See the Type B Tir            |                    |                  |                  |                  |                |        |  |  |  |  |

| •            |                               |                    |                  |                  |                  |                |        |  |  |  |  |

## REGISTER 25-6: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

- 3: See the High-Speed PWMx Module Register Interconnection Diagram (Figure 16-2).

- 4: See the Oscillator System Diagram (Figure 9-1).

| Field                                                                                                                                                                                                                                                         | Description                                                                                                                                                                                                                                           |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Wm,Wn                                                                                                                                                                                                                                                         | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                                           |  |  |  |  |  |

| Wm*Wm                                                                                                                                                                                                                                                         | Multiplicand and Multiplier working register pair for Square instructions $\in$ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                     |  |  |  |  |  |

| Wm*Wn                                                                                                                                                                                                                                                         | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                         |  |  |  |  |  |

| Wn                                                                                                                                                                                                                                                            | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                 |  |  |  |  |  |

| Wnd                                                                                                                                                                                                                                                           | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                     |  |  |  |  |  |

| Wns                                                                                                                                                                                                                                                           | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                          |  |  |  |  |  |

| WREG                                                                                                                                                                                                                                                          | W0 (working register used in file register instructions)                                                                                                                                                                                              |  |  |  |  |  |

| Ws                                                                                                                                                                                                                                                            | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                          |  |  |  |  |  |

| Wso                                                                                                                                                                                                                                                           | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                       |  |  |  |  |  |

| Wx                                                                                                                                                                                                                                                            | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none} |  |  |  |  |  |

| Wxd                                                                                                                                                                                                                                                           | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                              |  |  |  |  |  |

| WyY Data Space Prefetch Address register for DSP instructions<br>$\in \{[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - [W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = [W11 + W12], none}$ |                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Wyd                                                                                                                                                                                                                                                           | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                              |  |  |  |  |  |

| TABLE 28-1: | SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED) | ) |

|-------------|-------------------------------------------------|---|

|             | ······································          | , |

| AC CH                              | ARACTEI | RISTICS                                              | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |         |                                   |            |                                                                                               |  |

|------------------------------------|---------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------|------------|-----------------------------------------------------------------------------------------------|--|

| Param<br>No. Symbol Characteristic |         | Min.                                                 | Тур.                                                                                                                                                                                                                                                                                            | Max.    | Units                             | Conditions |                                                                                               |  |

|                                    |         |                                                      | Devi                                                                                                                                                                                                                                                                                            | ce Sup  | ply                               |            |                                                                                               |  |

| AD01                               | AVDD    | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or 3.0                                                                                                                                                                                                                                                              |         | Lesser of:<br>VDD + 0.3<br>or 3.6 | V          |                                                                                               |  |

| AD02                               | AVss    | Module Vss Supply                                    | Vss – 0.3                                                                                                                                                                                                                                                                                       |         | Vss + 0.3                         | V          |                                                                                               |  |

|                                    |         |                                                      | Refere                                                                                                                                                                                                                                                                                          | ence In | puts                              |            |                                                                                               |  |

| AD05                               | Vrefh   | Reference Voltage High                               | AVss + 2.5                                                                                                                                                                                                                                                                                      |         | AVDD                              | V          | VREFH = VREF+<br>VREFL = VREF- <b>(Note 1)</b>                                                |  |

| AD05a                              |         |                                                      | 3.0                                                                                                                                                                                                                                                                                             | _       | 3.6                               | V          | VREFH = AVDD<br>VREFL = AVSS = 0                                                              |  |

| AD06                               | VREFL   | Reference Voltage Low                                | AVss                                                                                                                                                                                                                                                                                            |         | AVDD - 2.5                        | V          | (Note 1)                                                                                      |  |

| AD06a                              |         |                                                      | 0                                                                                                                                                                                                                                                                                               |         | 0                                 | V          | VREFH = AVDD<br>VREFL = AVSS = 0                                                              |  |

| AD07                               | VREF    | Absolute Reference<br>Voltage                        | 2.5                                                                                                                                                                                                                                                                                             | _       | 3.6                               | V          | VREF = VREFH - VREFL                                                                          |  |

| AD08                               | IREF    | Current Drain                                        |                                                                                                                                                                                                                                                                                                 |         | 10<br>600                         | μΑ<br>μΑ   | ADC off<br>ADC on                                                                             |  |

| AD09                               | Iad     | Operating Current <sup>(2)</sup>                     | —                                                                                                                                                                                                                                                                                               | 5       | _                                 | mA         | ADC operating in 10-bit mode (Note 1)                                                         |  |

|                                    |         |                                                      | —                                                                                                                                                                                                                                                                                               | 2       | —                                 | mA         | ADC operating in 12-bit mode (Note 1)                                                         |  |

|                                    | •       |                                                      | Ana                                                                                                                                                                                                                                                                                             | log Inp | ut                                |            | •                                                                                             |  |

| AD12                               | Vinh    | Input Voltage Range<br>VinH                          | VINL                                                                                                                                                                                                                                                                                            |         | Vrefh                             | V          | This voltage reflects Sample-and-<br>Hold Channels 0, 1, 2 and 3<br>(CH0-CH3), positive input |  |

| AD13                               | VINL    | Input Voltage Range<br>VINL                          | Vrefl                                                                                                                                                                                                                                                                                           | _       | AVss + 1V                         | V          | This voltage reflects Sample-and-<br>Hold Channels 0, 1, 2 and 3<br>(CH0-CH3), negative input |  |

| AD17                               | Rin     | Recommended<br>Impedance of Analog<br>Voltage Source | _                                                                                                                                                                                                                                                                                               | _       | 200                               | Ω          | Impedance to achieve maximum<br>performance of ADC                                            |  |

## TABLE 30-57: ADC MODULE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: Parameter is characterized but not tested in manufacturing.

## 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |