Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Dectano                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp504-h-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

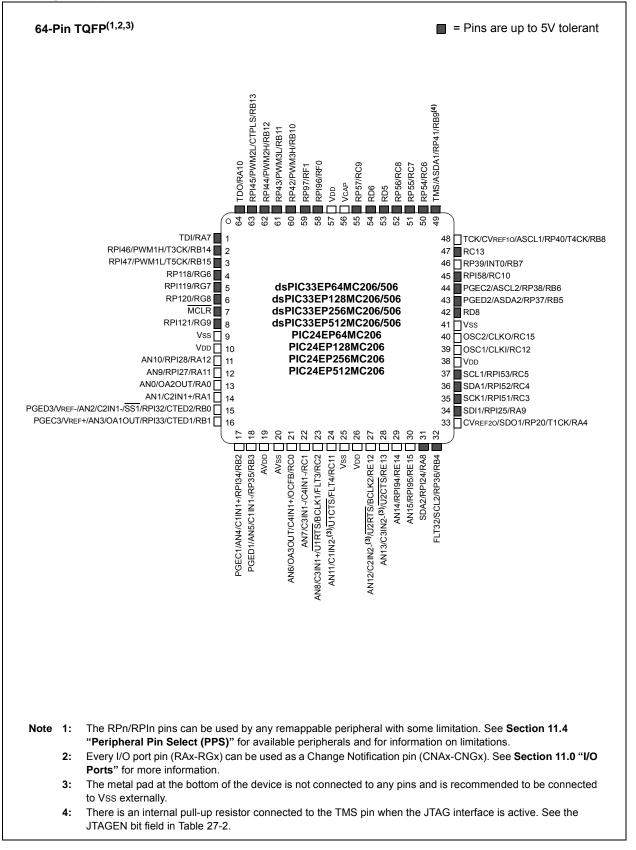

# Pin Diagrams (Continued)

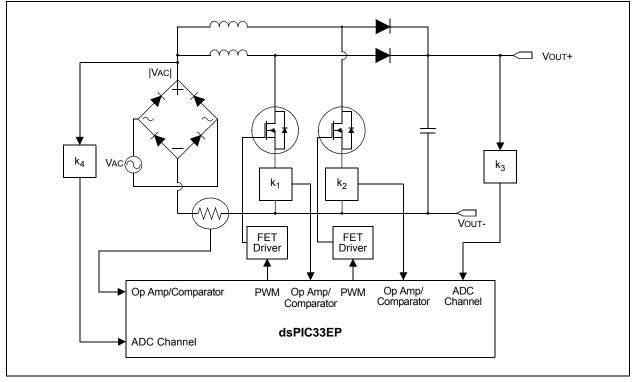

#### FIGURE 2-7: INTERLEAVED PFC

#### 4.2.5 X AND Y DATA SPACES

# The dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXXGP/MC20X devices.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

# 4.3 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 4.3.1 KEY RESOURCES

- "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

# TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8 | Bit 7 | Bit 6 | Bit 5     | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|-----------------------|-------|-------|-------|-----------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | —       | —      | —       | —      | —      | —      | —                     | _     |       |       |           | I2C1 Recei   | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202  | _       | _      | _       | _      | —      | _      | —                     | _     |       |       |           | I2C1 Transi  | mit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204  | _       | _      | _       | _      | _      | _      | _                     |       |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                | SMEN  | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                | ADD10 | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      |                       |       |       |       | I2C1 Addr | ess Register | r            |       |       |       | 0000          |

| I2C1MSK      | 020C  | _       | _      | _       | _      | _      | _      |                       |       |       |       | I2C1 Add  | dress Mask   |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | _       | _      | _       | _      | _      | _      | _                     | _     |       |       |           | I2C2 Recei   | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | _       | _      | _       | _      | _      | _      | _                     | _     |       |       |           | I2C2 Transi  | mit Register |       |       |       | OOFF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | _      | _                     |       |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                | SMEN  | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT                | ADD10 | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | _       | _      | —      | _      |                       |       |       |       | I2C2 Addr | ess Register | r            |       |       |       | 0000          |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | -      | I2C2 Address Mask 000 |       |       |       |           |              | 0000         |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14                                                                               | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7      | Bit 6    | Bit 5 | Bit 4      | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|--------------------------------------------------------------------------------------|----------|--------|--------|--------|-------|----------|------------|----------|-------|------------|----------|-------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | —                                                                                    | USIDL    | IREN   | RTSMD  | _      | UEN<  | :1:0>    | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV                                                                               | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        | _                                                                                    | _        | _      | _      | _      | _     |          |            |          | UART1 | Transmit F | Register |       |        |       | xxxx          |

| U1RXREG     | 0226  | _        | _                                                                                    | _        | _      | _      | _      | _     |          |            |          | UART  | Receive R  | legister |       |        |       | 0000          |

| U1BRG       | 0228  |          |                                                                                      |          |        |        |        | Baud  | Rate Gen | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

| U2MODE      | 0230  | UARTEN   | _                                                                                    | USIDL    | IREN   | RTSMD  | _      | UEN<  | :1:0>    | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV                                                                               | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _                                                                                    | _        | _      | _      | _      | _     |          |            |          | UART2 | Transmit F | Register |       |        |       | xxxx          |

| U2RXREG     | 0236  | _        | —         —         —         —         —         UART2 Receive Register         000 |          |        |        |        |       |          |            | 0000     |       |            |          |       |        |       |               |

| U2BRG       | 0238  |          |                                                                                      |          |        |        |        | Baud  | Rate Gen | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR de | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        |        |        | INT1R<6:0> |        |       |       | _     | _     | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1       | 06A2  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       |       | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ٦     | [2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  |        |        |        |        | IC2R<6:0>  |        |       |       | _     |       |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  |        |        |        |        | IC4R<6:0>  |        |       |       | _     |       |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |        |        | S      | CK2INR<6:0 | )>     |       |       | _     |       |       | :     | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      | _      | —      | —          | _      | _     | —     | —     |       |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26      | 06D4  | —      | _      | _      | -      | _          | _      | —     |       | —     |       |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14       | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------------|--------------|--------|------------|--------|-------|-------|-------|------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |              |              |        | INT1R<6:0> |        |       |       | —     | —          | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1    | 06A2  |        | _            | _            | _      | _          | _      | _     | _     | _     |            |       |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3    | 06A6  |        | _            |              |        |            |        |       |       | _     | T2CKR<6:0> |       |       |            |       |       | 0000  |               |

| RPINR7    | 06AE  |        |              | IC2R<6:0>    |        |            |        |       |       | _     |            |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8    | 06B0  |        |              |              |        | IC4R<6:0>  |        |       |       | _     |            |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11   | 06B6  |        | _            | _            | _      | _          | _      | _     | _     | _     |            |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12   | 06B8  |        |              | FLT2R<6:0>   |        |            |        |       |       | _     | FLT1R<6:0> |       |       |            |       |       |       | 0000          |

| RPINR14   | 06BC  |        |              |              | (      | QEB1R<6:0  | >      |       |       | _     |            |       | (     | QEA1R<6:0  | >     |       |       | 0000          |

| RPINR15   | 06BE  |        |              |              | Н      | OME1R<6:0  | )>     |       |       | _     |            |       | I     | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18   | 06C4  |        | _            | _            | _      | _          | _      | _     | _     | _     | U1RXR<6:0> |       |       |            |       |       |       | 0000          |

| RPINR19   | 06C6  |        | _            | _            | _      | _          | _      | _     | _     | _     |            |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22   | 06CC  | _      |              |              | S      | CK2INR<6:( | )>     |       |       | —     |            |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —            | —            |        | —          | —      |       | —     | —     |            |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      |              |              |        |            |        |       | —     | —     |            |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      | SYNCI1R<6:0> |              |        |            |        |       | —     | —     | —          | —     | —     |            |       |       | 0000  |               |

| RPINR38   | 06EC  | _      | DTCMP1R<6:0> |              |        |            |        |       | —     |       |            |       |       |            |       | 0000  |       |               |

| RPINR39   | 06EE  | _      |              | DTCMP3R<6:0> |        |            |        |       |       | _     |            |       | D     | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0          | U-0          | U-0                                                                                                                       | U-0           | U-0                | U-0      | U-0    | U-0    |  |  |  |  |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------|---------------|--------------------|----------|--------|--------|--|--|--|--|

| —            | —            | —                                                                                                                         | —             | —                  | —        | —      | —      |  |  |  |  |

| bit 15       |              |                                                                                                                           |               |                    |          |        | bit 8  |  |  |  |  |

|              |              |                                                                                                                           |               |                    |          |        |        |  |  |  |  |

| U-0          | U-0          | U-0                                                                                                                       | U-0           | R-0                | R-0      | R-0    | R-0    |  |  |  |  |

|              |              | <u> </u>                                                                                                                  | _             | PWCOL3             | PWCOL2   | PWCOL1 | PWCOL0 |  |  |  |  |

| bit 7        |              |                                                                                                                           |               |                    |          |        | bit 0  |  |  |  |  |

|              |              |                                                                                                                           |               |                    |          |        |        |  |  |  |  |

| Legend:      |              |                                                                                                                           |               |                    |          |        |        |  |  |  |  |

| R = Readab   | le bit       |                                                                                                                           |               |                    |          |        |        |  |  |  |  |

| -n = Value a | t POR        | OR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown                                                                  |               |                    |          |        |        |  |  |  |  |

|              |              |                                                                                                                           |               |                    |          |        |        |  |  |  |  |

| bit 15-4     | Unimplemen   | ted: Read as '                                                                                                            | 0'            |                    |          |        |        |  |  |  |  |

| bit 3        | PWCOL3: DI   | MA Channel 3 F                                                                                                            | Peripheral Wi | rite Collision Fla | ag bit   |        |        |  |  |  |  |

|              |              | lision is detecte                                                                                                         |               |                    |          |        |        |  |  |  |  |

|              |              | collision is dete                                                                                                         |               |                    |          |        |        |  |  |  |  |

| bit 2        |              |                                                                                                                           | •             | rite Collision Fla | ag bit   |        |        |  |  |  |  |

|              |              | lision is detecte                                                                                                         |               |                    |          |        |        |  |  |  |  |

| bit 1        |              | <ul> <li>0 = No write collision is detected</li> <li>PWCOL1: DMA Channel 1 Peripheral Write Collision Flag bit</li> </ul> |               |                    |          |        |        |  |  |  |  |

| DILI         |              | lision is detecte                                                                                                         | •             |                    |          |        |        |  |  |  |  |

|              |              | collision is dete                                                                                                         |               |                    |          |        |        |  |  |  |  |

| bit 0        | PWCOL0: DI   | MA Channel 0 F                                                                                                            | Peripheral Wi | rite Collision Fla | ag bit   |        |        |  |  |  |  |

|              |              | lision is detecte                                                                                                         | •             | -                  | <b>č</b> |        |        |  |  |  |  |

|              | 0 = No write | collision is dete                                                                                                         | ected         |                    |          |        |        |  |  |  |  |

|              |              |                                                                                                                           |               |                    |          |        |        |  |  |  |  |

# REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

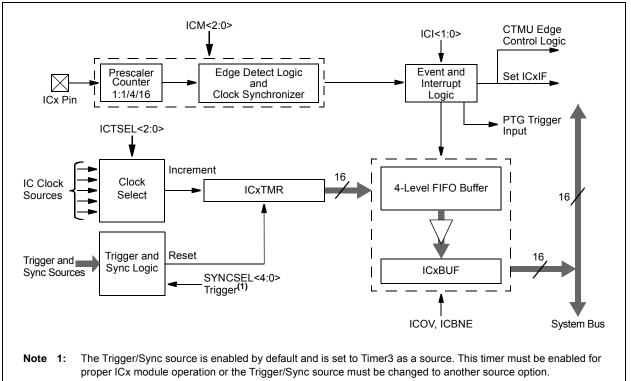

# 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|       | R/W-0            | R/W-0           | R/W-0                                 | R/W-0                                                            | R/W-0                                                                                                | R/W-0                                                                                                    |

|-------|------------------|-----------------|---------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|       |                  | QEIG            | EC<31:24>                             |                                                                  |                                                                                                      |                                                                                                          |

|       |                  |                 |                                       |                                                                  |                                                                                                      | bit 8                                                                                                    |

|       | DAMO             |                 |                                       |                                                                  | DAMO                                                                                                 |                                                                                                          |

| R/W-U | R/W-0            |                 |                                       | R/W-U                                                            | R/W-U                                                                                                | R/W-0                                                                                                    |

|       |                  | QEIGE           | EC<23:16>                             |                                                                  |                                                                                                      |                                                                                                          |

|       |                  |                 |                                       |                                                                  |                                                                                                      | bit (                                                                                                    |

|       |                  |                 |                                       |                                                                  |                                                                                                      |                                                                                                          |

|       | W = Writable bi  | t               | U = Unimplem                          | nented bit, rea                                                  | d as '0'                                                                                             |                                                                                                          |

| २     | '1' = Bit is set |                 | '0' = Bit is clea                     | ared                                                             | x = Bit is unkn                                                                                      | iown                                                                                                     |

|       | R/W-0            | W = Writable bi | R/W-0 R/W-0 QEIGI<br>W = Writable bit | R/W-0 R/W-0 R/W-0 QEIGEC<23:16><br>W = Writable bit U = Unimplem | R/W-0     R/W-0     R/W-0       QEIGEC<23:16>       W = Writable bit     U = Unimplemented bit, real | R/W-0       R/W-0       R/W-0       R/W-0         QEIGEC<23:16>       U = Unimplemented bit, read as '0' |

#### REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

#### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | QEIGE | C<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | QEIG  | EC<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | AMSK9 | AMSK8 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| AMSK7  | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7  |       |       |       |       |       |       | bit 0 |

#### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2CxMSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

NOTES:

#### 25.1 Op Amp Application Considerations

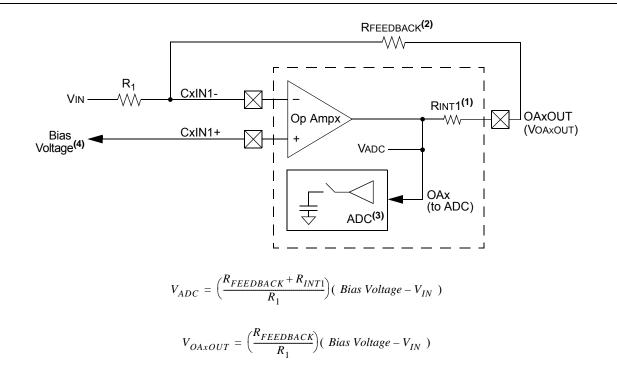

There are two configurations to take into consideration when designing with the op amp modules that available in the dsPIC33EPXXXGP50X. are dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices. Configuration A (see Figure 25-6) takes advantage of the internal connection to the ADC module to route the output of the op amp directly to the ADC for measurement. Configuration B (see Figure 25-7) requires that the designer externally route the output of the op amp (OAxOUT) to a separate analog input pin (ANy) on the device. Table 30-55 in Section 30.0 "Electrical Characteristics" describes the performance characteristics for the op amps, distinguishing between the two configuration types where applicable.

#### 25.1.1 OP AMP CONFIGURATION A

Figure 25-6 shows a typical inverting amplifier circuit taking advantage of the internal connections from the op amp output to the input of the ADC. The advantage of this configuration is that the user does not need to consume another analog input (ANy) on the device, and allows the user to simultaneously sample all three op amps with the ADC module, if needed. However, the presence of the internal resistance, RINT1, adds an error in the feedback path. Since RINT1 is an internal resistance, in relation to the op amp output (VOAXOUT) and ADC internal connection (VADC), RINT1 must be included in the numerator term of the transfer function. See Table 30-53 in Section 30.0 "Electrical Characteristics" for the typical value of RINT1. Table 30-60 and Table 30-61 in Section 30.0 "Electrical Characteristics" describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration. Figure 25-6 also defines the equations that should be used when calculating the expected voltages at points, VADC and VOAXOUT.

#### FIGURE 25-6: OP AMP CONFIGURATION A

Note 1: See Table 30-53 for the Typical value.

- 2: See Table 30-53 for the Minimum value for the feedback resistor.

- 3: See Table 30-60 and Table 30-61 for the minimum sample time (TSAMP).

- 4: CVREF10 or CVREF20 are two options that are available for supplying bias voltage to the op amps.

# REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

bit 3 ABEN: AND Gate B Input Enable bit 1 = MBI is connected to AND gate 0 = MBI is not connected to AND gate bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate 0 = Inverted MBI is not connected to AND gate bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to AND gate 0 = MAI is not connected to AND gate bit 0 AANEN: AND Gate A Input Inverted Enable bit 1 = Inverted MAI is connected to AND gate 0 = Inverted MAI is not connected to AND gate

# 27.6 JTAG Interface

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |

|-------|----------------------------------------------|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |

|       | Reference Manual" for further information    |

|       | on usage, configuration and operation of the |

|       | JTAG interface.                              |

# 27.7 In-Circuit Serial Programming

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

# 27.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

# 27.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X, and PIC24EPXXXGP/MC20X devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to "CodeGuard<sup>™</sup> Security" (DS70634) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

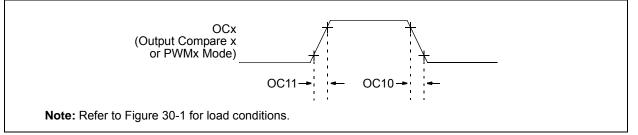

# FIGURE 30-7: OUTPUT COMPARE x MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 30-27: OUTPUT COMPARE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |      |       |                    |  |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           | Min. | Тур. | Max. | Units | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time                                                                                                                                                                                                                                                                    | _    |      | _    | ns    | See Parameter DO32 |  |

| OC11               | TccR   | OCx Output Rise Time                                                                                                                                                                                                                                                                    | _    | _    | —    | ns    | See Parameter DO31 |  |

Note 1: These parameters are characterized but not tested in manufacturing.

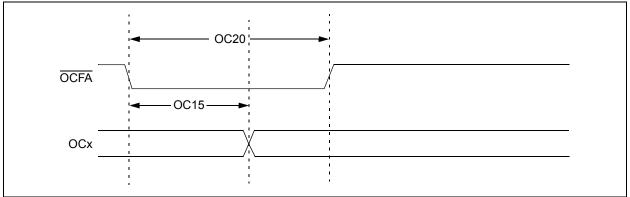

#### FIGURE 30-8: OCx/PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 30-28: OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |          |      |          |       |            |

|--------------------|--------|-------------------------------------------------------|----------|------|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                         | Min.     | Тур. | Max.     | Units | Conditions |

| OC15               | TFD    | Fault Input to PWMx I/O<br>Change                     | —        | _    | Tcy + 20 | ns    |            |

| OC20               | TFLT   | Fault Input Pulse Width                               | TCY + 20 |      | —        | ns    |            |

**Note 1:** These parameters are characterized but not tested in manufacturing.

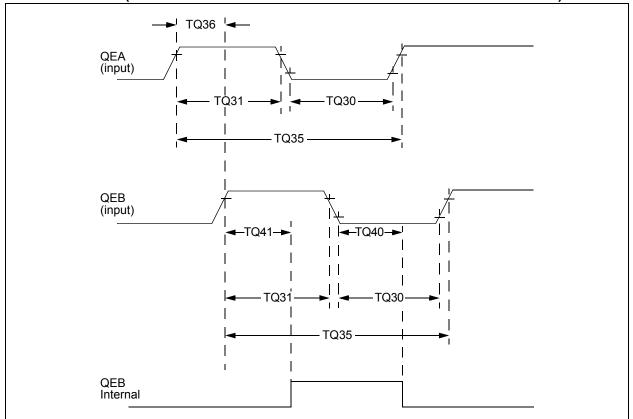

#### FIGURE 30-12: QEA/QEB INPUT CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

# TABLE 30-31: QUADRATURE DECODER TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                    |                          |   |       |                                                         |  |

|--------------------|--------|----------------------------------------------------|--------------------------|---|-------|---------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                      | Typ. <sup>(2)</sup> Max. |   | Units | Conditions                                              |  |

| TQ30               | TQUL   | Quadrature Input Low Time                          | 6 Tcy                    |   | ns    |                                                         |  |

| TQ31               | TQUH   | Quadrature Input High Time                         | 6 Tcy                    | — | ns    |                                                         |  |

| TQ35               | TQUIN  | Quadrature Input Period                            | 12 TCY                   | _ | ns    |                                                         |  |

| TQ36               | TQUP   | Quadrature Phase Period                            | 3 TCY                    | — | ns    |                                                         |  |

| TQ40               | TQUFL  | Filter Time to Recognize Low, with Digital Filter  | 3 * N * Tcy              | — | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |  |

| TQ41               | TQUFH  | Filter Time to Recognize High, with Digital Filter | 3 * N * Tcy              | — | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: N = Index Channel Digital Filter Clock Divide Select bits. Refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "*dsPIC33/PIC24 Family Reference Manual*". Please see the Microchip web site for the latest family reference manual sections.

| AC CHARACTERISTICS |                       |                                                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |         |       |       |                                         |

|--------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-----------------------------------------|

| Param<br>No.       | Symbol Characteristic |                                                                                                           | Min.                                                                                                                                                                                                                                                                                        | Тур.    | Max.  | Units | Conditions                              |

|                    | -                     | Cloci                                                                                                     | k Paramet                                                                                                                                                                                                                                                                                   | ters    |       |       | ·                                       |

| AD50               | TAD                   | ADC Clock Period                                                                                          | 117.6                                                                                                                                                                                                                                                                                       | _       | _     | ns    |                                         |

| AD51               | tRC                   | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                          |                                                                                                                                                                                                                                                                                             | 250     | _     | ns    |                                         |

|                    |                       | Conv                                                                                                      | version R                                                                                                                                                                                                                                                                                   | ate     |       |       |                                         |

| AD55               | tCONV                 | Conversion Time                                                                                           | _                                                                                                                                                                                                                                                                                           | 14 Tad  |       | ns    |                                         |

| AD56               | FCNV                  | Throughput Rate                                                                                           | _                                                                                                                                                                                                                                                                                           | _       | 500   | ksps  |                                         |

| AD57a              | TSAMP                 | Sample Time when Sampling any ANx Input                                                                   | 3 Tad                                                                                                                                                                                                                                                                                       | —       | _     |       |                                         |

| AD57b              | TSAMP                 | Sample Time when Sampling the Op<br>Amp Outputs (Configuration A and<br>Configuration B) <sup>(4,5)</sup> | 3 Tad                                                                                                                                                                                                                                                                                       | —       | -     |       |                                         |

|                    |                       | Timin                                                                                                     | g Parame                                                                                                                                                                                                                                                                                    | ters    |       |       |                                         |

| AD60               | tPCS                  | Conversion Start from Sample<br>Trigger <sup>(2,3)</sup>                                                  | 2 Tad                                                                                                                                                                                                                                                                                       | -       | 3 Tad | —     | Auto-convert trigger is<br>not selected |

| AD61               | tPSS                  | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2,3)</sup>                                           | 2 Tad                                                                                                                                                                                                                                                                                       | —       | 3 Tad |       |                                         |

| AD62               | tcss                  | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2,3)</sup>                                      |                                                                                                                                                                                                                                                                                             | 0.5 Tad | —     |       |                                         |

| AD63               | tdpu                  | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup>                                 | —                                                                                                                                                                                                                                                                                           | —       | 20    | μS    | (Note 6)                                |

# TABLE 30-60: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- **6:** The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

# TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                 | Update Description                                                                                                                                                       |  |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Section 30.0 "Electrical<br>Characteristics" | Removed Voltage on VCAP with respect to Vss and added Note 5 in Absolute Maximum Ratings <sup>(1)</sup> .                                                                |  |  |  |  |  |

|                                              | Removed Parameter DC18 (VCORE) and Note 3 from the DC Temperature and Voltage Specifications (see Table 30-4).                                                           |  |  |  |  |  |

|                                              | Updated Note 1 in the DC Characteristics: Operating Current (IDD) (see Table 30-6).                                                                                      |  |  |  |  |  |

|                                              | Updated Note 1 in the DC Characteristics: Idle Current (IIDLE) (see Table 30-7).                                                                                         |  |  |  |  |  |

|                                              | Changed the Typical values for Parameters DC60a-DC60d and updated Note 1 in the DC Characteristics: Power-down Current (IPD) (see Table 30-8).                           |  |  |  |  |  |

|                                              | Updated Note 1 in the DC Characteristics: Doze Current (IDOZE) (see Table 30-9).                                                                                         |  |  |  |  |  |

|                                              | Updated Note 2 in the Electrical Characteristics: BOR (see Table 30-12).                                                                                                 |  |  |  |  |  |

|                                              | Updated Parameters CM20 and CM31, and added Parameters CM44 and CM45 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                  |  |  |  |  |  |

|                                              | Added the Op amp/Comparator Reference Voltage Settling Time Specifications (see Table 30-15).                                                                            |  |  |  |  |  |

|                                              | Added Op amp/Comparator Voltage Reference DC Specifications (see Table 30-16).                                                                                           |  |  |  |  |  |

|                                              | Updated Internal FRC Accuracy Parameter F20a (see Table 30-21).                                                                                                          |  |  |  |  |  |

|                                              | Updated the Typical value and Units for Parameter CTMUI1, and added Parameters CTMUI4, CTMUFV1, and CTMUFV2 to the CTMU Current Source Specifications (see Table 30-55). |  |  |  |  |  |

| Section 31.0 "Packaging<br>Information"      | Updated packages by replacing references of VLAP with TLA.                                                                                                               |  |  |  |  |  |

| "Product Identification<br>System"           | Changed VLAP to TLA.                                                                                                                                                     |  |  |  |  |  |

# **Revision F (November 2012)**

Removed "Preliminary" from data sheet footer.

# **Revision G (March 2013)**

This revision includes the following global changes:

- changes "FLTx" pin function to "FLTx" on all occurrences

- adds Section 31.0 "High-Temperature Electrical Characteristics" for high-temperature (+150°C) data

This revision also includes minor typographical and formatting changes throughout the text.

Other major changes are referenced by their respective section in Table A-5.

| Section Name                                                         | Update Description                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cover Section                                                        | <ul> <li>Changes internal oscillator specification to 1.0%</li> <li>Changes I/O sink/source values to 12 mA or 6 mA</li> <li>Corrects 44-pin VTLA pin diagram (pin 32 now shows as 5V tolerant)</li> </ul>                                                                                                                                                                           |

| Section 4.0 "Memory<br>Organization"                                 | <ul> <li>Deletes references to Configuration Shadow registers</li> <li>Corrects the spelling of the JTAGIP and PTGWDTIP bits throughout</li> <li>Corrects the Reset value of all IOCON registers as C000h</li> <li>Adds footnote to Table 4-42 to indicate the absence of Comparator 3 in 28-pin devices</li> </ul>                                                                  |

| Section 6.0 "Resets"                                                 | <ul> <li>Removes references to cold and warm Resets, and clarifies the initial configuration of<br/>the device clock source on all Resets</li> </ul>                                                                                                                                                                                                                                 |

| Section 7.0 "Interrupt<br>Controller"                                | Corrects the definition of GIE as "Global Interrupt Enable" (not "General")                                                                                                                                                                                                                                                                                                          |

| Section 9.0 "Oscillator<br>Configuration"                            | <ul> <li>Clarifies the behavior of the CF bit when cleared in software</li> <li>Removes POR behavior footnotes from all control registers</li> <li>Corrects the tuning range of the TUN&lt;5:0&gt; bits in Register 9-4 to an overall range ±1.5%</li> </ul>                                                                                                                         |

| Section 13.0 "Timer2/3 and Timer4/5"                                 | <ul> <li>Clarifies the presence of the ADC Trigger in 16-bit Timer3 and Timer5, as well as the<br/>32-bit timers</li> </ul>                                                                                                                                                                                                                                                          |

| Section 15.0 "Output<br>Compare"                                     | <ul> <li>Corrects the first trigger source for SYNCSEL&lt;4:0&gt; (OCxCON2&lt;4:0&gt;) as OCxRS<br/>match</li> </ul>                                                                                                                                                                                                                                                                 |

| Section 16.0 "High-Speed<br>PWM Module"                              | <ul> <li>Clarifies the source of the PWM interrupts in Figure 16-1</li> <li>Corrects the Reset states of IOCONx&lt;15:14&gt; in Register 16-13 as '11'</li> </ul>                                                                                                                                                                                                                    |

| Section 17.0 "Quadrature<br>Encoder Interface (QEI)<br>Module"       | <ul> <li>Clarifies the operation of the IMV&lt;1:0&gt; bits (QEICON&lt;9:8&gt;) with updated text and additional notes</li> <li>Corrects the first prescaler value for QFVDIV&lt;2:0&gt; (QEI10C&lt;13:11&gt;), now 1:128</li> </ul>                                                                                                                                                 |

| Section 23.0 "10-Bit/12-Bit<br>Analog-to-Digital Converter<br>(ADC)" | <ul> <li>Adds note to Figure 23-1 that Op Amp 3 is not available in 28-pin devices</li> <li>Changes "sample clock" to "sample trigger" in AD1CON1 (Register 23-1)</li> <li>Clarifies footnotes on op amp usage in Registers 23-5 and 23-6</li> </ul>                                                                                                                                 |

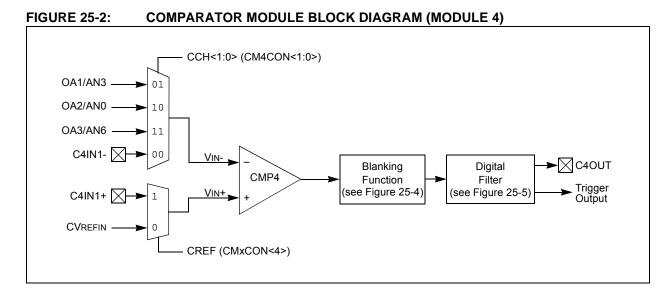

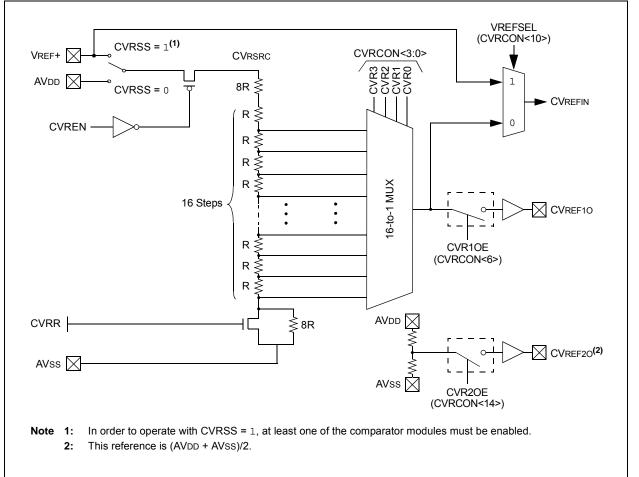

| Section 25.0 "Op Amp/<br>Comparator Module"                          | <ul> <li>Adds Note text to indicate that Comparator 3 is unavailable in 28-pin devices</li> <li>Splits Figure 25-1 into two figures for clearer presentation (Figure 25-1 for Op amp/<br/>Comparators 1 through 3, Figure 25-2 for Comparator 4). Subsequent figures are<br/>renumbered accordingly.</li> <li>Corrects reference description in xxxxx (now (AVDD+AVSS)/2)</li> </ul> |

| Section 27.0 "Special Features"                                      | <ul> <li>Changes CMSTAT&lt;15&gt; in Register 25-1 to "PSIDL"</li> <li>Corrects the addresses of all Configuration bytes for 512 Kbyte devices</li> </ul>                                                                                                                                                                                                                            |

#### TABLE A-5: MAJOR SECTION UPDATES

# TABLE A-5: MAJOR SECTION UPDATES (CONTINUED)