Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 44-QFN (8x8)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp504t-e-ml |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

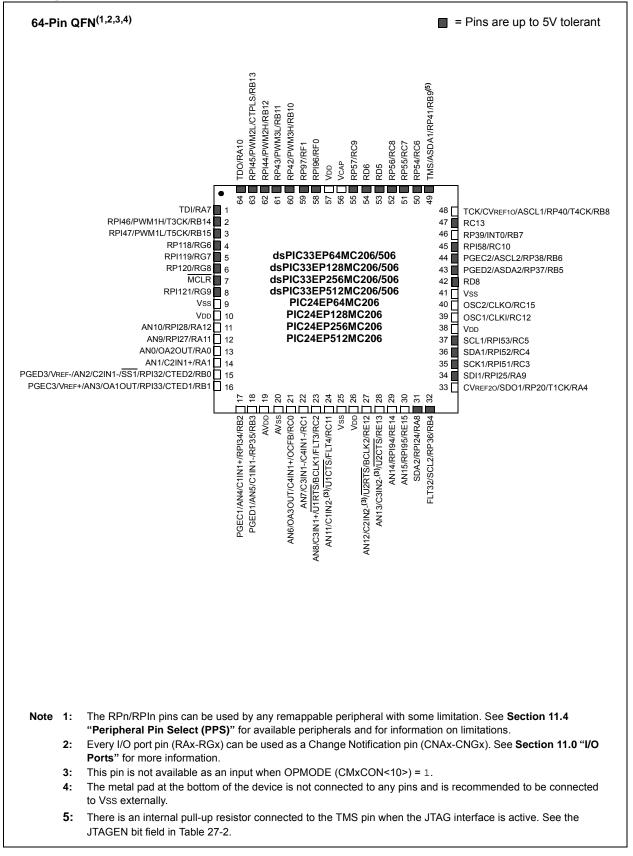

### Pin Diagrams (Continued)

| IABLE 4-2  | 1: E  | ECANTI  | REGIST    |         | WHEN    |                        | TOTRE   | 1<0>) =   | 0 OR . | L FOR asi        | PIC33E    | PXXXIV             | IC/GP5  |        | ICES O   | NLY      |        |               |

|------------|-------|---------|-----------|---------|---------|------------------------|---------|-----------|--------|------------------|-----------|--------------------|---------|--------|----------|----------|--------|---------------|

| File Name  | Addr. | Bit 15  | Bit 14    | Bit 13  | Bit 12  | Bit 11                 | Bit 10  | Bit 9     | Bit 8  | Bit 7            | Bit 6     | Bit 5              | Bit 4   | Bit 3  | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

| C1CTRL1    | 0400  | _       | —         | CSIDL   | ABAT    | CANCKS                 | R       | EQOP<2:0  | >      | OPM              | /IODE<2:0 | >                  | —       | CANCAP | —        | —        | WIN    | 0480          |

| C1CTRL2    | 0402  | _       | _         | —       | _       | _                      | _       | —         | _      | —                | _         | _                  |         | D      | NCNT<4:0 | >        |        | 0000          |

| C1VEC      | 0404  | _       | —         | —       |         | FILHIT<4:0>            |         |           |        | —                |           | ICODE<6:0>         |         |        |          |          | 0040   |               |

| C1FCTRL    | 0406  | C       | DMABS<2:0 | >       |         | _                      | —       | —         | _      | _                | _         | _                  |         |        | FSA<4:0> |          |        | 0000          |

| C1FIFO     | 0408  |         | —         |         |         | FBP<5:0> — — FNRB<5:0> |         |           |        |                  |           | 0000               |         |        |          |          |        |               |

| C1INTF     | 040A  |         | —         | TXBO    | TXBP    | RXBP                   | TXWAR   | RXWAR     | EWARN  | IVRIF            | WAKIF     | ERRIF              | _       | FIFOIF | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C  |         | —         | —       |         | _                      | —       | —         | _      | IVRIE            | WAKIE     | ERRIE              | _       | FIFOIE | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC       | 040E  |         |           |         | TERRCN  | T<7:0>                 |         |           |        | RERRCNT<7:0>     |           |                    |         |        |          | 0000     |        |               |

| C1CFG1     | 0410  | _       | _         | _       | _       | _                      | _       | _         | _      | SJW<1            | :0>       |                    |         | BRP    | <5:0>    |          |        | 0000          |

| C1CFG2     | 0412  | _       | WAKFIL    | _       | _       | _                      | SI      | =G2PH<2:( | )>     | SEG2PHTS         | SAM       | S                  | EG1PH<2 | :0>    | Р        | RSEG<2:0 | >      | 0000          |

| C1FEN1     | 0414  | FLTEN15 | FLTEN14   | FLTEN13 | FLTEN12 | FLTEN11                | FLTEN10 | FLTEN9    | FLTEN8 | FLTEN7           | FLTEN6    | FLTEN5             | FLTEN4  | FLTEN3 | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418  | F7MSł   | <<1:0>    | F6MSł   | <<1:0>  | F5MS                   | K<1:0>  | F4MS      | K<1:0> | F3MSK<1:0> F2MSI |           | SK<1:0> F1MSK<1:0> |         | F0MS   | <<1:0>   | 0000     |        |               |

| C1FMSKSEL2 | 041A  | F15MS   | K<1:0>    | F14MS   | K<1:0>  | F13MS                  | K<1:0>  | F12MS     | K<1:0> | F11MSK           | <1:0>     | F10MS              | K<1:0>  | F9MSk  | <<1:0>   | F8MSI    | <<1:0> | 0000          |

#### TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 OR 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-22: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

| File Name | Addr          | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8         | Bit 7        | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|---------|---------|---------|---------|---------|---------|---------------|--------------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E |         |         |         |         |         |         | S       | ee definition | when WIN     | = x     |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9  | RXFUL8        | RXFUL7       | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24       | RXFUL23      | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9  | RXOVF8        | RXOVF7       | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24       | RXOVF23      | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1   | TXABT1  | TXLARB1 | TXERR1  | TXREQ1  | RTREN1  | TX1PF   | RI<1:0>       | TXEN0        | TXABAT0 | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3   | TXABT3  | TXLARB3 | TXERR3  | TXREQ3  | RTREN3  | TX3PF   | RI<1:0>       | TXEN2        | TXABAT2 | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5   | TXABT5  | TXLARB5 | TXERR5  | TXREQ5  | RTREN5  | TX5PF   | RI<1:0>       | TXEN4        | TXABAT4 | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7   | TXABT7  | TXLARB7 | TXERR7  | TXREQ7  | RTREN7  | TX7PF   | RI<1:0>       | TXEN6        | TXABAT6 | TXLARB6 | TXERR6  | TXREQ6  | RTREN6  | TX6PF   | RI<1:0> | xxxx          |

| C1RXD     | 0440          |         |         |         |         |         |         | E       | CAN1 Rece     | eive Data Wo | ord     |         |         |         |         |         |         | xxxx          |

| C1TXD     | 0442          |         |         |         |         |         |         | E       | CAN1 Trans    | smit Data Wo | ord     |         |         |         |         |         |         | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

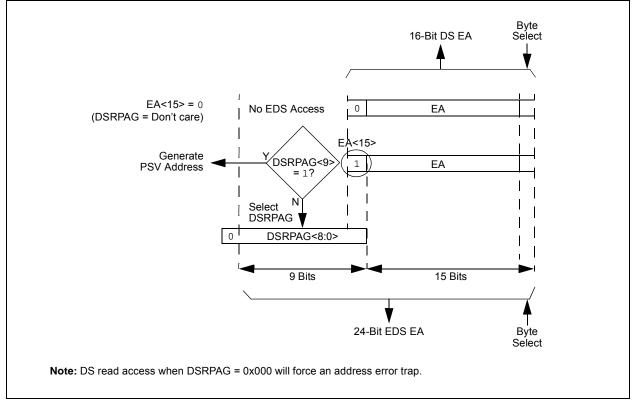

#### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

| U-0          | U-0                         | U-0                                          | U-0            | U-0              | U-0              | U-0             | U-0   |

|--------------|-----------------------------|----------------------------------------------|----------------|------------------|------------------|-----------------|-------|

| -            | —                           | —                                            | —              | —                | —                | —               | —     |

| bit 15       |                             |                                              |                |                  |                  |                 | bit 8 |

| U-0          | U-0                         | U-0                                          | U-0            | R-1              | R-1              | R-1             | R-1   |

| _            | _                           | _                                            | _              |                  | LSTC             | H<3:0>          |       |

| bit 7        |                             |                                              |                |                  |                  |                 | bit 0 |

| Legend:      |                             |                                              |                |                  |                  |                 |       |

| R = Readat   | ole bit                     | W = Writable                                 | bit            | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value a | at POR                      | '1' = Bit is set                             |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                             |                                              |                |                  |                  |                 |       |

| bit 15-4     | Unimplemen                  | ted: Read as '                               | 0'             |                  |                  |                 |       |

| bit 3-0      | LSTCH<3:0>                  | : Last DMAC C                                | hannel Active  | e Status bits    |                  |                 |       |

|              | 1111 = No DI<br>1110 = Rese | MA transfer has<br>rved                      | s occurred sir | nce system Res   | set              |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              |                             | rved<br>data transfer wa<br>data transfer wa |                |                  |                  |                 |       |

|              |                             | data transfer wa                             |                |                  |                  |                 |       |

### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0000 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      | —     |       |       | —          | —     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —      |       |       |       | U1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

#### REGISTER 11-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0' bit 6-0 U1RXR<6:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 . . . . . . . . . .

#### REGISTER 11-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| 0-0     | 0-0   | 0-0   | 0-0   | 0-0        | 0-0   | 0-0   | 0-0   |

|         | —     |       | _     | _          | —     | —     |       |

| bit 15  |       |       |       |            |       |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —       |       |       |       | U2RXR<6:0> | >     |       |       |

| bit 7   |       |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Legend: |       |       |       |            |       |       |       |

|         |       |       |       |            |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

<sup>0000000 =</sup> Input tied to Vss

| U-0             | U-0        | R/W-0                               | R/W-0 | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

|-----------------|------------|-------------------------------------|-------|--------------------------|------------------|-----------------|-------|

| —               | —          |                                     |       | RP57                     | R<5:0>           |                 |       |

| bit 15          |            |                                     |       |                          |                  |                 | bit 8 |

|                 |            |                                     |       |                          |                  |                 |       |

| U-0             | U-0        | R/W-0                               | R/W-0 | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

| _               | —          |                                     |       | RP56                     | R<5:0>           |                 |       |

| bit 7           |            |                                     |       |                          |                  |                 | bit 0 |

|                 |            |                                     |       |                          |                  |                 |       |

| Legend:         |            |                                     |       |                          |                  |                 |       |

| R = Readable I  | bit        | W = Writable                        | bit   | U = Unimplen             | nented bit, read | d as '0'        |       |

| -n = Value at P | OR         | '1' = Bit is set                    | :     | '0' = Bit is clea        | ared             | x = Bit is unkr | iown  |

|                 |            |                                     |       |                          |                  |                 |       |

| bit 15-14       | Unimplemen | ted: Read as '                      | 0'    |                          |                  |                 |       |

| bit 13-8        |            | : Peripheral Ou<br>-3 for periphera |       | is Assigned to<br>mbers) | RP57 Output F    | Pin bits        |       |

| bit 7-6         | Unimplemen | ted: Read as '                      | 0'    |                          |                  |                 |       |

### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

| REGISTE       | R 16-7: PWMC                            | CONX: PWMX (                                                                                                                      | CONTROL R      | EGISTER          |                      |                      |                     |  |  |  |

|---------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|--|--|--|

| HS/HC-        | 0 HS/HC-0                               | HS/HC-0                                                                                                                           | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>              | TRGSTAT                                                                                                                           | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |  |  |

| bit 15        | ·                                       | •                                                                                                                                 |                | ÷                |                      |                      | bit                 |  |  |  |

| R/W-0         | R/W-0                                   | R/W-0                                                                                                                             | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |

| DTC1          |                                         | DTCP <sup>(3)</sup>                                                                                                               | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |  |  |

| bit 7         | DICO                                    | DICE                                                                                                                              | _              | INT DO           | CAIM                 | AFRES'               | bit                 |  |  |  |

|               |                                         |                                                                                                                                   |                |                  |                      |                      | <u> </u>            |  |  |  |

| Legend:       |                                         | HC = Hardware                                                                                                                     | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |  |  |  |

| R = Reada     | able bit                                | W = Writable bi                                                                                                                   | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |  |  |  |

| -n = Value    | at POR                                  | '1' = Bit is set                                                                                                                  |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |  |  |  |

| bit 15        | ELTSTAT: ES                             | ult Interrupt Statu                                                                                                               | is hit(1)      |                  |                      |                      |                     |  |  |  |

| DIL 15        |                                         | rrupt is pending                                                                                                                  |                |                  |                      |                      |                     |  |  |  |

|               |                                         | interrupt is pendi                                                                                                                | ng             |                  |                      |                      |                     |  |  |  |

|               |                                         | ared by setting F                                                                                                                 |                |                  |                      |                      |                     |  |  |  |

| bit 14        |                                         | rent-Limit Interru                                                                                                                | •              |                  |                      |                      |                     |  |  |  |

|               |                                         | mit interrupt is pe                                                                                                               |                |                  |                      |                      |                     |  |  |  |

|               |                                         | 0 = No current-limit interrupt is pending<br>This bit is cleared by setting CLIEN = 0.                                            |                |                  |                      |                      |                     |  |  |  |

| bit 13        | TRGSTAT: Trigger Interrupt Status bit   |                                                                                                                                   |                |                  |                      |                      |                     |  |  |  |

|               | 1 = Trigger interrupt is pending        |                                                                                                                                   |                |                  |                      |                      |                     |  |  |  |

|               |                                         | r interrupt is pen                                                                                                                |                |                  |                      |                      |                     |  |  |  |

|               |                                         | ared by setting T                                                                                                                 |                |                  |                      |                      |                     |  |  |  |

| bit 12        |                                         | FLTIEN: Fault Interrupt Enable bit                                                                                                |                |                  |                      |                      |                     |  |  |  |

|               |                                         | rrupt is enabled rrupt is disabled                                                                                                | and the FLTS   | TAT bit is clear | ed                   |                      |                     |  |  |  |

| bit 11        |                                         | ent-Limit Interrup                                                                                                                |                |                  | cu .                 |                      |                     |  |  |  |

|               |                                         | mit interrupt is er                                                                                                               |                |                  |                      |                      |                     |  |  |  |

|               |                                         | mit interrupt is di                                                                                                               |                | e CLSTAT bit is  | s cleared            |                      |                     |  |  |  |

| bit 10        | TRGIEN: Trig                            | ger Interrupt En                                                                                                                  | able bit       |                  |                      |                      |                     |  |  |  |

|               |                                         | event generates                                                                                                                   |                |                  | T hit is cleared     |                      |                     |  |  |  |

| bit 9         |                                         | vent interrupts ar                                                                                                                |                |                  | i bit is cleared     |                      |                     |  |  |  |

| DIL 9         |                                         | <b>ITB:</b> Independent Time Base Mode bit <sup>(2)</sup><br>1 = PHASEx register provides time base period for this PWM generator |                |                  |                      |                      |                     |  |  |  |

|               |                                         | egister provides f                                                                                                                | •              |                  | •                    |                      |                     |  |  |  |

| bit 8         |                                         | er Duty Cycle Re                                                                                                                  |                |                  |                      |                      |                     |  |  |  |

|               |                                         | ister provides du<br>jister provides du                                                                                           |                |                  |                      | r                    |                     |  |  |  |

| Note 1:       | Software must clea                      |                                                                                                                                   |                |                  | -                    |                      | t controller        |  |  |  |

| Note 1.<br>2: | These bits should                       | -                                                                                                                                 |                | -                | -                    | the interrup         |                     |  |  |  |

| 3:            | DTC<1:0> = 11 fo                        | -                                                                                                                                 |                | -                | -                    |                      |                     |  |  |  |

| 4:            | The Independent T<br>CAM bit is ignored | Time Base (ITB =                                                                                                                  |                | •                |                      | igned mode. If       | TTB = 0, the        |  |  |  |

| 5:            | To operate in Exter                     |                                                                                                                                   | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |  |  |  |

### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

# REGISTER 16-13: IOCONX: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1 SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0 OSYNC: Output Override Synchronization bit

1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWMx period boundary

- 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

| U-0                         | U-0                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                               | R/W-0            | R/W-0             | R/W-0         |  |  |  |  |  |  |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|-------------------|---------------|--|--|--|--|--|--|--|--|

| _                           | _                                                                                                                                                                                                          | _                                                                                                                                                                                                                                              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BLANKSEL3                                                                                           | BLANKSEL2        | BLANKSEL1         | BLANKSEL      |  |  |  |  |  |  |  |  |

| bit 15                      | •                                                                                                                                                                                                          | •                                                                                                                                                                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •                                                                                                   |                  | •                 | bit 8         |  |  |  |  |  |  |  |  |

| U-0                         | U-0                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                               | R/W-0            | R/W-0             | R/W-0         |  |  |  |  |  |  |  |  |

|                             |                                                                                                                                                                                                            | CHOPSEL3                                                                                                                                                                                                                                       | CHOPSEL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHOPSEL1                                                                                            | CHOPSEL0         | CHOPHEN           | CHOPLEN       |  |  |  |  |  |  |  |  |

| bit 7                       |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  | onornen           | bit           |  |  |  |  |  |  |  |  |

|                             |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   |               |  |  |  |  |  |  |  |  |

| Legend:                     |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  | (0)               |               |  |  |  |  |  |  |  |  |

| R = Readab                  |                                                                                                                                                                                                            | W = Writable                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                   | ented bit, read  |                   |               |  |  |  |  |  |  |  |  |

| -n = Value a                | at POR                                                                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '0' = Bit is clea                                                                                   | red              | x = Bit is unkr   | nown          |  |  |  |  |  |  |  |  |

| bit 15-12                   | Unimplemen                                                                                                                                                                                                 | ted: Read as '                                                                                                                                                                                                                                 | D'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                     |                  |                   |               |  |  |  |  |  |  |  |  |

| bit 11-8                    | -                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | urce Select bits                                                                                    |                  |                   |               |  |  |  |  |  |  |  |  |

|                             | The selected                                                                                                                                                                                               | state blank sig                                                                                                                                                                                                                                | nal will block t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | he current-limit                                                                                    | and/or Fault inp | out signals (if e | nabled via th |  |  |  |  |  |  |  |  |

|                             | BCH and BCI                                                                                                                                                                                                | The selected state blank signal will block the current-limit and/or Fault input signals (if enabled via the BCH and BCL bits in the LEBCONx register).                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   |               |  |  |  |  |  |  |  |  |

|                             | 1001 <b>= Rese</b>                                                                                                                                                                                         | rved                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   |               |  |  |  |  |  |  |  |  |

|                             |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   |               |  |  |  |  |  |  |  |  |

|                             |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     | •                |                   |               |  |  |  |  |  |  |  |  |

|                             | •                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   |               |  |  |  |  |  |  |  |  |

|                             | •<br>•<br>0100 = Rese                                                                                                                                                                                      | rved                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   |               |  |  |  |  |  |  |  |  |

|                             | •<br>•<br>0100 = Rese<br>0011 = PWM                                                                                                                                                                        | rved<br>3H selected as                                                                                                                                                                                                                         | state blank so                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ource                                                                                               |                  |                   |               |  |  |  |  |  |  |  |  |

|                             | 0011 = PWM<br>0010 = PWM                                                                                                                                                                                   | 3H selected as 2H selected as                                                                                                                                                                                                                  | state blank so                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ource                                                                                               |                  |                   |               |  |  |  |  |  |  |  |  |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM                                                                                                                                                                     | 3H selected as<br>2H selected as<br>1H selected as                                                                                                                                                                                             | state blank so                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ource                                                                                               |                  |                   |               |  |  |  |  |  |  |  |  |

| hit 7-6                     | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st                                                                                                                                                     | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking                                                                                                                                                                             | state blank so<br>state blank so                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ource                                                                                               |                  |                   |               |  |  |  |  |  |  |  |  |

|                             | 0011 = PWM<br>0010 = PWM<br>0001 = PWM<br>0000 = No st<br>Unimplemen                                                                                                                                       | 3H selected as<br>2H selected as<br>1H selected as<br>ate blanking<br>ted: Read as '                                                                                                                                                           | state blank so<br>state blank so<br>o'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | burce<br>burce                                                                                      |                  |                   |               |  |  |  |  |  |  |  |  |