Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 44-VTLA (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp504t-e-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0 | U-0             | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|-----------------|-------|--------------|------------------|--------|-------|

| —              | —   | —               | —     | —            | —                | -      | —     |

| bit 15         |     |                 |       |              |                  |        | bit 8 |

|                |     |                 |       |              |                  |        |       |

| R-0            | R-0 | R-0             | R-0   | R-0          | R-0              | R-0    | R-0   |

|                |     |                 | DSADR | <23:16>      |                  |        |       |

| bit 7          |     |                 |       |              |                  |        | bit 0 |

|                |     |                 |       |              |                  |        |       |

| Legend:        |     |                 |       |              |                  |        |       |

| R = Readable b | it  | W = Writable bi | t     | U = Unimpler | nented bit, read | as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0              | R-0 | R-0              | R-0                                           | R-0            | R-0         | R-0       | R-0   |

|------------------|-----|------------------|-----------------------------------------------|----------------|-------------|-----------|-------|

|                  |     |                  | DSAD                                          | DR<15:8>       |             |           |       |

| bit 15           |     |                  |                                               |                |             |           | bit 8 |

|                  |     |                  |                                               |                |             |           |       |

| R-0              | R-0 | R-0              | R-0                                           | R-0            | R-0         | R-0       | R-0   |

|                  |     |                  | DSA                                           | DR<7:0>        |             |           |       |

| bit 7            |     |                  |                                               |                |             |           | bit 0 |

|                  |     |                  |                                               |                |             |           |       |

| Legend:          |     |                  |                                               |                |             |           |       |

| R = Readable b   | it  | W = Writable bit |                                               | U = Unimplemen | ted bit, re | ad as '0' |       |

| -n = Value at PC | OR  | '1' = Bit is set | s set '0' = Bit is cleared x = Bit is unknown |                |             |           |       |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

NOTES:

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —            |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15       |              |                                                          |               |                   |                 |                 | bit 8 |

|              |              |                                                          |               |                   |                 |                 |       |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7        |              |                                                          |               |                   |                 |                 | bit C |

|              |              |                                                          |               |                   |                 |                 |       |

| Legend:      |              |                                                          |               |                   |                 |                 |       |

| R = Readab   | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0      | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

## REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

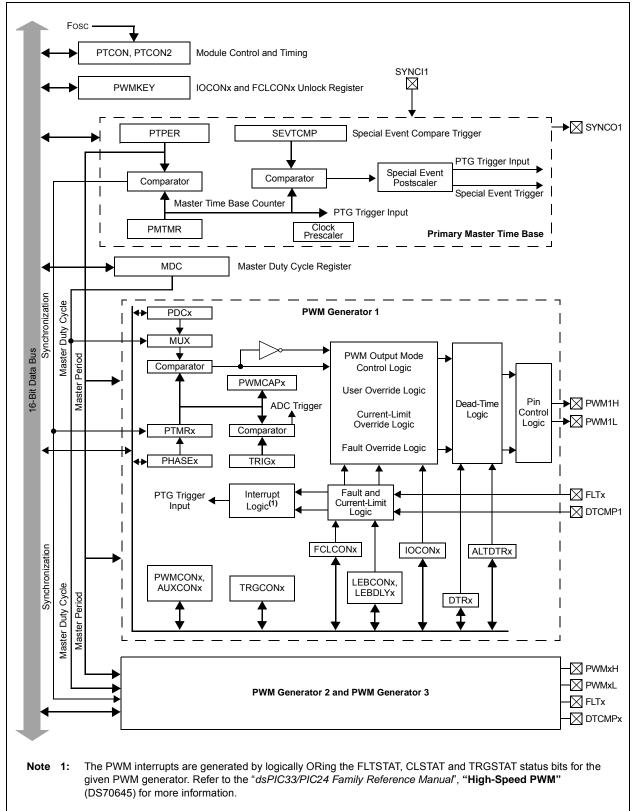

#### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

# REGISTER 16-13: IOCONX: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1 SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0 OSYNC: Output Override Synchronization bit

1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWMx period boundary

- 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

## 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

## REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                            |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

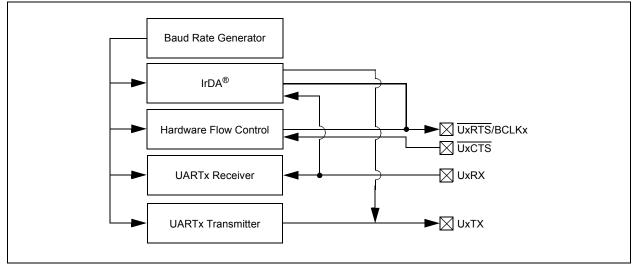

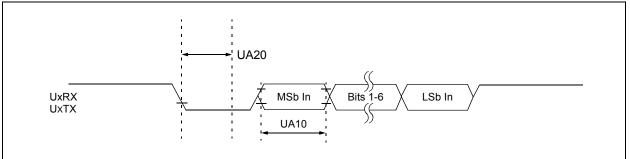

## 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

| U-0                          | U-0               | U-0                                   | U-0            | U-0          | U-0              | U-0             | U-0   |

|------------------------------|-------------------|---------------------------------------|----------------|--------------|------------------|-----------------|-------|

| _                            | —                 | —                                     |                | —            | —                | —               | _     |

| bit 15                       |                   |                                       |                |              |                  |                 | bit   |

|                              |                   |                                       |                |              |                  |                 |       |

| R/W-0                        | R/W-0             | R/W-0                                 | U-0            | R/W-0        | R/W-0            | R/W-0           | R/W-0 |

| IVRIE                        | WAKIE             | ERRIE                                 | —              | FIFOIE       | RBOVIE           | RBIE            | TBIE  |

| bit 7                        |                   |                                       |                |              |                  |                 | bit   |

|                              |                   |                                       |                |              |                  |                 |       |

| <b>Legend:</b><br>R = Readab | la hit            | W = Writable b                        | .it            |              | montod bit rook  | l oo 'O'        |       |

| n = Value a                  |                   | '1' = Bit is set                      | אנ             | 0 = Onimpler | mented bit, read | x = Bit is unkr |       |

|                              | IL POR            | I = DILIS SEL                         |                |              | areu             |                 | IOWI  |

| bit 15-8                     | Unimplemen        | ted: Read as '0                       | ,              |              |                  |                 |       |

| bit 7                        | -                 | Message Inter                         |                | bit          |                  |                 |       |

|                              |                   | request is enabl                      | •              | ~            |                  |                 |       |

|                              |                   | request is not er                     |                |              |                  |                 |       |

| bit 6                        | WAKIE: Bus        | Wake-up Activit                       | y Interrupt E  | nable bit    |                  |                 |       |

|                              |                   | equest is enabl                       |                |              |                  |                 |       |

|                              |                   | request is not er                     |                |              |                  |                 |       |

| bit 5                        |                   | Interrupt Enabl                       |                |              |                  |                 |       |

|                              |                   | request is enabl<br>request is not er |                |              |                  |                 |       |

| bit 4                        |                   | ted: Read as '0                       |                |              |                  |                 |       |

| bit 3                        | -                 | Almost Full Int                       |                | o hit        |                  |                 |       |

| DIL J                        |                   | request is enabl                      | •              | ebit         |                  |                 |       |

|                              |                   | request is not er                     |                |              |                  |                 |       |

| bit 2                        | <b>RBOVIE:</b> RX | Buffer Overflow                       | / Interrupt Er | nable bit    |                  |                 |       |

|                              | 1 = Interrupt     | equest is enabl                       | ed             |              |                  |                 |       |

|                              | 0 = Interrupt i   | request is not er                     | nabled         |              |                  |                 |       |

| bit 1                        |                   | ffer Interrupt En                     |                |              |                  |                 |       |

|                              |                   | equest is enabl                       |                |              |                  |                 |       |

|                              |                   | request is not er                     | nabled         |              |                  |                 |       |

|                              | •                 | •                                     |                |              |                  |                 |       |

| bit 0                        | TBIE: TX Buf      | fer Interrupt Ena<br>request is enabl | able bit       |              |                  |                 |       |

## REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER

| R/W-0         | R/W-0                                    | R/W-0                                                                                                                                                                                                                             | R/W-0            | R/W-0                                | R/W-0            | R/W-0           | R/W-0  |

|---------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------|------------------|-----------------|--------|

|               | F15BP<3:0>                               |                                                                                                                                                                                                                                   |                  |                                      | F14BI            | P<3:0>          |        |

| bit 15        |                                          |                                                                                                                                                                                                                                   |                  |                                      |                  |                 | bit 8  |

| R/W-0         | R/W-0                                    | R/W-0                                                                                                                                                                                                                             | R/W-0            | R/W-0                                | R/W-0            | R/W-0           | R/W-0  |

| 1010 0        |                                          | P<3:0>                                                                                                                                                                                                                            | 10110            |                                      |                  | P<3:0>          | 1010 0 |

| bit 7         |                                          |                                                                                                                                                                                                                                   |                  |                                      |                  |                 | bit 0  |

| Legend:       |                                          |                                                                                                                                                                                                                                   |                  |                                      |                  |                 |        |

| R = Readabl   | e bit                                    | W = Writable                                                                                                                                                                                                                      | bit              | U = Unimplen                         | nented bit, read | d as '0'        |        |

| -n = Value at | t POR                                    | '1' = Bit is set                                                                                                                                                                                                                  | '1' = Bit is set |                                      | ared             | x = Bit is unkr | nown   |

| bit 15-12     | 1111 = Filte<br>1110 = Filte             | F15BP<3:0>: RX Buffer Mask for Filter 1<br>1111 = Filter hits received in RX FIFO bu<br>1110 = Filter hits received in RX Buffer 1<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |                  |                                      |                  |                 |        |

| bit 11-8      | F14BP<3:0;                               | RX Buffer Ma                                                                                                                                                                                                                      | sk for Filter 1  | 4 bits (same val                     | ues as bits<15   | :12>)           |        |

| bit 7-4       | F13BP<3:0;                               | RX Buffer Ma                                                                                                                                                                                                                      | sk for Filter 1  | 3 bits (same val                     | ues as bits<15   | :12>)           |        |

| bit 3-0       | F12BP<3:0>: RX Buffer Mask for Filter 12 |                                                                                                                                                                                                                                   |                  | 12 bits (same values as bits<15:12>) |                  |                 |        |

## REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|--------|-----|-----|-----|-----|----------|----------|---------|

| —      | —   | —   | —   | -   | CH123NB1 | CH123NB0 | CH123SB |

| bit 15 |     |     |     |     |          |          | bit 8   |

|        |     |     |     |     |          |          |         |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | —   | —   | —   | —   | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

## Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9

**CH123NB<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXB bits In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |  |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|--|

| value           | CH1         | CH2   | CH3   |  |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |  |

| 0x              | Vrefl       | VREFL | Vrefl |  |  |  |  |

bit 8 **CH123SB:** Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value          | ADC Channel CH1 CH2 CH3 |         |         |  |  |  |  |  |

|----------------|-------------------------|---------|---------|--|--|--|--|--|

| value          |                         |         |         |  |  |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3                 | OA2/AN0 | OA3/AN6 |  |  |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0                 | AN1     | AN2     |  |  |  |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 **CH123NA<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '0':

| Value           |         | ADC Channel |       |

|-----------------|---------|-------------|-------|

| value           | CH1     | CH2         | CH3   |

| 11              | AN9     | AN10        | AN11  |

| 10 <b>(1,2)</b> | OA3/AN6 | AN7         | AN8   |

| 0x              | VREFL   | VREFL       | Vrefl |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

## 24.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Peripheral Trigger Generator (PTG)" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 24.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "Steps", that the user writes to the PTG Queue registers (PTGQUE0-PTGQUE7), which perform operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple clock sources

- Two 16-bit general purpose timers

- Two 16-bit general limit counters

- Configurable for rising or falling edge triggering

- Generates processor interrupts to include:

- Four configurable processor interrupts

- Interrupt on a Step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to receive trigger signals from these peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to trigger or synchronize to these peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

| REGISTER      | 25-3: CM40                                              | CON: COMPA                             | RATOR 4 CO        | ONTROL RE        | GISTER             |                                            |                     |

|---------------|---------------------------------------------------------|----------------------------------------|-------------------|------------------|--------------------|--------------------------------------------|---------------------|

| R/W-0         | R/W-0                                                   | R/W-0                                  | U-0               | U-0              | U-0                | R/W-0                                      | R/W-0               |

| CON           | COE                                                     | CPOL                                   | —                 | —                | _                  | CEVT                                       | COUT                |

| bit 15        |                                                         |                                        |                   |                  |                    |                                            | bit 8               |

| R/W-0         | DAALO                                                   | U-0                                    |                   | U-0              | U-0                |                                            | R/W-0               |

|               | R/W-0                                                   | 0-0                                    | R/W-0             | 0-0              | 0-0                | R/W-0                                      |                     |

| EVPOL1        | EVPOL0                                                  | —                                      | CREF              | —                | _                  | CCH1 <sup>(1)</sup>                        | CCH0 <sup>(1)</sup> |

| bit 7         |                                                         |                                        |                   |                  |                    |                                            | bit (               |

| Legend:       |                                                         |                                        |                   |                  |                    |                                            |                     |

| R = Readable  | e bit                                                   | W = Writable                           | bit               | U = Unimple      | mented bit, rea    | d as '0'                                   |                     |

| -n = Value at |                                                         | '1' = Bit is se                        |                   | '0' = Bit is cle |                    | x = Bit is unkr                            | iown                |

|               |                                                         |                                        | •                 |                  |                    |                                            |                     |

| bit 15        | CON: Comp                                               | arator Enable b                        | bit               |                  |                    |                                            |                     |

|               |                                                         | ator is enabled                        |                   |                  |                    |                                            |                     |

|               |                                                         | ator is disabled                       |                   |                  |                    |                                            |                     |

| bit 14        | COE: Comp                                               | arator Output E                        | nable bit         |                  |                    |                                            |                     |

|               |                                                         | ator output is pr<br>ator output is in |                   | xOUT pin         |                    |                                            |                     |

| bit 13        | CPOL: Com                                               | parator Output                         | Polarity Select   | bit              |                    |                                            |                     |

|               |                                                         | ator output is in                      |                   |                  |                    |                                            |                     |

|               | 0 = Compara                                             | ator output is no                      | ot inverted       |                  |                    |                                            |                     |

| bit 12-10     | Unimpleme                                               | nted: Read as                          | '0'               |                  |                    |                                            |                     |

| bit 9         | CEVT: Com                                               | parator Event b                        | it                |                  |                    |                                            |                     |

|               | interrup                                                | ts until the bit is                    | cleared           | POL<1:0> set     | tings occurred;    | disables future                            | triggers and        |

|               | •                                                       | ator event did i                       |                   |                  |                    |                                            |                     |

| bit 8         |                                                         | parator Output                         |                   |                  |                    |                                            |                     |

|               | $\frac{\text{VVnen CPOL}}{1 = \text{VIN} + > \text{V}}$ | <u>. = 0 (non-inver</u><br>/N-         | ted polarity):    |                  |                    |                                            |                     |

|               | 0 = VIN + < V                                           |                                        |                   |                  |                    |                                            |                     |

|               | When CPOL                                               | = 1 (inverted p                        | olarity):         |                  |                    |                                            |                     |

|               | 1 = VIN+ < V                                            |                                        |                   |                  |                    |                                            |                     |

|               | 0 = VIN + > V                                           | 'IN-                                   |                   |                  |                    |                                            |                     |

| bit 7-6       |                                                         | >: Trigger/Ever                        |                   | -                |                    |                                            |                     |

|               | 10 = Trigger                                            |                                        | generated only    |                  |                    | or output (while (<br>ne polarity selected |                     |

|               |                                                         | L = 1 (inverted)<br>-high transition   |                   | ator output.     |                    |                                            |                     |

|               |                                                         | L = 0 (non-inve<br>-low transition     |                   | ator output.     |                    |                                            |                     |

|               |                                                         | /event/interrupt<br>(while CEVT =      |                   | v on low-to-higl | n transition of th | e polarity selecte                         | ed comparato        |

|               |                                                         | L = 1 (inverted                        |                   | ator output.     |                    |                                            |                     |

|               |                                                         | L = 0 (non-inve<br>-high transition    |                   | ator output.     |                    |                                            |                     |

|               | 00 = Trigger                                            | /event/interrupt                       | generation is     | disabled         |                    |                                            |                     |

| Note 1: In    | puts that are se                                        | lected and not a                       | available will be | e tied to Vss. S | See the "Pin Dia   | agrams" sectior                            | n for available     |

Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

## 26.3 Programmable CRC Registers

## REGISTER 26-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0                            | U-0                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                  | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R-0                                                                                      | R-0                                                | R-0             | R-0            |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------|----------------|

| CRCEN                            | —                                                                                                                                                                                                                                                             | CSIDL                                                                                                                                                                                                                                                                  | VWORD4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VWORD3                                                                                   | VWORD2                                             | VWORD1          | VWORD0         |

| bit 15                           | ·                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                          |                                                    |                 | bit 8          |

| R-0                              | R-1                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                    | U-0                                                | U-0             | U-0            |

| CRCFUL                           | CRCMPT                                                                                                                                                                                                                                                        | CRCISEL                                                                                                                                                                                                                                                                | CRCGO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LENDIAN                                                                                  | _                                                  | _               | _              |

| bit 7                            | •                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                          |                                                    |                 | bit (          |

| Legend:                          |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                          |                                                    |                 |                |

| R = Readable                     | e bit                                                                                                                                                                                                                                                         | W = Writable                                                                                                                                                                                                                                                           | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U = Unimplen                                                                             | nented bit, read                                   | d as '0'        |                |

| -n = Value at                    | POR                                                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is cle                                                                         | ared                                               | x = Bit is unkr | nown           |

| bit 15                           | 0 = CRC mo                                                                                                                                                                                                                                                    | dule is enabled                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | chines, pointer                                                                          | s and CRCWD                                        | AT/CRCDAT a     | re reset, othe |