Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 256KB (85.5K x 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

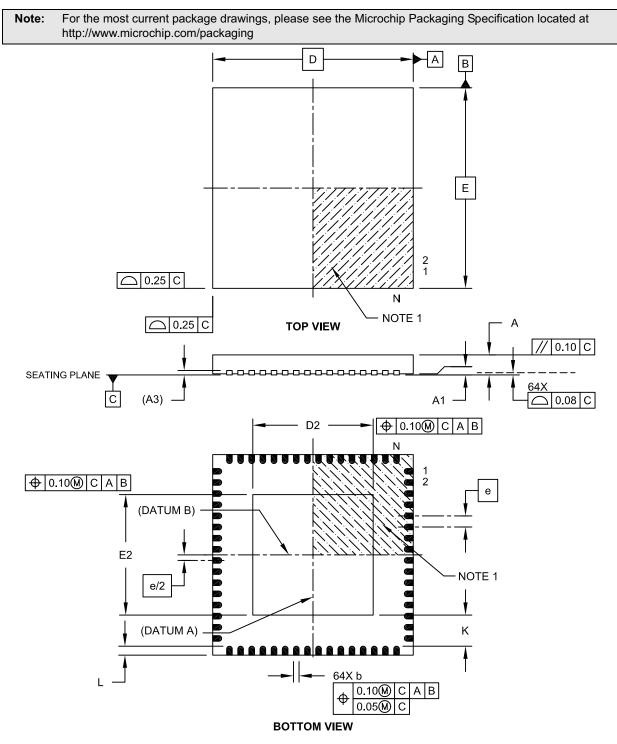

| Package / Case             | 44-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 44-QFN (8x8)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp504t-i-ml |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

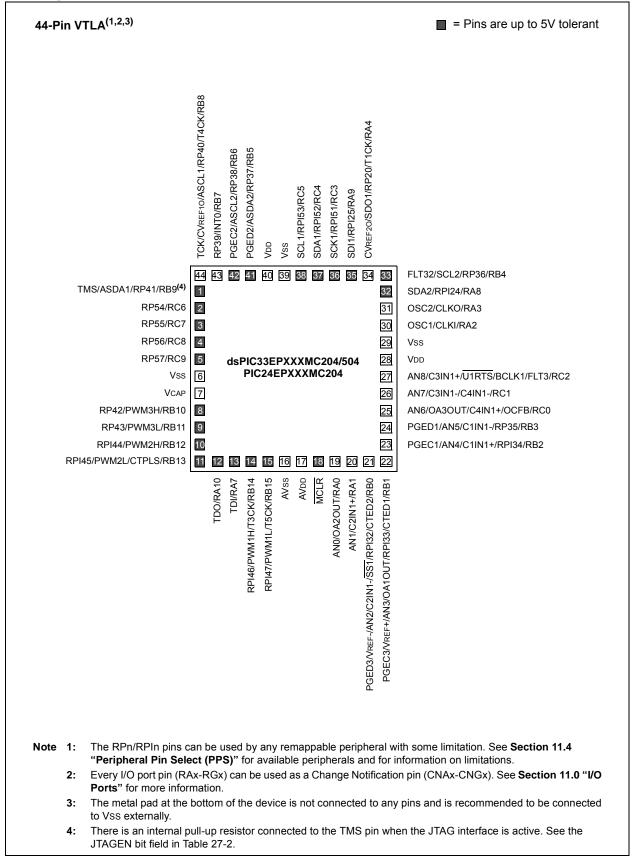

### Pin Diagrams (Continued)

### TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | _      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND7        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | —     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | —      |        | _      | _      | PWM3MD | PWM2MD | PWM1MD | —      |       |       | _      | —      |        | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

### TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

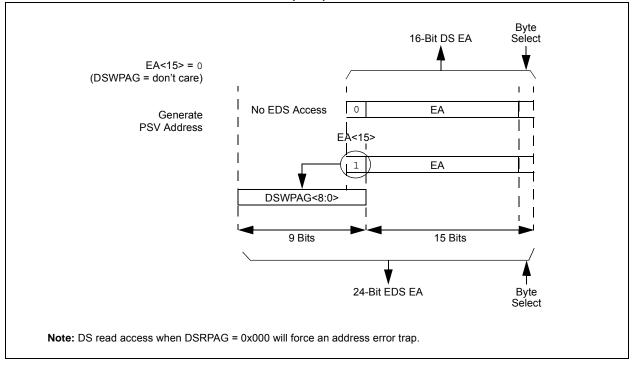

### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

### 14.2 Input Capture Registers

### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit |                    |  |  |  |

|-------------------|-----------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re  | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

NOTES:

| REGISTE       | R 16-7: PWMC                            | CONX: PWMX (                               | CONTROL R      | EGISTER          |                      |                      |                     |

|---------------|-----------------------------------------|--------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|

| HS/HC-        | 0 HS/HC-0                               | HS/HC-0                                    | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>              | TRGSTAT                                    | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |

| bit 15        | ·                                       | •                                          |                | ÷                |                      |                      | bit                 |

| R/W-0         | R/W-0                                   | R/W-0                                      | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| DTC1          |                                         | DTCP <sup>(3)</sup>                        | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |

| bit 7         | DICO                                    | DICE                                       | _              | INT DO           | CAIM                 | AFRES'               | bit                 |

|               |                                         |                                            |                |                  |                      |                      | <u> </u>            |

| Legend:       |                                         | HC = Hardware                              | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |

| R = Reada     | able bit                                | W = Writable bi                            | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |

| -n = Value    | at POR                                  | '1' = Bit is set                           |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |

| bit 15        | ELTSTAT: ES                             | ult Interrupt Statu                        | is hit(1)      |                  |                      |                      |                     |

| DIL 15        |                                         | rrupt is pending                           |                |                  |                      |                      |                     |

|               |                                         | interrupt is pendi                         | ng             |                  |                      |                      |                     |

|               |                                         | ared by setting F                          |                |                  |                      |                      |                     |

| bit 14        |                                         | rent-Limit Interru                         | •              |                  |                      |                      |                     |

|               |                                         | mit interrupt is pe                        |                |                  |                      |                      |                     |

|               |                                         | nt-limit interrupt is<br>ared by setting C |                |                  |                      |                      |                     |

| bit 13        |                                         | igger Interrupt S                          |                |                  |                      |                      |                     |

|               |                                         | terrupt is pendin                          |                |                  |                      |                      |                     |

|               |                                         | r interrupt is pen                         |                |                  |                      |                      |                     |

|               |                                         | ared by setting T                          |                |                  |                      |                      |                     |

| bit 12        |                                         | t Interrupt Enable                         | e bit          |                  |                      |                      |                     |

|               |                                         | rrupt is enabled rrupt is disabled         | and the FLTS   | TAT bit is clear | ed                   |                      |                     |

| bit 11        |                                         | ent-Limit Interrup                         |                |                  | cu .                 |                      |                     |

|               |                                         | mit interrupt is er                        |                |                  |                      |                      |                     |

|               |                                         | mit interrupt is di                        |                | e CLSTAT bit is  | s cleared            |                      |                     |

| bit 10        | TRGIEN: Trig                            | ger Interrupt En                           | able bit       |                  |                      |                      |                     |

|               |                                         | event generates                            |                |                  | T hit is cleared     |                      |                     |

| bit 9         |                                         | vent interrupts ar<br>dent Time Base I     |                |                  | i bit is cleared     |                      |                     |

| DIL 9         |                                         | register provides                          |                | riad for this PM | VM generator         |                      |                     |

|               |                                         | egister provides f                         | •              |                  | •                    |                      |                     |

| bit 8         |                                         | er Duty Cycle Re                           |                |                  |                      |                      |                     |

|               |                                         | ister provides du<br>jister provides du    |                |                  |                      | r                    |                     |

| Note 1:       | Software must clea                      |                                            |                |                  | -                    |                      | t controller        |

| Note 1.<br>2: | These bits should                       | -                                          |                | -                | -                    | the interrup         |                     |

| 3:            | DTC<1:0> = 11 fo                        | -                                          |                | -                | -                    |                      |                     |

| 4:            | The Independent T<br>CAM bit is ignored | Time Base (ITB =                           |                | •                |                      | igned mode. If       | TTB = 0, the        |

| 5:            | To operate in Exter                     |                                            | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |

### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

### 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

| U-0                 | U-0                                                                                                           | U-0             | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|--|

|                     | —                                                                                                             | _               | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |  |

| bit 15              |                                                                                                               | •               |                                       | •                    | •                    | •                    | bit                  |  |  |  |  |

| R/W-0               | R/W-0                                                                                                         | R/W-0           | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                                                                                           | MSTEN           | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |  |

| bit 7               | CKF                                                                                                           | WISTEN          | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |  |  |  |  |

|                     |                                                                                                               |                 |                                       |                      |                      |                      |                      |  |  |  |  |

| Legend:             |                                                                                                               |                 |                                       |                      |                      |                      |                      |  |  |  |  |

| R = Readabl         | le bit                                                                                                        | W = Writable    | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |  |  |  |  |

| -n = Value at       | t POR                                                                                                         | '1' = Bit is se | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |  |  |  |  |

|                     |                                                                                                               |                 |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 15-13           | Unimplemen                                                                                                    | ted: Read as    | 0'                                    |                      |                      |                      |                      |  |  |  |  |

| bit 12              |                                                                                                               |                 | bit (SPIx Mas                         | -                    | ()                   |                      |                      |  |  |  |  |

|                     |                                                                                                               | PIx clock is di | sabled, pin fun                       | ctions as I/O        |                      |                      |                      |  |  |  |  |

| oit 11              |                                                                                                               | able SDOx Pir   |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                               |                 | / the module; p                       | oin functions as     | s I/O                |                      |                      |  |  |  |  |

|                     |                                                                                                               | is controlled b |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 10              | MODE16: Wo                                                                                                    | ord/Byte Comn   | nunication Sele                       | ect bit              |                      |                      |                      |  |  |  |  |

|                     | <ul> <li>1 = Communication is word-wide (16 bits)</li> <li>0 = Communication is byte-wide (8 bits)</li> </ul> |                 |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                               | •               | . ,                                   |                      |                      |                      |                      |  |  |  |  |

| bit 9               |                                                                                                               | ata Input Sam   | ole Phase bit                         |                      |                      |                      |                      |  |  |  |  |

|                     | Master mode                                                                                                   | -               | end of data o                         | utout time           |                      |                      |                      |  |  |  |  |

|                     |                                                                                                               |                 | middle of data                        |                      |                      |                      |                      |  |  |  |  |

|                     | Slave mode:                                                                                                   |                 |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                               |                 | SPIx is used i                        | n Slave mode.        |                      |                      |                      |  |  |  |  |

| bit 8               |                                                                                                               | lock Edge Sele  |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                               |                 |                                       |                      |                      | lle clock state (r   |                      |  |  |  |  |

| bit 7               |                                                                                                               |                 | bit (Slave mo                         |                      |                      | ve clock state (i    |                      |  |  |  |  |

|                     |                                                                                                               | sused for Slav  |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                               |                 |                                       | is controlled b      | by port function     |                      |                      |  |  |  |  |

| bit 6               | CKP: Clock F                                                                                                  | Polarity Select | bit                                   |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                               |                 | nigh level; activ<br>ow level; active |                      |                      |                      |                      |  |  |  |  |

| bit 5               | MSTEN: Mas                                                                                                    | ter Mode Enat   | ole bit                               |                      |                      |                      |                      |  |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                                  |                 |                                       |                      |                      |                      |                      |  |  |  |  |

| Note 1: T           | he CKE bit is not                                                                                             | used in Frame   | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |  |  |  |  |

|                     | his bit must be cl                                                                                            |                 |                                       |                      |                      |                      |                      |  |  |  |  |

| <b>0</b>            |                                                                                                               |                 |                                       |                      |                      |                      |                      |  |  |  |  |

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

#### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

### REGISTER 21-12: CxBUFPNT1: ECANx FILTER 0-3 BUFFER POINTER REGISTER 1

| R/W-0                                                         | R/W-0                                                       | R/W-0                                                          | R/W-0            | R/W-0                                   | R/W-0           | R/W-0  | R/W-0 |  |  |

|---------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------|------------------|-----------------------------------------|-----------------|--------|-------|--|--|

|                                                               | F3BF                                                        | ><3:0>                                                         |                  | F2BP<3:0>                               |                 |        |       |  |  |

| bit 15                                                        |                                                             |                                                                |                  |                                         |                 |        | bit 8 |  |  |

| R/W-0                                                         | R/W-0                                                       | R/W-0                                                          | R/W-0            | R/W-0                                   | R/W-0           | R/W-0  | R/W-0 |  |  |

|                                                               | F1BF                                                        | ><3:0>                                                         |                  |                                         | F0BF            | P<3:0> |       |  |  |

| bit 7                                                         |                                                             |                                                                |                  |                                         |                 |        | bit C |  |  |

| Legend:                                                       |                                                             |                                                                |                  |                                         |                 |        |       |  |  |

| R = Readabl                                                   | e bit                                                       | W = Writable                                                   | bit              | U = Unimplemented bit, read as '0'      |                 |        |       |  |  |

| -n = Value at                                                 | POR                                                         | '1' = Bit is set                                               |                  | '0' = Bit is cleared x = Bit is unknown |                 |        |       |  |  |

| bit 15-12                                                     | F3BP<3:0>                                                   | : RX Buffer Mas                                                | k for Filter 3 b | oits                                    |                 |        |       |  |  |

|                                                               | 1110 = Filte<br>•                                           | r hits received in<br>r hits received in<br>r hits received in | n RX Buffer 14   |                                         |                 |        |       |  |  |

|                                                               | 0001                                                        | er hits received in<br>thits received in                       |                  |                                         |                 |        |       |  |  |

| bit 11-8                                                      | F2BP<3:0>                                                   | RX Buffer Mas                                                  | k for Filter 2 b | oits (same value                        | s as bits<15:1  | 2>)    |       |  |  |

| bit 7-4 F1BP<3:0>: RX Buffer Mask for Filter 1 bits (same val |                                                             |                                                                |                  |                                         | s as bits<15:12 | 2>)    |       |  |  |

|                                                               | bit 3-0 <b>F0BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 0 |                                                                |                  |                                         |                 |        |       |  |  |

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |  |

|--------|-----|-----|-----|----------|----------|----------|----------|--|

| —      | —   | —   | —   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |  |

| bit 15 |     |     |     |          |          |          | bit 8    |  |

|        |     |     |     |          |          |          |          |  |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 15-12 Unimplemented: Read as '0'

| DIL 10-12 | Uninpienienieu. Reau as 0                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8  | SELSRCC<3:0>: Mask C Input Select bits                                                                                                                                                                                                         |

|           | 1111 <b>= FLT4</b>                                                                                                                                                                                                                             |

|           | 1110 <b>= FLT2</b>                                                                                                                                                                                                                             |

|           | 1101 <b>= PTGO19</b>                                                                                                                                                                                                                           |

|           | 1100 = PTGO18                                                                                                                                                                                                                                  |

|           | 1011 = Reserved                                                                                                                                                                                                                                |

|           | 1010 = Reserved                                                                                                                                                                                                                                |

|           | 1001 = Reserved                                                                                                                                                                                                                                |

|           | 1000 = Reserved                                                                                                                                                                                                                                |

|           | 0111 = Reserved                                                                                                                                                                                                                                |

|           | 0110 = Reserved                                                                                                                                                                                                                                |

|           | 0101 = PWM3H                                                                                                                                                                                                                                   |

|           | 0100 = PWM3L                                                                                                                                                                                                                                   |

|           | 0011 = PWM2H                                                                                                                                                                                                                                   |

|           | 0010 = PWM2L                                                                                                                                                                                                                                   |

|           | 0001 = PWM1H                                                                                                                                                                                                                                   |

|           | 0000 = PWM1L                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits                                                                                                                                                                                                         |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits 1111 = FLT4                                                                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2                                                                                                                                                                                                                     |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19                                                                                                                                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18                                                                                                                                                                                   |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved                                                                                                                                                                |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved                                                                                                                          |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved                                                                                                       |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved                                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM2L |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

| Base<br>Instr<br># Assembly<br>Mnemonic |        |         | Assembly Syntax                           | Description                                                | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|-----------------------------------------|--------|---------|-------------------------------------------|------------------------------------------------------------|---------------|-------------------------------|--------------------------|

| 9                                       | BTG    | BTG     | f,#bit4                                   | Bit Toggle f                                               | 1             | 1                             | None                     |

|                                         |        | BTG     | Ws,#bit4                                  | Bit Toggle Ws                                              | 1             | 1                             | None                     |

| 10                                      | BTSC   | BTSC    | f,#bit4                                   | Bit Test f, Skip if Clear                                  | 1             | 1<br>(2 or 3)                 | None                     |

|                                         |        | BTSC    | Ws,#bit4                                  | Bit Test Ws, Skip if Clear                                 | 1             | 1<br>(2 or 3)                 | None                     |

| 11                                      | BTSS   | BTSS    | f,#bit4                                   | Bit Test f, Skip if Set                                    | 1             | 1<br>(2 or 3)                 | None                     |

|                                         |        | BTSS    | Ws,#bit4                                  | Bit Test Ws, Skip if Set                                   | 1             | 1<br>(2 or 3)                 | None                     |

| 12                                      | BTST   | BTST    | f,#bit4                                   | Bit Test f                                                 | 1             | 1                             | Z                        |

|                                         |        | BTST.C  | Ws,#bit4                                  | Bit Test Ws to C                                           | 1             | 1                             | С                        |

|                                         |        | BTST.Z  | Ws,#bit4                                  | Bit Test Ws to Z                                           | 1             | 1                             | Z                        |

|                                         |        | BTST.C  | Ws,Wb                                     | Bit Test Ws <wb> to C</wb>                                 | 1             | 1                             | С                        |

|                                         |        | BTST.Z  | Ws,Wb                                     | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1                             | Z                        |

| 13                                      | BTSTS  | BTSTS   | f,#bit4                                   | Bit Test then Set f                                        | 1             | 1                             | Z                        |

|                                         |        | BTSTS.C | Ws,#bit4                                  | Bit Test Ws to C, then Set                                 | 1             | 1                             | С                        |

|                                         |        | BTSTS.Z | Ws,#bit4                                  | Bit Test Ws to Z, then Set                                 | 1             | 1                             | Z                        |

| 14                                      | CALL   | CALL    | lit23                                     | Call subroutine                                            | 2             | 4                             | SFA                      |

|                                         |        | CALL    | Wn                                        | Call indirect subroutine                                   | 1             | 4                             | SFA                      |

|                                         |        | CALL.L  | Wn                                        | Call indirect subroutine (long address)                    | 1             | 4                             | SFA                      |

| 15                                      | CLR    | CLR     | f                                         | f = 0x0000                                                 | 1             | 1                             | None                     |

|                                         |        | CLR     | WREG                                      | WREG = 0x0000                                              | 1             | 1                             | None                     |

|                                         |        | CLR     | Ws                                        | Ws = 0x0000                                                | 1             | 1                             | None                     |

|                                         |        | CLR     | Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Clear Accumulator                                          | 1             | 1                             | OA,OB,SA,SB              |

| 16                                      | CLRWDT | CLRWDT  |                                           | Clear Watchdog Timer                                       | 1             | 1                             | WDTO,Sleep               |

| 17                                      | СОМ    | COM     | f                                         | f = f                                                      | 1             | 1                             | N,Z                      |

|                                         |        | COM     | f,WREG                                    | WREG = f                                                   | 1             | 1                             | N,Z                      |

|                                         |        | COM     | Ws,Wd                                     | $Wd = \overline{Ws}$                                       | 1             | 1                             | N,Z                      |

| 18                                      | CP     | CP      | f                                         | Compare f with WREG                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | CP      | Wb,#lit8                                  | Compare Wb with lit8                                       | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | CP      | Wb,Ws                                     | Compare Wb with Ws (Wb – Ws)                               | 1             | 1                             | C,DC,N,OV,Z              |

| 19                                      | CP0    | CPO     | f                                         | Compare f with 0x0000                                      | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | CPO     | Ws                                        | Compare Ws with 0x0000                                     | 1             | 1                             | C,DC,N,OV,Z              |

| 20                                      | CPB    | CPB     | f                                         | Compare f with WREG, with Borrow                           | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | CPB     | Wb,#lit8                                  | Compare Wb with lit8, with Borrow                          | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | CPB     | Wb,Ws                                     | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

| 21                                      | CPSEQ  | CPSEQ   | Wb,Wn                                     | Compare Wb with Wn, skip if =                              | 1             | 1<br>(2 or 3)                 | None                     |

|                                         | CPBEQ  | CPBEQ   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if =                            | 1             | 1 (5)                         | None                     |

| 22                                      | CPSGT  | CPSGT   | Wb,Wn                                     | Compare Wb with Wn, skip if >                              | 1             | 1<br>(2 or 3)                 | None                     |

|                                         | CPBGT  | CPBGT   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if >                            | 1             | 1 (5)                         | None                     |

| 23                                      | CPSLT  | CPSLT   | Wb,Wn                                     | Compare Wb with Wn, skip if <                              | 1             | 1<br>(2 or 3)                 | None                     |

|                                         | CPBLT  | CPBLT   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if <                            | 1             | 1 (5)                         | None                     |

| 24                                      | CPSNE  | CPSNE   | Wb,Wn                                     | Compare Wb with Wn, skip if ≠                              | 1             | 1<br>(2 or 3)                 | None                     |

|                                         | CPBNE  | CPBNE   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if ≠                            | 1             | 1 (5)                         | None                     |

| <b>TABLE 28-2:</b> | <b>INSTRUCTION SET OVERVIEW (</b> | CONTINUED | ) |

|--------------------|-----------------------------------|-----------|---|

|                    |                                   | CONTINUED | , |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        |                                                  | Description                               | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected<br>None |  |

|--------------------|----------------------|--------|--------------------------------------------------|-------------------------------------------|---------------|-------------------------------|----------------------------------|--|

| 46 MOV             |                      | MOV    | f,Wn                                             | Move f to Wn                              | 1             | 1                             |                                  |  |

|                    |                      | MOV    | f                                                | Move f to f                               | 1             | 1                             | None                             |  |

|                    |                      | MOV    | f,WREG                                           | Move f to WREG                            | 1             | 1                             | None                             |  |

|                    |                      | MOV    | #litl6,Wn                                        | Move 16-bit literal to Wn                 | 1             | 1                             | None                             |  |

|                    |                      | MOV.b  | #lit8,Wn                                         | Move 8-bit literal to Wn                  | 1             | 1                             | None                             |  |

|                    |                      | MOV    | Wn,f                                             | Move Wn to f                              | 1             | 1                             | None                             |  |

|                    |                      | MOV    | Wso,Wdo                                          | Move Ws to Wd                             | 1             | 1                             | None                             |  |

|                    |                      | MOV    | WREG, f                                          | Move WREG to f                            | 1             | 1                             | None                             |  |

|                    |                      | MOV.D  | Wns,Wd                                           | Move Double from W(ns):W(ns + 1) to<br>Wd | 1             | 2                             | None                             |  |

|                    |                      | MOV.D  | Ws , Wnd                                         | Move Double from Ws to W(nd +<br>1):W(nd) | 1             | 2                             | None                             |  |

| 47                 | MOVPAG               | MOVPAG | #lit10,DSRPAG                                    | Move 10-bit literal to DSRPAG             | 1             | 1                             | None                             |  |

|                    |                      | MOVPAG | #lit9,DSWPAG                                     | Move 9-bit literal to DSWPAG              | 1             | 1                             | None                             |  |

|                    |                      | MOVPAG | #lit8,TBLPAG                                     | Move 8-bit literal to TBLPAG              | 1             | 1                             | None                             |  |

|                    |                      | MOVPAG | Ws, DSRPAG                                       | Move Ws<9:0> to DSRPAG                    | 1             | 1                             | None                             |  |

|                    |                      | MOVPAG | Ws, DSWPAG                                       | Move Ws<8:0> to DSWPAG                    | 1             | 1                             | None                             |  |

|                    |                      | MOVPAG | Ws, TBLPAG                                       | Move Ws<7:0> to TBLPAG                    | 1             | 1                             | None                             |  |

| 48                 | MOVSAC               | MOVSAC | Acc,Wx,Wxd,Wy,Wyd,AWB <sup>(1)</sup>             | Prefetch and store accumulator            | 1             | 1                             | None                             |  |

| 49                 | MPY                  | MPY    | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | Multiply Wm by Wn to Accumulator          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB          |  |

|                    |                      | MPY    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>           | Square Wm to Accumulator                  | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB          |  |

| 50                 | MPY.N                | MPY.N  | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | -(Multiply Wm by Wn) to Accumulator       | 1             | 1                             | None                             |  |

| 51                 | MSC                  | MSC    | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Subtract from Accumulator    | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB          |  |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| TABLE 30-23: TIME | R1 EXTERNAL CLOCK TIMING REQUIREMENTS <sup>(1)</sup> | ) |

|-------------------|------------------------------------------------------|---|

|-------------------|------------------------------------------------------|---|

| АС СН        | ARACTERIS | TICS                                                                                               |                          | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |               |       |                                                                             |  |

|--------------|-----------|----------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|--|

| Param<br>No. | Symbol    | Charao                                                                                             | cteristic <sup>(2)</sup> | Min.                                                 | Тур. | Max.          | Units | Conditions                                                                  |  |

| TA10         | ТтхН      | T1CK High<br>Time                                                                                  | Synchronous<br>mode      | Greater of:<br>20 or<br>(Tcy + 20)/N                 |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |  |

|              |           |                                                                                                    | Asynchronous             | 35                                                   | _    | —             | ns    |                                                                             |  |

| TA11         | ΤτχL      | T1CK Low<br>Time                                                                                   | Synchronous<br>mode      | Greater of:<br>20 or<br>(Tcy + 20)/N                 | _    | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |  |

|              |           |                                                                                                    | Asynchronous             | 10                                                   |      | —             | ns    |                                                                             |  |

| TA15         | ΤτχΡ      | T1CK Input<br>Period                                                                               | Synchronous mode         | Greater of:<br>40 or<br>(2 Tcy + 40)/N               | _    | —             | ns    | N = prescale value<br>(1, 8, 64, 256)                                       |  |

| OS60         | Ft1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting bit, TCS<br>(T1CON<1>)) |                          | DC                                                   |      | 50            | kHz   |                                                                             |  |

| TA20         | TCKEXTMRL | Delay from External T1CK<br>Clock Edge to Timer<br>Increment                                       |                          | 0.75 Tcy + 40                                        | _    | 1.75 Tcy + 40 | ns    |                                                                             |  |

Note 1: Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

## FIGURE 30-11: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

### TABLE 30-30: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |           |                                                              |                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                                  |  |

|--------------------|-----------|--------------------------------------------------------------|-----------------------------|-------------------------------------------------------|------|------|-------|----------------------------------|--|

| Param<br>No.       | Symbol    | Charao                                                       | cteristic <sup>(1)</sup>    | Min.                                                  | Тур. | Max. | Units | Conditions                       |  |

| TQ10               | TtQH      | TQCK High<br>Time                                            | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25        |      |      | ns    | Must also meet<br>Parameter TQ15 |  |

| TQ11               | TtQL      | TQCK Low<br>Time                                             | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25        | —    | _    | ns    | Must also meet<br>Parameter TQ15 |  |

| TQ15               | TtQP      | TQCP Input<br>Period                                         | Synchronous, with prescaler | Greater of 25 + 50<br>or<br>(1 Tcy/N) + 50            | —    | _    | ns    |                                  |  |

| TQ20               | TCKEXTMRL | Delay from External TQCK<br>Clock Edge to Timer<br>Increment |                             | _                                                     | 1    | Тсү  | —     |                                  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

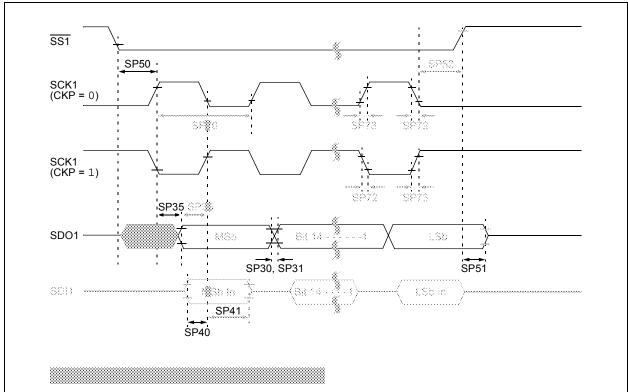

### FIGURE 30-28: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS