Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 44-VTLA (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp504t-i-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

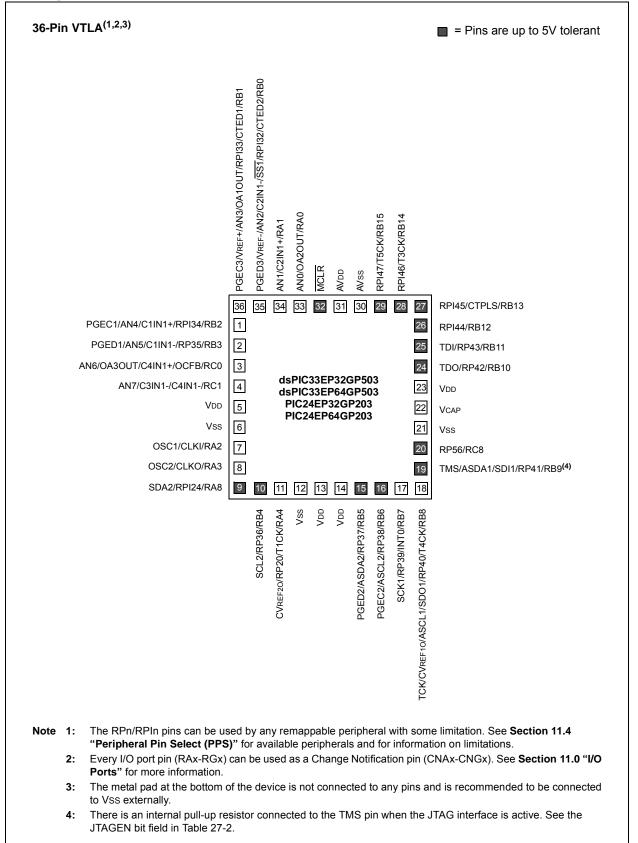

#### **Pin Diagrams (Continued)**

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

|              |       |        |        | -            | -      | -          |        |       |       |       |              |       |       |            |       |       |       |               |

|--------------|-------|--------|--------|--------------|--------|------------|--------|-------|-------|-------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0       | 06A0  | _      |        | INT1R<6:0>   |        |            |        |       |       |       | _            | _     | _     | _          |       | _     | _     | 0000          |

| RPINR1       | 06A2  |        | —      |              |        |            |        |       | -     | -     |              |       |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _            | _      | _          | _      | _     | _     | _     |              |       | -     | [2CKR<6:0> | >     |       |       | 0000          |

| RPINR7       | 06AE  | _      |        |              |        | IC2R<6:0>  |        |       |       | —     |              |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  | _      |        |              |        | IC4R<6:0>  |        |       |       | —     |              |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  | _      | _      | _            | —      | _          | _      | _     | _     | —     | - OCFAR<6:0> |       |       |            |       | 0000  |       |               |

| RPINR12      | 06B8  | _      |        |              | l      | =LT2R<6:0> |        |       |       | —     |              |       |       | FLT1R<6:0> | >     |       |       | 0000          |

| RPINR14      | 06BC  | _      |        |              | (      | QEB1R<6:0  | >      |       |       | —     | QEA1R<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR15      | 06BE  | _      |        |              | Н      | OME1R<6:0  | )>     |       |       | —     | INDX1R<6:0>  |       |       |            |       | 0000  |       |               |

| RPINR18      | 06C4  | _      | _      | _            | —      | _          | _      | _     | _     | —     |              |       | ι     | J1RXR<6:0> | >     |       |       | 0000          |

| RPINR19      | 06C6  | _      | _      | _            | _      | _          | _      | _     | _     | —     |              |       | ι     | J2RXR<6:0> | >     |       |       | 0000          |

| RPINR22      | 06CC  | _      |        | •            | S      | CK2INR<6:0 | )>     |       |       | _     |              |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      |              | _      | _          | _      | _     | _     | _     |              |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR37      | 06EA  | _      |        |              | S      | YNCI1R<6:0 | )>     |       |       | _     | _            | _     | _     | _          | _     | _     | _     | 0000          |

| RPINR38      | 06EC  | _      |        | DTCMP1R<6:0> |        |            |        |       |       | _     | _            | _     | _     |            | _     | _     | _     | 0000          |

| RPINR39      | 06EE  | _      |        |              | DT     | CMP3R<6:   | 0>     |       |       | —     |              |       | D     | CMP2R<6:   | 0>    |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-----------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      | _         | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _      | _      |        | _      | _      | _     | _      |           |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |        |        |        |        |        |       | STA<15 | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _      | _      | _      | _      | _      | _     | _      |           |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |        |        |        |        |        |       | STB<1  | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | —      | —      | _      | _      | —      | —     | —      |           |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |        |        |        |        |        |       | PAD<1  | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _      |        |        |        |        |       |        | CNT<1     | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —      | _         | —     | AMOD  | E<1:0> | —       | _      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _      | _      |        | _      | _      | _     | _      |           |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |        |        |        |        |        |       | STA<15 | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | —      | —      | _      | _      | —      | —     | —      |           |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |        |        |        |        |        |       | STB<1  | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | _      | _      | _      |        | _      | _     | _      |           |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |        |        |        |        |        |        |       | PAD<1  | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA1CNT   | 0B1E  | _      | —      |        |        |        |        |       |        | CNT<13:0> |       |       |        | 0000    |        |        |        |               |

| DMA2CON   | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | _     | _      | _         | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _      | _      |        | _      | _      | _     | _      |           |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |        |        |        |        |        |       | STA<18 | TA<15:0>  |       |       |        |         | 0000   |        |        |               |

| DMA2STAH  | 0B26  | _      | _      | _      | _      | _      | _      | _     | _      |           |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |        |        |        |        |        |       | STB<1  | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _      | _      | _      | _      | _      | _      | _     | _      |           |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |        |        |        |        |        |       | PAD<1  | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _      |        |        |        |        |       |        | CNT<1     | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _         | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _      | _      | _      | _      | _      | _     | _      |           |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |        |        |        |        |        |       | STA<18 | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _      | _      | _      | _      | _      | _     | _      |           |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |        |        |        |        |        |       | STB<1  | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _      | _      | _      | _      | _      | _     | _      |           |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |        |        |        |        |        |       | PAD<1  | 5:0>      |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _      |        |        |        |        |       |        | CNT<1     | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | _      | —      | —      | —      | —      | —      |       | _      | —         | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | —      | _      | _      | _      | _      | _     | _      | _         | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _      | _         | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _      | _      | _      | _      | _      | _     | _      | _         | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |        |        |        |        |        |        |       | DSADR< | 15:0>     |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | —      | —      | —      | —      | —      | —     | —      |           |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

## 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

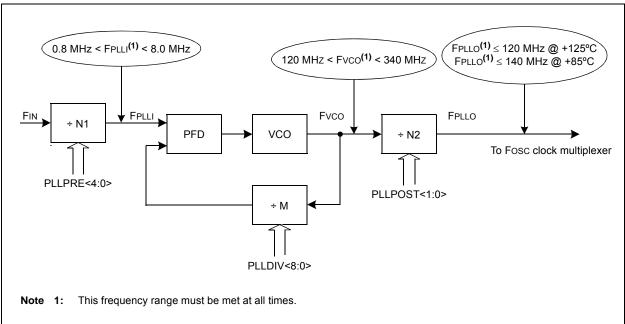

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

#### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

#### EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

DS70000657H-page 154

#### © 2011-2013 Microchip Technology Inc.

## FIGURE 9-2: PLL BLOCK DIAGRAM

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 3 SPI1MD: SPI1 Module Disable bit 1 = SPI1 module is disabled

- 0 = SPI1 module is enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: ECAN1 Module Disable bit<sup>(2)</sup> 1 = ECAN1 module is disabled 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit 1 = ADC1 module is disabled 0 = ADC1 module is enabled

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                                                                                                                      | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------------------|------------------|-----------------|-------|

| —               | —                                                                                                                                        |                  |       | RP57              | R<5:0>           |                 |       |

| bit 15          |                                                                                                                                          |                  |       |                   |                  |                 | bit 8 |

|                 |                                                                                                                                          |                  |       |                   |                  |                 |       |

| U-0             | U-0                                                                                                                                      | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| _               | —                                                                                                                                        |                  |       | RP56              | R<5:0>           |                 |       |

| bit 7           |                                                                                                                                          |                  |       |                   |                  |                 | bit 0 |

|                 |                                                                                                                                          |                  |       |                   |                  |                 |       |

| Legend:         |                                                                                                                                          |                  |       |                   |                  |                 |       |

| R = Readable I  | bit                                                                                                                                      | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR                                                                                                                                       | '1' = Bit is set | :     | '0' = Bit is clea | ared             | x = Bit is unkr | iown  |

|                 |                                                                                                                                          |                  |       |                   |                  |                 |       |

| bit 15-14       | Unimplemen                                                                                                                               | ted: Read as '   | 0'    |                   |                  |                 |       |

| bit 13-8        | <b>RP57R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers) |                  |       |                   |                  |                 |       |

| bit 7-6         | Unimplemented: Read as '0'                                                                                                               |                  |       |                   |                  |                 |       |

#### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

## 12.2 Timer1 Control Register

| R/W-0              | U-0                                                           | R/W-0                             | U-0                       | U-0              | U-0                      | U-0              | U-0                |

|--------------------|---------------------------------------------------------------|-----------------------------------|---------------------------|------------------|--------------------------|------------------|--------------------|

| TON <sup>(1)</sup> | —                                                             | TSIDL                             | —                         | _                | —                        | _                | _                  |

| bit 15             |                                                               |                                   |                           |                  |                          |                  | bit 8              |

|                    |                                                               |                                   |                           |                  |                          |                  |                    |

| U-0                | R/W-0                                                         | R/W-0                             | R/W-0                     | U-0              | R/W-0                    | R/W-0            | U-0                |

|                    | TGATE TCKPS1 TCKPS0 — TSYNC <sup>(1)</sup> TCS <sup>(1)</sup> |                                   |                           |                  |                          |                  |                    |

| bit 7              |                                                               |                                   |                           |                  |                          |                  | bit (              |

| Legend:            |                                                               |                                   |                           |                  |                          |                  |                    |

| R = Readable       | e bit                                                         | W = Writable                      | bit                       | U = Unimplei     | mented bit, read         | l as '0'         |                    |

| -n = Value at      | POR                                                           | '1' = Bit is set                  |                           | '0' = Bit is cle | ared                     | x = Bit is unkno | own                |

|                    |                                                               | o                                 |                           |                  |                          |                  |                    |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16-                          |                                   |                           |                  |                          |                  |                    |

|                    | 0 = Stops 16-                                                 |                                   |                           |                  |                          |                  |                    |

| bit 14             | Unimplemen                                                    | ted: Read as '                    | 0'                        |                  |                          |                  |                    |

| bit 13             | TSIDL: Timer                                                  | 1 Stop in Idle N                  | /lode bit                 |                  |                          |                  |                    |

|                    |                                                               | ues module op                     |                           |                  | ldle mode                |                  |                    |

|                    |                                                               | s module opera                    |                           | ode              |                          |                  |                    |

| bit 12-7           | -                                                             | ted: Read as '                    |                           |                  |                          |                  |                    |

| bit 6              |                                                               | r1 Gated Time                     | Accumulation              | h Enable bit     |                          |                  |                    |

|                    | When TCS =<br>This bit is igno                                |                                   |                           |                  |                          |                  |                    |

|                    | When TCS =                                                    |                                   |                           |                  |                          |                  |                    |

|                    |                                                               | e accumulatio                     |                           |                  |                          |                  |                    |

|                    |                                                               | e accumulatio                     |                           | 0.1.1.1.1.1      |                          |                  |                    |

| bit 5-4            |                                                               | : Timer1 Input                    | Clock Prescal             | e Select bits    |                          |                  |                    |

|                    | 11 = 1:256<br>10 = 1:64                                       |                                   |                           |                  |                          |                  |                    |

|                    | 01 = 1:8                                                      |                                   |                           |                  |                          |                  |                    |

|                    | 00 = 1:1                                                      |                                   |                           |                  |                          |                  |                    |

| bit 3              | -                                                             | ted: Read as '                    |                           |                  |                          |                  |                    |

| bit 2              |                                                               | er1 External Clo                  | ock Input Synd            | chronization S   | elect bit <sup>(1)</sup> |                  |                    |

|                    | When TCS =                                                    |                                   |                           |                  |                          |                  |                    |

|                    |                                                               | izes external c<br>synchronize e> |                           | nut              |                          |                  |                    |

|                    | When TCS =                                                    | •                                 |                           | iput             |                          |                  |                    |

|                    | This bit is igno                                              |                                   |                           |                  |                          |                  |                    |

| bit 1              | TCS: Timer1                                                   | Clock Source S                    | Select bit <sup>(1)</sup> |                  |                          |                  |                    |

|                    | 1 = External c<br>0 = Internal cl                             | clock is from pi<br>ock (FP)      | n, T1CK (on th            | ne rising edge)  | •                        |                  |                    |

| bit 0              | Unimplemen                                                    | ted: Read as '                    | 0'                        |                  |                          |                  |                    |

|                    | nen Timer1 is er<br>empts by user s                           |                                   |                           |                  |                          | SYNC = 1, TON    | <b>\ =</b> 1), any |

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

© 2011-2013 Microchip Technology Inc.

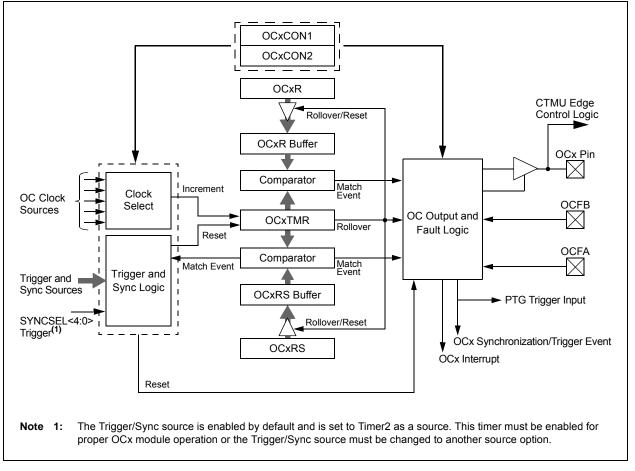

## 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select one of seven available clock sources for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The output compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual" for OCxR and OCxRS register restrictions.

## 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | R/W-x                        | U-0                                     | U-0             | U-0              | R/W-x            | R/W-x           | R/W-x   |

|---------------|------------------------------|-----------------------------------------|-----------------|------------------|------------------|-----------------|---------|

| _             | WAKFIL                       | _                                       | —               |                  | SEG2PH2          | SEG2PH1         | SEG2PH0 |

| bit 15        |                              |                                         |                 |                  |                  |                 | bit     |

| R/W-x         | R/W-x                        | R/W-x                                   | R/W-x           | R/W-x            | R/W-x            | R/W-x           | R/W-x   |

|               |                              |                                         |                 | 1                |                  | 1               |         |

| SEG2PHTS      | SAM                          | SEG1PH2                                 | SEG1PH1         | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |

| bit 7         |                              |                                         |                 |                  |                  |                 | bit     |

| Legend:       |                              |                                         |                 |                  |                  |                 |         |

| R = Readable  | e bit                        | W = Writable                            | bit             | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value at | POR                          | '1' = Bit is set                        |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|               |                              |                                         |                 |                  |                  |                 |         |

| bit 15        | Unimplemer                   | nted: Read as '                         | 0'              |                  |                  |                 |         |

| bit 14        |                              | lect CAN Bus L                          |                 | Vake-up bit      |                  |                 |         |

|               |                              | N bus line filter<br>line filter is not |                 | e-up             |                  |                 |         |

| bit 13-11     | Unimplemer                   | nted: Read as '                         | 0'              |                  |                  |                 |         |

| bit 10-8      | SEG2PH<2:0                   | 0>: Phase Segr                          | nent 2 bits     |                  |                  |                 |         |

|               | 111 = Length                 | -                                       |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | 000 = Length                 | n is 1 x Tq                             |                 |                  |                  |                 |         |

| bit 7         |                              | Phase Segmer                            | nt 2 Time Sele  | ct bit           |                  |                 |         |

|               | 1 = Freely pr<br>0 = Maximun | ogrammable<br>n of SEG1PHx I            | oits or Informa | tion Processin   | g Time (IPT), w  | hichever is gre | ater    |

| bit 6         | SAM: Sample                  | e of the CAN B                          | us Line bit     |                  |                  | -               |         |

|               |                              | is sampled three<br>is sampled once     |                 |                  |                  |                 |         |

| bit 5-3       | SEG1PH<2:0                   | 0>: Phase Segr                          | nent 1 bits     | -                |                  |                 |         |

|               | 111 = Length                 | n is 8 x Tq                             |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | 000 = Length                 |                                         |                 |                  |                  |                 |         |

| bit 2-0       |                              | >: Propagation                          | Time Segmen     | t bits           |                  |                 |         |

|               | 111 = Length                 | n is 8 x Tq                             |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               |                              |                                         |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

## REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup> (CONTINUED)

| bit 4 | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| bit 3 | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 2 | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 1 | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 0 | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

|       |                                                                                                                                                                                                |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

#### DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                                                  | Description                               | # of<br>Words                                                                                                                                                                   | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|--------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------|

| 46                 | MOV                  | MOV             | f,Wn                                             | Move f to Wn                              | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOV             | f                                                | Move f to f                               | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOV             | f,WREG                                           | Move f to WREG                            | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOV             | #litl6,Wn                                        | Move 16-bit literal to Wn                 | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOV.b           | #lit8,Wn                                         | Move 8-bit literal to Wn                  | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOV             | Wn,f                                             | Move Wn to f                              | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOV             | Wso,Wdo                                          | Move Ws to Wd                             | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOV             | WREG, f                                          | Move WREG to f                            | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOV.D           | Wns,Wd                                           | Move Double from W(ns):W(ns + 1) to<br>Wd | 1                                                                                                                                                                               | 2                             | None                     |

|                    |                      | MOV.D           | Ws , Wnd                                         | Move Double from Ws to W(nd +<br>1):W(nd) | 1                                                                                                                                                                               | 2                             | None                     |

| 47                 | MOVPAG               | MOVPAG          | #lit10,DSRPAG                                    | Move 10-bit literal to DSRPAG             | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOVPAG          | #lit9,DSWPAG                                     | Move 9-bit literal to DSWPAG              | 1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     1       1     2       1     2 | None                          |                          |

|                    |                      | MOVPAG          | #lit8,TBLPAG                                     | Move 8-bit literal to TBLPAG              | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOVPAG          | Ws, DSRPAG                                       | Move Ws<9:0> to DSRPAG                    | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOVPAG          | Ws, DSWPAG                                       | Move Ws<8:0> to DSWPAG                    | 1                                                                                                                                                                               | 1                             | None                     |

|                    |                      | MOVPAG          | Ws, TBLPAG                                       | Move Ws<7:0> to TBLPAG                    | 1                                                                                                                                                                               | 1                             | None                     |

| 48                 | MOVSAC               | MOVSAC          | Acc,Wx,Wxd,Wy,Wyd,AWB <sup>(1)</sup>             | Prefetch and store accumulator            | 1                                                                                                                                                                               | 1                             | None                     |

| 49                 | MPY                  | MPY             | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | Multiply Wm by Wn to Accumulator          | 1                                                                                                                                                                               | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY             | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>           | Square Wm to Accumulator                  | 1                                                                                                                                                                               | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 50                 | MPY.N                | MPY.N           | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | -(Multiply Wm by Wn) to Accumulator       | 1                                                                                                                                                                               | 1                             | None                     |

| 51                 | MSC                  | MSC             | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Subtract from Accumulator    | 1                                                                                                                                                                               | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACTERISTICS |        |                                                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |         |            |                        |  |

|--------------------|--------|---------------------------------------------------------|-------------------------------------------------------|-----|---------|------------|------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                          | Min. Typ. Max. Units                                  |     |         | Conditions |                        |  |

|                    | VIL    | Input Low Voltage                                       |                                                       |     |         |            |                        |  |

| DI10               |        | Any I/O Pin and MCLR                                    | Vss                                                   | —   | 0.2 VDD | V          |                        |  |

| DI18               |        | I/O Pins with SDAx, SCLx                                | Vss                                                   | —   | 0.3 VDD | V          | SMBus disabled         |  |

| DI19               |        | I/O Pins with SDAx, SCLx                                | Vss                                                   | —   | 0.8     | V          | SMBus enabled          |  |

|                    | VIH    | Input High Voltage                                      |                                                       |     |         |            |                        |  |

| DI20               |        | I/O Pins Not 5V Tolerant                                | 0.8 VDD                                               | —   | Vdd     | V          | (Note 3)               |  |

|                    |        | I/O Pins 5V Tolerant and MCLR                           | 0.8 VDD                                               | —   | 5.5     | V          | (Note 3)               |  |

|                    |        | I/O Pins with SDAx, SCLx                                | 0.8 VDD                                               | —   | 5.5     | V          | SMBus disabled         |  |

|                    |        | I/O Pins with SDAx, SCLx                                | 2.1                                                   | _   | 5.5     | V          | SMBus enabled          |  |

|                    | ICNPU  | Change Notification Pull-up Current                     |                                                       |     |         |            |                        |  |

| DI30               |        |                                                         | 150                                                   | 250 | 550     | μA         | VDD = 3.3V, VPIN = VSS |  |

|                    | ICNPD  | Change Notification<br>Pull-Down Current <sup>(4)</sup> |                                                       |     |         |            |                        |  |

| DI31               |        |                                                         | 20                                                    | 50  | 100     | μA         | Vdd = 3.3V, Vpin = Vdd |  |

#### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (VSS 0.3). Characterized but not tested.

**5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- 8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

| АС СНА       | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |                                               |              |          |           |       |                                                         |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------|----------|-----------|-------|---------------------------------------------------------|--|--|

| Param<br>No. | Symbol                                                                                                                                                                                                                                                                                        | Characteristic                                | Min.         | Тур.     | Max.      | Units | Conditions                                              |  |  |

|              |                                                                                                                                                                                                                                                                                               | ADC A                                         | ccuracy (    | 10-Bit N | lode)     |       |                                                         |  |  |

| AD20b        | Nr                                                                                                                                                                                                                                                                                            | Resolution                                    | 10 Data Bits |          | bits      |       |                                                         |  |  |

| AD21b        | INL                                                                                                                                                                                                                                                                                           | Integral Nonlinearity                         | -0.625       |          | 0.625     | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                             |  |  |

|              |                                                                                                                                                                                                                                                                                               |                                               | -1.5         |          | 1.5       | LSb   | +85°C < TA ≤ +125°C (Note 2)                            |  |  |

| AD22b        | DNL                                                                                                                                                                                                                                                                                           | Differential Nonlinearity                     | -0.25        | —        | 0.25      | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                             |  |  |

|              |                                                                                                                                                                                                                                                                                               |                                               | -0.25        | —        | 0.25      | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |  |  |

| AD23b        | Gerr                                                                                                                                                                                                                                                                                          | Gain Error                                    | -2.5         | —        | 2.5       | LSb   | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                   |  |  |

|              |                                                                                                                                                                                                                                                                                               |                                               | -2.5         |          | 2.5       | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |  |  |

| AD24b        | EOFF                                                                                                                                                                                                                                                                                          | Offset Error                                  | -1.25        | —        | 1.25      | LSb   | $-40^{\circ}C \le TA \le +85^{\circ}C \text{ (Note 2)}$ |  |  |

|              |                                                                                                                                                                                                                                                                                               |                                               | -1.25        | —        | 1.25      | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |  |  |

| AD25b        | —                                                                                                                                                                                                                                                                                             | Monotonicity                                  | _            |          | _         | —     | Guaranteed                                              |  |  |

|              |                                                                                                                                                                                                                                                                                               | Dynamic P                                     | erforman     | ce (10-E | Bit Mode) |       |                                                         |  |  |

| AD30b        | THD                                                                                                                                                                                                                                                                                           | Total Harmonic Distortion <sup>(3)</sup>      | _            | 64       |           | dB    |                                                         |  |  |

| AD31b        | SINAD                                                                                                                                                                                                                                                                                         | Signal to Noise and Distortion <sup>(3)</sup> |              | 57       |           | dB    |                                                         |  |  |

| AD32b        | SFDR                                                                                                                                                                                                                                                                                          | Spurious Free Dynamic<br>Range <sup>(3)</sup> | —            | 72       | —         | dB    |                                                         |  |  |

| AD33b        | Fnyq                                                                                                                                                                                                                                                                                          | Input Signal Bandwidth <sup>(3)</sup>         |              | 550      | —         | kHz   |                                                         |  |  |

| AD34b        | ENOB                                                                                                                                                                                                                                                                                          | Effective Number of Bits <sup>(3)</sup>       | _            | 9.4      | —         | bits  |                                                         |  |  |

#### TABLE 30-59: ADC MODULE SPECIFICATIONS (10-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

**3:** Parameters are characterized but not tested in manufacturing.

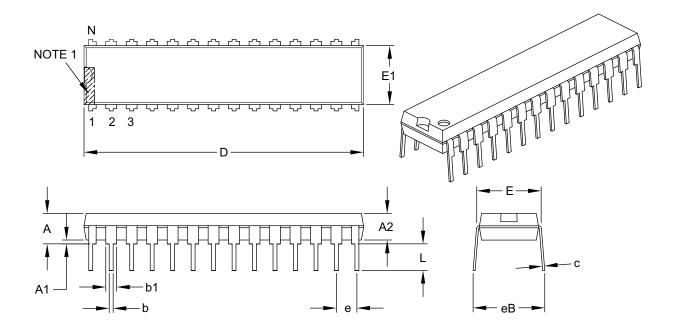

#### 33.2 Package Details

#### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES |          |       |       |  |  |

|----------------------------|--------|----------|-------|-------|--|--|

| Dimension                  | MIN    | NOM      | MAX   |       |  |  |

| Number of Pins             | Ν      |          | 28    |       |  |  |

| Pitch                      | е      | .100 BSC |       |       |  |  |

| Top to Seating Plane       | Α      | -        | -     | .200  |  |  |

| Molded Package Thickness   | A2     | .120     | .135  | .150  |  |  |

| Base to Seating Plane      | A1     | .015     | -     | -     |  |  |

| Shoulder to Shoulder Width | E      | .290     | .310  | .335  |  |  |

| Molded Package Width       | E1     | .240     | .285  | .295  |  |  |

| Overall Length             | D      | 1.345    | 1.365 | 1.400 |  |  |

| Tip to Seating Plane       | L      | .110     | .130  | .150  |  |  |