Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

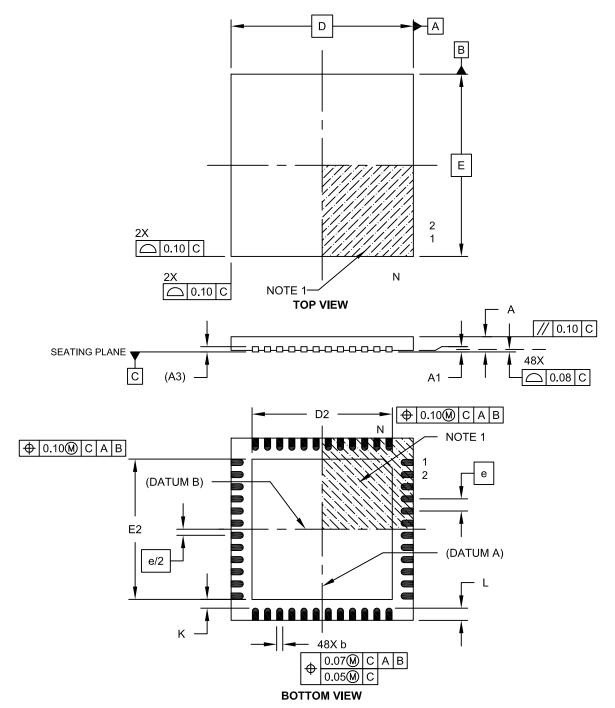

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp506-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

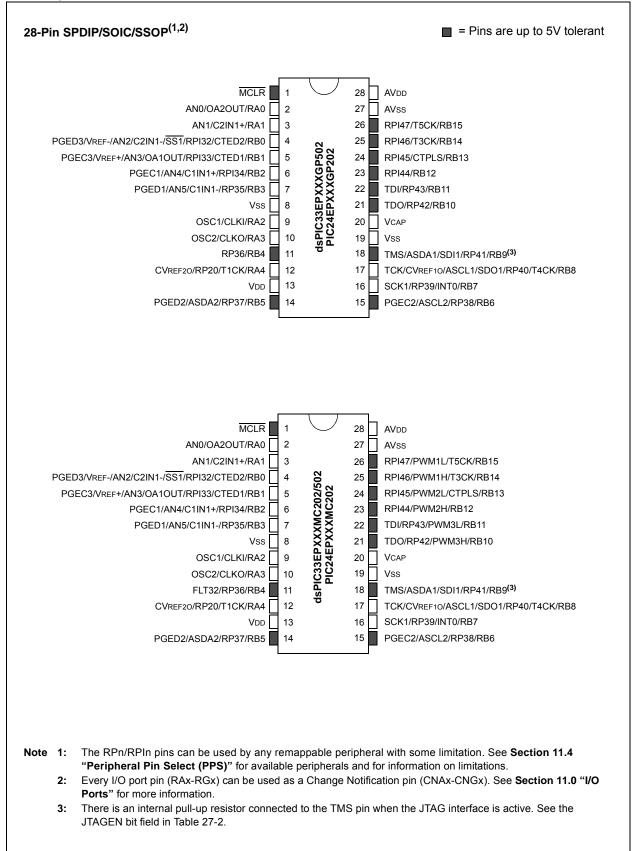

#### **Pin Diagrams**

| TABLE 4   | 4-9:  | INPUT                             | INPUT CAPTURE 1 THROUGH INPUT CAPTURE 4 REGISTER MAP |        |        |           |        |       |              |              |          |       |                     |                     |          |          |       |               |

|-----------|-------|-----------------------------------|------------------------------------------------------|--------|--------|-----------|--------|-------|--------------|--------------|----------|-------|---------------------|---------------------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15                            | Bit 14                                               | Bit 13 | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4               | Bit 3               | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _                                 | —                                                    | ICSIDL | 10     | CTSEL<2:0 | >      | —     | -            | —            | ICI<     | :0>   | ICOV                | ICOV ICBNE ICM<2:0> |          |          | 0000  |               |

| IC1CON2   | 0142  | _                                 | _                                                    |        | _      |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |                     | S                   | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144  |                                   |                                                      |        |        |           |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |       |                     |                     |          |          |       | xxxx          |

| IC1TMR    | 0146  |                                   |                                                      |        |        |           |        |       | Input Capt   | ture 1 Time  | r        |       |                     |                     |          |          |       | 0000          |

| IC2CON1   | 0148  |                                   | _                                                    | ICSIDL | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV ICBNE ICM<2:0> |                     |          |          | 0000  |               |

| IC2CON2   | 014A  | IC32 ICTRIG TRIGSTAT SYNCSEL<4:0> |                                                      |        |        |           |        |       | 000D         |              |          |       |                     |                     |          |          |       |               |

| IC2BUF    | 014C  |                                   |                                                      |        |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |                     |                     |          |          |       | xxxx          |

| IC2TMR    | 014E  |                                   |                                                      |        |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |                     |                     |          |          |       | 0000          |

| IC3CON1   | 0150  |                                   | _                                                    | ICSIDL | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV                | ICBNE               |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |                                   | _                                                    |        |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |                     | S                   | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |                                   |                                                      |        |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |                     |                     |          |          |       | xxxx          |

| IC3TMR    | 0156  |                                   |                                                      |        |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |                     |                     |          |          |       | 0000          |

| IC4CON1   | 0158  |                                   | _                                                    | ICSIDL | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV                | ICBNE               |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _                                 | _                                                    |        | _      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |                     | S                   | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  |                                   |                                                      |        |        |           |        | Inp   | ut Capture 4 | 4 Buffer Reg | gister   |       |                     |                     |          |          |       | xxxx          |

| IC4TMR    | 015E  |                                   |                                                      |        |        |           |        |       | Input Capt   | ure 4 Time   | r        |       |                     |                     |          |          |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

## 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|--------|-------|-------|--------|---------------------|-----|-------|-------|

| VAR    | —     | US1   | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15 | -     | •     |        |                     |     |       | bit 8 |

|        |       |       |        |                     |     |       |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7  |       | •     |        |                     |     |       | bit 0 |

|        |       |       |        |                     |     |       |       |

|        |       |       |        |                     |     |       |       |

# **REGISTER 7-2:** CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                      |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared | x = Bit is unknown |

bit

| VAR: Variable Exception Processing Latency Control                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>1 = Variable exception processing is enabled</li> </ol>                                                              |

| 0 = Fixed exception processing is enabled                                                                                     |

| IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                                |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

|                                                                                                                               |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| R/S-0                | U-0                                                                           | U-0                                                                              | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| FORCE <sup>(1)</sup> |                                                                               | _                                                                                | _                     | —                |                  | _               |         |  |  |  |  |

| bit 15               |                                                                               |                                                                                  |                       |                  |                  |                 | bit 8   |  |  |  |  |

|                      |                                                                               |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

| R/W-0                |                                                                               |                                                                                  |                       |                  |                  | R/W-0           | R/W-0   |  |  |  |  |

| IRQSEL7              | IRQSEL6                                                                       | IRQSEL5                                                                          | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |  |  |

| bit 7                |                                                                               |                                                                                  |                       |                  |                  |                 | bit     |  |  |  |  |

| Legend:              |                                                                               | S = Settable b                                                                   | oit                   |                  |                  |                 |         |  |  |  |  |

| R = Readable         | bit                                                                           | W = Writable                                                                     | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value at F      | POR                                                                           | '1' = Bit is set                                                                 |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |

|                      |                                                                               |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

| bit 15               | FORCE: Force                                                                  | e DMA Transfe                                                                    | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |  |  |

|                      | 1 = Forces a                                                                  | single DMA tra                                                                   | insfer (Manua         | l mode)          |                  |                 |         |  |  |  |  |

|                      | 0 = Automati                                                                  | c DMA transfer                                                                   | initiation by D       | DMA request      |                  |                 |         |  |  |  |  |

| bit 14-8             | Unimplemen                                                                    | ted: Read as 'd                                                                  | )'                    |                  |                  |                 |         |  |  |  |  |

| bit 7-0              | IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits                            |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 01000110 = ECAN1 – TX Data Request <sup>(2)</sup>                             |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00100110 = IC4 – Input Capture 4                                              |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00100101 = IC3 - Input Capture 3                                              |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                               | 00100010 = ECAN1 – RX Data Ready <sup>(2)</sup><br>00100001 = SPI2 Transfer Done |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                               | UART2TX – UA                                                                     |                       | itter            |                  |                 |         |  |  |  |  |

|                      |                                                                               | UART2RX – U                                                                      |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                               | TMR5 – Timer5                                                                    |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011011 = TMR4 – Timer4                                                      |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011010 = OC4 – Output Compare 4                                             |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011001 = OC3 – Output Compare 3                                             |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001101 = ADC1 – ADC1 Convert done<br>00001100 = UART1TX – UART1 Transmitter |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                               |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001011 = UART1RX – UART1 Receiver                                           |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001010 = SPI1 – Transfer Done                                               |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001000 = TMR3 – Timer3<br>00000111 = TMR2 – Timer2                          |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                               | OC2 – Output (                                                                   |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                               | IC2 – Input Ca                                                                   |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00000010 =                                                                    | OC1 – Output (                                                                   | Compare 1             |                  |                  |                 |         |  |  |  |  |

|                      |                                                                               | IC1 – Input Ca                                                                   |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00000000 = INT0 – External Interrupt 0                                        |                                                                                  |                       |                  |                  |                 |         |  |  |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

| R/W-0         | U-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ROON          |                                                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                   | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15        |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       | •                     | bit                   |

| U-0           | U-0                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |

|               | _                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | _                     |                       | _                     |                       |

| bit 7         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       | bit                   |

| Legend:       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| R = Readable  | e bit                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                                                                                   | U = Unimpler          | nented bit, read      | l as '0'              |                       |

| -n = Value at |                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as '                                                                                                                                                                                                                                                                                                                                        | out is disabled                                                                                                                                                                                                       |                       | .K pin <sup>(2)</sup> |                       |                       |

| bit 13        | -                                                                                                                                                                                                                                            | ference Oscilla                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       | en hit                |                       |                       |                       |

|               | 1 = Reference                                                                                                                                                                                                                                | e oscillator out<br>e oscillator out                                                                                                                                                                                                                                                                                                                                                                     | out continues                                                                                                                                                                                                         | to run in Sleep       |                       |                       |                       |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                               | erence Oscillato<br>crystal is used<br>lock is used as                                                                                                                                                                                                                                                                                                                                                   | as the refere                                                                                                                                                                                                         | nce clock             |                       |                       |                       |

| bit 11-8      | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>1000 = Refer<br>1011 = Refer<br>1001 = Refer<br>1000 = Refer<br>0111 = Refer<br>0111 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer<br>0011 = Refer | Reference Os<br>rence clock divi<br>rence clock divi | ded by 32,763<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 8                     |                       |                       |                       |

|               | 0000 = Refer                                                                                                                                                                                                                                 | ence clock                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                     |                       |                       |                       |                       |

## REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

## REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP118 | 3R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       |       |         |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0     | U-0   | U-0   |

| —      | —   |       | —     | _     | _       | —     | _     |

| bit 7  |     |       |       |       |         |       | bit 0 |

|        |     |       |       |       |         |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP118R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP118 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-----|-------|-------------|-------|-------|-------|-------|--|--|--|

| —     | —   |       | RP120R<5:0> |       |       |       |       |  |  |  |

| bit 7 |     |       |             |       |       |       | bit 0 |  |  |  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP120R<5:0>:** Peripheral Output Function is Assigned to RP120 Output Pin bits (see Table 11-3 for peripheral function numbers)

## 13.2 Timer Control Registers

| R/W-0         | U-0                                    | R/W-0                              | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |  |  |

|---------------|----------------------------------------|------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| TON           |                                        | TSIDL                              | —              | _                |                 |                 | _     |  |  |  |  |  |

| bit 15        |                                        |                                    |                |                  |                 |                 | bit 8 |  |  |  |  |  |

|               |                                        |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| U-0           | R/W-0                                  | R/W-0                              | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |  |  |

| _             | TGATE                                  | TCKPS1                             | TCKPS0         | T32              | _               | TCS             | _     |  |  |  |  |  |

| bit 7         |                                        |                                    |                |                  |                 |                 | bit ( |  |  |  |  |  |

| <u> </u>      |                                        |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| Legend:       | - 1-:4                                 |                                    |                | II II.           |                 |                 |       |  |  |  |  |  |

| R = Readable  |                                        | W = Writable                       |                | -                | nented bit, rea |                 |       |  |  |  |  |  |

| -n = Value at | POR                                    | '1' = Bit is set                   |                | '0' = Bit is cle | ared            | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15        | TON: Timerx                            | On hit                             |                |                  |                 |                 |       |  |  |  |  |  |

|               | When T32 = 2                           |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = Starts 32-                         | bit Timerx/y                       |                |                  |                 |                 |       |  |  |  |  |  |

|               | 0 = Stops 32-                          |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | <u>When T32 = 0</u><br>1 = Starts 16-  |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 0 = Stops 16-                          |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| bit 14        | Unimplemen                             | ted: Read as '                     | )'             |                  |                 |                 |       |  |  |  |  |  |

| bit 13        | TSIDL: Timer                           | x Stop in Idle M                   | lode bit       |                  |                 |                 |       |  |  |  |  |  |

|               |                                        | ues module op                      |                |                  | dle mode        |                 |       |  |  |  |  |  |

|               |                                        | s module opera                     |                | ode              |                 |                 |       |  |  |  |  |  |

| bit 12-7      | -                                      | ted: Read as '                     |                |                  |                 |                 |       |  |  |  |  |  |

| bit 6         |                                        | erx Gated Time                     | Accumulation   | Enable bit       |                 |                 |       |  |  |  |  |  |

|               | When TCS =<br>This bit is igno         |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | When TCS =                             |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = Gated time accumulation is enabled |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               |                                        | e accumulation                     |                |                  |                 |                 |       |  |  |  |  |  |

| bit 5-4       |                                        | : Timerx Input                     | Clock Prescal  | e Select bits    |                 |                 |       |  |  |  |  |  |

|               | 11 = 1:256<br>10 = 1:64                |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 01 = 1:8                               |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 00 = 1:1                               |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| bit 3         | T32: 32-Bit Ti                         | mer Mode Sele                      | ect bit        |                  |                 |                 |       |  |  |  |  |  |

|               |                                        | nd Timery form<br>nd Timery act as |                |                  |                 |                 |       |  |  |  |  |  |

| bit 2         | Unimplemen                             | ted: Read as '                     | )'             |                  |                 |                 |       |  |  |  |  |  |

| bit 1         | TCS: Timerx                            | Clock Source S                     | elect bit      |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl      | clock is from pir<br>lock (FP)     | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |  |  |  |

| bit 0         | Unimplomen                             | ted: Read as '                     | .,             |                  |                 |                 |       |  |  |  |  |  |

# REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

## 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| U-0                | U-0                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                               | R/W-0            | R/W-0             | R/W-0         |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|-------------------|---------------|

| _                  |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BLANKSEL3                                                                                           | BLANKSEL2        | BLANKSEL1         | BLANKSEL      |

| bit 15             |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   | bit           |