Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp506-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

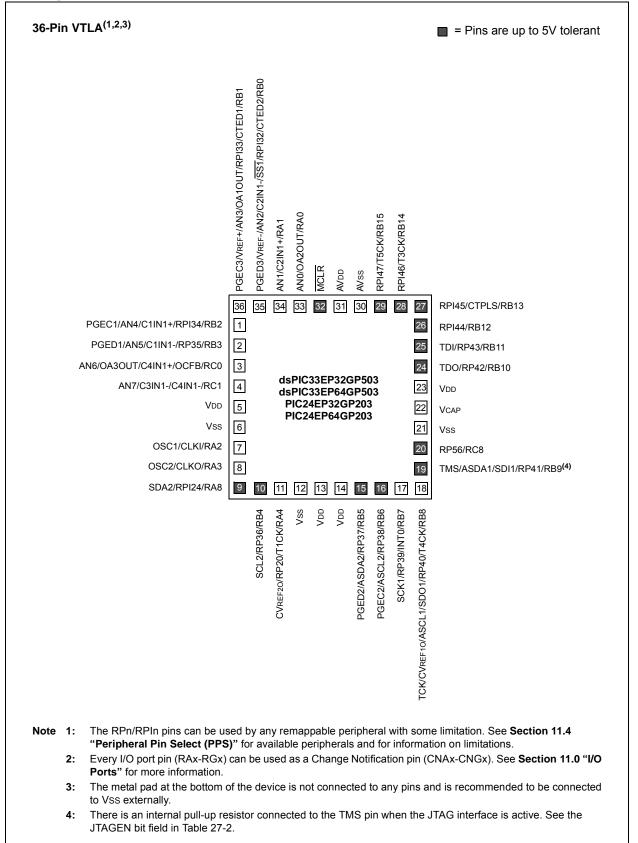

### **Pin Diagrams (Continued)**

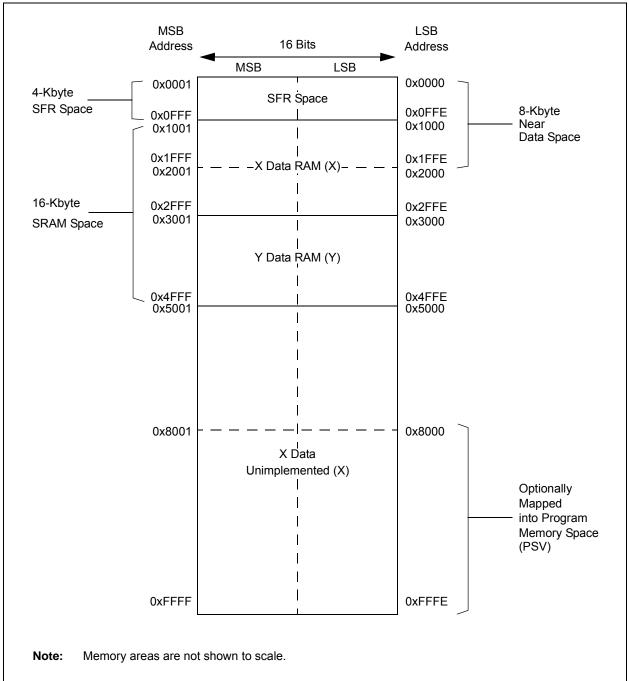

## FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

| IABLE 4-2  | 23: E | CAN1 I                  | REGIST | ER MA  | P WHE  | N WIN  | (CICIE   | <l1<0></l1<0> | •) = 1 FC | OR dsPIC | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|-------|-------------------------|--------|--------|--------|--------|----------|---------------|-----------|----------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr  | Bit 15                  | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9         | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | 046E  |                         |        |        | EID<   | :15:8> |          |               |           |          | EID<7:0> |        |        |        |        |       | xxxx  |               |

| C1RXF12SID | 0470  | 0470 SID<10:3>          |        |        |        |        |          |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472  | 1472 EID<15:8> EID<7:0> |        |        |        |        |          |               |           | xxxx     |          |        |        |        |        |       |       |               |

| C1RXF13SID | 0474  | '4 SID<10:3>            |        |        |        |        |          |               |           | SID<2:0> |          | _      | EXIDE  | —      | EID<1  | 7:16> | xxxx  |               |

| C1RXF13EID | 0476  |                         |        |        | EID<   | :15:8> |          |               |           | EID<7:0> |          |        |        |        | xxxx   |       |       |               |

| C1RXF14SID | 0478  |                         |        |        | SID<   | :10:3> |          |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A  | 047A EID<15:8>          |        |        |        |        | EID<7:0> |               |           |          |          | xxxx   |        |        |        |       |       |               |

| C1RXF15SID | 047C  | 7C SID<10:3>            |        |        |        |        |          |               |           | SID<2:0> |          | _      | EXIDE  | _      | EID<1  | 7:16> | xxxx  |               |

| C1RXF15EID | 047E  |                         |        |        | EID<   | :15:8> |          |               |           | EID<7:0> |          |        |        |        |        | xxxx  |       |               |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15        | Bit 14     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|---------------|------------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN          | SIZE       | DIR    | HALF   | NULLW  |        | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE         | _          | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |               |            |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _             | _          | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |               |            |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _             | STB<23:16> |        |        |        |        |       |        |       |       | 0000  |        |         |        |        |        |               |

| DMA0PAD   | 0B0C  |               | PAD<15:0>  |        |        |        |        |       |        |       |       |       | 0000   |         |        |        |        |               |

| DMA0CNT   | 0B0E  | CNT<13:0>     |            |        |        |        |        |       |        |       |       | 0000  |        |         |        |        |        |               |

| DMA1CON   | 0B10  | CHEN          | SIZE       | DIR    | HALF   | NULLW  | _      | —     | —      | _     | —     | AMOD  | E<1:0> | —       | _      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE         | _          | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |               |            |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _             | —          | _      | _      | _      | —      | —     | —      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |               |            |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _             | —          | _      | _      |        | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA1PAD   | 0B1C  | PAD<15:0>     |            |        |        |        |        |       |        |       | 0000  |       |        |         |        |        |        |               |

| DMA1CNT   | 0B1E  | — — CNT<13:0> |            |        |        |        |        |       |        |       | 0000  |       |        |         |        |        |        |               |

| DMA2CON   | 0B20  | CHEN          | SIZE       | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE         | _          | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |               |            |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _             | _          | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |               |            |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _             | _          | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |               |            |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _             | _          |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN          | SIZE       | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE         | _          | _      | _      | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |               |            |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _             | _          | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |               |            |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _             | _          | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |               |            |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _             | _          |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | _             | —          | —      | —      | —      | —      |       | _      | —     | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _             | —          | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _             | —          | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _             | _          | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |               |            |        |        |        |        |       | DSADR< | 15:0> |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  |               |            |        |        |        |        |       |        |       |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

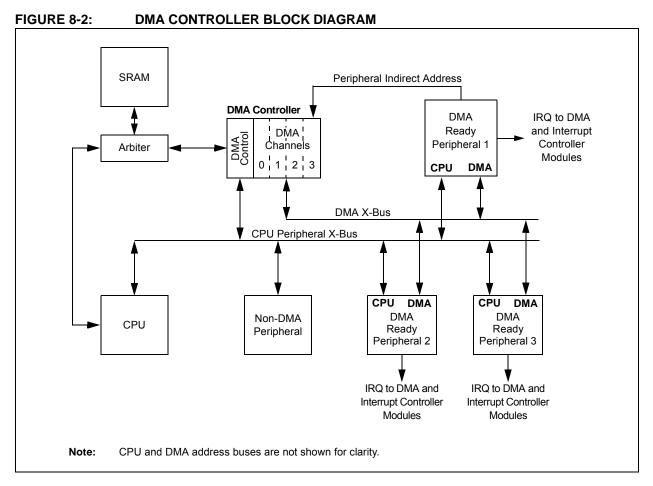

### 8.1 DMA Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 8.2 DMAC Registers

Each DMAC Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

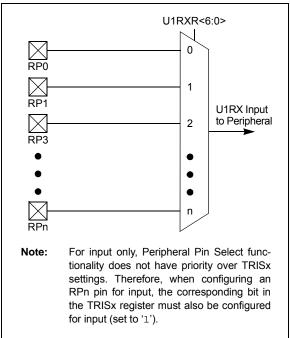

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/ comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

# EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

| RPINR15 = 0x2500; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */                   |

|-------------------|-----------------------------------------------------------------------|

| RPINR7 = 0x009;   | /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

| QEI1IOC = 0x4000; | /* Enable the QEI digital filter */                                   |

| QEI1CON = 0x8000; | /* Enable the QEI module */                                           |

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment          | Peripheral Pir<br>Select Input<br>Register Value |     | Pin Assignment |

|--------------------------------------------------|------------------|-------------------------|--------------------------------------------------|-----|----------------|

| 000 0000                                         | I                | Vss                     | 010 1101                                         |     | RPI45          |

| 000 0001                                         | I                | C1OUT <sup>(1)</sup>    | 010 1110                                         | I   | RPI46          |

| 000 0010                                         | I                | C2OUT <sup>(1)</sup>    | 010 1111                                         | I   | RPI47          |

| 000 0011                                         | I                | C3OUT <sup>(1)</sup>    | 011 0000                                         | _   | _              |

| 000 0100                                         | I                | C4OUT <sup>(1)</sup>    | 011 0001                                         |     | _              |

| 000 0101                                         | —                | _                       | 011 0010                                         | _   | _              |

| 000 0110                                         | I                | PTGO30 <sup>(1)</sup>   | 011 0011                                         | I   | RPI51          |

| 000 0111                                         | I                | PTGO31 <sup>(1)</sup>   | 011 0100                                         | I   | RPI52          |

| 000 1000                                         | I                | FINDX1 <sup>(1,2)</sup> | 011 0101                                         | I   | RPI53          |

| 000 1001                                         | I                | FHOME1 <sup>(1,2)</sup> | 011 0110                                         | I/O | RP54           |

| 000 1010                                         | _                | _                       | 011 0111                                         | I/O | RP55           |

| 000 1011                                         | —                | _                       | 011 1000                                         | I/O | RP56           |

| 000 1100                                         | —                | —                       | 011 1001                                         | I/O | RP57           |

| 000 1101                                         | _                |                         | 011 1010                                         | I   | RPI58          |

| 000 1110                                         | —                | —                       | 011 1011                                         | _   | —              |

| 000 1111                                         | —                | —                       | 011 1100                                         | _   | —              |

| 001 0000                                         | —                | _                       | 011 1101                                         | —   | _              |

| 001 0001                                         | —                | —                       | 011 1110                                         | _   | —              |

| 001 0010                                         | —                | —                       | 011 1111                                         | —   | —              |

| 001 0011                                         | —                | _                       | 100 0000                                         | —   | _              |

| 001 0100                                         | I/O              | RP20                    | 100 0001                                         |     | —              |

| 001 0101                                         | —                | —                       | 100 0010                                         | —   | —              |

| 001 0110                                         | —                | —                       | 100 0011                                         | _   | —              |

| 001 0111                                         | —                | —                       | 100 0100                                         |     | —              |

| 001 1000                                         | I                | RPI24                   | 100 0101                                         | _   | —              |

| 001 1001                                         | I                | RPI25                   | 100 0110                                         | _   | —              |

| 001 1010                                         | —                | —                       | 100 0111                                         |     | —              |

| 001 1011                                         | I                | RPI27                   | 100 1000                                         | _   | _              |

| 001 1100                                         | I                | RPI28                   | 100 1001                                         | _   |                |

| 001 1101                                         | —                | _                       | 100 1010                                         | _   | _              |

| 001 1110                                         | —                |                         | 100 1011                                         | _   |                |

| 001 1111                                         | —                |                         | 100 1100                                         | —   | _              |

| 010 0000                                         | I                | RPI32                   | 100 1101                                         | —   | _              |

| 010 0001                                         | I                | RPI33                   | 100 1110                                         | _   | _              |

| 010 0010                                         | I                | RPI34                   | 100 1111                                         | _   |                |

| 010 0011                                         | I/O              | RP35                    | 101 0000                                         | _   | <u> </u>       |

| 010 0100                                         | I/O              | RP36                    | 101 0001                                         | —   | _              |

| 010 0101                                         | I/O              | RP37                    | 101 0010                                         | —   | _              |

| 010 0110                                         | I/O              | RP38                    | 101 0011                                         | —   | _              |

| 010 0111                                         | I/O              | RP39                    | 101 0100                                         | _   | _              |

### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

#### 11.4.4.2 Output Mapping

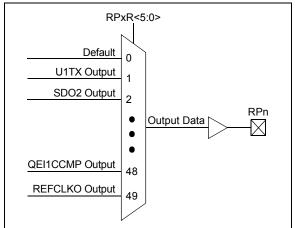

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

#### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|        |     |       |       | DD20  |         |       |       |

|--------|-----|-------|-------|-------|---------|-------|-------|

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       | RP35  | iR<5:0> |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

### REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP20  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

|       |     |       |       |       |        |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP37  | ′R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —     | —   |       | RP36R<5:0> |       |       |       |       |  |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP37R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP36R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers) |

NOTES:

### 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNC01 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

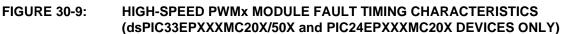

### 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

### 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32.

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0             | U-0                                            | U-0            | U-0                                     | U-0          | U-0                     | U-0                     | U-0         |

|-----------------|------------------------------------------------|----------------|-----------------------------------------|--------------|-------------------------|-------------------------|-------------|

| —               | —                                              | —              | _                                       | —            | —                       | —                       | _           |

| bit 15          |                                                |                |                                         |              |                         |                         | bit 8       |

|                 |                                                |                |                                         |              |                         |                         |             |

| U-0             | U-0                                            | U-0            | U-0                                     | U-0          | R/W-0                   | R/W-0                   | R/W-0       |

| —               | —                                              | —              | _                                       | —            | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |

| bit 7           |                                                |                |                                         |              |                         |                         | bit 0       |

|                 |                                                |                |                                         |              |                         |                         |             |

| Legend:         |                                                |                |                                         |              |                         |                         |             |

| R = Readable    | bit                                            | W = Writable   | bit                                     | U = Unimpler | mented bit, read        | as '0'                  |             |

| -n = Value at F | n = Value at POR '1' = Bit is set '0' = Bit is |                | '0' = Bit is cleared x = Bit is unknown |              |                         | own                     |             |

|                 |                                                |                |                                         |              |                         |                         |             |

| bit 15-3        | Unimplemen                                     | ted: Read as ' | י'                                      |              |                         |                         |             |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| R/W-0        | R/W-0                                                                                                    | R/W-0                              | R/W-0          | U-0                                                                                                | U-0                 | U-0              | U-0          |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------------------------------------------------------------------------------------------|---------------------|------------------|--------------|--|--|--|--|--|--|

|              | TRGD                                                                                                     | V<3:0>                             |                | —                                                                                                  |                     | —                | _            |  |  |  |  |  |  |

| bit 15       |                                                                                                          |                                    |                |                                                                                                    |                     |                  | bit 8        |  |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

| U-0          | U-0                                                                                                      | R/W-0                              | R/W-0          | R/W-0                                                                                              | R/W-0               | R/W-0            | R/W-0        |  |  |  |  |  |  |

| _            |                                                                                                          |                                    |                | TRGSTF                                                                                             | RT<5:0> <b>(1)</b>  |                  |              |  |  |  |  |  |  |

| bit 7        |                                                                                                          |                                    |                |                                                                                                    |                     |                  | bit          |  |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

| Legend:      | 1. 1.4                                                                                                   |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

| R = Readab   |                                                                                                          | W = Writable                       |                | •                                                                                                  | nented bit, read    |                  |              |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                                    | '1' = Bit is set                   |                | '0' = Bit is clea                                                                                  | ared                | x = Bit is unkn  | own          |  |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

| bit 15-12    |                                                                                                          | <b>)&gt;:</b> Trigger # Ou         | -              |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 1111 = Trigger output for every 16th trigger event                                                       |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 1110 = Trigger output for every 15th trigger event                                                       |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 1101 = Trigger output for every 14th trigger event<br>1100 = Trigger output for every 13th trigger event |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 1000 = Trigger output for every 13th trigger event<br>1011 = Trigger output for every 12th trigger event |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 1010 = Trigger output for every 11th trigger event                                                       |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | per output for ev                  |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | per output for ev                  |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 0101 = Trigger output for every 6th trigger event                                                        |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 0100 = Trigger output for every 5th trigger event                                                        |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 0011 = Trigger output for every 4th trigger event                                                        |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 0010 = Trigger output for every 3rd trigger event                                                        |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 0001 = Trigger output for every 2nd trigger event                                                        |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | 0000 = Trigg                                                                                             | ger output for ev                  | ery trigger ev | ent                                                                                                |                     |                  |              |  |  |  |  |  |  |

| bit 11-6     | -                                                                                                        | nted: Read as '                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

| bit 5-0      | TRGSTRT<                                                                                                 | 5:0>: Trigger Po                   | stscaler Start | Enable Select                                                                                      | bits <sup>(1)</sup> |                  |              |  |  |  |  |  |  |

| 011 3-0      | 111111 <b>=</b> W                                                                                        | aits 63 PWM cy                     | cles before g  | 111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled |                     |                  |              |  |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

|              | •                                                                                                        |                                    |                | ·                                                                                                  |                     |                  |              |  |  |  |  |  |  |

|              | •                                                                                                        |                                    |                | -                                                                                                  |                     |                  |              |  |  |  |  |  |  |

|              | •                                                                                                        |                                    |                | -                                                                                                  |                     |                  |              |  |  |  |  |  |  |

|              | •<br>•<br>•                                                                                              | aits 2 PW/M ava                    | les hefore co  | nerating the fire                                                                                  | t trigger event :   | after the module | a is anabled |  |  |  |  |  |  |

|              |                                                                                                          | /aits 2 PWM cyc<br>/aits 1 PWM cyc |                |                                                                                                    |                     |                  |              |  |  |  |  |  |  |

### REGISTER 16-12: TRGCONx: PWMx TRIGGER CONTROL REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|-------------------|-------|-----------------|-------|

|                                   |       |                  | TRGC                               | MP<15:8>          |       |                 |       |

| bit 15                            |       |                  |                                    |                   |       |                 | bit 8 |

|                                   |       |                  |                                    |                   |       |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                                   |       |                  | TRGC                               | MP<7:0>           |       |                 |       |

| bit 7                             |       |                  |                                    |                   |       |                 | bit 0 |

| Legend:                           |       |                  |                                    |                   |       |                 |       |

| R = Readable bit W = Writable bit |       | oit              | U = Unimplemented bit, read as '0' |                   |       |                 |       |

| -n = Value at P                   | OR    | '1' = Bit is set |                                    | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |

### REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 17-13: QEI1LECH: QEI1 LESS THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|----------------|-----------------|-------|

|                 |       |                  | QEILE | C<31:24>          |                |                 |       |

| bit 15          |       |                  |       |                   |                |                 | bit 8 |

|                 |       |                  |       |                   |                |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|                 |       |                  | QEILE | C<23:16>          |                |                 |       |

| bit 7           |       |                  |       |                   |                |                 | bit 0 |

|                 |       |                  |       |                   |                |                 |       |

| Legend:         |       |                  |       |                   |                |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplem      | ented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | red            | x = Bit is unkr | nown  |

bit 15-0 QEILEC<31:16>: High Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

### REGISTER 17-14: QEI1LECL: QEI1 LESS THAN OR EQUAL COMPARE LOW WORD REGISTER

| R = Readable t | R = Readable bitW = Writable bitn = Value at POR'1' = Bit is set |       |       | U = Unimplemented bit,<br>'0' = Bit is cleared |       | ad as '0'<br>x = Bit is unkr |       |

|----------------|------------------------------------------------------------------|-------|-------|------------------------------------------------|-------|------------------------------|-------|

| Legend:        |                                                                  |       |       |                                                |       |                              |       |

|                |                                                                  |       |       |                                                |       |                              |       |

| bit 7          |                                                                  |       |       |                                                |       |                              | bit   |

|                |                                                                  |       | QEIL  | EC<7:0>                                        |       |                              |       |

| R/W-0          | R/W-0                                                            | R/W-0 | R/W-0 | R/W-0                                          | R/W-0 | R/W-0                        | R/W-0 |

| bit 15         |                                                                  |       |       |                                                |       |                              | bit   |

|                |                                                                  |       | QEILE | EC<15:8>                                       |       |                              |       |

| R/W-0          | R/W-0                                                            | R/W-0 | R/W-0 | R/W-0                                          | R/W-0 | R/W-0                        | R/W-0 |

bit 15-0 QEILEC<15:0>: Low Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

### 21.4 ECAN Control Registers

| U-0             | U-0                                                                                                              | R/W-0                                                     | R/W-0                         | R/W-0                          | R/W-1            | R/W-0           | R/W-0  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------|--------------------------------|------------------|-----------------|--------|--|--|--|--|

| —               | —                                                                                                                | CSIDL                                                     | ABAT                          | CANCKS                         | REQOP2           | REQOP1          | REQOP0 |  |  |  |  |

| bit 15          |                                                                                                                  |                                                           |                               |                                |                  |                 | bit 8  |  |  |  |  |

| R-1             | R-0                                                                                                              | R-0                                                       | U-0                           | R/W-0                          | U-0              | U-0             | R/W-0  |  |  |  |  |

| OPMODE2         | OPMODE1                                                                                                          | OPMODE0                                                   | _                             | CANCAP                         |                  |                 | WIN    |  |  |  |  |

| bit 7           |                                                                                                                  |                                                           |                               |                                |                  |                 | bit (  |  |  |  |  |

| Legend:         |                                                                                                                  |                                                           |                               |                                |                  |                 |        |  |  |  |  |

| R = Readable    | bit                                                                                                              | W = Writable I                                            | oit                           | U = Unimpler                   | mented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value at F | OR                                                                                                               | '1' = Bit is set                                          |                               | '0' = Bit is cle               |                  | x = Bit is unkr | nown   |  |  |  |  |

|                 |                                                                                                                  |                                                           |                               |                                |                  |                 |        |  |  |  |  |

| bit 15-14       | Unimplemen                                                                                                       | ted: Read as 'o                                           | )'                            |                                |                  |                 |        |  |  |  |  |

| bit 13          | CSIDL: ECAN                                                                                                      | Nx Stop in Idle I                                         | Node bit                      |                                |                  |                 |        |  |  |  |  |

|                 |                                                                                                                  | ues module opera module opera                             |                               | device enters I<br>ode         | dle mode         |                 |        |  |  |  |  |

| bit 12          | ABAT: Abort                                                                                                      | All Pending Tra                                           | nsmissions b                  | bit                            |                  |                 |        |  |  |  |  |

|                 |                                                                                                                  | I transmit buffe<br>ill clear this bit                    |                               | ansmission<br>smissions are a  | aborted          |                 |        |  |  |  |  |

| bit 11          | CANCKS: ECANx Module Clock (FCAN) Source Select bit                                                              |                                                           |                               |                                |                  |                 |        |  |  |  |  |

|                 | 1 = FCAN is e<br>0 = FCAN is e                                                                                   | ·                                                         |                               |                                |                  |                 |        |  |  |  |  |

| bit 10-8        | 111 = Set Lis<br>110 = Reserv<br>101 = Reserv<br>100 = Set Co<br>011 = Set Lis<br>010 = Set Loc<br>001 = Set Dis | ed<br>nfiguration moo<br>ten Only mode<br>opback mode     | es mode<br>le                 | bits                           |                  |                 |        |  |  |  |  |

| bit 7-5         | 111 = Module<br>110 = Reserv<br>101 = Reserv<br>100 = Module                                                     |                                                           | Messages n<br>ation mode      | node                           |                  |                 |        |  |  |  |  |

|                 | 010 = Module<br>001 = Module<br>000 = Module                                                                     | e is in Loopback<br>e is in Disable n<br>e is in Normal C | mode<br>node<br>operation mod | de                             |                  |                 |        |  |  |  |  |

| bit 4           | -                                                                                                                | ted: Read as '                                            |                               |                                |                  |                 |        |  |  |  |  |

| bit 3           |                                                                                                                  | nput capture ba                                           |                               | Capture Event<br>message recei |                  |                 |        |  |  |  |  |

| bit 2-1         |                                                                                                                  | ted: Read as '(                                           | ı'                            |                                |                  |                 |        |  |  |  |  |

| bit 0           | -                                                                                                                | ap Window Sele                                            |                               |                                |                  |                 |        |  |  |  |  |

| UIL U           | 1 = Uses filter                                                                                                  | -                                                         | יטו טונ                       |                                |                  |                 |        |  |  |  |  |

### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|              | R/W-0         | U-0                 | U-0                         | U-0             | R/W-0                                | R/W-0                | R/W-0                |

|--------------|---------------|---------------------|-----------------------------|-----------------|--------------------------------------|----------------------|----------------------|

| CSS31        | CSS30         | —                   | —                           | _               | CSS26 <sup>(2)</sup>                 | CSS25 <sup>(2)</sup> | CSS24 <sup>(2)</sup> |

| bit 15       | - 1           |                     |                             |                 |                                      |                      | bit 8                |

|              |               |                     |                             |                 |                                      |                      |                      |

| U-0          | U-0           | U-0                 | U-0                         | U-0             | U-0                                  | U-0                  | U-0                  |

| _            |               | _                   | _                           | —               |                                      | _                    |                      |

| bit 7        |               |                     |                             |                 |                                      |                      | bit (                |

|              |               |                     |                             |                 |                                      |                      |                      |

| Legend:      |               |                     |                             |                 |                                      |                      |                      |

| R = Readab   | le bit        | W = Writable        | bit                         | U = Unimple     | emented bit, read                    | d as '0'             |                      |

| -n = Value a | t POR         | '1' = Bit is set    |                             | '0' = Bit is cl | eared                                | x = Bit is unk       | nown                 |

|              |               |                     |                             |                 |                                      |                      |                      |

| bit 15       |               | 1 Input Scan S      |                             |                 |                                      |                      |                      |

|              |               |                     |                             |                 | input scan (Ope                      |                      |                      |

|              | •             | •                   |                             | surement for ir | nput scan (Open                      | )                    |                      |

| bit 14       |               | 1 Input Scan S      |                             |                 |                                      |                      |                      |

|              |               |                     |                             |                 | or input scan (CT<br>input scan (CTN |                      |                      |

| bit 13-11    | Unimplemen    | ted: Read as '      | 0'                          |                 |                                      |                      |                      |

| bit 10       | CSS26: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              | 1 = Selects C | )<br>A3/AN6 for inp | ut scan                     |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 3/AN6 for input     | scan                        |                 |                                      |                      |                      |

| bit 9        | CSS25: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              | 1 = Selects C | 0A2/AN0 for inp     | ut scan                     |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 2/AN0 for input     | scan                        |                 |                                      |                      |                      |

| bit 8        | CSS24: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              |               | 0A1/AN3 for inp     |                             |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 1/AN3 for input     | scan                        |                 |                                      |                      |                      |

|              |               |                     |                             |                 |                                      |                      |                      |

### REGISTER 23-7: AD1CSSH: ADC1 INPUT SCAN SELECT REGISTER HIGH<sup>(1)</sup>

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                  | R/W-0 | R/W-0            | R/W-0            | R/W-0                | R/W-0                         | R/W-0              | R/W-0 |

|------------------------|-------|------------------|------------------|----------------------|-------------------------------|--------------------|-------|

|                        |       |                  | PTGT0            | _IM<15:8>            |                               |                    |       |

| bit 15                 |       |                  |                  |                      |                               |                    | bit 8 |

|                        |       |                  |                  |                      |                               |                    |       |

| R/W-0                  | R/W-0 | R/W-0            | R/W-0            | R/W-0                | R/W-0                         | R/W-0              | R/W-0 |

|                        |       |                  | PTGT0            | LIM<7:0>             |                               |                    |       |

| bit 7 bit 7            |       |                  |                  |                      |                               | bit 0              |       |

|                        |       |                  |                  |                      |                               |                    |       |

| Legend:                |       |                  |                  |                      |                               |                    |       |

| R = Readable bit W = V |       | W = Writable b   | W = Writable bit |                      | U = Unimplemented bit, read a |                    |       |

| -n = Value at POR      |       | '1' = Bit is set |                  | '0' = Bit is cleared |                               | x = Bit is unknown |       |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------|----------|-------|-------|-------|

|        |       |       | PTGT1LI | IM<15:8> |       |       |       |

| bit 15 |       |       |         |          |       |       |       |