Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256KB (85.5K x 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 16                                                                          |

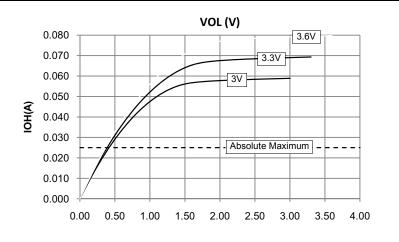

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gp506t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

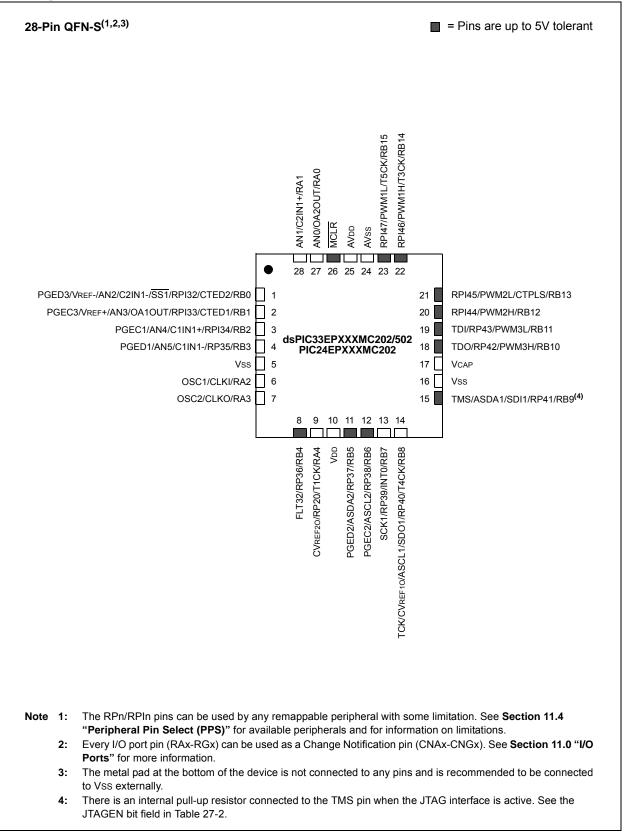

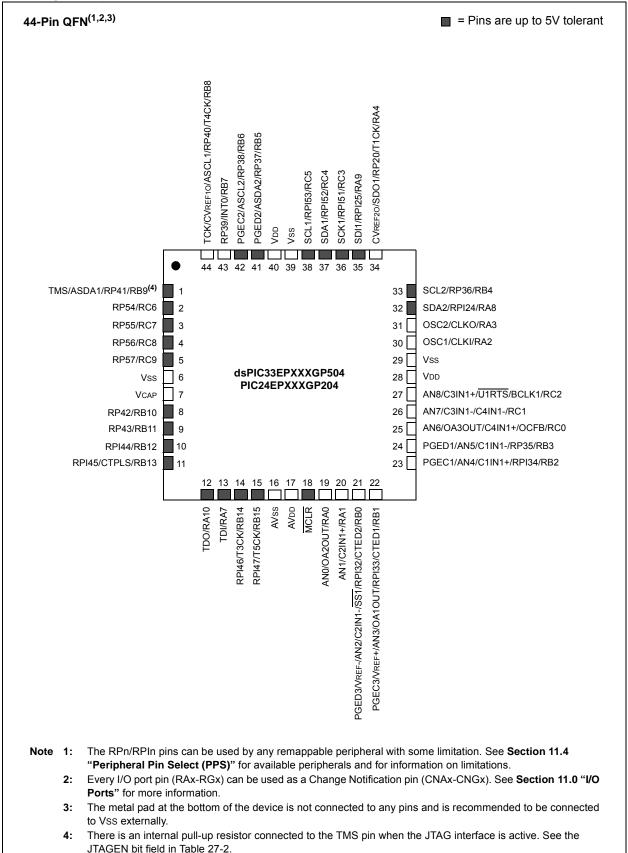

## Pin Diagrams (Continued)

#### **Pin Diagrams (Continued)**

| R/W-0               | U-0                          | R/W-0                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |

|---------------------|------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|

| VAR                 | —                            | US1 <sup>(1)</sup>                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |

| bit 15              |                              |                                                          |                         |                             |                           |                    | bit                |

| R/W-0               | R/W-0                        | R/W-1                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>          | SATDW <sup>(1)</sup>                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |

| bit 7               | I                            |                                                          |                         |                             | I                         | 1                  | bit                |

| Legend:             |                              | C = Clearable                                            | e bit                   |                             |                           |                    |                    |

| R = Readabl         | e bit                        | W = Writable                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |

| -n = Value at       | POR                          | '1' = Bit is set                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |

| bit 15              | 1 = Variable                 | le Exception Pro<br>exception proce                      | essing latency          | is enabled                  |                           |                    |                    |

| bit 14              |                              | nted: Read as '                                          |                         |                             |                           |                    |                    |

| bit 13-12           | -                            | SP Multiply Uns                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |

|                     | 01 = DSP er<br>00 = DSP er   | ngine multiplies<br>ngine multiplies<br>ngine multiplies | are unsigned are signed |                             |                           |                    |                    |

| bit 11              | •                            | O Loop Terminatives executing Dot<br>t                   |                         |                             | iteration                 |                    |                    |

| bit 10-8            |                              | Loop Nesting<br>oops are active                          |                         | (1)                         |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | 001 = 1 DO k<br>000 = 0 DO k | oop is active<br>oops are active                         |                         |                             |                           |                    |                    |

| bit 7               | SATA: ACCA                   | A Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator A saturatio<br>ator A saturatio                     |                         |                             |                           |                    |                    |

| bit 6               | SATB: ACCE                   | B Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator B saturatio<br>ator B saturatio                     |                         |                             |                           |                    |                    |

| bit 5               | SATDW: Dat                   | ta Space Write                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |

|                     |                              | ace write satura<br>ace write satura                     |                         | I                           |                           |                    |                    |

| bit 4               |                              | cumulator Satu                                           |                         | elect bit <sup>(1)</sup>    |                           |                    |                    |

|                     |                              | uration (super s<br>uration (normal                      | ,                       |                             |                           |                    |                    |

| bit 3               |                              | nterrupt Priority                                        |                         |                             |                           |                    |                    |

|                     |                              | errupt Priority Le<br>errupt Priority Le                 |                         |                             |                           |                    |                    |

|                     | nis bit is availabl          |                                                          | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP                | 50X devices on     | ly.                |

| 2: Th               | nis bit is always            | reau as 0.                                               |                         |                             |                           |                    |                    |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| IABLE 4-2  | 23: E                                                    | CAN1 I | REGIST    | ER MA  | P WHE  | N WIN  | (CICIE | <l1<0></l1<0> | •) = 1 FC | OR dsPIC                      | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|----------------------------------------------------------|--------|-----------|--------|--------|--------|--------|---------------|-----------|-------------------------------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr                                                     | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8     | Bit 7                         | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | 046E                                                     |        |           |        | EID<   | :15:8> |        |               |           |                               |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF12SID | RXF12SID 0470 SID<10:3> SID<2:0> - EXIDE - EID<17:16> xx |        |           |        |        |        |        |               |           | xxxx                          |          |        |        |        |        |       |       |               |

| C1RXF12EID | 0472                                                     |        | EID<15:8> |        |        |        |        |               | EID<7:0>  |                               |          |        |        |        | xxxx   |       |       |               |

| C1RXF13SID | 0474                                                     |        |           |        | SID<   | :10:3> |        |               |           | SID<2:0> — EXIDE — EID<17:16> |          |        |        |        | xxxx   |       |       |               |

| C1RXF13EID | 0476                                                     |        | EID<15:8> |        |        |        |        |               |           | EID<                          | 7:0>     |        |        |        | xxxx   |       |       |               |

| C1RXF14SID | 0478                                                     |        |           |        | SID<   | :10:3> |        |               |           |                               | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A                                                     |        |           |        | EID<   | :15:8> |        |               |           |                               |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF15SID | 047C                                                     |        |           |        | SID<   | :10:3> |        |               |           |                               | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF15EID | 047E                                                     |        |           |        | EID<   | :15:8> |        |               |           |                               |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | _      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | _      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | —      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-1        | R/W-0         | R/W-0                                                                                                                            | U-0           | U-0              | U-0              | U-0             | U-0    |  |  |  |  |  |

|--------------|---------------|----------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|--|--|--|--|--|

| GIE          | DISI          | SWTRAP                                                                                                                           |               |                  |                  | _               |        |  |  |  |  |  |

| bit 15       |               |                                                                                                                                  |               |                  |                  |                 | bit 8  |  |  |  |  |  |

|              |               |                                                                                                                                  |               |                  |                  |                 |        |  |  |  |  |  |

| U-0          | U-0           | U-0                                                                                                                              | U-0           | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

|              | —             |                                                                                                                                  |               |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |  |  |

| bit 7        |               |                                                                                                                                  |               |                  |                  |                 | bit C  |  |  |  |  |  |

| Legend:      |               |                                                                                                                                  |               |                  |                  |                 |        |  |  |  |  |  |

| R = Readab   | le bit        | W = Writable                                                                                                                     | bit           | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |  |  |

| -n = Value a |               | '1' = Bit is set                                                                                                                 |               | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |  |  |  |  |

|              |               |                                                                                                                                  |               |                  |                  |                 |        |  |  |  |  |  |

| bit 15       | GIE: Global   | Interrupt Enable                                                                                                                 | e bit         |                  |                  |                 |        |  |  |  |  |  |

|              | 1 = Interrupt | s and associate                                                                                                                  | d IE bits are | enabled          |                  |                 |        |  |  |  |  |  |

|              |               | s are disabled, I                                                                                                                | •             | still enabled    |                  |                 |        |  |  |  |  |  |

| bit 14       | DISI: DISI    | nstruction Statu                                                                                                                 | s bit         |                  |                  |                 |        |  |  |  |  |  |

|              |               | struction is active<br>struction is not a                                                                                        | -             |                  |                  |                 |        |  |  |  |  |  |

| bit 13       | SWTRAP: S     | Software Trap St                                                                                                                 | atus bit      |                  |                  |                 |        |  |  |  |  |  |

|              |               | e trap is enabled<br>e trap is disabled                                                                                          |               |                  |                  |                 |        |  |  |  |  |  |

| bit 12-3     | Unimpleme     | nted: Read as '                                                                                                                  | 0'            |                  |                  |                 |        |  |  |  |  |  |

| bit 2        | INT2EP: Ext   | ternal Interrupt 2                                                                                                               | 2 Edge Detec  | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |

|              |               | on negative edg                                                                                                                  |               |                  |                  |                 |        |  |  |  |  |  |

| bit 1        | INT1EP: Ext   | ternal Interrupt 1                                                                                                               | Edge Detec    | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |

|              |               | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge<br>0 = Interrupt on positive edge |               |                  |                  |                 |        |  |  |  |  |  |

| bit 0        | INTOEP: Ext   | INT0EP: External Interrupt 0 Edge Detect Polarity Select bit                                                                     |               |                  |                  |                 |        |  |  |  |  |  |

|              |               | on negative edg                                                                                                                  |               |                  |                  |                 |        |  |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

### REGISTER 8-3: DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0            | U-0   | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-------|----------------|-------|--------------|------------------|--------|-------|

| —              | _     | —              | —     | —            | —                | —      | —     |

| bit 15         |       |                |       |              |                  |        | bit 8 |

|                |       |                |       |              |                  |        |       |

| R/W-0          | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                |       |                | STA<  | 23:16>       |                  |        |       |

| bit 7          |       |                |       |              |                  |        | bit 0 |

|                |       |                |       |              |                  |        |       |

| Legend:        |       |                |       |              |                  |        |       |

| R = Readable b | oit   | W = Writable b | it    | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

### bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

#### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|----------------------------------------------------------------------|-------|------------------|-------|------------------|-------|-----------------|-------|

|                                                                      |       |                  | STA   | <15:8>           |       |                 |       |

| bit 15                                                               |       |                  |       |                  |       |                 | bit 8 |

|                                                                      |       |                  |       |                  |       |                 |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|                                                                      |       |                  | STA   | A<7:0>           |       |                 |       |

| bit 7                                                                |       |                  |       |                  |       |                 | bit 0 |

|                                                                      |       |                  |       |                  |       |                 |       |

| Legend:                                                              |       |                  |       |                  |       |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                  |       |                 |       |

| -n = Value at P                                                      | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared  | x = Bit is unki | nown  |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

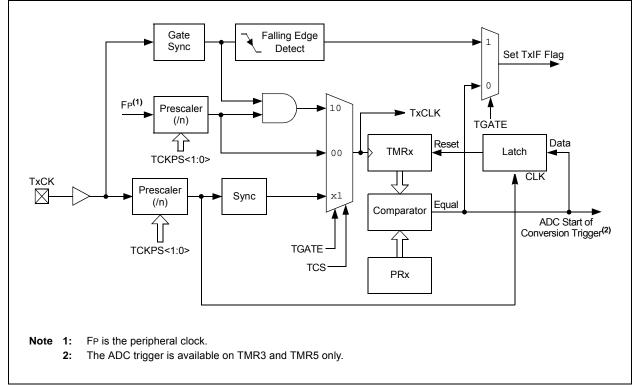

#### FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

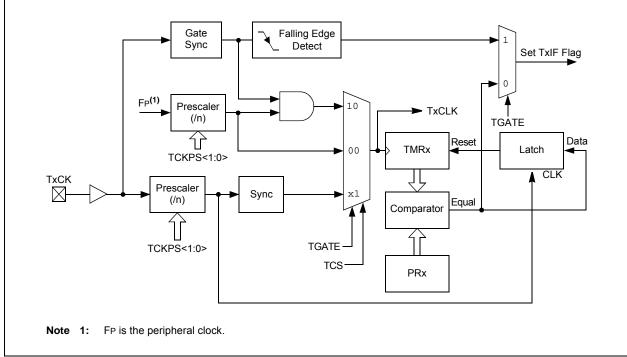

## FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

| R/W-1        | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 |

|--------------|-------|------------------|-------|--------------|------------------|----------|-------|

|              |       |                  | PTPE  | R<15:8>      |                  |          |       |

| bit 15       |       |                  |       |              |                  |          | bit 8 |

|              |       |                  |       |              |                  |          |       |

| R/W-1        | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-0            | R/W-0    | R/W-0 |

|              |       |                  | PTPE  | R<7:0>       |                  |          |       |

| bit 7        |       |                  |       |              |                  |          | bit 0 |

|              |       |                  |       |              |                  |          |       |

| Legend:      |       |                  |       |              |                  |          |       |

| R = Readable | bit   | W = Writable bit | t     | U = Unimpler | mented bit, read | l as '0' |       |

'0' = Bit is cleared

x = Bit is unknown

## REGISTER 16-3: PTPER: PWMx PRIMARY MASTER TIME BASE PERIOD REGISTER

bit 15-0 **PTPER<15:0>:** Primary Master Time Base (PMTMR) Period Value bits

'1' = Bit is set

#### REGISTER 16-4: SEVTCMP: PWMx PRIMARY SPECIAL EVENT COMPARE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | SEVTC | MP<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | SEVT  | CMP<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable bi  | t     | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 SEVTCMP<15:0>: Special Event Compare Count Value bits

-n = Value at POR

|                                   | R/W-0            | R/W-0           | R/W-0                                 | R/W-0                                                            | R/W-0                                                                                                | R/W-0                                                                                                    |

|-----------------------------------|------------------|-----------------|---------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                                   |                  | QEIG            | EC<31:24>                             |                                                                  |                                                                                                      |                                                                                                          |

|                                   |                  |                 |                                       |                                                                  |                                                                                                      | bit 8                                                                                                    |

|                                   | DAMO             |                 |                                       |                                                                  | DAMO                                                                                                 |                                                                                                          |

| R/W-U                             | R/W-0            |                 |                                       | R/W-U                                                            | R/W-U                                                                                                | R/W-0                                                                                                    |

|                                   |                  | QEIGE           | EC<23:16>                             |                                                                  |                                                                                                      |                                                                                                          |

|                                   |                  |                 |                                       |                                                                  |                                                                                                      | bit (                                                                                                    |

|                                   |                  |                 |                                       |                                                                  |                                                                                                      |                                                                                                          |

| R = Readable bit W = Writable bit |                  | t               | U = Unimplemented bit, read as '0'    |                                                                  |                                                                                                      |                                                                                                          |

| २                                 | '1' = Bit is set |                 | '0' = Bit is clea                     | ared                                                             | x = Bit is unkn                                                                                      | iown                                                                                                     |

|                                   | R/W-0            | W = Writable bi | R/W-0 R/W-0 QEIGI<br>W = Writable bit | R/W-0 R/W-0 R/W-0 QEIGEC<23:16><br>W = Writable bit U = Unimplem | R/W-0     R/W-0     R/W-0       QEIGEC<23:16>       W = Writable bit     U = Unimplemented bit, real | R/W-0       R/W-0       R/W-0       R/W-0         QEIGEC<23:16>       U = Unimplemented bit, read as '0' |

#### REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

#### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0                             | R/W-0                              | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-----------------------------------|------------------------------------|---------|-------|-------|-------|

|                                    |       |                                   | QEIGE                              | C<15:8> |       |       |       |

| bit 15                             |       |                                   |                                    |         |       |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0                             | R/W-0                              | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |                                   | QEIG                               | EC<7:0> |       |       |       |

| bit 7                              |       |                                   |                                    |         |       |       | bit 0 |

| Legend:                            |       |                                   |                                    |         |       |       |       |

| R = Readable bit W = Writable bit  |       |                                   | U = Unimplemented bit, read as '0' |         |       |       |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is u |                                    |         | nown  |       |       |

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | INTHL | D<31:24>          |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | INTHL | D<23:16>          |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable I  | bit   | W = Writable b   | oit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-0 INTHLD<31:16>: Hold Register for Reading and Writing INT1TMRH bits

## REGISTER 17-20: INT1HLDL: INTERVAL 1 TIMER HOLD LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0    | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|----------|-----------------|-------|-------|

|                                    |       |       | INTHL                              | .D<15:8> |                 |       |       |

| bit 15                             |       |       |                                    |          |                 |       | bit 8 |

|                                    |       |       |                                    |          |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0    | R/W-0           | R/W-0 | R/W-0 |

|                                    |       |       | INTH                               | _D<7:0>  |                 |       |       |

| bit 7                              |       |       |                                    |          |                 |       | bit 0 |

|                                    |       |       |                                    |          |                 |       |       |

| Legend:                            |       |       |                                    |          |                 |       |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimplemented bit, read as '0' |          |                 |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle                   | ared     | x = Bit is unkr | nown  |       |

|                                    |       |       |                                    |          |                 |       |       |

bit 15-0 INTHLD<15:0>: Hold Register for Reading and Writing INT1TMRL bits

# 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

#### 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                        | R/W-0                                                                                                               | R/W-0                                                                                                                                           | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                     | R/W-0                        | R/W-0  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------|--------|

| F15MSK<1:0>                                  |                                                                                                                     | F14MSK<1:0>                                                                                                                                     |                                                                                                                                                      | F13MSK<1:0>                                                                                                               |                                                                           | F12MSK<1:0>                  |        |

| bit 15                                       |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              | bit 8  |

| R/W-0                                        | R/W-0                                                                                                               | R/W-0                                                                                                                                           | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                     | R/W-0                        | R/W-0  |

|                                              | 1SK<1:0>                                                                                                            | F10MS                                                                                                                                           |                                                                                                                                                      |                                                                                                                           | K<1:0>                                                                    |                              | K<1:0> |

| bit 7                                        |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              | bit C  |

|                                              |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| Legend:                                      |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| R = Readabl                                  | le bit                                                                                                              | W = Writable                                                                                                                                    | bit                                                                                                                                                  | U = Unimplem                                                                                                              | nented bit, read                                                          | l as '0'                     |        |

| -n = Value at                                | t POR                                                                                                               | '1' = Bit is set                                                                                                                                |                                                                                                                                                      | '0' = Bit is cleared                                                                                                      |                                                                           | x = Bit is unknown           |        |

|                                              |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

|                                              |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| bit 15-14                                    | F15MSK<1:                                                                                                           | 0>: Mask Sourc                                                                                                                                  | e for Filter 15                                                                                                                                      | bits                                                                                                                      |                                                                           |                              |        |

| bit 15-14                                    | 11 = Reserv                                                                                                         | ed                                                                                                                                              |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| bit 15-14                                    | 11 = Reserv<br>10 = Accepta                                                                                         | ed<br>ance Mask 2 reg                                                                                                                           | gisters contair                                                                                                                                      | n mask                                                                                                                    |                                                                           |                              |        |

| bit 15-14                                    | 11 = Reserv<br>10 = Accepta<br>01 = Accepta                                                                         | ed                                                                                                                                              | gisters contair<br>gisters contair                                                                                                                   | n mask<br>n mask                                                                                                          |                                                                           |                              |        |

| bit 15-14<br>bit 13-12                       | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                         | ed<br>ance Mask 2 reg<br>ance Mask 1 reg                                                                                                        | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                | ies as bits<15∷                                                           | 14>)                         |        |

|                                              | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:                                            | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                                                     | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14                                                          | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu                                                                   |                                                                           |                              |        |

| bit 13-12                                    | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0                             | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc                                                         | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu                                                          | les as bits<15∷                                                           | 14>)                         |        |

| bit 13-12<br>bit 11-10                       | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:                  | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc                             | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu                                       | ies as bits<15:<br>ies as bits<15:                                        | 14>)<br>14>)                 |        |

| bit 13-12<br>bit 11-10<br>bit 9-8            | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:<br>F11MSK<1:     | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11                    | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu                    | ies as bits<15∷<br>ies as bits<15∷<br>es as bits<15:1                     | 14>)<br>14>)<br>14>)         |        |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6 | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F11MSK<1:0<br>F11MSK<1:0 | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Sourc<br>0>: Mask Sourc<br>0>: Mask Sourc<br>0>: Mask Sourc             | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 13<br>e for Filter 11<br>e for Filter 10 | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:1<br>ies as bits<15:1 | 14>)<br>14>)<br>14>)<br>14>) |        |

| R/W-0         | R/W-0                                                                                       | R/W-0                                                                                                                                                                                  | R/W-0                                                                                                                                     | R/W-0                                                                                    | R/W-0                                 | R/W-0           | R/W-0 |

|---------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------|-----------------|-------|

| ITRIM5        | ITRIM4                                                                                      | ITRIM3                                                                                                                                                                                 | ITRIM2                                                                                                                                    | ITRIM1                                                                                   | ITRIM0                                | IRNG1           | IRNG0 |

| bit 15        |                                                                                             |                                                                                                                                                                                        |                                                                                                                                           |                                                                                          |                                       |                 | bit   |

|               |                                                                                             |                                                                                                                                                                                        |                                                                                                                                           |                                                                                          |                                       |                 |       |

| U-0           | U-0                                                                                         | U-0                                                                                                                                                                                    | U-0                                                                                                                                       | U-0                                                                                      | U-0                                   | U-0             | U-0   |

|               |                                                                                             |                                                                                                                                                                                        | _                                                                                                                                         |                                                                                          | _                                     |                 | _     |

| bit 7         |                                                                                             |                                                                                                                                                                                        |                                                                                                                                           |                                                                                          |                                       |                 | bit   |

| Legend:       |                                                                                             |                                                                                                                                                                                        |                                                                                                                                           |                                                                                          |                                       |                 |       |

| R = Readabl   | e bit                                                                                       | W = Writable                                                                                                                                                                           | bit                                                                                                                                       | U = Unimplem                                                                             | nented bit, read                      | 1 as '0'        |       |

| -n = Value at | POR                                                                                         | '1' = Bit is set                                                                                                                                                                       |                                                                                                                                           | '0' = Bit is clea                                                                        |                                       | x = Bit is unkr | nown  |

|               |                                                                                             |                                                                                                                                                                                        |                                                                                                                                           |                                                                                          |                                       |                 |       |

|               | 011110 = Ma<br>•                                                                            | ximum positive                                                                                                                                                                         | e change from                                                                                                                             |                                                                                          | 1 + 00 /0                             |                 |       |

|               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | nimum positive<br>nimum positive<br>minal current c<br>nimum negative                                                                                                                  | change from r<br>change from r<br>output specified<br>e change from                                                                       | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren<br>nominal curren | + 4%<br>+ 2%<br>t – 2%                |                 |       |

|               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | nimum positive<br>nimum positive<br>minal current o<br>nimum negative<br>nimum negative<br>ximum negative                                                                              | change from r<br>change from r<br>output specified<br>e change from<br>e change from                                                      | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren                   | + 4%<br>+ 2%<br>-<br>t – 2%<br>t – 4% |                 |       |

| bit 9-8       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | nimum positive<br>nimum positive<br>minal current o<br>nimum negative<br>nimum negative<br>ximum negative<br>current Source<br>ase Current <sup>(2)</sup><br>se Current <sup>(2)</sup> | change from r<br>change from r<br>output specified<br>e change from<br>e change from<br>ve change from<br>e change from<br>a Range Select | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren<br>nominal curren | + 4%<br>+ 2%<br>-<br>t – 2%<br>t – 4% |                 |       |

#### REGISTER 22-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

2: Refer to the CTMU Current Source Specifications (Table 30-56) in Section 30.0 "Electrical Characteristics" for the current range selection values.

#### 25.1.2 OP AMP CONFIGURATION B

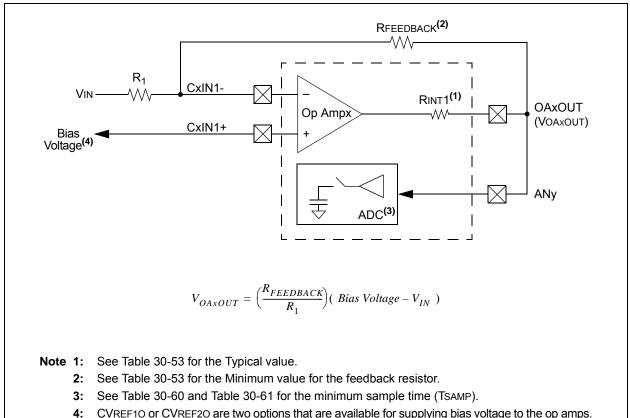

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

## 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | product page using the link above, enter    |  |  |  |  |  |

|       | this URL in your browser:                   |  |  |  |  |  |

|       | http://www.microchip.com/wwwproducts/       |  |  |  |  |  |

|       | Devices.aspx?dDocName=en555464              |  |  |  |  |  |

#### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 25-7: OP AMP CONFIGURATION B

| R/W-0         | R/W-0              | R/W-0                              | U-0                 | U-0              | R/W-0            | R/W-0               | R/W-0               |

|---------------|--------------------|------------------------------------|---------------------|------------------|------------------|---------------------|---------------------|

| CON           | COE <sup>(2)</sup> | CPOL                               | _                   | —                | OPMODE           | CEVT                | COUT                |

| bit 15        |                    |                                    |                     |                  |                  |                     | bit 8               |

|               |                    |                                    |                     |                  |                  |                     |                     |

| R/W-0         | R/W-0              | U-0                                | R/W-0               | U-0              | U-0              | R/W-0               | R/W-0               |

| EVPOL1        | EVPOL0             | —                                  | CREF <sup>(1)</sup> | _                | —                | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |

| bit 7         |                    |                                    |                     |                  |                  |                     | bit (               |

| Legend:       |                    |                                    |                     |                  |                  |                     |                     |

| R = Readabl   | e bit              | W = Writable                       | bit                 | U = Unimple      | mented bit, read | as '0'              |                     |

| -n = Value at | POR                | '1' = Bit is set                   |                     | '0' = Bit is cle | eared            | x = Bit is unkr     | nown                |

|               |                    |                                    |                     |                  |                  |                     |                     |

| bit 15        | CON: Op Am         | p/Comparator                       | Enable bit          |                  |                  |                     |                     |

|               |                    | comparator is e                    |                     |                  |                  |                     |                     |

|               |                    | comparator is d                    |                     |                  |                  |                     |                     |

| bit 14        |                    | arator Output Ei                   |                     |                  |                  |                     |                     |

|               |                    | tor output is pre                  |                     | CxOUT pin        |                  |                     |                     |

|               | -                  | tor output is int                  | -                   |                  |                  |                     |                     |

| bit 13        | •                  | parator Output I                   | •                   | t bit            |                  |                     |                     |