Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc202-h-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

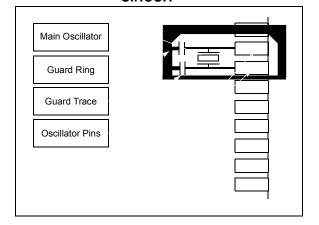

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        |        |        |        | RP35   | R<5:0> |       |       | _     | —     |       |       | RP20F | ₹<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        |        | RP37   | R<5:0> |       |       |       | —     |       |       | RP36F | <5:0>  |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |        | RP39   | R<5:0> |       |       |       | —     |       |       | RP38F | <5:0>  |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        |        | RP41   | R<5:0> |       |       |       | —     |       |       | RP40F | <5:0>  |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |        | RP43   | R<5:0> |       |       |       | —     |       |       | RP42F | <5:0>  |       |       | 0000          |

| RPOR5        | 068A  | _      | —      |        |        | RP55   | R<5:0> |       |       | _     | —     |       |       | RP54F | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  | _      | —      |        |        | RP57   | R<5:0> |       |       | _     | —     |       |       | RP56F | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6         | Bit 5        | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|---------------|--------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        |        | RP35F      | R<5:0> |       |       | _     | _             |              | •     | RP20F | R<5:0> |       | •     | 0000          |

| RPOR1        | 0682  | _      |        |        |        | RP37F      | R<5:0> |       |       | _     | _             |              |       | RP36  | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | —      |        |        | RP39F      | २<5:0> |       |       | _     | _             |              |       | RP38  | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | —      |        |        | RP41F      | २<5:0> |       |       | _     | _             |              |       | RP40  | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |        | RP43F      | २<5:0> |       |       | —     | _             |              |       | RP42  | R<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |        |        | RP55F      | २<5:0> |       |       | —     | _             | RP54R<5:0>   |       |       |        | 0000  |       |               |

| RPOR6        | 068C  | _      | _      |        |        | RP57R<5:0> |        |       |       | —     | _             | – RP56R<5:0> |       |       |        | 0000  |       |               |

| RPOR7        | 068E  | _      | _      |        |        | RP97F      | २<5:0> |       |       | —     | _             | _            | _     | _     | _      | _     | _     | 0000          |

| RPOR8        | 0690  |        | _      |        |        | RP118      | R<5:0> |       |       | _     |               |              |       |       | 0000   |       |       |               |

| RPOR9        | 0692  | —      | _      | _      | _      | _          | _      | _     | _     | _     | - RP120R<5:0> |              |       |       | 0000   |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-49: PORTD REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|--------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD        | 0E30  | _      | _      | _      |        | _      | _      | _     | TRISD8 |       | TRISD6 | TRISD5 |       |       |       |       | _     | 0160          |

| PORTD        | 0E32  | _      | _      |        | _      | _      | _      |       | RD8    | —     | RD6    | RD5    | —     | _     | _     | _     |       | xxxx          |

| LATD         | 0E34  | _      | _      |        | _      | _      | _      |       | LATD8  | —     | LATD6  | LATD5  | —     | _     | _     | _     |       | xxxx          |

| ODCD         | 0E36  | _      |        |        | -      |        |        |       | ODCD8  | —     | ODCD6  | ODCD5  | —     | _     | _     | _     |       | 0000          |

| CNEND        | 0E38  | _      |        |        | -      |        |        |       | CNIED8 | —     | CNIED6 | CNIED5 | —     | _     | _     | _     |       | 0000          |

| CNPUD        | 0E3A  | _      | _      |        | _      | _      | _      |       | CNPUD8 | —     | CNPUD6 | CNPUD5 | —     | _     | _     | _     |       | 0000          |

| CNPDD        | 0E3C  | _      | _      |        | _      | _      | _      |       | CNPDD8 | —     | CNPDD6 | CNPDD5 | —     | _     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-50: PORTE REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISE        | 0E40  | TRISE15 | TRISE14 | TRISE13 | TRISE12 | —      | _      | _     | —     | _     |       | -     | —     | —     | _     | —     |       | F000          |

| PORTE        | 0E42  | RE15    | RE14    | RE13    | RE12    | _      | —      | —     | —     | -     | —     | —     | _     | —     | —     | —     | —     | xxxx          |

| LATE         | 0E44  | LATE15  | LATE14  | LATE13  | LATE12  | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | xxxx          |

| ODCE         | 0E46  | ODCE15  | ODCE14  | ODCE13  | ODCE12  | —      | -      | -     | _     |       |       | -     | —     | —     | _     | _     | -     | 0000          |

| CNENE        | 0E48  | CNIEE15 | CNIEE14 | CNIEE13 | CNIEE12 | _      | —      | —     | —     | -     | —     | —     | _     | —     | —     | —     | —     | 0000          |

| CNPUE        | 0E4A  | CNPUE15 | CNPUE14 | CNPUE13 | CNPUE12 | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | 0000          |

| CNPDE        | 0E4C  | CNPDE15 | CNPDE14 | CNPDE13 | CNPDE12 | _      | _      | _     | _     | -     | _     | —     | _     | —     | _     | _     | _     | 0000          |

| ANSELE       | 0E4E  | ANSE15  | ANSE14  | ANSE13  | ANSE12  |        | —      | _     | —     | _     | _     | _     |       |       | _     |       | _     | F000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-51: PORTF REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISF        | 0E50  | —      | -      | —      |        | —      |        | —     | -     | -     | —     | -     | -     | —     | -     | TRISF1 | TRISF0 | 0003          |

| PORTF        | 0E52  | —      | —      | _      | —      | —      | —      | —     | _     | —     | —     | —     | —     | —     | —     | RF1    | RF0    | xxxx          |

| LATF         | 0E54  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | LATF1  | LATF0  | xxxx          |

| ODCF         | 0E56  | _      | -      | _      | -      | —      | -      | —     |       |       | —     |       |       | _     | -     | ODCF1  | ODCF0  | 0000          |

| CNENF        | 0E58  |        | —      | -      |        | —      | -      | _     | -     | -     | —     | -     | -     | —     | -     | CNIEF1 | CNIEF0 | 0000          |

| CNPUF        | 0E5A  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | CNPUF1 | CNPUF0 | 0000          |

| CNPDF        | 0E5C  | _      | _      | _      | _      | -      |        | _     | _     | _     | _     | _     | _     | _     | -     | CNPDF1 | CNPDF0 | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

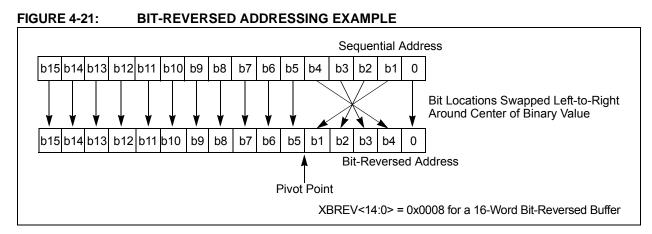

## TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      |    |    | Bit-Rev | ersed Ac | ldress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

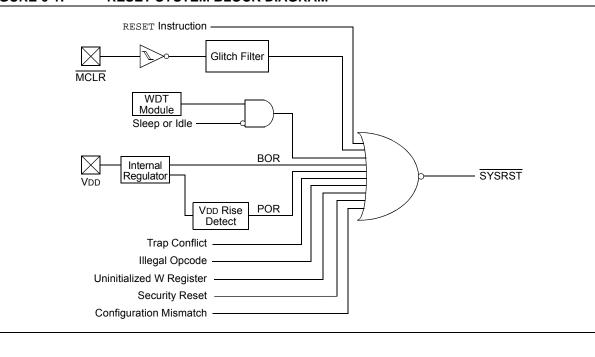

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

NOTES:

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 16.3 PWMx Control Registers

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 | •                       |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit | t                  |

|-------------------|-----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re  | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15  | PTEN: PWMx Module Enable bit                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = PWMx module is enabled</li> <li>0 = PWMx module is disabled</li> </ul>                                                                     |

| bit 14  | Unimplemented: Read as '0'                                                                                                                              |

| bit 13  | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                            |

|         | <ul> <li>1 = PWMx time base halts in CPU Idle mode</li> <li>0 = PWMx time base runs in CPU Idle mode</li> </ul>                                         |

| bit 12  | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|         | <ul> <li>1 = Special event interrupt is pending</li> <li>0 = Special event interrupt is not pending</li> </ul>                                          |

| bit 11  | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|         | 1 = Special event interrupt is enabled                                                                                                                  |

|         | 0 = Special event interrupt is disabled                                                                                                                 |

| bit 10  | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Active Period register is updated immediately</li> <li>0 = Active Period register updates occur on PWMx cycle boundaries</li> </ul>        |

| bit 9   | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                       |

|         | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)                                                                                                     |

|         | 0 = SYNCI1/SYNCO1 is active-high                                                                                                                        |

| bit 8   | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                               |

|         | 1 = SYNCO1 output is enabled                                                                                                                            |

| L:1 7   | 0 = SYNCO1 output is disabled                                                                                                                           |

| bit 7   | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|         | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

|         |                                                                                                                                                         |

| Note 1: | These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user                                                   |

|         | application must program the period register with a value that is slightly larger than the expected period of                                           |

the external synchronization input signal.

2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

#### REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

- bit 7-3 FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator # bits 11111 = Fault 32 (default) 11110 = Reserved . . 01100 = Reserved 01011 = Comparator 4 01010 = Op Amp/Comparator 3

- 01001 = Op Amp/Comparator 2

- 01000 = Op Amp/Comparator 1

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = Reserved

- 00011 = Fault 4

- 00010 = Fault 3

- 00001 = Fault 2 00000 = Fault 1

- bit 2 **FLTPOL:** Fault Polarity for PWM Generator # bit<sup>(2)</sup>

- 1 = The selected Fault source is active-low

- 0 = The selected Fault source is active-high

- bit 1-0 **FLTMOD<1:0>:** Fault Mode for PWM Generator # bits

- 11 = Fault input is disabled

- 10 = Reserved

- 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

- 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

- **Note 1:** If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

- 2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| R/W-0         | R/W-0                                                                                                                                    | R/W-0             | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0    |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-------------------|-----------------|-----------------|----------|--|--|--|

| EDG1MOD       | EDG1POL                                                                                                                                  | EDG1SEL3          | EDG1SEL2         | EDG1SEL1          | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |  |

| bit 15        |                                                                                                                                          | 1                 |                  | 11                |                 |                 | bit 8    |  |  |  |

|               |                                                                                                                                          |                   |                  |                   |                 |                 |          |  |  |  |

| R/W-0         | R/W-0                                                                                                                                    | R/W-0             | R/W-0            | R/W-0             | R/W-0           | U-0             | U-0      |  |  |  |

| EDG2MOD       | EDG2POL                                                                                                                                  | EDG2SEL3          | EDG2SEL2         | EDG2SEL1          | EDG2SEL0        | _               | _        |  |  |  |

| bit 7         |                                                                                                                                          |                   |                  | 1 1               |                 |                 | bit C    |  |  |  |

|               |                                                                                                                                          |                   |                  |                   |                 |                 |          |  |  |  |

| Legend:       |                                                                                                                                          |                   |                  |                   |                 |                 |          |  |  |  |

| R = Readabl   | le bit                                                                                                                                   | W = Writable      | oit              | U = Unimplem      | ented bit, read | l as '0'        |          |  |  |  |

| -n = Value at | POR                                                                                                                                      | '1' = Bit is set  |                  | '0' = Bit is clea | red             | x = Bit is unkr | nown     |  |  |  |

|               |                                                                                                                                          |                   |                  |                   |                 |                 |          |  |  |  |

| bit 15        | EDG1MOD: E                                                                                                                               | Edge 1 Edge Sa    | ampling Mode     | Selection bit     |                 |                 |          |  |  |  |

|               | 1 = Edge 1 is                                                                                                                            | s edge-sensitive  | 9                |                   |                 |                 |          |  |  |  |

|               | •                                                                                                                                        | s level-sensitive |                  |                   |                 |                 |          |  |  |  |

| bit 14        |                                                                                                                                          | dge 1 Polarity    |                  |                   |                 |                 |          |  |  |  |

|               | <ul> <li>1 = Edge 1 is programmed for a positive edge response</li> <li>0 = Edge 1 is programmed for a negative edge response</li> </ul> |                   |                  |                   |                 |                 |          |  |  |  |

| L:1 40 40     | •                                                                                                                                        |                   | •                | •                 |                 |                 |          |  |  |  |

| bit 13-10     |                                                                                                                                          | :0>: Edge 1 So    | urce Select bits | 5                 |                 |                 |          |  |  |  |

|               | 1xxx = Reserved<br>01xx = Reserved                                                                                                       |                   |                  |                   |                 |                 |          |  |  |  |

|               | 011x = Reserved<br>0011 = CTED1 pin                                                                                                      |                   |                  |                   |                 |                 |          |  |  |  |

|               | 0010 = CTED2 pin                                                                                                                         |                   |                  |                   |                 |                 |          |  |  |  |

|               | 0001 = OC1 module                                                                                                                        |                   |                  |                   |                 |                 |          |  |  |  |

| hit 0         | 0000 = Timer1 module                                                                                                                     |                   |                  |                   |                 |                 |          |  |  |  |

| bit 9         | EDG2STAT: Edge 2 Status bit                                                                                                              |                   |                  |                   |                 |                 |          |  |  |  |

|               | Indicates the status of Edge 2 and can be written to control the edge source.<br>1 = Edge 2 has occurred                                 |                   |                  |                   |                 |                 |          |  |  |  |

|               | 1 = Edge 2 has occurred<br>0 = Edge 2 has not occurred                                                                                   |                   |                  |                   |                 |                 |          |  |  |  |

| bit 8         | EDG1STAT: Edge 1 Status bit                                                                                                              |                   |                  |                   |                 |                 |          |  |  |  |

|               | Indicates the status of Edge 1 and can be written to control the edge source.                                                            |                   |                  |                   |                 |                 |          |  |  |  |

|               | 1 = Edge 1 has occurred<br>0 = Edge 1 has not occurred                                                                                   |                   |                  |                   |                 |                 |          |  |  |  |

|               | -                                                                                                                                        |                   |                  |                   |                 |                 |          |  |  |  |

| bit 7         | EDG2MOD: Edge 2 Edge Sampling Mode Selection bit                                                                                         |                   |                  |                   |                 |                 |          |  |  |  |

|               | <ul> <li>1 = Edge 2 is edge-sensitive</li> <li>0 = Edge 2 is level-sensitive</li> </ul>                                                  |                   |                  |                   |                 |                 |          |  |  |  |

| bit 6         | EDG2POL: Edge 2 Polarity Select bit                                                                                                      |                   |                  |                   |                 |                 |          |  |  |  |

| Sit 0         | 1 = Edge 2 is programmed for a positive edge response                                                                                    |                   |                  |                   |                 |                 |          |  |  |  |

|               | 0 = Edge 2 is programmed for a negative edge response                                                                                    |                   |                  |                   |                 |                 |          |  |  |  |

| bit 5-2       | EDG2SEL<3:0>: Edge 2 Source Select bits                                                                                                  |                   |                  |                   |                 |                 |          |  |  |  |

|               | 1111 = Reserved                                                                                                                          |                   |                  |                   |                 |                 |          |  |  |  |

|               | 01xx = Reserved                                                                                                                          |                   |                  |                   |                 |                 |          |  |  |  |

|               | 0100 = CMP <sup>2</sup><br>0011 = CTEE                                                                                                   |                   |                  |                   |                 |                 |          |  |  |  |

|               | 0010 = CTEE                                                                                                                              |                   |                  |                   |                 |                 |          |  |  |  |

|               | 0001 = OC1 module                                                                                                                        |                   |                  |                   |                 |                 |          |  |  |  |

|               | 0001 = OC1                                                                                                                               | module            |                  |                   |                 |                 |          |  |  |  |

|               |                                                                                                                                          | module            |                  |                   |                 |                 |          |  |  |  |

#### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

## 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/ PIC24 Family Reference Manual".

### 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en555464                                                                                                                          |

### 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

| U-0          | U-0                                   | U-0                 | U-0              | U-0              | U-0              | U-0            | U-0    |  |  |  |  |

|--------------|---------------------------------------|---------------------|------------------|------------------|------------------|----------------|--------|--|--|--|--|

|              | —                                     | —                   | _                | —                |                  | —              | _      |  |  |  |  |

| bit 15       |                                       |                     |                  |                  |                  |                | bit    |  |  |  |  |

|              |                                       |                     |                  |                  |                  |                |        |  |  |  |  |

| U-0          | R/W-0                                 | R/W-0               | R/W-0            | R/W-0            | R/W-0            | R/W-0          | R/W-0  |  |  |  |  |

|              | CFSEL2                                | CFSEL1              | CFSEL0           | CFLTREN          | CFDIV2           | CFDIV1         | CFDIV0 |  |  |  |  |

| bit 7        |                                       |                     |                  |                  |                  |                | bit    |  |  |  |  |

| Legend:      |                                       |                     |                  |                  |                  |                |        |  |  |  |  |

| R = Readab   | le bit                                | W = Writable        | bit              | U = Unimpler     | mented bit, read | as '0'         |        |  |  |  |  |

| -n = Value a |                                       | '1' = Bit is set    |                  | '0' = Bit is cle |                  | x = Bit is unk | nown   |  |  |  |  |

|              |                                       |                     |                  |                  |                  |                | -      |  |  |  |  |

| bit 15-7     | Unimplemen                            | ted: Read as        | ʻ0'              |                  |                  |                |        |  |  |  |  |

| bit 6-4      | CFSEL<2:0>                            | : Comparator        | Filter Input Clo | ock Select bits  |                  |                |        |  |  |  |  |

|              | 111 = T5CLK                           |                     | ·                |                  |                  |                |        |  |  |  |  |

|              | 110 = T4CLK                           |                     |                  |                  |                  |                |        |  |  |  |  |

|              | 101 = T3CLK                           | $101 = T3CLK^{(1)}$ |                  |                  |                  |                |        |  |  |  |  |

|              | 100 = T2CLK                           | <mark>(</mark> (2)  |                  |                  |                  |                |        |  |  |  |  |

|              | 011 = Reserv                          |                     |                  |                  |                  |                |        |  |  |  |  |

|              | 010 = SYNC                            | 01 <sup>(3)</sup>   |                  |                  |                  |                |        |  |  |  |  |

|              |                                       | $001 = Fosc^{(4)}$  |                  |                  |                  |                |        |  |  |  |  |

|              | 000 = FP <sup>(4)</sup>               |                     |                  |                  |                  |                |        |  |  |  |  |

| bit 3        | CFLTREN: Comparator Filter Enable bit |                     |                  |                  |                  |                |        |  |  |  |  |

|              | 1 = Digital filter is enabled         |                     |                  |                  |                  |                |        |  |  |  |  |

|              | •                                     | er is disabled      |                  |                  |                  |                |        |  |  |  |  |

| bit 2-0      | CFDIV<2:0>:                           | : Comparator F      | ilter Clock Div  | vide Select bits |                  |                |        |  |  |  |  |

|              | 111 = Clock Divide 1:128              |                     |                  |                  |                  |                |        |  |  |  |  |

|              | 110 = Clock Divide 1:64               |                     |                  |                  |                  |                |        |  |  |  |  |

|              | 101 = Clock Divide 1:32               |                     |                  |                  |                  |                |        |  |  |  |  |

|              | 100 = Clock Divide 1:16               |                     |                  |                  |                  |                |        |  |  |  |  |

|              | 011 = Clock Divide 1:8                |                     |                  |                  |                  |                |        |  |  |  |  |

|              | 010 = Clock Divide 1:4                |                     |                  |                  |                  |                |        |  |  |  |  |

|              | 001 = Clock Divide 1:2                |                     |                  |                  |                  |                |        |  |  |  |  |

|              | 000 = Clock                           | Divide 1:1          |                  |                  |                  |                |        |  |  |  |  |

| Note 1: S    | See the Type C Ti                     | mer Block Diag      | gram (Figure 1   | 3-2).            |                  |                |        |  |  |  |  |

|              | See the Type B Ti                     |                     |                  |                  |                  |                |        |  |  |  |  |

| •            |                                       |                     |                  |                  |                  |                |        |  |  |  |  |

# REGISTER 25-6: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

- 3: See the High-Speed PWMx Module Register Interconnection Diagram (Figure 16-2).

- 4: See the Oscillator System Diagram (Figure 9-1).

| Base<br>Instr<br># Assembly<br>Mnemonic<br>25 DAW |      | Assembly Syntax DAW Wn |                                                  | Description                                 | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|---------------------------------------------------|------|------------------------|--------------------------------------------------|---------------------------------------------|---------------|-------------------------------|--------------------------|

|                                                   |      |                        |                                                  | Wn = decimal adjust Wn                      |               | 1                             | С                        |

| 26                                                | DEC  | DEC                    | f                                                | f = f - 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                                                   |      | DEC                    | f,WREG                                           | WREG = f – 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                                                   |      | DEC                    | Ws,Wd                                            | Wd = Ws - 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 27                                                | DEC2 | DEC2                   | f                                                | f = f - 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                                                   |      | DEC2                   | f,WREG                                           | WREG = f – 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                                                   |      | DEC2                   | Ws,Wd                                            | Wd = Ws - 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 28                                                | DISI | DISI                   | #lit14                                           | Disable Interrupts for k instruction cycles | 1             | 1                             | None                     |

| 29                                                | DIV  | DIV.S                  | Wm,Wn                                            | Signed 16/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                                                   |      | DIV.SD                 | Wm,Wn                                            | Signed 32/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                                                   |      | DIV.U                  | Wm,Wn                                            | Unsigned 16/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

|                                                   |      | DIV.UD                 | Wm,Wn                                            | Unsigned 32/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

| 30                                                | DIVF | DIVF                   | Wm , Wn <sup>(1)</sup>                           | Signed 16/16-bit Fractional Divide          | 1             | 18                            | N,Z,C,OV                 |

| 31                                                | DO   | DO                     | #lit15,Expr <sup>(1)</sup>                       | Do code to PC + Expr, lit15 + 1 times       | 2             | 2                             | None                     |

|                                                   |      | DO                     | Wn, Expr(1)                                      | Do code to PC + Expr, (Wn) + 1 times        | 2             | 2                             | None                     |

| 32                                                | ED   | ED                     | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance (no accumulate)          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 33                                                | EDAC | EDAC                   | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance                          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 34                                                | EXCH | EXCH                   | Wns,Wnd                                          | Swap Wns with Wnd                           | 1             | 1                             | None                     |

| 35                                                | FBCL | FBCL                   | Ws,Wnd                                           | Find Bit Change from Left (MSb) Side        | 1             | 1                             | С                        |

| 36                                                | FF1L | FF1L                   | Ws,Wnd                                           | Find First One from Left (MSb) Side         | 1             | 1                             | С                        |

| 37                                                | FF1R | FF1R                   | Ws,Wnd                                           | Find First One from Right (LSb) Side        | 1             | 1                             | С                        |

| 38                                                | GOTO | GOTO                   | Expr                                             | Go to address                               | 2             | 4                             | None                     |

|                                                   |      | GOTO                   | Wn                                               | Go to indirect                              | 1             | 4                             | None                     |

|                                                   |      | GOTO.L                 | Wn                                               | Go to indirect (long address)               | 1             | 4                             | None                     |

| 39                                                | INC  | INC                    | f                                                | f = f + 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                                                   |      | INC                    | f,WREG                                           | WREG = f + 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                                                   |      | INC                    | Ws,Wd                                            | Wd = Ws + 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 40                                                | INC2 | INC2                   | f                                                | f = f + 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                                                   |      | INC2                   | f,WREG                                           | WREG = f + 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                                                   |      | INC2                   | Ws,Wd                                            | Wd = Ws + 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 41                                                | IOR  | IOR                    | f                                                | f = f .IOR. WREG                            | 1             | 1                             | N,Z                      |

|                                                   |      | IOR                    | f,WREG                                           | WREG = f .IOR. WREG                         | 1             | 1                             | N,Z                      |

|                                                   |      | IOR                    | #litl0,Wn                                        | Wd = lit10 .IOR. Wd                         | 1             | 1                             | N,Z                      |

|                                                   |      | IOR                    | Wb,Ws,Wd                                         | Wd = Wb .IOR. Ws                            | 1             | 1                             | N,Z                      |

|                                                   |      | IOR                    | Wb,#lit5,Wd                                      | Wd = Wb .IOR. lit5                          | 1             | 1                             | N,Z                      |

| 42                                                | LAC  | LAC                    | Wso,#Slit4,Acc                                   | Load Accumulator                            | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 43                                                | LNK  | LNK                    | #lit14                                           | Link Frame Pointer                          | 1             | 1                             | SFA                      |

| 44                                                | LSR  | LSR                    | f                                                | f = Logical Right Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                                                   |      | LSR                    | f,WREG                                           | WREG = Logical Right Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                                                   |      | LSR                    | Ws,Wd                                            | Wd = Logical Right Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                                                   |      | LSR                    | Wb,Wns,Wnd                                       | Wnd = Logical Right Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                                                   |      | LSR                    | Wb,#lit5,Wnd                                     | Wnd = Logical Right Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 45                                                | MAC  | MAC                    | Wm*Wn, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Accumulate                     | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                                                   |      | MAC                    | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd <sup>(1)</sup>      | Square and Accumulate                       | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

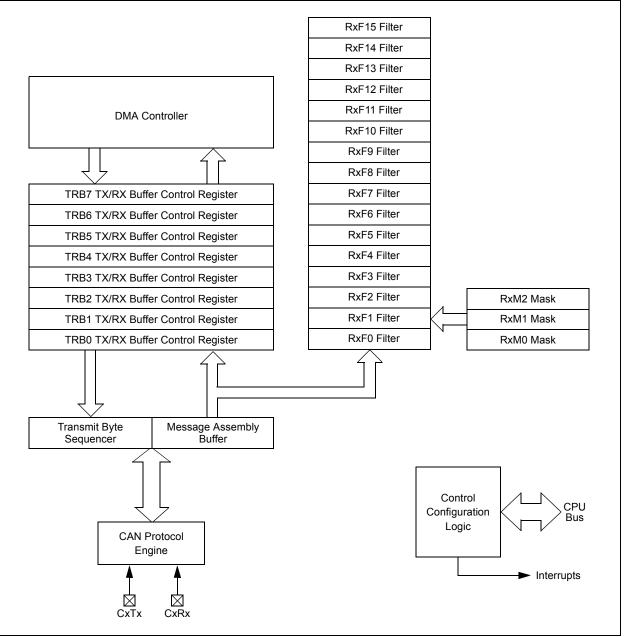

### FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS                                  |      |                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                  |                                  |  |

|-----------------------------------------------------|------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|----------------------------------|--|

| Param.<br>No. Symbol Characteristics <sup>(1)</sup> |      |                     | Min.                                                                                                                                                                                                                                                                                    | Max. | Units | Conditions                       |                                  |  |

| IC10                                                | TccL | ICx Input Low Time  | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                          |      | ns    | Must also meet<br>Parameter IC15 |                                  |  |

| IC11                                                | ТссН | ICx Input High Time | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                          | —    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |  |

| IC15                                                | TccP | ICx Input Period    | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50                                                                                                                                                                                                                                           | _    | ns    |                                  |                                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

Temperature (Celsius)

70 80 90 100 110 120

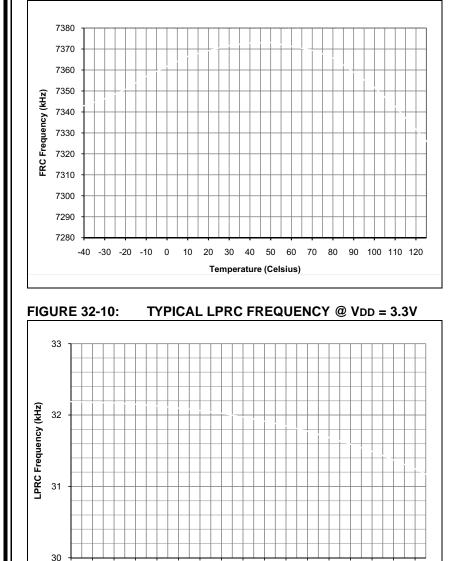

TYPICAL FRC FREQUENCY @ VDD = 3.3V

-40 -30 -20 -10

0 10 20 30 40 50 60

**FIGURE 32-9:**

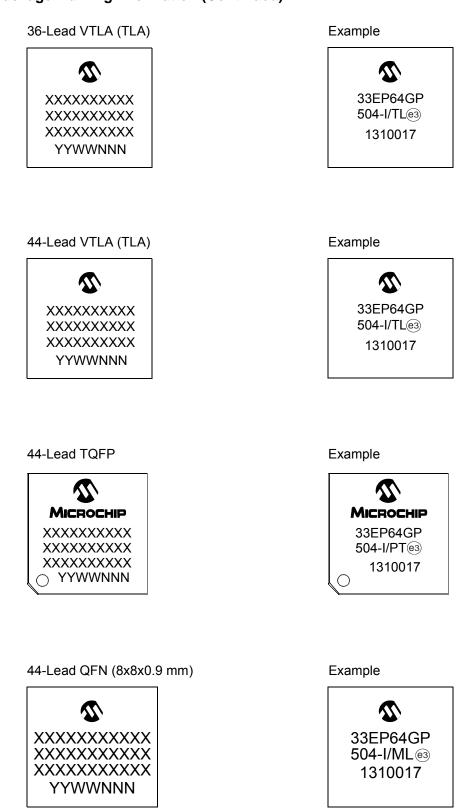

#### 33.1 Package Marking Information (Continued)