Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

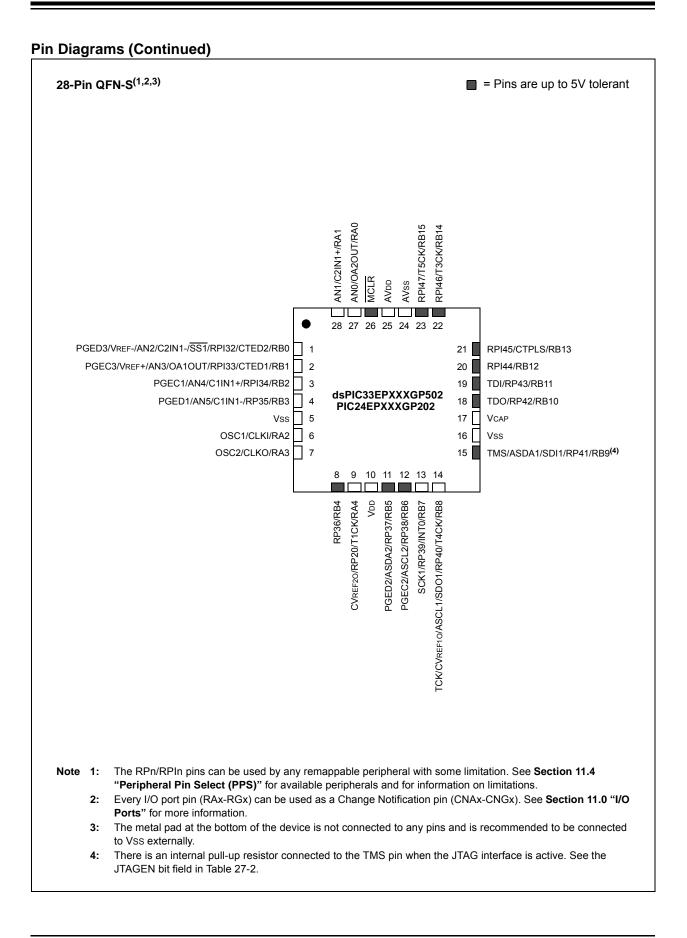

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc202-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

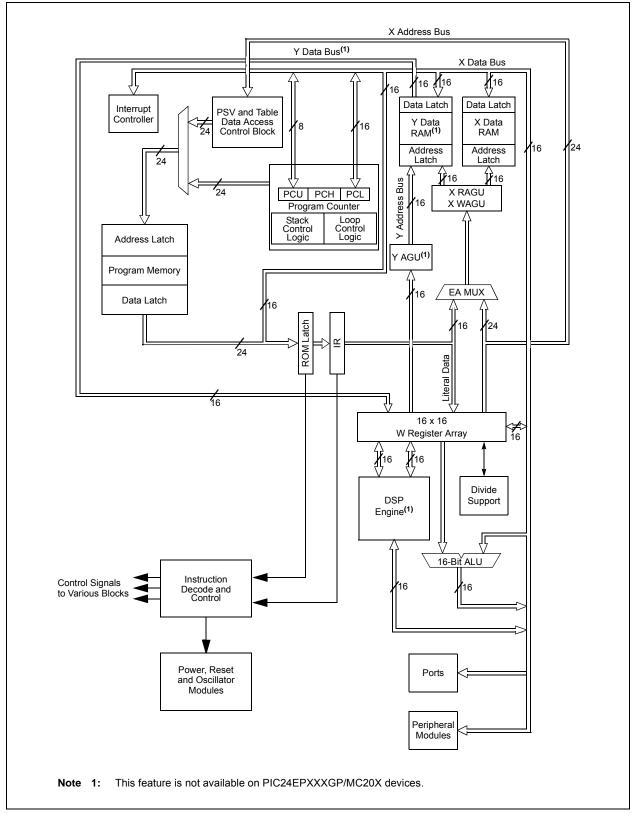

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

## TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | _      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | _      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | —      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>        | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |

|------------------------------|--------------------------------------------|-----------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| WR                           | WREN                                       | WRERR                       | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |

| bit 15                       | I                                          | 1                           | 1                             |                         |                         |                         | bit 8                  |

|                              |                                            |                             |                               |                         |                         |                         |                        |

| U-0                          | U-0                                        | U-0                         | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |

| _                            | —                                          | —                           | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |

| bit 7                        |                                            |                             |                               |                         |                         |                         | bit (                  |

| lagandi                      |                                            | SO - Sottab                 | la Only hit                   |                         |                         |                         |                        |

| L <b>egend:</b><br>R = Reada | ble hit                                    | SO = Settab<br>W = Writable | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |

| -n = Value                   |                                            | '1' = Bit is se             |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |

|                              |                                            | 1 - Dit 13 30               |                               |                         |                         |                         | lowin                  |

| bit 15                       | WR: Write Co                               | ontrol bit(1)               |                               |                         |                         |                         |                        |

|                              |                                            |                             | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |

|                              | cleared b                                  | y hardware o                | nce the operati               | on is complete          |                         |                         |                        |

|                              | -                                          |                             | ration is comple              | ete and inactive        | 9                       |                         |                        |

| bit 14                       | WREN: Write                                |                             | n/erase operati               | 000                     |                         |                         |                        |

|                              |                                            |                             | /erase operatio               |                         |                         |                         |                        |

| oit 13                       |                                            |                             | Error Flag bit <sup>(1)</sup> |                         |                         |                         |                        |

|                              | 1 = An impro                               | per program o               | r erase sequend               |                         | rmination has oc        | curred (bit is se       | t automatically        |

|                              |                                            | et attempt of th            | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |

| bit 12                       |                                            |                             | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |

|                              |                                            |                             | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |

|                              |                                            |                             | r is active durin             |                         |                         |                         |                        |

| bit 11-4                     | Unimplemen                                 | ted: Read as                | '0'                           |                         |                         |                         |                        |

| bit 3-0                      | NVMOP<3:0>                                 | NVM Operation               | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |

|                              | 1111 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1110 = Rese<br>1101 = Rese                 |                             |                               |                         |                         |                         |                        |

|                              | 1100 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1011 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1010 = Rese<br>0011 = Memo                 |                             | e operation                   |                         |                         |                         |                        |

|                              | 0010 = Rese                                | rved                        | -                             |                         |                         |                         |                        |

|                              |                                            |                             | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |

|                              | 0000 <b>= Rese</b>                         | rvea                        |                               |                         |                         |                         |                        |

|                              | These bits can onl                         | -                           |                               |                         |                         |                         |                        |

|                              | If this bit is set, the (TVREG) before Fla |                             |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |

|                              | All other combinati                        |                             | •                             |                         |                         |                         |                        |

| <b>.</b> .                   |                                            |                             |                               | in ploinenteu.          |                         |                         |                        |

| 4:                           | Execution of the P                         | wrsav instruc               | tion is ianored               | while any of th         | e NVM operatio          | ns are in progr         | ess.                   |

## REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

| R/W-0         | R/W-0                                     | U-0                                    | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |

|---------------|-------------------------------------------|----------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|

| TRAPF         | R IOPUWR                                  | —                                      | _             | VREGSF                | —                 | CM               | VREGS         |

| bit 15        |                                           |                                        |               |                       |                   |                  | bit 8         |

|               |                                           | DANIO                                  | DAA/ O        | DAMA                  | DAMO              |                  |               |

| R/W-0         |                                           | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR<br>bit 7 | SWR                                       | SWDTEN <sup>(2)</sup>                  | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |

|               |                                           |                                        |               |                       |                   |                  | bit (         |

| Legend:       |                                           |                                        |               |                       |                   |                  |               |

| R = Reada     | able bit                                  | W = Writable I                         | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |

| -n = Value    | at POR                                    | '1' = Bit is set                       |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |

|               |                                           |                                        |               |                       |                   |                  |               |

| bit 15        | •                                         | Reset Flag bit                         |               |                       |                   |                  |               |

|               |                                           | onflict Reset ha<br>onflict Reset ha   |               | d                     |                   |                  |               |

| bit 14        | •                                         | gal Opcode or                          |               |                       | et Flag bit       |                  |               |

|               |                                           | I opcode detec                         |               |                       | •                 | lized W registe  | er used as ar |

|               |                                           | Pointer caused                         |               |                       |                   |                  |               |

|               | -                                         | l opcode or Uni                        |               | egister Reset h       | as not occurred   | d                |               |

| bit 13-12     | -                                         | ted: Read as '                         |               |                       | . 1.9             |                  |               |

| bit 11        |                                           | ash Voltage Reg<br>Itage regulator i   |               |                       | p bit             |                  |               |

|               |                                           | ltage regulator (                      |               | •                     | ing Sleep         |                  |               |

| bit 10        |                                           | ted: Read as '                         | -             | ,,                    | 5                 |                  |               |

| bit 9         | CM: Configur                              | ation Mismatch                         | Flag bit      |                       |                   |                  |               |

|               | 1 = A Configu                             | uration Mismatc<br>uration Mismatc     | h Reset has   |                       |                   |                  |               |

| bit 8         | VREGS: Volta                              | age Regulator S                        | Standby Durir | ng Sleep bit          |                   |                  |               |

|               | •                                         | egulator is active<br>egulator goes in | •             | •                     | еер               |                  |               |

| bit 7         | EXTR: Extern                              | nal Reset (MCL                         | R) Pin bit    |                       |                   |                  |               |

|               |                                           | Clear (pin) Res<br>Clear (pin) Res     |               |                       |                   |                  |               |

| bit 6         | SWR: Softwa                               | re RESET (Instr                        | uction) Flag  | bit                   |                   |                  |               |

|               |                                           | instruction has instruction has        |               |                       |                   |                  |               |

| bit 5         | SWDTEN: So                                | oftware Enable/                        | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |

|               | 1 = WDT is e<br>0 = WDT is di             |                                        |               |                       |                   |                  |               |

| bit 4         | WDTO: Watc                                | hdog Timer Tim                         | e-out Flag bi | it                    |                   |                  |               |

|               |                                           | e-out has occur<br>e-out has not oc    |               |                       |                   |                  |               |

| Note 1:       | All of the Reset sta<br>cause a device Re |                                        | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir     | onfiguration bit i                     | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

## REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0       | >               |                 |        |

| bit 15       |              |                                                        |               |                  |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0           | 5444.0          | -               | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>      | >               |                 |        |

| bit 7        |              |                                                        |               |                  |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                  |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                  |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                  |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                  |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                  |                 |                 |        |

NOTES:

### REGISTER 17-17: INT1TMRH: INTERVAL 1 TIMER HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | R<31:24>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTTM | R<23:16>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

### REGISTER 17-18: INT1TMRL: INTERVAL 1 TIMER LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | IR<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTT  | /IR<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

# 21.4 ECAN Control Registers

| U-0             | U-0                                                                                                              | R/W-0                                                     | R/W-0                         | R/W-0                          | R/W-1            | R/W-0           | R/W-0  |

|-----------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------|--------------------------------|------------------|-----------------|--------|

| —               | —                                                                                                                | CSIDL                                                     | ABAT                          | CANCKS                         | REQOP2           | REQOP1          | REQOP0 |

| bit 15          |                                                                                                                  |                                                           |                               |                                |                  |                 | bit 8  |

| R-1             | R-0                                                                                                              | R-0                                                       | U-0                           | R/W-0                          | U-0              | U-0             | R/W-0  |

| OPMODE2         | OPMODE1                                                                                                          | OPMODE0                                                   | _                             | CANCAP                         |                  |                 | WIN    |

| bit 7           |                                                                                                                  |                                                           |                               |                                |                  |                 | bit (  |

| Legend:         |                                                                                                                  |                                                           |                               |                                |                  |                 |        |

| R = Readable    | bit                                                                                                              | W = Writable I                                            | oit                           | U = Unimpler                   | mented bit, read | d as '0'        |        |

| -n = Value at F | OR                                                                                                               | '1' = Bit is set                                          |                               | '0' = Bit is cle               |                  | x = Bit is unkr | nown   |

|                 |                                                                                                                  |                                                           |                               |                                |                  |                 |        |

| bit 15-14       | Unimplemen                                                                                                       | ted: Read as 'o                                           | )'                            |                                |                  |                 |        |

| bit 13          | CSIDL: ECAN                                                                                                      | Nx Stop in Idle I                                         | Node bit                      |                                |                  |                 |        |

|                 |                                                                                                                  | ues module opera module opera                             |                               | device enters I<br>ode         | dle mode         |                 |        |

| bit 12          | ABAT: Abort                                                                                                      | All Pending Tra                                           | nsmissions b                  | bit                            |                  |                 |        |

|                 |                                                                                                                  | I transmit buffe<br>ill clear this bit                    |                               | ansmission<br>smissions are a  | aborted          |                 |        |

| bit 11          | CANCKS: EC                                                                                                       | ANx Module C                                              | lock (FCAN)                   | Source Select b                | bit              |                 |        |

|                 | 1 = FCAN is e<br>0 = FCAN is e                                                                                   | ·                                                         |                               |                                |                  |                 |        |

| bit 10-8        | 111 = Set Lis<br>110 = Reserv<br>101 = Reserv<br>100 = Set Co<br>011 = Set Lis<br>010 = Set Loc<br>001 = Set Dis | ed<br>nfiguration moo<br>ten Only mode<br>opback mode     | es mode<br>le                 | bits                           |                  |                 |        |

| bit 7-5         | 111 = Module<br>110 = Reserv<br>101 = Reserv<br>100 = Module                                                     |                                                           | Messages n<br>ation mode      | node                           |                  |                 |        |

|                 | 010 = Module<br>001 = Module<br>000 = Module                                                                     | e is in Loopback<br>e is in Disable n<br>e is in Normal C | mode<br>node<br>operation mod | de                             |                  |                 |        |

| bit 4           | -                                                                                                                | ted: Read as '                                            |                               |                                |                  |                 |        |

| bit 3           |                                                                                                                  | nput capture ba                                           |                               | Capture Event<br>message recei |                  |                 |        |

| bit 2-1         |                                                                                                                  | ted: Read as '(                                           | ı'                            |                                |                  |                 |        |

| bit 0           | -                                                                                                                | ap Window Sele                                            |                               |                                |                  |                 |        |

| UIL U           | 1 = Uses filter                                                                                                  | -                                                         | יטו טונ                       |                                |                  |                 |        |

| R/W-0       R/W-0       U-0       U-0       U-0       U-0         DMABS2       DMABS1       DMABS0                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| bit 15<br>U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0<br>FSA4 FSA3 FSA2 FSA1<br>bit 7<br>Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknov<br>bit 15-13 DMABS<2:0>: DMA Buffer Size bits<br>111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                               | U-0   |

| U-0       U-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0         —       —       —       FSA4       FSA3       FSA2       FSA1         bit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-13       DMABS<2:0>: DMA Buffer Size bits       111 = Reserved       110 = 32 buffers in RAM       101 = 24 buffers in RAM | —     |

| FSA4     FSA3     FSA2     FSA1       bit 7       Legend:       R = Readable bit     W = Writable bit     U = Unimplemented bit, read as '0'       -n = Value at POR     '1' = Bit is set     '0' = Bit is cleared     x = Bit is unknown       bit 15-13     DMABS<2:0>: DMA Buffer Size bits       111 = Reserved       110 = 32 buffers in RAM       101 = 24 buffers in RAM                                                                                                                                   | bit 8 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| bit 7  Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow bit 15-13 DMABS<2:0>: DMA Buffer Size bits 111 = Reserved 110 = 32 buffers in RAM 101 = 24 buffers in RAM                                                                                                                                                                                                                                           | R/W-0 |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-13       DMABS<2:0>: DMA Buffer Size bits         111 = Reserved       110 = 32 buffers in RAM         101 = 24 buffers in RAM                                                                                                                                                               | FSA0  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 15-13       DMABS<2:0>: DMA Buffer Size bits       111 = Reserved         110 = 32 buffers in RAM       101 = 24 buffers in RAM                                                                                                                                                                                  | bit C |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 15-13       DMABS<2:0>: DMA Buffer Size bits       111 = Reserved         110 = 32 buffers in RAM       101 = 24 buffers in RAM                                                                                                                                                                                  |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow<br>bit 15-13 DMABS<2:0>: DMA Buffer Size bits<br>111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                   |       |

| bit 15-13 DMABS<2:0>: DMA Buffer Size bits<br>111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                              | wn    |

| 111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| 100 - 16 huffers in DAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| 100 = 16 builds in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| 011 = 12 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| 010 = 8 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| 001 = 6 buffers in RAM<br>000 = 4 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| bit 12-5 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| bit 4-0 <b>FSA&lt;4:0&gt;:</b> FIFO Area Starts with Buffer bits                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| 11111 = Read Buffer RB31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| 11110 = Read Buffer RB30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| 00001 = TX/RX Buffer TRB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| 00000 = TX/RX Buffer TRB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

## REGISTER 21-4: CxFCTRL: ECANx FIFO CONTROL REGISTER

# REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | PTGT0 | _IM<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PTGT0 | LIM<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------|----------|-------|-------|-------|

|        |       |       | PTGT1LI | IM<15:8> |       |       |       |

| bit 15 |       |       |         |          |       |       | bit 8 |

|        |       |       |         |          |       |       |       |

| R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|----------|-------|-------|-------|

|       |       |       | PTGT1L | -IM<7:0> |       |       |       |

| bit 7 |       |       |        |          |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

| REGISTER 24-6: | PTGSDLIM: PTG STEP DELAY LIMIT REGISTER <sup>(1,2)</sup> |

|----------------|----------------------------------------------------------|

|                |                                                          |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PTGSD | LIM<15:8>         |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PTGSE | )LIM<7:0>         |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

**Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | PTGC0 | LIM<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PTGC  | )LIM<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable bi  | it    | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unki | nown  |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

bit 3 ABEN: AND Gate B Input Enable bit 1 = MBI is connected to AND gate 0 = MBI is not connected to AND gate bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate 0 = Inverted MBI is not connected to AND gate bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to AND gate 0 = MAI is not connected to AND gate bit 0 AANEN: AND Gate A Input Inverted Enable bit 1 = Inverted MAI is connected to AND gate 0 = Inverted MAI is not connected to AND gate

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHA       | RACTERI | STICS                                                            | (unless | d Operati<br>otherwis | <b>e stated)</b><br>ature -4 | 0°C ≤ T⁄ | <b>.0V to 3.6V</b><br>A $\leq$ +85°C for Industrial<br>A $\leq$ +125°C for Extended |

|--------------|---------|------------------------------------------------------------------|---------|-----------------------|------------------------------|----------|-------------------------------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic                                                   | Min.    | Typ. <sup>(1)</sup>   | Max.                         | Units    | Conditions                                                                          |

| OS50         | Fplli   | PLL Voltage Controlled Oscillator<br>(VCO) Input Frequency Range | 0.8     | _                     | 8.0                          | MHz      | ECPLL, XTPLL modes                                                                  |

| OS51         | Fvco    | On-Chip VCO System Frequency                                     | 120     | —                     | 340                          | MHz      |                                                                                     |

| OS52         | TLOCK   | PLL Start-up Time (Lock Time)                                    | 0.9     | 1.5                   | 3.1                          | ms       |                                                                                     |

| OS53         | DCLK    | CLKO Stability (Jitter) <sup>(2)</sup>                           | -3      | 0.5                   | 3                            | %        |                                                                                     |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases, or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if Fosc = 120 MHz and the SPIx bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

#### TABLE 30-19: INTERNAL FRC ACCURACY

| AC CHA       | RACTERISTICS           |           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |             |   |                                         |                |  |

|--------------|------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---|-----------------------------------------|----------------|--|

| Param<br>No. | Characteristic         | Min.      | Min. Typ. Max. Units Conditions                                                                                                                                                                       |             |   |                                         |                |  |

| Internal     | FRC Accuracy @ FRC Fre | equency = | : 7.37 MHz                                                                                                                                                                                            | <u>,(1)</u> |   |                                         |                |  |

| F20a         | FRC                    | -1.5      | 0.5                                                                                                                                                                                                   | +1.5        | % | $-40^{\circ}C \le TA \le -10^{\circ}C$  | VDD = 3.0-3.6V |  |

|              |                        | -1        | 0.5                                                                                                                                                                                                   | +1          | % | $-10^{\circ}C \le TA \le +85^{\circ}C$  | VDD = 3.0-3.6V |  |

| F20b         | FRC                    | -2        | 1                                                                                                                                                                                                     | +2          | % | $+85^{\circ}C \le TA \le +125^{\circ}C$ | VDD = 3.0-3.6V |  |

Note 1: Frequency is calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

#### TABLE 30-20: INTERNAL LPRC ACCURACY

| AC CH        | ARACTERISTICS               |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |   |                                           |                |  |

|--------------|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|-------------------------------------------|----------------|--|

| Param<br>No. | Characteristic              | Min. | Min. Typ. Max. Units Conditions                                                                                                                                                                       |     |   |                                           |                |  |

| LPRC (       | @ 32.768 kHz <sup>(1)</sup> |      |                                                                                                                                                                                                       |     |   |                                           |                |  |

| F21a         | LPRC                        | -30  | —                                                                                                                                                                                                     | +30 | % | $-40^{\circ}C \le TA \le -10^{\circ}C$    | VDD = 3.0-3.6V |  |

|              |                             | -20  | _                                                                                                                                                                                                     | +20 | % | $-10^{\circ}C \leq TA \leq +85^{\circ}C$  | VDD = 3.0-3.6V |  |

| F21b         | LPRC                        | -30  | _                                                                                                                                                                                                     | +30 | % | $+85^{\circ}C \leq TA \leq +125^{\circ}C$ | VDD = 3.0-3.6V |  |

**Note 1:** The change of LPRC frequency as VDD changes.

# FIGURE 30-11: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

## TABLE 30-30: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| АС СНА       | ARACTERIST | rics                                      |                             | Standard Operating<br>(unless otherwise s<br>Operating temperatu | <b>tated)</b><br>re -40 | °C ≤ Ta ≤ | ≤ +85°C | ₩<br>for Industrial<br>C for Extended |

|--------------|------------|-------------------------------------------|-----------------------------|------------------------------------------------------------------|-------------------------|-----------|---------|---------------------------------------|

| Param<br>No. | Symbol     | Charao                                    | cteristic <sup>(1)</sup>    | Min.                                                             | Тур.                    | Max.      | Units   | Conditions                            |

| TQ10         | TtQH       | TQCK High<br>Time                         | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25                   |                         |           | ns      | Must also meet<br>Parameter TQ15      |

| TQ11         | TtQL       | TQCK Low<br>Time                          | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25                   | —                       | _         | ns      | Must also meet<br>Parameter TQ15      |

| TQ15         | TtQP       | TQCP Input<br>Period                      | Synchronous, with prescaler | Greater of 25 + 50<br>or<br>(1 Tcy/N) + 50                       | —                       | _         | ns      |                                       |

| TQ20         | TCKEXTMRL  | Delay from E<br>Clock Edge t<br>Increment | xternal TQCK<br>o Timer     | _                                                                | 1                       | Тсү       | —       |                                       |

Note 1: These parameters are characterized but not tested in manufacturing.

48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | N         | <b>ILLIMETER</b> | S    |

|------------------------|--------|-----------|------------------|------|

| Dimension              | Limits | MIN       | NOM              | MAX  |

| Number of Pins         | N      |           | 48               |      |

| Pitch                  | е      |           | 0.40 BSC         |      |

| Overall Height         | Α      | 0.45      | 0.50             | 0.55 |

| Standoff               | A1     | 0.00      | 0.02             | 0.05 |

| Contact Thickness      | A3     | 0.127 REF |                  |      |

| Overall Width          | E      |           | 6.00 BSC         |      |

| Exposed Pad Width      | E2     | 4.45      | 4.60             | 4.75 |

| Overall Length         | D      |           | 6.00 BSC         |      |

| Exposed Pad Length     | D2     | 4.45      | 4.60             | 4.75 |

| Contact Width          | b      | 0.15      | 0.20             | 0.25 |

| Contact Length         | L      | 0.30      | 0.40             | 0.50 |

| Contact-to-Exposed Pad | K      | 0.20      | -                | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2

# INDEX

## Α

| Absolute Maximum Ratings4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 01                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|