Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\times$  FI

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc202t-e-mm |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

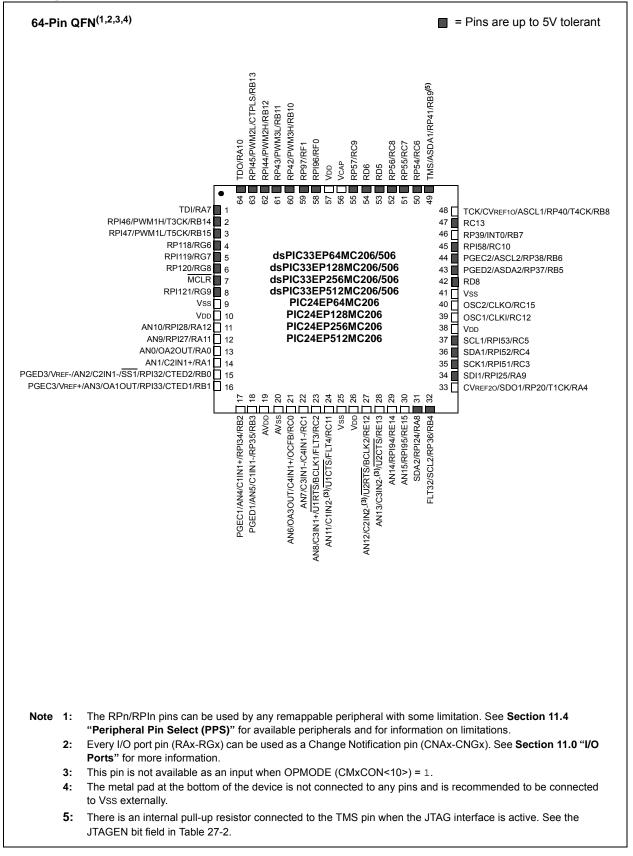

## Pin Diagrams (Continued)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10     | Bit 9      | Bit 8  | Bit 7 | Bit 6      | Bit 5         | Bit 4  | Bit 3         | Bit 2    | Bit 1        | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|------------|------------|--------|-------|------------|---------------|--------|---------------|----------|--------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF     | SPI1EIF    | T3IF   | T2IF  | OC2IF      | IC2IF         | DMA0IF | T1IF          | OC1IF    | IC1IF        | <b>INT0IF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF      | OC3IF      | DMA2IF | _     | _          | _             | INT1IF | CNIF          | CMIF     | MI2C1IF      | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      |        | _          | _      | _      |            | _          | _      |       | IC4IF      | IC3IF         | DMA3IF | _             | —        | SPI2IF       | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | QEI1IF     | PSEMIF     | _      | _     | _          | _             | _      | _             | MI2C2IF  | SI2C2IF      | —             | 0000          |

| IFS4         | 0808  | -      | _      | CTMUIF     | _      | _      |            | —          | _      | _     |            | _             | _      | CRCIF         | U2EIF    | U1EIF        |               | 0000          |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          | _      | _      |            | —          | _      | _     |            | _             | _      | _             | _        | _            |               | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | _      |            | —          | _      | _     |            | _             | _      | _             | _        | _            | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          | _      | _      |            | —          | _      | _     |            | _             | _      | _             | _        | _            | _             | 0000          |

| IFS9         | 0812  | _      | _      | _          | -      | _      | _          | _          | —      | _     | PTG3IF     | PTG2IF        | PTG1IF | PTG0IF        | PTGWDTIF | PTGSTEPIF    |               | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE     | SPI1EIE    | T3IE   | T2IE  | OC2IE      | IC2IE         | DMA0IE | T1IE          | OC1IE    | IC1IE        | INTOIE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE      | OC3IE      | DMA2IE | —     | _          | —             | INT1IE | CNIE          | CMIE     | MI2C1IE      | SI2C1IE       | 0000          |

| IEC2         | 0824  | _      | _      | —          | -      | _      |            | —          | —      | _     | IC4IE      | IC3IE         | DMA3IE |               | _        | SPI2IE       | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | _          | -      | _      | QEI1IE     | PSEMIE     | —      | _     | _          | —             | —      | -             | MI2C2IE  | SI2C2IE      | —             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | -      | _      |            | —          | —      | _     | _          | —             | _      | CRCIE         | U2EIE    | U1EIE        |               | 0000          |

| IEC5         | 082A  | PWM2IE | PWM1IE | —          | -      | _      | _          | _          | _      | _     | _          | —             | _      |               | _        | —            |               | 0000          |

| IEC6         | 082C  | _      | _      | _          | -      | _      | _          | _          | _      | _     | _          | —             | _      | -             | _        | —            | PWM3IE        | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | -      | _      | _          | _          | _      | _     | _          | —             | _      | -             | _        | —            | —             | 0000          |

| IEC9         | 0832  | _      | _      | _          | -      | _      | _          | _          | _      | _     | PTG3IE     | PTG2IE        | PTG1IE | PTG0IE        | PTGWDTIE | PTGSTEPIE    |               | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |            | OC1IP<2:0  | )>     | _     |            | IC1IP<2:0>    |        |               |          | INT0IP<2:0>  |               | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      | OC2IP<2:0> |            |        | _     | IC2IP<2:0> |               | -      | - DMA0IP<2:0> |          |              | 4444          |               |

| IPC2         | 0844  | _      | -      | U1RXIP<2:0 | >      | _      | :          | SPI1IP<2:0 | )>     | _     |            | SPI1EIP<2:0   | >      | -             |          | T3IP<2:0>    |               | 4444          |

| IPC3         | 0846  | _      | _      | —          | —      | _      | C          | MA1IP<2:   | 0>     | _     |            | AD1IP<2:0>    |        | -             |          | U1TXIP<2:0>  |               | 0444          |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |            | CMIP<2:0   | >      | _     |            | MI2C1IP<2:0   | >      | -             | 5        | SI2C1IP<2:0> |               | 4444          |

| IPC5         | 084A  | _      | _      | —          | —      | _      |            | —          | —      | _     | _          | —             | —      | -             |          | INT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |            | OC4IP<2:0  | )>     |       |            | OC3IP<2:0>    |        |               | [        | DMA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  | _      |        | U2TXIP<2:0 | >      | _      | ι          | J2RXIP<2:  | 0>     |       |            | INT2IP<2:0>   | •      |               |          | T5IP<2:0>    |               | 4444          |

| IPC8         | 0850  | _      | _      | —          | —      | _      |            | —          | —      | _     |            | SPI2IP<2:0>   | •      | -             | 5        | SPI2EIP<2:0> |               | 0044          |

| IPC9         | 0852  | _      | _      | _          | -      | _      |            | IC4IP<2:0  | >      | _     |            | IC3IP<2:0>    |        | -             | [        | DMA3IP<2:0>  |               | 0444          |

| IPC12        | 0858  | _      | _      | _          |        | _      | N          | 112C2IP<2: | 0>     | _     |            | SI2C2IP<2:0>  |        | -             | _        | —            |               | 0440          |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (          | QEI1IP<2:0 | )>     | _     |            | PSEMIP<2:0> — |        | _             | _        | _            | 0440          |               |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |            | U2EIP<2:0  | >      | _     |            | U1EIP<2:0>    |        | _             | _        | _            | _             | 4440          |

| IPC19        | 0866  | _      | _      | —          | —      | _      | —          | —          | _      | _     |            | CTMUIP<2:0    | >      | _             | _        | _            | _             | 0040          |

| IPC23        | 086E  | _      | F      | PWM2IP<2:0 | )>     | _      | P          | WM1IP<2:   | 0>     | _     | _          | _             | —      | _             | _        | _            | _             | 4400          |

| IPC24        | 0870  | _      | _      |            |        | _      |            | _          |        |       | _          | _             | _      | _             | F        | PWM3IP<2:0>  |               | 4004          |

## TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4         | -16:  | QEI1   | REGR               |          | P FOR d    | SPIC33E    | PXXXMO   | 20X/50)  | ( AND PI    | C24EP) |        | 20X DE     | VICES O  | NLY                   | 1      |        |        | r             |

|-----------------|-------|--------|--------------------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|-----------------------|--------|--------|--------|---------------|

| File Name       | Addr. | Bit 15 | Bit 14             | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3                 | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON         | 01C0  | QEIEN  | —                  | QEISIDL  |            | PIMOD<2:0> |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL GATEN CCM<1:0> |        |        |        | 0000          |

| QEI1IOC         | 01C2  | QCAPEN | FLTREN             |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME                  | INDEX  | QEB    | QEA    | 000x          |

| <b>QEI1STAT</b> | 01C4  | _      | _                  | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ                | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL        | 01C6  |        |                    |          |            |            |          |          | POSCNT<15   | :0>    |        |            |          |                       |        |        |        | 0000          |

| POS1CNTH        | 01C8  |        |                    |          |            |            |          | ł        | POSCNT<31:  | 16>    |        |            |          |                       |        |        |        | 0000          |

| POS1HLD         | 01CA  |        |                    |          |            |            |          |          | POSHLD<15   | 0>     |        |            |          |                       |        |        |        | 0000          |

| VEL1CNT         | 01CC  |        |                    |          |            |            |          |          | VELCNT<15   | 0>     |        |            |          |                       |        |        |        | 0000          |

| INT1TMRL        | 01CE  |        | INTTMR<15:0> 000   |          |            |            |          |          |             |        | 0000   |            |          |                       |        |        |        |               |

| INT1TMRH        | 01D0  |        | INTTMR<31:16> 0000 |          |            |            |          |          |             |        | 0000   |            |          |                       |        |        |        |               |

| INT1HLDL        | 01D2  |        |                    |          |            |            |          |          | INTHLD<15:  | )>     |        |            |          |                       |        |        |        | 0000          |

| INT1HLDH        | 01D4  |        |                    |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |                       |        |        |        | 0000          |

| INDX1CNTL       | 01D6  |        |                    |          |            |            |          |          | INDXCNT<15  | :0>    |        |            |          |                       |        |        |        | 0000          |

| INDX1CNTH       | 01D8  |        |                    |          |            |            |          |          | NDXCNT<31:  | 16>    |        |            |          |                       |        |        |        | 0000          |

| INDX1HLD        | 01DA  |        |                    |          |            |            |          |          | INDXHLD<15  | :0>    |        |            |          |                       |        |        |        | 0000          |

| QEI1GECL        | 01DC  |        |                    |          |            |            |          |          | QEIGEC<15   | 0>     |        |            |          |                       |        |        |        | 0000          |

| <b>QEI1ICL</b>  | 01DC  |        |                    |          |            |            |          |          | QEIIC<15:0  | >      |        |            |          |                       |        |        |        | 0000          |

| QEI1GECH        | 01DE  |        | QEIGEC<31:16> 000  |          |            |            |          |          |             |        | 0000   |            |          |                       |        |        |        |               |

| QEI1ICH         | 01DE  |        | QEIIC<31:16> 000   |          |            |            |          |          |             |        | 0000   |            |          |                       |        |        |        |               |

| QEI1LECL        | 01E0  |        |                    |          |            |            |          |          | QEILEC<15:  | )>     |        |            |          |                       |        |        |        | 0000          |

| <b>QEI1LECH</b> | 01E2  |        |                    |          |            |            |          |          | QEILEC<31:1 | 6>     |        |            |          |                       |        |        |        | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

| File<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7      | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------------|--------------|--------|------------|--------|-------|-------|------------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | _      |              | INT1R<6:0>   |        |            |        |       |       | _          | _            | _     | _     |            | _     | _     | 0000  |               |

| RPINR1       | 06A2  |        | —            |              |        |            |        |       | -     | INT2R<6:0> |              |       |       |            |       | 0000  |       |               |

| RPINR3       | 06A6  |        | _            | _            | _      | _          | _      | _     | _     | _          |              |       | -     | [2CKR<6:0> | >     |       |       | 0000          |

| RPINR7       | 06AE  | _      |              | IC2R<6:0>    |        |            |        |       |       | —          | IC1R<6:0>    |       |       |            |       |       | 0000  |               |

| RPINR8       | 06B0  | _      |              | IC4R<6:0>    |        |            |        |       |       | —          |              |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  | _      | _            | OCFAR<6:0>   |        |            |        |       |       |            | 0000         |       |       |            |       |       |       |               |

| RPINR12      | 06B8  | _      |              |              | l      | =LT2R<6:0> |        |       |       | —          | FLT1R<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR14      | 06BC  | _      |              |              | (      | QEB1R<6:0  | >      |       |       | —          | QEA1R<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR15      | 06BE  | _      |              |              | Н      | OME1R<6:0  | )>     |       |       | —          | INDX1R<6:0>  |       |       |            |       |       | 0000  |               |

| RPINR18      | 06C4  | _      | _            | _            | —      | _          | _      | _     | _     | —          | U1RXR<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR19      | 06C6  | _      | _            | _            | _      | _          | _      | _     | _     | —          |              |       | ι     | J2RXR<6:0> | >     |       |       | 0000          |

| RPINR22      | 06CC  | _      |              | •            | S      | CK2INR<6:0 | )>     |       |       | _          |              |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _            |              | _      | _          | _      | _     | _     | _          |              |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR37      | 06EA  | _      | SYNCI1R<6:0> |              |        |            |        | _     | _     | _          | _            | _     | _     | _          | _     | 0000  |       |               |

| RPINR38      | 06EC  | _      |              | DTCMP1R<6:0> |        |            |        |       |       | _          | _            | _     | _     |            | _     | _     | _     | 0000          |

| RPINR39      | 06EE  | _      |              |              | DT     | CMP3R<6:   | 0>     |       |       | —          | DTCMP2R<6:0> |       |       |            |       |       | 0000  |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

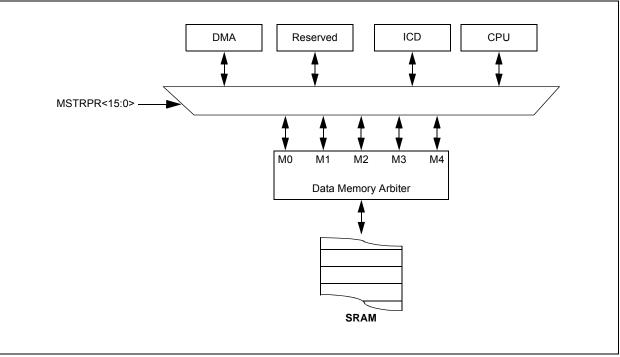

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

## FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

## 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

## 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

## 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

## 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

## 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

## 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

## 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

## 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

## 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

## 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

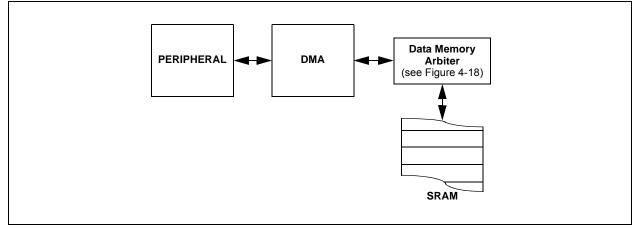

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

## FIGURE 8-1: DMA CONTROLLER MODULE

| REGISTER                          | TU-5: PIVID6                                   | . PERIPHER       |                           | DISABLE C         | UNIROL RE             | GISIER 6              |                       |  |

|-----------------------------------|------------------------------------------------|------------------|---------------------------|-------------------|-----------------------|-----------------------|-----------------------|--|

| U-0                               | U-0                                            | U-0              | U-0                       | U-0               | R/W-0                 | R/W-0                 | R/W-0                 |  |

| —                                 | —                                              | —                | —                         | _                 | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |  |

| bit 15                            |                                                |                  |                           |                   |                       |                       | bit 8                 |  |

|                                   |                                                |                  |                           |                   |                       |                       |                       |  |

| U-0                               | U-0                                            | U-0              | U-0                       | U-0               | U-0                   | U-0                   | U-0                   |  |

|                                   |                                                |                  |                           |                   |                       |                       |                       |  |

| bit 7                             |                                                |                  |                           |                   |                       |                       | bit 0                 |  |

|                                   |                                                |                  |                           |                   |                       |                       |                       |  |

| Legend:                           |                                                |                  |                           |                   |                       |                       |                       |  |

| R = Readable bit W = Writable bit |                                                |                  | bit                       | U = Unimplen      | nented bit, read      | l as '0'              |                       |  |

| -n = Value a                      | t POR                                          | '1' = Bit is set |                           | '0' = Bit is clea | ared                  | x = Bit is unknown    |                       |  |

|                                   |                                                |                  |                           |                   |                       |                       |                       |  |

| bit 15-11                         | Unimplement                                    | ted: Read as '   | כ'                        |                   |                       |                       |                       |  |

| bit 10                            | PWM3MD: P\                                     | NM3 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |  |

|                                   | 1 = PWM3 mo                                    | odule is disable | ed                        |                   |                       |                       |                       |  |

|                                   | 0 = PWM3 mo                                    | odule is enable  | d                         |                   |                       |                       |                       |  |

| bit 9                             | PWM2MD: P\                                     | NM2 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |  |

| 1 = PWM2 module is disabled       |                                                |                  | ed                        |                   |                       |                       |                       |  |

|                                   | 0 = PWM2 module is enabled                     |                  |                           |                   |                       |                       |                       |  |

| bit 8                             | PWM1MD: PWM1 Module Disable bit <sup>(1)</sup> |                  |                           |                   |                       |                       |                       |  |

| 1 = PWM1 module is disabled       |                                                |                  |                           |                   |                       |                       |                       |  |

|                                   | 0 = PWM1 mo                                    | odule is enable  | d                         |                   |                       |                       |                       |  |

| bit 7-0                           | Unimplement                                    | ted: Read as '   | כ'                        |                   |                       |                       |                       |  |

## REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

## 15.2 Output Compare Control Registers

## REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0        | U-0                                                   | R/W-0                                       | R/W-0           | R/W-0             | R/W-0                  | U-0             | R/W-0         |  |  |

|------------|-------------------------------------------------------|---------------------------------------------|-----------------|-------------------|------------------------|-----------------|---------------|--|--|

| 0-0        | 0-0                                                   | OCSIDL                                      | OCTSEL2         | OCTSEL1           | OCTSEL0                | 0-0             | ENFLTB        |  |  |

| <br>bit 15 |                                                       | OCSIDE                                      | OCTSEL2         | OCISELI           | OCTSELU                | —               | bit 8         |  |  |

| DIL 15     |                                                       |                                             |                 |                   |                        |                 | DIL O         |  |  |

| R/W-0      | U-0                                                   | R/W-0, HSC                                  | R/W-0, HSC      | R/W-0             | R/W-0                  | R/W-0           | R/W-0         |  |  |

| ENFLTA     |                                                       | OCFLTB                                      | OCFLTA          | TRIGMODE          | OCM2                   | OCM1            | OCM0          |  |  |

| bit 7      |                                                       | 001218                                      | OOFEIN          | ITTOMODE          | 001112                 | 0.0111          | bit 0         |  |  |

|            |                                                       |                                             |                 |                   |                        |                 | 2.1.0         |  |  |

| Legend:    |                                                       | HSC = Hardw                                 | are Settable/Cl | earable bit       |                        |                 |               |  |  |

| R = Read   | able bit                                              | W = Writable I                              | bit             | U = Unimplem      | nented bit, read       | as '0'          |               |  |  |

| -n = Value | e at POR                                              | '1' = Bit is set                            |                 | '0' = Bit is clea | ared                   | x = Bit is unkn | own           |  |  |

|            |                                                       |                                             |                 |                   |                        |                 |               |  |  |

| bit 15-14  | Unimplemen                                            | ted: Read as 'o                             | )'              |                   |                        |                 |               |  |  |

| bit 13     | OCSIDL: Out                                           | tput Compare x                              | Stop in Idle Mo | de Control bit    |                        |                 |               |  |  |

|            |                                                       | compare x Halts                             |                 |                   |                        |                 |               |  |  |

|            | •                                                     | compare x conti                             | •               |                   | ode                    |                 |               |  |  |

| bit 12-10  |                                                       | D>: Output Com                              | pare x Clock Se | elect bits        |                        |                 |               |  |  |

|            | 111 = Periph<br>110 = Reserv                          | eral clock (FP)                             |                 |                   |                        |                 |               |  |  |

|            | 101 = PTGO                                            |                                             |                 |                   |                        |                 |               |  |  |

|            |                                                       | is the clock so                             | urce of the OC  | k (only the sync  | hronous clock          | is supported)   |               |  |  |

|            |                                                       | is the clock so                             |                 |                   |                        |                 |               |  |  |

|            |                                                       | is the clock so                             |                 |                   |                        |                 |               |  |  |

|            |                                                       | ( is the clock so<br>( is the clock so      |                 |                   |                        |                 |               |  |  |

| bit 9      |                                                       | ted: Read as '0                             |                 | -                 |                        |                 |               |  |  |

| bit 8      | -                                                     | ult B Input Enab                            |                 |                   |                        |                 |               |  |  |

|            |                                                       | ompare Fault B                              |                 | is enabled        |                        |                 |               |  |  |

|            | -                                                     | compare Fault B                             |                 | is disabled       |                        |                 |               |  |  |

| bit 7      |                                                       | ult A Input Enab                            |                 |                   |                        |                 |               |  |  |

|            |                                                       | Compare Fault A<br>Compare Fault A          |                 |                   |                        |                 |               |  |  |

| bit 6      | •                                                     | •                                           | ,               | is disabled       |                        |                 |               |  |  |

| bit 5      | -                                                     | i <b>ted:</b> Read as '0<br>VM Fault B Cond |                 |                   |                        |                 |               |  |  |

| DIL 5      |                                                       | ult B condition of                          |                 |                   |                        |                 |               |  |  |

|            |                                                       | I Fault B condition                         |                 |                   |                        |                 |               |  |  |

| bit 4      | OCFLTA: PWM Fault A Condition Status bit              |                                             |                 |                   |                        |                 |               |  |  |

|            | 1 = PWM Fault A condition on OCFA pin has occurred    |                                             |                 |                   |                        |                 |               |  |  |

|            | 0 = No PWM Fault A condition on OCFA pin has occurred |                                             |                 |                   |                        |                 |               |  |  |

| Note 1:    | OCxR and OCxF                                         | RS are double-b                             | ouffered in PWN | /I mode only.     |                        |                 |               |  |  |

| 2:         | Each Output Cor                                       |                                             |                 | -                 | urce. See <b>Secti</b> | on 24.0 "Perip  | heral Trigger |  |  |

|            | Generator (PTG                                        |                                             |                 |                   |                        |                 |               |  |  |

|            | PTGO4 = OC1                                           |                                             |                 |                   |                        |                 |               |  |  |

|            | PTG05 = 0C2                                           |                                             |                 |                   |                        |                 |               |  |  |

|            | PTGO6 = OC3<br>PTGO7 = OC4                            |                                             |                 |                   |                        |                 |               |  |  |

|            |                                                       |                                             |                 |                   |                        |                 |               |  |  |

## 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

## 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0         | R/W-0                                                                                                    | R/W-0                                  | R/W-0           | U-0               | U-0                 | U-0              | U-0        |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------|-------------------|---------------------|------------------|------------|--|--|--|--|

|               | TRGD                                                                                                     | IV<3:0>                                |                 | —                 |                     | —                |            |  |  |  |  |

| bit 15        |                                                                                                          |                                        |                 |                   |                     |                  | bit 8      |  |  |  |  |

|               |                                                                                                          |                                        |                 |                   |                     |                  |            |  |  |  |  |

| U-0           | U-0                                                                                                      | R/W-0                                  | R/W-0           | R/W-0             | R/W-0               | R/W-0            | R/W-0      |  |  |  |  |

|               | —                                                                                                        |                                        |                 | TRGSTF            | RT<5:0> <b>(1)</b>  |                  |            |  |  |  |  |

| bit 7         |                                                                                                          |                                        |                 |                   |                     |                  | bit        |  |  |  |  |

|               |                                                                                                          |                                        |                 |                   |                     |                  |            |  |  |  |  |

| Legend:       |                                                                                                          |                                        |                 |                   |                     |                  |            |  |  |  |  |

| R = Readabl   | le bit                                                                                                   | W = Writable                           | bit             | U = Unimplem      | nented bit, read    | as '0'           |            |  |  |  |  |

| -n = Value at | t POR                                                                                                    | '1' = Bit is set                       |                 | '0' = Bit is clea | ared                | x = Bit is unkn  | own        |  |  |  |  |

|               |                                                                                                          |                                        |                 |                   |                     |                  |            |  |  |  |  |

| bit 15-12     | TRGDIV<3:                                                                                                | <b>0&gt;:</b> Trigger # Ou             | itput Divider b | pits              |                     |                  |            |  |  |  |  |

|               | 1111 = Trigger output for every 16th trigger event                                                       |                                        |                 |                   |                     |                  |            |  |  |  |  |

|               | 1110 = Trigger output for every 15th trigger event                                                       |                                        |                 |                   |                     |                  |            |  |  |  |  |

|               | 1101 = Trigger output for every 14th trigger event                                                       |                                        |                 |                   |                     |                  |            |  |  |  |  |

|               | 1100 = Trigger output for every 13th trigger event<br>1011 = Trigger output for every 12th trigger event |                                        |                 |                   |                     |                  |            |  |  |  |  |

|               |                                                                                                          |                                        |                 |                   |                     |                  |            |  |  |  |  |

|               |                                                                                                          | ger output for ev<br>ger output for ev |                 |                   |                     |                  |            |  |  |  |  |

|               |                                                                                                          | ger output for ev                      |                 |                   |                     |                  |            |  |  |  |  |

|               |                                                                                                          | ger output for ev                      |                 |                   |                     |                  |            |  |  |  |  |

|               |                                                                                                          | ger output for ev                      |                 |                   |                     |                  |            |  |  |  |  |

|               |                                                                                                          | ger output for ev                      |                 |                   |                     |                  |            |  |  |  |  |

|               |                                                                                                          | ger output for ev                      |                 |                   |                     |                  |            |  |  |  |  |

|               |                                                                                                          | ger output for ev                      |                 |                   |                     |                  |            |  |  |  |  |

|               |                                                                                                          | ger output for ev                      |                 |                   |                     |                  |            |  |  |  |  |

|               | 0001 = Trigg                                                                                             | ger output for ev                      | ery 2nd trigge  | er event          |                     |                  |            |  |  |  |  |

|               | 0000 <b>= Trig</b> g                                                                                     | ger output for ev                      | ery trigger ev  | vent              |                     |                  |            |  |  |  |  |

| bit 11-6      | Unimpleme                                                                                                | nted: Read as '                        | 0'              |                   |                     |                  |            |  |  |  |  |

| bit 5-0       | TRGSTRT<                                                                                                 | 5:0>: Trigger Po                       | stscaler Start  | t Enable Select   | bits <sup>(1)</sup> |                  |            |  |  |  |  |

|               | 111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled       |                                        |                 |                   |                     |                  |            |  |  |  |  |

|               | •                                                                                                        |                                        |                 |                   |                     |                  |            |  |  |  |  |

|               | •                                                                                                        |                                        |                 |                   |                     |                  |            |  |  |  |  |

|               | •                                                                                                        |                                        |                 |                   |                     |                  |            |  |  |  |  |

|               |                                                                                                          |                                        |                 |                   |                     |                  |            |  |  |  |  |

|               | ()()()()()()() = V                                                                                       | aits 2 PWM cvc                         | les before de   | nerating the firs | t trigger event :   | after the module | is enabled |  |  |  |  |

|               |                                                                                                          | /aits 2 PWM cyc<br>/aits 1 PWM cyc     |                 |                   |                     |                  |            |  |  |  |  |

## REGISTER 16-12: TRGCONx: PWMx TRIGGER CONTROL REGISTER

| R/W-1           | R/W-1           | R/W-0                                                                        | R/W-0                      | R/W-0                | R/W-0                           | R/W-0           | R/W-0        |

|-----------------|-----------------|------------------------------------------------------------------------------|----------------------------|----------------------|---------------------------------|-----------------|--------------|

| PENH            | PENL            | POLH                                                                         | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>            | OVRENH          | OVRENL       |

| bit 15          |                 | •                                                                            |                            |                      |                                 |                 | bit          |

| R/W-0           | R/W-0           | R/W-0                                                                        | R/W-0                      | R/W-0                | R/W-0                           | R/W-0           |              |

|                 | -               | -                                                                            |                            | -                    | -                               | -               | R/W-0        |

| OVRDAT1         | OVRDAT0         | FLTDAT1                                                                      | FLTDAT0                    | CLDAT1               | CLDAT0                          | SWAP            | OSYNC        |

| bit 7           |                 |                                                                              |                            |                      |                                 |                 | bit          |

| Legend:         |                 |                                                                              |                            |                      |                                 |                 |              |

| R = Readable    | bit             | W = Writable                                                                 | bit                        | U = Unimpler         | mented bit, read                | l as '0'        |              |

| -n = Value at I | POR             | '1' = Bit is set                                                             |                            | '0' = Bit is cle     | ared                            | x = Bit is unkr | nown         |

| bit 15          |                 | xH Output Pin                                                                | Ownershin hit              |                      |                                 |                 |              |

| bit 10          |                 | odule controls                                                               | •                          |                      |                                 |                 |              |

|                 |                 | dule controls P                                                              |                            |                      |                                 |                 |              |

| bit 14          | PENL: PWM       | L Output Pin                                                                 | Ownership bit              |                      |                                 |                 |              |

|                 |                 | odule controls                                                               |                            |                      |                                 |                 |              |

|                 | 0 = GPIO mo     | dule controls P                                                              | WMxL pin                   |                      |                                 |                 |              |

| bit 13          |                 | xH Output Pin                                                                | -                          |                      |                                 |                 |              |

|                 |                 | oin is active-lov<br>oin is active-hig                                       |                            |                      |                                 |                 |              |

| bit 12          | POLL: PWM       | kL Output Pin F                                                              | Polarity bit               |                      |                                 |                 |              |

|                 |                 | in is active-low<br>in is active-hig                                         |                            |                      |                                 |                 |              |

| bit 11-10       | PMOD<1:0>:      | PWMx # I/O F                                                                 | in Mode bits <sup>(1</sup> | )                    |                                 |                 |              |

|                 | 01 = PWMx I     | d; do not use<br>/O pin pair is in<br>/O pin pair is in<br>/O pin pair is in | the Redunda                | nt Output mod        | е                               |                 |              |

| bit 9           |                 | verride Enable                                                               | •                          |                      |                                 |                 |              |

|                 | 1 = OVRDAT      | <1> controls ou<br>enerator contro                                           | utput on PWM               | xH pin               |                                 |                 |              |

| bit 8           | OVRENL: Ov      | erride Enable                                                                | for PWMxL Pir              | n bit                |                                 |                 |              |

|                 | 1 = OVRDAT      | <0> controls ou                                                              | utput on PWM               | xL pin               |                                 |                 |              |

|                 | 0 = PWMx ge     | nerator contro                                                               | ls PWMxL pin               |                      |                                 |                 |              |

| bit 7-6         | OVRDAT<1:0      | D>: Data for PV                                                              | VMxH, PWMxI                | Pins if Overri       | ide is Enabled b                | oits            |              |

|                 |                 |                                                                              |                            |                      | d by OVRDAT<<br>by OVRDAT<0     |                 |              |

| bit 5-4         | FLTDAT<1:0      | >: Data for PW                                                               | MxH and PWN                | MxL Pins if FL       | rMOD is Enable                  | ed bits         |              |

|                 |                 |                                                                              |                            |                      | by FLTDAT<1><br>by FLTDAT<0>.   |                 |              |

| bit 3-2         | CLDAT<1:0>      | : Data for PWN                                                               | /IxH and PWM               | IxL Pins if CLM      | 10D is Enabled                  | bits            |              |

|                 |                 |                                                                              |                            | •                    | ecified by CLDA                 |                 |              |

|                 | ese bits should | -                                                                            |                            |                      | enabled (PTEN<br>le IOCONx regi | -               | written afte |

# REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

|                                   | R/W-0            | R/W-0           | R/W-0                                 | R/W-0                                                            | R/W-0                                                                                                  | R/W-0                                                                                                    |

|-----------------------------------|------------------|-----------------|---------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                                   |                  | QEIG            | EC<31:24>                             |                                                                  |                                                                                                        |                                                                                                          |

|                                   |                  |                 |                                       |                                                                  |                                                                                                        | bit 8                                                                                                    |

|                                   | DAM 0            |                 |                                       | DAMA                                                             | DAVO                                                                                                   |                                                                                                          |

| R/W-U                             | R/W-U            |                 |                                       | R/W-U                                                            | R/W-U                                                                                                  | R/W-0                                                                                                    |

|                                   |                  | QEIGE           | EC<23:16>                             |                                                                  |                                                                                                        |                                                                                                          |

|                                   |                  |                 |                                       |                                                                  |                                                                                                        | bit (                                                                                                    |

|                                   |                  |                 |                                       |                                                                  |                                                                                                        |                                                                                                          |

| R = Readable bit W = Writable bit |                  | t               | U = Unimplemented bit, read as '0'    |                                                                  |                                                                                                        |                                                                                                          |

| २                                 | '1' = Bit is set |                 | '0' = Bit is cleared                  |                                                                  | x = Bit is unknown                                                                                     |                                                                                                          |

|                                   | R/W-0            | W = Writable bi | R/W-0 R/W-0 QEIGI<br>W = Writable bit | R/W-0 R/W-0 R/W-0 QEIGEC<23:16><br>W = Writable bit U = Unimplem | R/W-0     R/W-0     R/W-0       QEIGEC<23:16>       W = Writable bit       U = Unimplemented bit, real | R/W-0       R/W-0       R/W-0       R/W-0         QEIGEC<23:16>       U = Unimplemented bit, read as '0' |

## REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

## REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|--------------------------------------|------------------------------------|-------|-------|-------|--|

|                                    |       |       | QEIGE                                | C<15:8>                            |       |       |       |  |

| bit 15                             |       |       |                                      |                                    |       |       | bit 8 |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |       |       | QEIG                                 | EC<7:0>                            |       |       |       |  |

| bit 7                              |       |       |                                      |                                    |       |       | bit 0 |  |

| Legend:                            |       |       |                                      |                                    |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       | bit                                  | U = Unimplemented bit, read as '0' |       |       |       |  |