Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decans                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

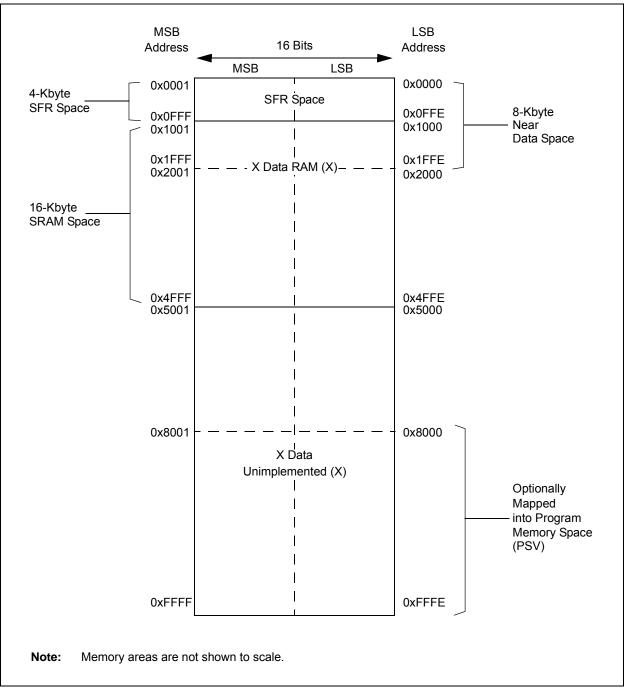

| RAM Size                   | 16K × 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc202t-e-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

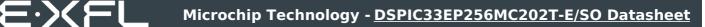

### FIGURE 2-7: INTERLEAVED PFC

## TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _     | _       | _           | _       | —       | —      | —           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

|                                               | Vector | IRQ        |                   | Inte     | errupt Bit L | ocation     |

|-----------------------------------------------|--------|------------|-------------------|----------|--------------|-------------|

| Interrupt Source                              | # #    |            | IVT Address       | Flag     | Enable       | Priority    |

|                                               | High   | est Natura | I Order Priority  |          |              |             |

| INT0 – External Interrupt 0                   | 8      | 0          | 0x000014          | IFS0<0>  | IEC0<0>      | IPC0<2:0>   |

| IC1 – Input Capture 1                         | 9      | 1          | 0x000016          | IFS0<1>  | IEC0<1>      | IPC0<6:4>   |

| OC1 – Output Compare 1                        | 10     | 2          | 0x000018          | IFS0<2>  | IEC0<2>      | IPC0<10:8>  |

| T1 – Timer1                                   | 11     | 3          | 0x00001A          | IFS0<3>  | IEC0<3>      | IPC0<14:12> |

| DMA0 – DMA Channel 0                          | 12     | 4          | 0x00001C          | IFS0<4>  | IEC0<4>      | IPC1<2:0>   |

| IC2 – Input Capture 2                         | 13     | 5          | 0x00001E          | IFS0<5>  | IEC0<5>      | IPC1<6:4>   |

| OC2 – Output Compare 2                        | 14     | 6          | 0x000020          | IFS0<6>  | IEC0<6>      | IPC1<10:8>  |

| T2 – Timer2                                   | 15     | 7          | 0x000022          | IFS0<7>  | IEC0<7>      | IPC1<14:12> |

| T3 – Timer3                                   | 16     | 8          | 0x000024          | IFS0<8>  | IEC0<8>      | IPC2<2:0>   |

| SPI1E – SPI1 Error                            | 17     | 9          | 0x000026          | IFS0<9>  | IEC0<9>      | IPC2<6:4>   |

| SPI1 – SPI1 Transfer Done                     | 18     | 10         | 0x000028          | IFS0<10> | IEC0<10>     | IPC2<10:8>  |

| U1RX – UART1 Receiver                         | 19     | 11         | 0x00002A          | IFS0<11> | IEC0<11>     | IPC2<14:12> |

| U1TX – UART1 Transmitter                      | 20     | 12         | 0x00002C          | IFS0<12> | IEC0<12>     | IPC3<2:0>   |

| AD1 – ADC1 Convert Done                       | 21     | 13         | 0x00002E          | IFS0<13> | IEC0<13>     | IPC3<6:4>   |

| DMA1 – DMA Channel 1                          | 22     | 14         | 0x000030          | IFS0<14> | IEC0<14>     | IPC3<10:8>  |

| Reserved                                      | 23     | 15         | 0x000032          |          |              | _           |

| SI2C1 – I2C1 Slave Event                      | 24     | 16         | 0x000034          | IFS1<0>  | IEC1<0>      | IPC4<2:0>   |

| MI2C1 – I2C1 Master Event                     | 25     | 17         | 0x000036          | IFS1<1>  | IEC1<1>      | IPC4<6:4>   |

| CM – Comparator Combined Event                | 26     | 18         | 0x000038          | IFS1<2>  | IEC1<2>      | IPC4<10:8>  |

| CN – Input Change Interrupt                   | 27     | 19         | 0x00003A          | IFS1<3>  | IEC1<3>      | IPC4<14:12> |

| INT1 – External Interrupt 1                   | 28     | 20         | 0x00003C          | IFS1<4>  | IEC1<4>      | IPC5<2:0>   |

| Reserved                                      | 29-31  | 21-23      | 0x00003E-0x000042 |          |              | _           |

| DMA2 – DMA Channel 2                          | 32     | 24         | 0x000044          | IFS1<8>  | IEC1<8>      | IPC6<2:0>   |

| OC3 – Output Compare 3                        | 33     | 25         | 0x000046          | IFS1<9>  | IEC1<9>      | IPC6<6:4>   |

| OC4 – Output Compare 4                        | 34     | 26         | 0x000048          | IFS1<10> | IEC1<10>     | IPC6<10:8>  |

| T4 – Timer4                                   | 35     | 27         | 0x00004A          | IFS1<11> | IEC1<11>     | IPC6<14:12> |

| T5 – Timer5                                   | 36     | 28         | 0x00004C          | IFS1<12> | IEC1<12>     | IPC7<2:0>   |

| INT2 – External Interrupt 2                   | 37     | 29         | 0x00004E          | IFS1<13> | IEC1<13>     | IPC7<6:4>   |

| U2RX – UART2 Receiver                         | 38     | 30         | 0x000050          | IFS1<14> | IEC1<14>     | IPC7<10:8>  |

| U2TX – UART2 Transmitter                      | 39     | 31         | 0x000052          | IFS1<15> | IEC1<15>     | IPC7<14:12> |

| SPI2E – SPI2 Error                            | 40     | 32         | 0x000054          | IFS2<0>  | IEC2<0>      | IPC8<2:0>   |

| SPI2 – SPI2 Transfer Done                     | 41     | 33         | 0x000056          | IFS2<1>  | IEC2<1>      | IPC8<6:4>   |

| C1RX – CAN1 RX Data Ready <sup>(1)</sup>      | 42     | 34         | 0x000058          | IFS2<2>  | IEC2<2>      | IPC8<10:8>  |

| C1 – CAN1 Event <sup>(1)</sup>                | 43     | 35         | 0x00005A          | IFS2<3>  | IEC2<3>      | IPC8<14:12> |

| DMA3 – DMA Channel 3                          | 44     | 36         | 0x00005C          | IFS2<4>  | IEC2<4>      | IPC9<2:0>   |

| IC3 – Input Capture 3                         | 45     | 37         | 0x00005E          | IFS2<5>  | IEC2<5>      | IPC9<6:4>   |

| IC4 – Input Capture 4                         | 46     | 38         | 0x000060          | IFS2<6>  | IEC2<6>      | IPC9<10:8>  |

| Reserved                                      | 47-56  | 39-48      | 0x000062-0x000074 | —        | —            | —           |

| SI2C2 – I2C2 Slave Event                      | 57     | 49         | 0x000076          | IFS3<1>  | IEC3<1>      | IPC12<6:4>  |

| MI2C2 – I2C2 Master Event                     | 58     | 50         | 0x000078          | IFS3<2>  | IEC3<2>      | IPC12<10:8> |

| Reserved                                      | 59-64  | 51-56      | 0x00007A-0x000084 |          | _            |             |

| PSEM – PWM Special Event Match <sup>(2)</sup> | 65     | 57         | 0x000086          | IFS3<9>  | IEC3<9>      | IPC14<6:4>  |

### TABLE 7-1: INTERRUPT VECTOR DETAILS

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

# REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

NOTES:

### REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|-----------------|-------|

| —            |                           |                                                                                                    |                            | QEB1R<6:0>        |                 |                 |       |

| bit 15       |                           |                                                                                                    |                            |                   |                 |                 | bit 8 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |                           |                                                                                                    |                            | QEA1R<6:0>        |                 |                 |       |

| bit 7        |                           |                                                                                                    |                            |                   |                 |                 | bit 0 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| Legend:      |                           |                                                                                                    |                            |                   |                 |                 |       |

| R = Readat   | ole bit                   | W = Writable                                                                                       | bit                        | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR                    | '1' = Bit is set                                                                                   |                            | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 1111001 =                 | 1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss                    | 121<br>P1                  |                   |                 |                 |       |

| bit 7        | Unimpleme                 | nted: Read as '                                                                                    | 0'                         |                   |                 |                 |       |

| bit 6-0      | (see Table 1<br>1111001 = | >: Assign A (QE<br>1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss | selection nun<br>121<br>P1 |                   | n Pin bits      |                 |       |

## 13.2 Timer Control Registers

| R/W-0         | U-0                                                                                                                                     | R/W-0                                                          | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|--|--|

| TON           |                                                                                                                                         | TSIDL                                                          | —              | _                |                 |                 | _     |  |  |  |  |  |  |  |

| bit 15        |                                                                                                                                         |                                                                |                |                  |                 |                 | bit 8 |  |  |  |  |  |  |  |

|               |                                                                                                                                         |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| U-0           | R/W-0                                                                                                                                   | R/W-0                                                          | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |  |  |  |  |

| _             | TGATE                                                                                                                                   | TCKPS1                                                         | TCKPS0         | T32              | _               | TCS             | _     |  |  |  |  |  |  |  |

| bit 7         |                                                                                                                                         |                                                                |                |                  |                 |                 | bit ( |  |  |  |  |  |  |  |

| <u> </u>      |                                                                                                                                         |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| Legend:       | - 1-:4                                                                                                                                  |                                                                |                | II II.           |                 |                 |       |  |  |  |  |  |  |  |

| R = Readable  |                                                                                                                                         | W = Writable                                                   |                | -                | nented bit, rea |                 |       |  |  |  |  |  |  |  |

| -n = Value at | PUR                                                                                                                                     | '1' = Bit is set                                               |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |  |  |  |  |  |  |  |

| bit 15        | TON: Timerx                                                                                                                             | On hit                                                         |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | When T32 = 2                                                                                                                            |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 1 = Starts 32-                                                                                                                          | 1 = Starts 32-bit Timerx/y                                     |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | •                                                                                                                                       | 0 = Stops 32-bit Timerx/y                                      |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               |                                                                                                                                         | $\frac{\text{When T32 = 0:}}{1 = \text{Starts 16-bit Timerx}}$ |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 0 = Stops 16-                                                                                                                           |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 14        | Unimplemen                                                                                                                              | ted: Read as '                                                 | )'             |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 13        | TSIDL: Timer                                                                                                                            | TSIDL: Timerx Stop in Idle Mode bit                            |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               |                                                                                                                                         | -                                                              |                | ode              |                 |                 |       |  |  |  |  |  |  |  |

| bit 12-7      | -                                                                                                                                       | Unimplemented: Read as '0'                                     |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 6         | TGATE: Timerx Gated Time Accumulation Enable bit                                                                                        |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | <u>When TCS = 1:</u><br>This bit is ignored.                                                                                            |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | When TCS = $0$ :                                                                                                                        |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 1 = Gated time accumulation is enabled<br>0 = Gated time accumulation is disabled                                                       |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               |                                                                                                                                         |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 5-4       |                                                                                                                                         | : Timerx Input                                                 | Clock Prescal  | e Select bits    |                 |                 |       |  |  |  |  |  |  |  |

|               | 11 = 1:256<br>10 = 1:64                                                                                                                 |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 01 = 1:8                                                                                                                                |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 00 = 1:1                                                                                                                                |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 3         | T32: 32-Bit Ti                                                                                                                          | mer Mode Sele                                                  | ect bit        |                  |                 |                 |       |  |  |  |  |  |  |  |

|               |                                                                                                                                         | nd Timery form<br>nd Timery act as                             |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 2         | Unimplemen                                                                                                                              | ted: Read as '                                                 | )'             |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 1         | TCS: Timerx                                                                                                                             | Clock Source S                                                 | elect bit      |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl                                                                                                       | clock is from pir<br>lock (FP)                                 | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |  |  |  |  |  |

| bit 0         | Unimplomon                                                                                                                              | ted: Read as '                                                 | ı'             |                  |                 |                 |       |  |  |  |  |  |  |  |

# REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

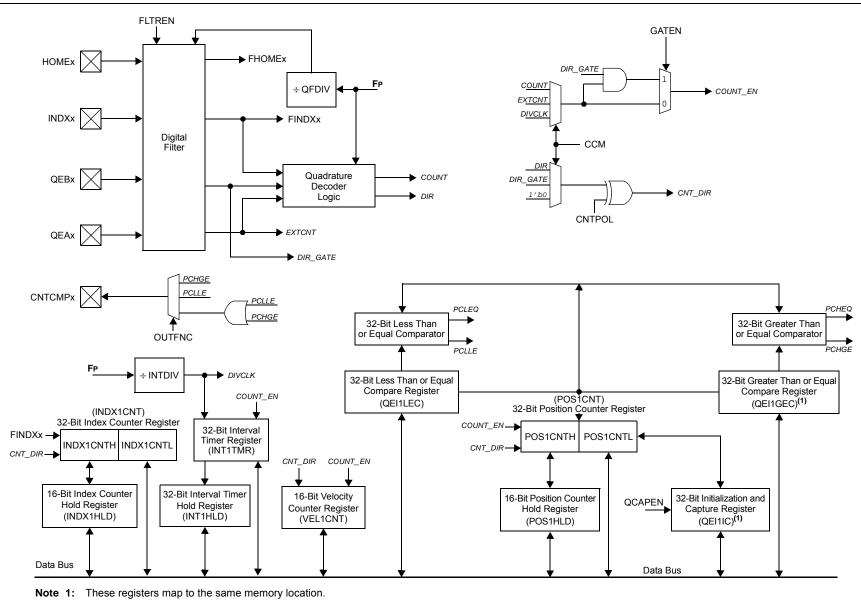

### FIGURE 17-1: QEI BLOCK DIAGRAM

### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

# REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                            |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                          | U-0                                                                                                | U-0                                                                                      | U-0      | U-0          | U-0              | U-0             | U-0   |  |  |  |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------|--------------|------------------|-----------------|-------|--|--|--|--|--|--|

| _                            | —                                                                                                  | —                                                                                        |          | —            | —                | —               | _     |  |  |  |  |  |  |

| bit 15                       |                                                                                                    |                                                                                          |          |              |                  |                 | bit   |  |  |  |  |  |  |

|                              |                                                                                                    |                                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

| R/W-0                        | R/W-0                                                                                              | R/W-0                                                                                    | U-0      | R/W-0        | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |  |

| IVRIE                        | WAKIE                                                                                              | ERRIE                                                                                    | —        | FIFOIE       | RBOVIE           | RBIE            | TBIE  |  |  |  |  |  |  |

| bit 7                        |                                                                                                    |                                                                                          |          |              |                  |                 | bit   |  |  |  |  |  |  |

|                              |                                                                                                    |                                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

| <b>Legend:</b><br>R = Readab | la hit                                                                                             | W = Writable b                                                                           | .it      |              | montod bit rook  | l oo 'O'        |       |  |  |  |  |  |  |

| n = Value a                  |                                                                                                    | '1' = Bit is set                                                                         | אנ       | 0 = Onimpler | mented bit, read | x = Bit is unkr |       |  |  |  |  |  |  |

|                              | IL POR                                                                                             | I = DILIS SEL                                                                            |          |              | areu             |                 | IOWI  |  |  |  |  |  |  |

| bit 15-8                     | Unimplemen                                                                                         | <b>ted:</b> Read as '0                                                                   | ,        |              |                  |                 |       |  |  |  |  |  |  |

| bit 7                        | -                                                                                                  | Unimplemented: Read as '0'<br>IVRIE: Invalid Message Interrupt Enable bit                |          |              |                  |                 |       |  |  |  |  |  |  |

|                              | 1 = Interrupt request is enabled                                                                   |                                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

|                              |                                                                                                    | request is not er                                                                        |          |              |                  |                 |       |  |  |  |  |  |  |

| bit 6                        | WAKIE: Bus Wake-up Activity Interrupt Enable bit                                                   |                                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

|                              | 1 = Interrupt request is enabled                                                                   |                                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

|                              |                                                                                                    | request is not er                                                                        |          |              |                  |                 |       |  |  |  |  |  |  |

| bit 5                        |                                                                                                    | ERRIE: Error Interrupt Enable bit                                                        |          |              |                  |                 |       |  |  |  |  |  |  |

|                              | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

| bit 4                        |                                                                                                    | ted: Read as '0                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

| bit 3                        | -                                                                                                  |                                                                                          |          | o hit        |                  |                 |       |  |  |  |  |  |  |

| DIL J                        |                                                                                                    | <b>FIFOIE:</b> FIFO Almost Full Interrupt Enable bit<br>1 = Interrupt request is enabled |          |              |                  |                 |       |  |  |  |  |  |  |

|                              | 0 = Interrupt request is not enabled                                                               |                                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

| bit 2                        | <b>RBOVIE:</b> RX                                                                                  | <b>RBOVIE:</b> RX Buffer Overflow Interrupt Enable bit                                   |          |              |                  |                 |       |  |  |  |  |  |  |

|                              | 1 = Interrupt i                                                                                    | 1 = Interrupt request is enabled                                                         |          |              |                  |                 |       |  |  |  |  |  |  |

|                              | 0 = Interrupt i                                                                                    | 0 = Interrupt request is not enabled                                                     |          |              |                  |                 |       |  |  |  |  |  |  |

| bit 1                        |                                                                                                    | ffer Interrupt En                                                                        |          |              |                  |                 |       |  |  |  |  |  |  |

|                              |                                                                                                    | equest is enabl                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

|                              | 0 = Interrupt request is not enabled                                                               |                                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

|                              | 0 = Interrupt request is not enabled <b>TBIE:</b> TX Buffer Interrupt Enable bit                   |                                                                                          |          |              |                  |                 |       |  |  |  |  |  |  |

| bit 0                        | TBIE: TX Buf                                                                                       | •                                                                                        | able bit |              |                  |                 |       |  |  |  |  |  |  |

### REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-x         | R/W-x                                        | R/W-x                                    | R/W-x         | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |  |  |  |  |  |

|---------------|----------------------------------------------|------------------------------------------|---------------|------------------------------------|-------|-----------------|-------|--|--|--|--|--|--|

| EID5          | EID4                                         | EID3                                     | EID2          | EID1                               | EID0  | RTR             | RB1   |  |  |  |  |  |  |

| bit 15        |                                              |                                          |               |                                    |       |                 | bit 8 |  |  |  |  |  |  |

|               |                                              |                                          |               |                                    |       |                 |       |  |  |  |  |  |  |

| U-x           | U-x                                          | U-x                                      | R/W-x         | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |  |  |  |  |  |

| —             | —                                            | —                                        | RB0           | DLC3                               | DLC2  | DLC1            | DLC0  |  |  |  |  |  |  |

| bit 7         |                                              |                                          |               |                                    |       |                 | bit 0 |  |  |  |  |  |  |

| Lonondi       |                                              |                                          |               |                                    |       |                 |       |  |  |  |  |  |  |

| Legend:       | l. h.:.                                      |                                          | L.11          |                                    |       | -l (O)          |       |  |  |  |  |  |  |

| R = Readab    |                                              | W = Writable                             |               | U = Unimplemented bit, read as '0' |       |                 |       |  |  |  |  |  |  |

| -n = Value a  | t POR                                        | '1' = Bit is set                         |               | '0' = Bit is cle                   | ared  | x = Bit is unkr | iown  |  |  |  |  |  |  |

|               |                                              |                                          |               |                                    |       |                 |       |  |  |  |  |  |  |

| bit 15-10     | EID<5:0>: E                                  | xtended Identifi                         | er bits       |                                    |       |                 |       |  |  |  |  |  |  |

| bit 9         | RTR: Remot                                   | RTR: Remote Transmission Request bit     |               |                                    |       |                 |       |  |  |  |  |  |  |

|               | When IDE = 1:                                |                                          |               |                                    |       |                 |       |  |  |  |  |  |  |

|               | 1 = Message will request remote transmission |                                          |               |                                    |       |                 |       |  |  |  |  |  |  |

|               |                                              | 0 = Normal message                       |               |                                    |       |                 |       |  |  |  |  |  |  |

|               |                                              | When IDE = 0:<br>The RTR bit is ignored. |               |                                    |       |                 |       |  |  |  |  |  |  |

| <b>h</b> :+ 0 | RB1: Reserv                                  | -                                        |               |                                    |       |                 |       |  |  |  |  |  |  |

| bit 8         |                                              |                                          | or CAN proto  |                                    |       |                 |       |  |  |  |  |  |  |

|               |                                              | et this bit to '0' p                     | -             | 0001.                              |       |                 |       |  |  |  |  |  |  |

| bit 7-5       | •                                            | nted: Read as '                          | 0             |                                    |       |                 |       |  |  |  |  |  |  |

| bit 4         | RB0: Reserv                                  |                                          | <b></b>       |                                    |       |                 |       |  |  |  |  |  |  |

|               | User must se                                 | et this bit to '0' p                     | per CAN proto | ocol.                              |       |                 |       |  |  |  |  |  |  |

| hit 2 0       |                                              | DLC - 2.0 + Data Langth Cada hita        |               |                                    |       |                 |       |  |  |  |  |  |  |

### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

### BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|

|                                   |       |                  | Ву    | /te 1                              |       |                    |       |  |

| bit 15                            |       |                  |       |                                    |       |                    | bit 8 |  |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

|                                   |       |                  | Ву    | rte 0                              |       |                    |       |  |

| bit 7                             |       |                  |       |                                    |       |                    | bit 0 |  |

| Legend:                           |       |                  |       |                                    |       |                    |       |  |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at POR                 |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

| R/W-0         | R/W-0                                                                                                                                    | R/W-0                                                 | R/W-0        | R/W-0             | R/W-0           | R/W-0           | R/W-0    |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------|-------------------|-----------------|-----------------|----------|--|--|--|--|

| EDG1MOD       | EDG1POL                                                                                                                                  | EDG1SEL3                                              | EDG1SEL2     | EDG1SEL1          | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |  |  |

| bit 15        |                                                                                                                                          | 1                                                     |              | 11                |                 | 1               | bit 8    |  |  |  |  |

|               |                                                                                                                                          |                                                       |              |                   |                 |                 |          |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                    | R/W-0                                                 | R/W-0        | R/W-0             | R/W-0           | U-0             | U-0      |  |  |  |  |

| EDG2MOD       | EDG2POL                                                                                                                                  | EDG2SEL3                                              | EDG2SEL2     | EDG2SEL1          | EDG2SEL0        | _               | _        |  |  |  |  |

| bit 7         |                                                                                                                                          |                                                       |              | 1 1               |                 |                 | bit C    |  |  |  |  |

|               |                                                                                                                                          |                                                       |              |                   |                 |                 |          |  |  |  |  |

| Legend:       |                                                                                                                                          |                                                       |              |                   |                 |                 |          |  |  |  |  |

| R = Readabl   | le bit                                                                                                                                   | W = Writable                                          | oit          | U = Unimplem      | ented bit, read | l as '0'        |          |  |  |  |  |

| -n = Value at | POR                                                                                                                                      | '1' = Bit is set                                      |              | '0' = Bit is clea | red             | x = Bit is unkr | nown     |  |  |  |  |

|               |                                                                                                                                          |                                                       |              |                   |                 |                 |          |  |  |  |  |

| bit 15        | EDG1MOD: E                                                                                                                               | Edge 1 Edge Sa                                        | ampling Mode | Selection bit     |                 |                 |          |  |  |  |  |

|               | 1 = Edge 1 is                                                                                                                            | s edge-sensitive                                      | 9            |                   |                 |                 |          |  |  |  |  |

|               | •                                                                                                                                        | s level-sensitive                                     |              |                   |                 |                 |          |  |  |  |  |

| bit 14        |                                                                                                                                          | dge 1 Polarity                                        |              |                   |                 |                 |          |  |  |  |  |

|               | 1 = Edge 1 is programmed for a positive edge response                                                                                    |                                                       |              |                   |                 |                 |          |  |  |  |  |

| L:1 40 40     | •                                                                                                                                        | 0 = Edge 1 is programmed for a negative edge response |              |                   |                 |                 |          |  |  |  |  |

| bit 13-10     |                                                                                                                                          | EDG1SEL<3:0>: Edge 1 Source Select bits               |              |                   |                 |                 |          |  |  |  |  |

|               | 1xxx = Reserved<br>01xx = Reserved                                                                                                       |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               |                                                                                                                                          | 011x = Reserved<br>0011 = CTED1 pin                   |              |                   |                 |                 |          |  |  |  |  |

|               | 0010 = CTED2 pin                                                                                                                         |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               | 0001 = OC1 module<br>0000 = Timer1 module                                                                                                |                                                       |              |                   |                 |                 |          |  |  |  |  |

| hit 0         |                                                                                                                                          |                                                       | :+           |                   |                 |                 |          |  |  |  |  |

| bit 9         |                                                                                                                                          | EDG2STAT: Edge 2 Status bit                           |              |                   |                 |                 |          |  |  |  |  |

|               | Indicates the status of Edge 2 and can be written to control the edge source.<br>1 = Edge 2 has occurred                                 |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               | 0 = Edge 2 has not occurred                                                                                                              |                                                       |              |                   |                 |                 |          |  |  |  |  |

| bit 8         | EDG1STAT: Edge 1 Status bit                                                                                                              |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               | Indicates the status of Edge 1 and can be written to control the edge source.                                                            |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               | 1 = Edge 1 has occurred<br>0 = Edge 1 has not occurred                                                                                   |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               | -                                                                                                                                        |                                                       |              |                   |                 |                 |          |  |  |  |  |

| bit 7         |                                                                                                                                          | EDG2MOD: Edge 2 Edge Sampling Mode Selection bit      |              |                   |                 |                 |          |  |  |  |  |

|               | 1 = Edge 2 is edge-sensitive<br>0 = Edge 2 is level-sensitive                                                                            |                                                       |              |                   |                 |                 |          |  |  |  |  |

| bit 6         | •                                                                                                                                        | dge 2 Polarity                                        |              |                   |                 |                 |          |  |  |  |  |

| Sit 0         |                                                                                                                                          | •                                                     |              | dae response      |                 |                 |          |  |  |  |  |

|               | <ul> <li>1 = Edge 2 is programmed for a positive edge response</li> <li>0 = Edge 2 is programmed for a negative edge response</li> </ul> |                                                       |              |                   |                 |                 |          |  |  |  |  |

| bit 5-2       | EDG2SEL<3:0>: Edge 2 Source Select bits                                                                                                  |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               | 1111 = Reserved                                                                                                                          |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               |                                                                                                                                          | 01xx = Reserved                                       |              |                   |                 |                 |          |  |  |  |  |

|               | 0100 = CMP <sup>2</sup><br>0011 = CTEE                                                                                                   |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               |                                                                                                                                          |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               | 0010 = CTED1 pin<br>0001 = OC1 module                                                                                                    |                                                       |              |                   |                 |                 |          |  |  |  |  |

|               | 0001 = OC1                                                                                                                               | module                                                |              |                   |                 |                 |          |  |  |  |  |

|               |                                                                                                                                          | module                                                |              |                   |                 |                 |          |  |  |  |  |

### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

| oit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                                                                      |

|---------|------------------------|-------------|---------------------------------------------------------------------------------------------------------|

|         | PTGCTRL(1)             | 0000        | Reserved.                                                                                               |

|         |                        | 0001        | Reserved.                                                                                               |

|         |                        | 0010        | Disable Step Delay Timer (PTGSD).                                                                       |

|         |                        | 0011        | Reserved.                                                                                               |

|         |                        | 0100        | Reserved.                                                                                               |

|         |                        | 0101        | Reserved.                                                                                               |

|         |                        | 0110        | Enable Step Delay Timer (PTGSD).                                                                        |

|         |                        | 0111        | Reserved.                                                                                               |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                   |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                   |

|         |                        | 1010        | Reserved.                                                                                               |

|         |                        | 1011        | Wait for the software trigger bit transition from low-to-high before continuing (PTGSWT = $0$ to $1$ ). |

|         |                        | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                        |

|         |                        | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                        |

|         |                        | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                        |

|         |                        | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                          |

|         | PTGADD(1)              | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                         |

|         |                        | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                         |

|         |                        | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                            |

|         |                        | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                            |

|         |                        | 0100        | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM)                         |

|         |                        | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                  |

|         |                        | 0110        | Reserved.                                                                                               |

|         |                        | 0111        | Reserved.                                                                                               |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                       |

|         |                        | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                       |

|         |                        | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                          |

|         |                        | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                          |

|         |                        | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                      |

|         |                        | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                |

|         |                        | 1110        | Reserved.                                                                                               |

|         |                        | 1111        | Reserved.                                                                                               |

### TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        |                                                  | Description                                 | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |  |

|--------------------|----------------------|--------|--------------------------------------------------|---------------------------------------------|---------------|-------------------------------|--------------------------|--|

| 25 DAW             |                      | DAW    | Wn                                               | Wn = decimal adjust Wn                      | 1             | 1                             | С                        |  |

| 26                 | DEC                  | DEC    | f                                                | f = f - 1                                   | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC    | f,WREG                                           | WREG = f – 1                                | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC    | Ws,Wd                                            | Wd = Ws - 1                                 | 1             | 1                             | C,DC,N,OV,Z              |  |

| 27                 | DEC2                 | DEC2   | f                                                | f = f - 2                                   | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC2   | f,WREG                                           | WREG = f – 2                                | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC2   | Ws,Wd                                            | Wd = Ws - 2                                 | 1             | 1                             | C,DC,N,OV,Z              |  |

| 28                 | DISI                 | DISI   | #lit14                                           | Disable Interrupts for k instruction cycles | 1             | 1                             | None                     |  |

| 29                 | DIV                  | DIV.S  | Wm,Wn                                            | Signed 16/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |  |

|                    |                      | DIV.SD | Wm,Wn                                            | Signed 32/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |  |

|                    |                      | DIV.U  | Wm,Wn                                            | Unsigned 16/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |  |

|                    |                      | DIV.UD | Wm,Wn                                            | Unsigned 32/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |  |

| 30                 | DIVF                 | DIVF   | Wm , Wn <sup>(1)</sup>                           | Signed 16/16-bit Fractional Divide          | 1             | 18                            | N,Z,C,OV                 |  |

| 31 DO              | DO                   | DO     | #lit15,Expr <sup>(1)</sup>                       | Do code to PC + Expr, lit15 + 1 times       | 2             | 2                             | None                     |  |

|                    |                      | DO     | Wn, Expr(1)                                      | Do code to PC + Expr, (Wn) + 1 times        | 2             | 2                             | None                     |  |

| 32                 | ED                   | ED     | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance (no accumulate)          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

| 33                 | EDAC                 | EDAC   | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance                          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |