Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc204-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

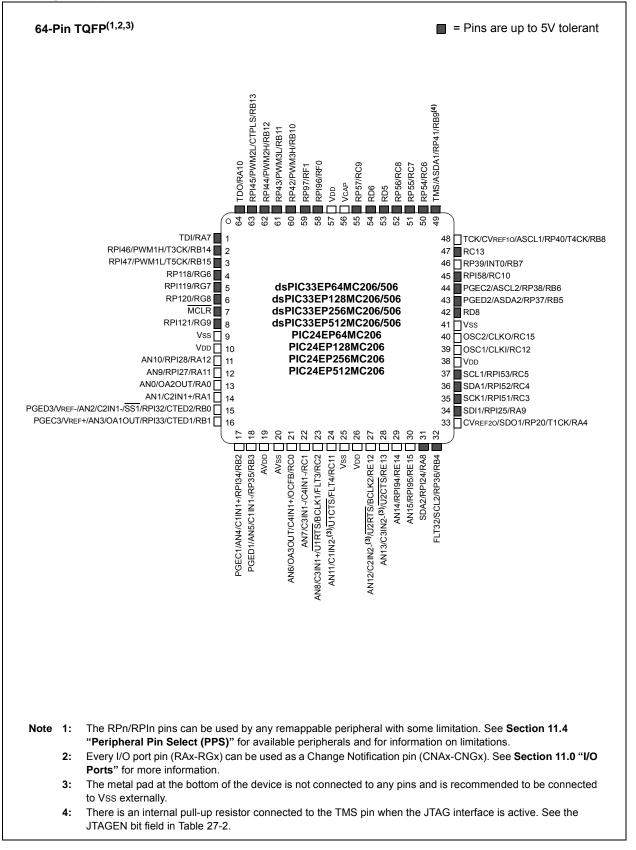

# Pin Diagrams (Continued)

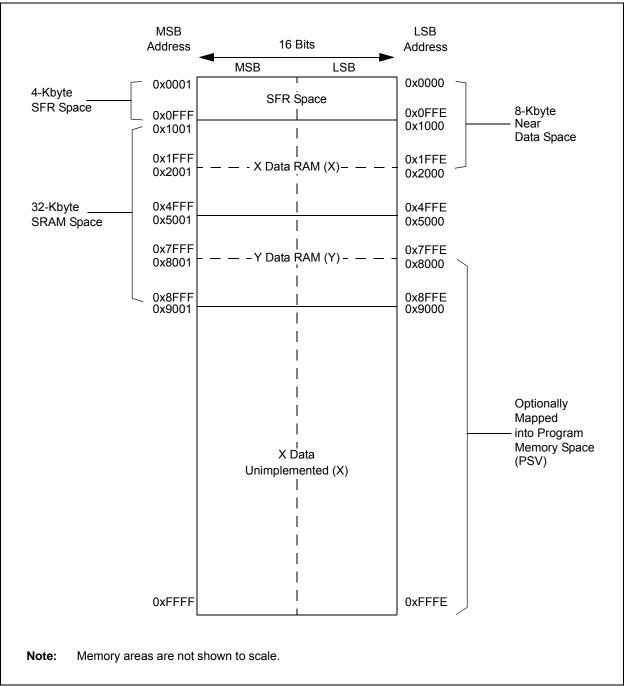

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

# TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10   | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|----------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |          | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT       | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F        | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |          | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |          |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |          |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -        | _          | —     | _     | _       | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<3:0> |            |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>      | —       |        | ICDIP<2:0  | >     | _        | —       | —           | _       | —       | _      | -           |        | 4400          |

| IPC36        | 0888  | -      | l      | PTG0IP<2:0 | )>      | _       | PT     | GWDTIP<    | 2:0>  | _        | P       | TGSTEPIP<2  | :0>     | —       | —      |             |        | 4440          |

| IPC37        | 088A  |        | _      | _          | _       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | >       | _       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | —       | _      |            |       | —        | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | —          | —       | —       | _      |            |       | —        | _       | DAE         | DOOVR   | _       | —      |             |        | 0000          |

| INTCON4      | 08C6  | -      | _      | —          | _       | _       | _      |            | _     | _        | _       | —           | —       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | -      | —      | —          | _       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | M<7:0>  |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

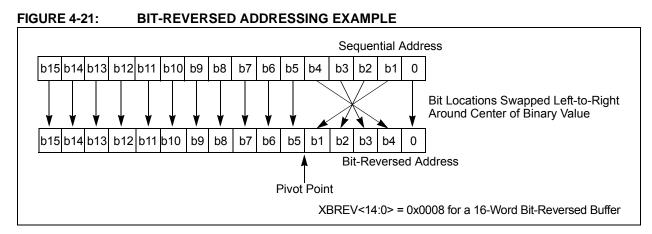

# TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      | Bit-Reversed Address |    |    |    |         |  |

|----|----|-------|-----------|---------|----------------------|----|----|----|---------|--|

| A3 | A2 | A1    | A0        | Decimal | A3                   | A2 | A1 | A0 | Decimal |  |

| 0  | 0  | 0     | 0         | 0       | 0                    | 0  | 0  | 0  | 0       |  |

| 0  | 0  | 0     | 1         | 1       | 1                    | 0  | 0  | 0  | 8       |  |

| 0  | 0  | 1     | 0         | 2       | 0                    | 1  | 0  | 0  | 4       |  |

| 0  | 0  | 1     | 1         | 3       | 1                    | 1  | 0  | 0  | 12      |  |

| 0  | 1  | 0     | 0         | 4       | 0                    | 0  | 1  | 0  | 2       |  |

| 0  | 1  | 0     | 1         | 5       | 1                    | 0  | 1  | 0  | 10      |  |

| 0  | 1  | 1     | 0         | 6       | 0                    | 1  | 1  | 0  | 6       |  |

| 0  | 1  | 1     | 1         | 7       | 1                    | 1  | 1  | 0  | 14      |  |

| 1  | 0  | 0     | 0         | 8       | 0                    | 0  | 0  | 1  | 1       |  |

| 1  | 0  | 0     | 1         | 9       | 1                    | 0  | 0  | 1  | 9       |  |

| 1  | 0  | 1     | 0         | 10      | 0                    | 1  | 0  | 1  | 5       |  |

| 1  | 0  | 1     | 1         | 11      | 1                    | 1  | 0  | 1  | 13      |  |

| 1  | 1  | 0     | 0         | 12      | 0                    | 0  | 1  | 1  | 3       |  |

| 1  | 1  | 0     | 1         | 13      | 1                    | 0  | 1  | 1  | 11      |  |

| 1  | 1  | 1     | 0         | 14      | 0                    | 1  | 1  | 1  | 7       |  |

| 1  | 1  | 1     | 1         | 15      | 1                    | 1  | 1  | 1  | 15      |  |

| -n = Value at F | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, rea | id as '0'       |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

|                 |       |                  |       |                  |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit C |

|                 |       |                  | NVMAD | )R<23:16>        |                 |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| _               | —     | —                | —     | —                | _               | —               | —     |

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0             | U-0             | U-0   |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADR<23:16>:** Nonvolatile Memory Write Address High bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-3: NVMADRL: NONVOLATILE MEMORY ADDRESS REGISTER LOW

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | NVMA  | DR<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | NVMA  | DR<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 NVMADR<15:0>: Nonvolatile Memory Write Address Low bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY

| U-0             | U-0 | U-0              | U-0  | U-0              | U-0             | U-0             | U-0   |

|-----------------|-----|------------------|------|------------------|-----------------|-----------------|-------|

| —               | —   | —                | _    | —                | —               | —               | —     |

| bit 15          |     |                  |      |                  |                 |                 | bit 8 |

|                 |     |                  |      |                  |                 |                 |       |

| W-0             | W-0 | W-0              | W-0  | W-0              | W-0             | W-0             | W-0   |

|                 |     |                  | NVMK | EY<7:0>          |                 |                 |       |

| bit 7           |     |                  |      |                  |                 |                 | bit 0 |

|                 |     |                  |      |                  |                 |                 |       |

| Legend:         |     |                  |      |                  |                 |                 |       |

| R = Readable I  | bit | W = Writable     | bit  | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

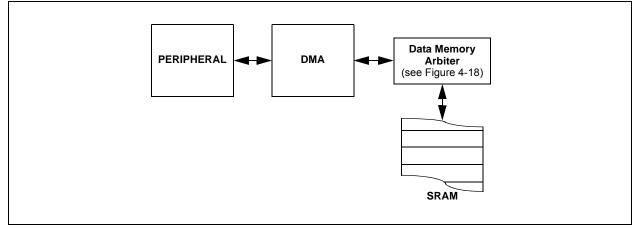

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

# FIGURE 8-1: DMA CONTROLLER MODULE

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00    |                                       |              |                   |                  |                 |        |

|-----------------|----------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |

| —               | —              | —                                     | —            | —                 | —                | —               | —      |

| bit 15          |                |                                       |              |                   |                  |                 | bit 8  |

|                 |                |                                       |              |                   |                  |                 |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |

| —               |                | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7           |                |                                       |              |                   |                  |                 | bit 0  |

|                 |                |                                       |              |                   |                  |                 |        |

| Legend:         |                |                                       |              |                   |                  |                 |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                 |                |                                       |              |                   |                  |                 |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                   |                  |                 |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl  | aa hit           |                 |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |                 |        |

|                 |                | e and interrupt<br>est collision is d |              |                   | elecieu          |                 |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                   |                  |                 |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |                 |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

# REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

## 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

# 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# REGISTER 11-16: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38 (dsPIC33EPXXXMC20X AND PIC24EPXXXMC20X DEVICES ONLY)

|              | -         |                                      |       |                  |                   | -               |                |

|--------------|-----------|--------------------------------------|-------|------------------|-------------------|-----------------|----------------|

| U-0          | R/W-0     | R/W-0                                | R/W-0 | R/W-0            | R/W-0             | R/W-0           | R/W-0          |

|              |           |                                      |       | DTCMP1R<6:       | 0>                |                 |                |

| bit 15       |           |                                      |       |                  |                   |                 | bit 8          |

|              |           |                                      |       |                  |                   |                 |                |

| U-0          | U-0       | U-0                                  | U-0   | U-0              | U-0               | U-0             | U-0            |

| —            | —         | —                                    | _     |                  | _                 | —               | —              |

| bit 7        |           |                                      |       |                  |                   |                 | bit C          |

|              |           |                                      |       |                  |                   |                 |                |

| Legend:      |           |                                      |       |                  |                   |                 |                |

| R = Readal   | ole bit   | W = Writable                         | bit   | U = Unimpler     | mented bit, read  | d as '0'        |                |

| -n = Value a | at POR    | '1' = Bit is set                     | :     | '0' = Bit is cle | ared              | x = Bit is unkr | nown           |

|              |           |                                      |       |                  |                   |                 |                |

| bit 15       | Unimpleme | nted: Read as '                      | 0'    |                  |                   |                 |                |

| bit 14-8     |           | 6:0>: Assign PV<br>1-2 for input pin |       | •                | on Input 1 to the | e Corresponding | g RPn Pin bits |

|              | 1111001 = | Input tied to RP                     | 1121  |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              |           | Input tied to CM                     | P1    |                  |                   |                 |                |

|              |           | Input tied to Vss                    |       |                  |                   |                 |                |

| bit 7-0      |           | nted: Read as '                      |       |                  |                   |                 |                |

|              |           |                                      | -     |                  |                   |                 |                |

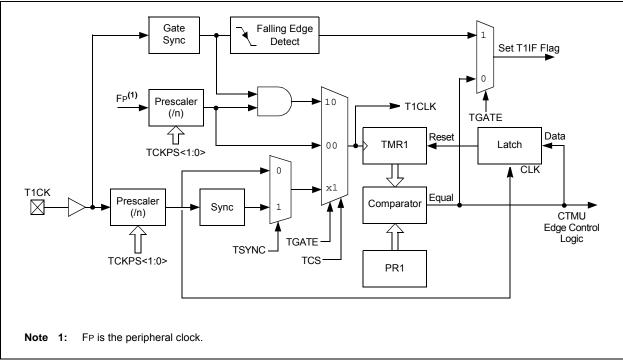

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | x     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### TABLE 12-1: TIMER MODE SETTINGS

# FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- 11001 = CMP2 module synchronizes or triggers  $ICx^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

| U-0                     | U-0                                  | U-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |  |

|-------------------------|--------------------------------------|------------------------------------|---------|------------------|-----------------|------------------|---------|--|--|

| _                       | _                                    |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1          | FILHIT0 |  |  |

| bit 15                  | <b>I</b>                             |                                    |         |                  |                 |                  | bit 8   |  |  |

|                         |                                      |                                    |         |                  |                 |                  |         |  |  |

| U-0                     | R-1                                  | R-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |  |

| _                       | ICODE6                               | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1           | ICODE0  |  |  |

| bit 7                   |                                      |                                    |         |                  |                 |                  | bit     |  |  |

| Logondi                 |                                      |                                    |         |                  |                 |                  |         |  |  |

| Legend:<br>R = Readable | - hit                                | W = Writable                       | hit     | LI – Unimplor    | mented bit, rea | d as '0'         |         |  |  |

| -n = Value at           |                                      | '1' = Bit is set                   |         | '0' = Bit is cle |                 | x = Bit is unkr  |         |  |  |

|                         | FUR                                  |                                    |         |                  | aleu            | x – Dit is uliki |         |  |  |

| bit 15-13               | Unimplemen                           | ted: Read as '                     | 0'      |                  |                 |                  |         |  |  |

| bit 12-8                | =                                    | Filter Hit Num                     |         |                  |                 |                  |         |  |  |

|                         |                                      | 1 = Reserved                       |         |                  |                 |                  |         |  |  |

|                         | 01111 <b>= Filte</b>                 | er 15                              |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | 00001 = Filter 1<br>00000 = Filter 0 |                                    |         |                  |                 |                  |         |  |  |

| bit 7                   | Unimplemented: Read as '0'           |                                    |         |                  |                 |                  |         |  |  |

| bit 6-0                 | ICODE<6:0>: Interrupt Flag Code bits |                                    |         |                  |                 |                  |         |  |  |

|                         | 1000101-1111111 = Reserved           |                                    |         |                  |                 |                  |         |  |  |

|                         |                                      | IFO almost full                    |         |                  |                 |                  |         |  |  |

|                         |                                      | leceiver overflo                   |         |                  |                 |                  |         |  |  |

|                         | 1000010 = K<br>1000001 = E           | Vake-up interru<br>rror interrupt  | μ       |                  |                 |                  |         |  |  |

|                         | 1000000 = N                          |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                  |         |  |  |

|                         | •                                    | B15 buffer inte                    | inupt   |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | 0001001 <b>= R</b>                   | B9 buffer inter                    | rupt    |                  |                 |                  |         |  |  |

|                         |                                      | B8 buffer inter                    |         |                  |                 |                  |         |  |  |

|                         |                                      | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                  |         |  |  |

|                         |                                      | RB5 buffer inte                    |         |                  |                 |                  |         |  |  |

|                         |                                      | RB4 buffer inte                    |         |                  |                 |                  |         |  |  |

|                         | 0000011 <b>= T</b>                   | RB3 buffer inte                    | errupt  |                  |                 |                  |         |  |  |

|                         |                                      |                                    |         |                  |                 |                  |         |  |  |

|                         |                                      | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                  |         |  |  |

# REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-x        | R/W-x                                           | R/W-x                | R/W-x         | R/W-x                                 | R/W-x | R/W-x | R/W-x |  |  |

|--------------|-------------------------------------------------|----------------------|---------------|---------------------------------------|-------|-------|-------|--|--|

| EID5         | EID4                                            | EID3                 | EID2          | EID1                                  | EID0  | RTR   | RB1   |  |  |

| bit 15       |                                                 |                      |               |                                       |       |       | bit 8 |  |  |

|              |                                                 |                      |               |                                       |       |       |       |  |  |

| U-x          | U-x                                             | U-x                  | R/W-x         | R/W-x                                 | R/W-x | R/W-x | R/W-x |  |  |

| —            | —                                               | —                    | RB0           | DLC3                                  | DLC2  | DLC1  | DLC0  |  |  |

| bit 7        |                                                 |                      |               |                                       |       |       | bit 0 |  |  |

|              |                                                 |                      |               |                                       |       |       |       |  |  |

| Legend:      |                                                 |                      |               |                                       |       |       |       |  |  |

| R = Readab   | le bit                                          | W = Writable         | bit           | U = Unimplemented bit, read as '0'    |       |       |       |  |  |

| -n = Value a | t POR                                           | '1' = Bit is set     |               | '0' = Bit is cleared x = Bit is unkno |       |       | nown  |  |  |

|              |                                                 |                      |               |                                       |       |       |       |  |  |

| bit 15-10    | EID<5:0>: E                                     | xtended Identifi     | er bits       |                                       |       |       |       |  |  |

| bit 9        | RTR: Remote Transmission Request bit            |                      |               |                                       |       |       |       |  |  |

|              | <u>When IDE = 1:</u>                            |                      |               |                                       |       |       |       |  |  |

|              | 1 = Message will request remote transmission    |                      |               |                                       |       |       |       |  |  |

|              | 0 = Normal message                              |                      |               |                                       |       |       |       |  |  |

|              | <u>When IDE = 0:</u><br>The RTR bit is ignored. |                      |               |                                       |       |       |       |  |  |

| bit 8        | RB1: Reserved Bit 1                             |                      |               |                                       |       |       |       |  |  |

|              | User must set this bit to '0' per CAN protocol. |                      |               |                                       |       |       |       |  |  |

| bit 7-5      |                                                 | nted: Read as '      | •             |                                       |       |       |       |  |  |

| bit 4        | RB0: Reserv                                     |                      | -             |                                       |       |       |       |  |  |

|              |                                                 | et this bit to '0' p | per CAN proto | ocol.                                 |       |       |       |  |  |

| hit 2 0      |                                                 |                      |               |                                       |       |       |       |  |  |

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

## BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

|-------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|

|                   |       |                  | Ву    | /te 1                              |       |                    |       |  |

| bit 15            |       |                  |       |                                    |       |                    | bit 8 |  |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

|                   |       |                  | Ву    | rte 0                              |       |                    |       |  |

| bit 7             |       |                  |       |                                    |       |                    | bit 0 |  |

| Legend:           |       |                  |       |                                    |       |                    |       |  |

| R = Readable      | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

# 24.3 PTG Control Registers

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0        | U-0     | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0                  |  |

|--------------|---------|---------|---------|-----|-----------------------|------------------------|------------------------|--|

| PTGEN        | —       | PTGSIDL | PTGTOGL | —   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS                |  |

| bit 15 bit 8 |         |         |         |     |                       |                        |                        |  |

|              |         |         |         |     |                       |                        |                        |  |

| R/W-0        | HS-0    | U-0     | U-0     | U-0 | U-0                   | R/W-0                  |                        |  |

| PTGSTRT      | PTGWDTO | _       | _       | _   | _                     | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |  |

| bit 7 |

|-------|

|-------|

| Legend: HS = Hardware Settable bit |                  | t                           |                    |

|------------------------------------|------------------|-----------------------------|--------------------|

| R = Readable bit                   | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR                  | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  |    | PTGEN: Module Enable bit                                                                                                                                                                                                      |

|---------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |    | 1 = PTG module is enabled                                                                                                                                                                                                     |

|         |    | 0 = PTG module is disabled                                                                                                                                                                                                    |

| bit 14  |    | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 13  |    | PTGSIDL: PTG Stop in Idle Mode bit                                                                                                                                                                                            |

|         |    | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                       |

| bit 12  |    | PTGTOGL: PTG TRIG Output Toggle Mode bit                                                                                                                                                                                      |

|         |    | <ul> <li>1 = Toggle state of the PTGOx for each execution of the PTGTRIG command</li> <li>0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits</li> </ul> |

| bit 11  |    | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 10  |    | PTGSWT: PTG Software Trigger bit <sup>(2)</sup>                                                                                                                                                                               |

|         |    | 1 = Triggers the PTG module                                                                                                                                                                                                   |

|         |    | 0 = No action (clearing this bit will have no effect)                                                                                                                                                                         |

| bit 9   |    | PTGSSEN: PTG Enable Single-Step bit <sup>(3)</sup>                                                                                                                                                                            |

|         |    | 1 = Enables Single-Step mode                                                                                                                                                                                                  |

|         |    | 0 = Disables Single-Step mode                                                                                                                                                                                                 |

| bit 8   |    | PTGIVIS: PTG Counter/Timer Visibility Control bit                                                                                                                                                                             |

|         |    | 1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their<br>corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)                                                                   |

|         |    | <ul> <li>Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written<br/>to those limit registers</li> </ul>                                                                                    |

| bit 7   |    | PTGSTRT: PTG Start Sequencer bit                                                                                                                                                                                              |

|         |    | <ul><li>1 = Starts to sequentially execute commands (Continuous mode)</li><li>0 = Stops executing commands</li></ul>                                                                                                          |

| bit 6   |    | PTGWDTO: PTG Watchdog Timer Time-out Status bit                                                                                                                                                                               |

|         |    | 1 = PTG Watchdog Timer has timed out                                                                                                                                                                                          |

|         |    | 0 = PTG Watchdog Timer has not timed out.                                                                                                                                                                                     |

| bit 5-2 |    | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| Note    | 1: | These bits apply to the PTGWHI and PTGWLO commands only.                                                                                                                                                                      |

|         | 2: | This bit is only used with the PTGCTRL step command software trigger option.                                                                                                                                                  |

3: Use of the PTG Single-Step mode is reserved for debugging tools only.

bit 0

## 25.3 Op Amp/Comparator Registers

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0             | U-0                          | R-0                  | R-0                  | R-0                  | R-0                  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|

| PSIDL         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _               | _                            | C4EVT <sup>(1)</sup> | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 | •                            |                      |                      |                      | bit                  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                              |                      |                      |                      |                      |  |  |  |

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0             | U-0                          | R-0                  | R-0                  | R-0                  | R-0                  |  |  |  |

| _             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _               | _                            | C4OUT <sup>(2)</sup> | C3OUT <sup>(2)</sup> | C2OUT <sup>(2)</sup> | C10UT <sup>(2)</sup> |  |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                              |                      |                      |                      | bit                  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                              |                      |                      |                      |                      |  |  |  |

| Legend:       | - 1-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | L:4                          |                      |                      |                      |                      |  |  |  |