Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc204-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

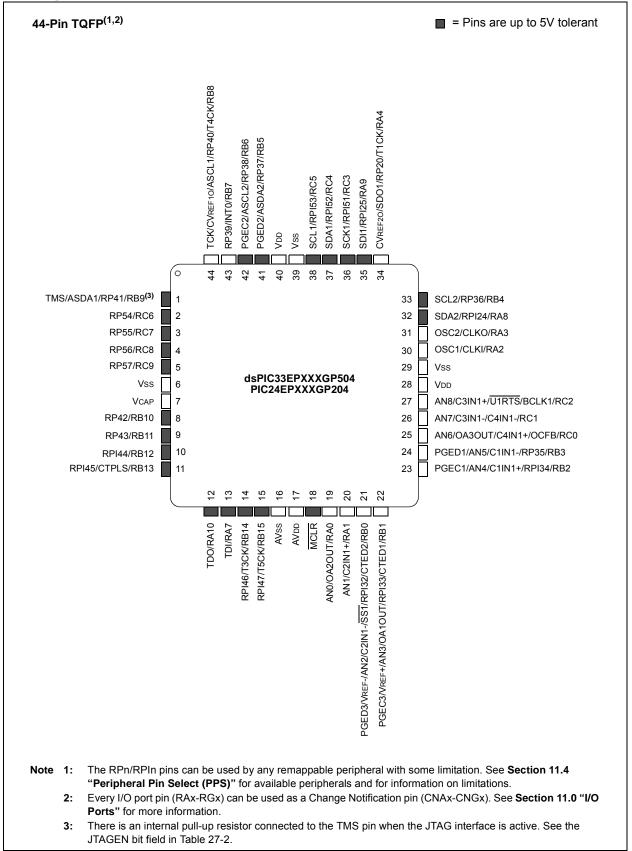

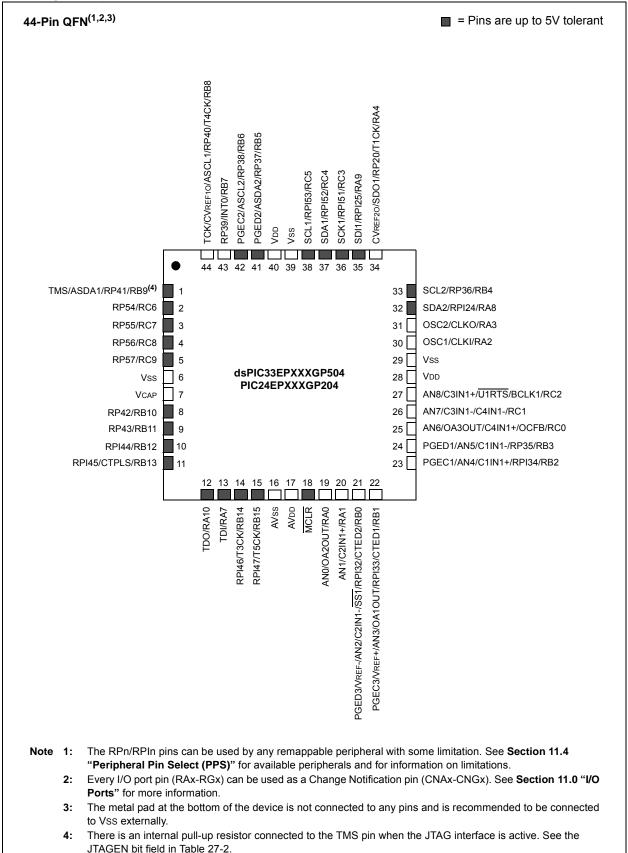

## **Pin Diagrams (Continued)**

### **Pin Diagrams (Continued)**

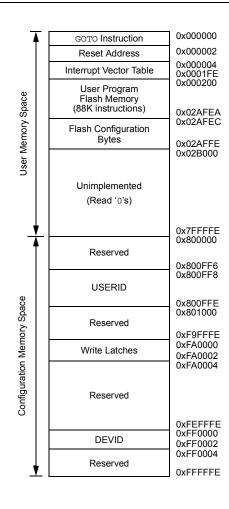

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

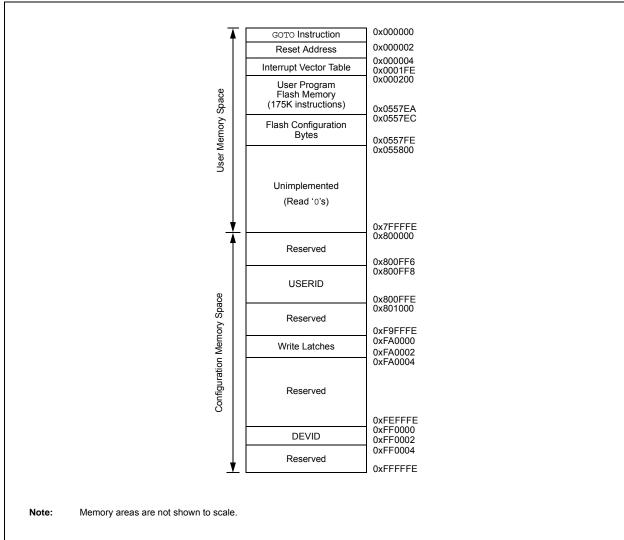

Note: Memory areas are not shown to scale.

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

# 4.4 Special Function Register Maps

# TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00   |        |        |              | 011 401    |        |       | 20/00/      |        |       |        |         |          |          | -     | r     |               |

|-----------|-------|--------|--------|--------|--------------|------------|--------|-------|-------------|--------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8       | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |        |        |        |              |            |        |       | W0 (WR      | EG)    |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |        |        |        |              |            |        |       | W1          |        |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |        |        |        |              |            |        |       | W2          |        |       |        |         |          |          |       |       | xxxx          |

| W3        | 0006  |        |        |        |              |            |        |       | W3          |        |       |        |         |          |          |       |       | xxxx          |

| W4        | 8000  |        |        |        |              |            |        |       | W4          |        |       |        |         |          |          |       |       | xxxx          |

| W5        | 000A  |        |        |        |              |            |        |       | W5          |        |       |        |         |          |          |       |       | xxxx          |

| W6        | 000C  |        |        |        |              |            |        |       | W6          |        |       |        |         |          |          |       |       | xxxx          |

| W7        | 000E  |        |        |        |              |            |        |       | W7          |        |       |        |         |          |          |       |       | xxxx          |

| W8        | 0010  |        |        |        |              |            |        |       | W8          |        |       |        |         |          |          |       |       | xxxx          |

| W9        | 0012  |        |        |        |              |            |        |       | W9          |        |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |        |        |        |              |            |        |       | W10         |        |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |        |        |        |              |            |        |       | W11         |        |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |        |        |        |              |            |        |       | W12         |        |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |        |        |        |              |            |        |       | W13         |        |       |        |         |          |          |       |       | xxxx          |

| W14       | 001C  |        |        |        |              |            |        |       | W14         |        |       |        |         |          |          |       |       | xxxx          |

| W15       | 001E  |        |        |        |              |            |        |       | W15         |        |       |        |         |          |          |       |       | xxxx          |

| SPLIM     | 0020  |        |        |        |              |            |        |       | SPLI        | N      |       |        |         |          |          |       |       | 0000          |

| ACCAL     | 0022  |        |        |        |              |            |        |       | ACCA        | L      |       |        |         |          |          |       |       | 0000          |

| ACCAH     | 0024  |        |        |        |              |            |        |       | ACCA        | H      |       |        |         |          |          |       |       | 0000          |

| ACCAU     | 0026  |        |        | Si     | gn Extensior | n of ACCA< | 39>    |       |             |        |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |        |        |        |              |            |        |       | ACCB        | L      |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |        |        |        |              |            |        |       | ACCB        | Н      |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |        |        | Si     | gn Extensior | n of ACCB< | 39>    |       |             |        |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |        |        |        |              |            |        | F     | PCL<15:0>   |        |       |        |         |          |          |       | —     | 0000          |

| PCH       | 0030  | _      | _      | _      | —            | _          | _      | —     | _           | _      |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _      | _      | _      | _            | _          | _      |       |             |        |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _      |        | _      | —            |            | _      | _     |             |        |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |        |        |        |              |            |        |       | RCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DCOUNT    | 0038  |        |        |        |              |            |        |       | DCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DOSTARTL  | 003A  |        |        |        |              |            |        | DOS   | STARTL<15:1 | >      |       |        |         |          |          |       |       | 0000          |

| DOSTARTH  | 003C  | _      | —      | —      | _            | —          | —      | —     | _           | _      | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  |        |        |        |              |            |        | DO    | ENDL<15:1>  | >      |       |        |         |          |          |       |       | 0000          |

| DOENDH    | 0040  | _      | —      | —      | —            | —          | —      | _     | —           | —      | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |        |        |        |              |            |        |       |             |        |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | U-0                                                                                                                              | U-0                               | U-0                      | U-0                         | U-0  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|-----------------------------|------|

|                                              | _                                                                                                                                                                            | _                                                                                                                                                                                                                            | _                                                                                                                                | _                                 | _                        | _                           | _    |

| bit 15                                       |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |

|                                              |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             |      |

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | R/W-0                                                                                                                            | R/W-0                             | U-0                      | U-0                         | U-0  |

| _                                            | -                                                                                                                                                                            | _                                                                                                                                                                                                                            | DMA0MD <sup>(1)</sup><br>DMA1MD <sup>(1)</sup><br>DMA2MD <sup>(1)</sup><br>DMA3MD <sup>(1)</sup>                                 | PTGMD                             | _                        | _                           | _    |

| bit 7                                        |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |

| <b>Legend:</b><br>R = Readab<br>-n = Value a |                                                                                                                                                                              | W = Writable<br>'1' = Bit is set                                                                                                                                                                                             |                                                                                                                                  | U = Unimplen<br>'0' = Bit is clea | nented bit, read<br>ared | l as '0'<br>x = Bit is unkn | iown |

| bit 15-5<br>bit 4                            | DMA0MD: DM<br>1 = DMA0 mo<br>0 = DMA0 mo<br>DMA1MD: DM<br>1 = DMA1 mo<br>0 = DMA1 mo<br>DMA2MD: DM<br>1 = DMA2 mo<br>0 = DMA2 mo<br>DMA3MD: DM<br>1 = DMA3 mo<br>0 = DMA3 mo | ted: Read as '<br>MA0 Module Di<br>odule is disable<br>odule is enable<br>MA1 Module Di<br>odule is disable<br>MA2 Module Di<br>odule is disable<br>odule is enable<br>MA3 Module Di<br>odule is disable<br>odule is disable | sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d |                                   |                          |                             |      |

| bit 3                                        |                                                                                                                                                                              | Module Disat<br>ule is disabled<br>ule is enabled                                                                                                                                                                            | ole bit                                                                                                                          |                                   |                          |                             |      |

| bit 2-0                                      | Unimplement                                                                                                                                                                  | ted: Read as '                                                                                                                                                                                                               | 0'                                                                                                                               |                                   |                          |                             |      |

| Note 1: T                                    | his single bit ena                                                                                                                                                           | ables and disal                                                                                                                                                                                                              | oles all four DM                                                                                                                 | A channels.                       |                          |                             |      |

## REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

## REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0       | >               |                 |        |

| bit 15       |              |                                                        |               |                  |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0           | 5444.0          |                 | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>      | >               |                 |        |

| bit 7        |              |                                                        |               |                  |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                  |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                  |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                  |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                  |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                  |                 |                 |        |

# 12.2 Timer1 Control Register

| R/W-0              | U-0                                  | R/W-0                             | U-0                       | U-0              | U-0                      | U-0              | U-0                |

|--------------------|--------------------------------------|-----------------------------------|---------------------------|------------------|--------------------------|------------------|--------------------|

| TON <sup>(1)</sup> | —                                    | TSIDL                             | —                         | _                | —                        | _                | _                  |

| bit 15             |                                      |                                   |                           |                  |                          |                  | bit 8              |

|                    |                                      |                                   |                           |                  |                          |                  |                    |

| U-0                | R/W-0                                | R/W-0<br>TCKPS1                   | R/W-0<br>TCKPS0           | U-0              | R/W-0                    | R/W-0            | U-0                |

|                    | TGATE                                | TSYNC <sup>(1)</sup>              | TCS <sup>(1)</sup>        |                  |                          |                  |                    |

| bit 7              |                                      |                                   |                           |                  |                          |                  | bit (              |

| Legend:            |                                      |                                   |                           |                  |                          |                  |                    |

| R = Readable       | e bit                                | W = Writable                      | bit                       | U = Unimplei     | mented bit, read         | l as '0'         |                    |

| -n = Value at      | POR                                  | '1' = Bit is set                  |                           | '0' = Bit is cle | ared                     | x = Bit is unkno | own                |

|                    |                                      | o                                 |                           |                  |                          |                  |                    |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16- |                                   |                           |                  |                          |                  |                    |

|                    | 0 = Stops 16-                        |                                   |                           |                  |                          |                  |                    |

| bit 14             | Unimplemen                           | ted: Read as '                    | 0'                        |                  |                          |                  |                    |

| bit 13             | TSIDL: Timer                         | 1 Stop in Idle N                  | /lode bit                 |                  |                          |                  |                    |

|                    |                                      | ues module op                     |                           |                  | ldle mode                |                  |                    |

|                    |                                      | s module opera                    |                           | ode              |                          |                  |                    |

| bit 12-7           | -                                    | ted: Read as '                    |                           |                  |                          |                  |                    |

| bit 6              |                                      | r1 Gated Time                     | Accumulation              | h Enable bit     |                          |                  |                    |

|                    | When TCS =<br>This bit is igno       |                                   |                           |                  |                          |                  |                    |

|                    | When TCS =                           |                                   |                           |                  |                          |                  |                    |

|                    |                                      | e accumulatio                     |                           |                  |                          |                  |                    |

|                    |                                      | e accumulatio                     |                           | 0.1.1.1.1.1      |                          |                  |                    |

| bit 5-4            |                                      | : Timer1 Input                    | Clock Prescal             | e Select bits    |                          |                  |                    |

|                    | 11 = 1:256<br>10 = 1:64              |                                   |                           |                  |                          |                  |                    |

|                    | 01 = 1:8                             |                                   |                           |                  |                          |                  |                    |

|                    | 00 = 1:1                             |                                   |                           |                  |                          |                  |                    |

| bit 3              | -                                    | ted: Read as '                    |                           |                  |                          |                  |                    |

| bit 2              |                                      | er1 External Clo                  | ock Input Synd            | chronization S   | elect bit <sup>(1)</sup> |                  |                    |

|                    | When TCS =                           |                                   |                           |                  |                          |                  |                    |

|                    |                                      | izes external c<br>synchronize e> |                           | nut              |                          |                  |                    |

|                    | When TCS =                           | •                                 |                           | iput             |                          |                  |                    |

|                    | This bit is ign                      |                                   |                           |                  |                          |                  |                    |

| bit 1              | TCS: Timer1                          | Clock Source S                    | Select bit <sup>(1)</sup> |                  |                          |                  |                    |

|                    | 1 = External c<br>0 = Internal cl    | clock is from pi<br>ock (FP)      | n, T1CK (on th            | ne rising edge)  | •                        |                  |                    |

| bit 0              | Unimplemen                           | ted: Read as '                    | 0'                        |                  |                          |                  |                    |

|                    | nen Timer1 is er<br>empts by user s  |                                   |                           |                  |                          | SYNC = 1, TON    | <b>\ =</b> 1), any |

## REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

© 2011-2013 Microchip Technology Inc.

| R/W-0        | R/W-0             | R/W-0                                  | R/W-0          | U-0               | U-0                 | U-0              | U-0          |

|--------------|-------------------|----------------------------------------|----------------|-------------------|---------------------|------------------|--------------|

|              | TRGD              | V<3:0>                                 |                | —                 |                     | —                | _            |

| bit 15       |                   |                                        |                |                   |                     |                  | bit 8        |

|              |                   |                                        |                |                   |                     |                  |              |

| U-0          | U-0               | R/W-0                                  | R/W-0          | R/W-0             | R/W-0               | R/W-0            | R/W-0        |

| _            |                   |                                        |                | TRGSTF            | RT<5:0> <b>(1)</b>  |                  |              |

| bit 7        |                   |                                        |                |                   |                     |                  | bit          |

|              |                   |                                        |                |                   |                     |                  |              |

| Legend:      | 1. 1.4            |                                        |                |                   |                     |                  |              |

| R = Readab   |                   | W = Writable                           |                | •                 | nented bit, read    |                  |              |

| -n = Value a | t POR             | '1' = Bit is set                       |                | '0' = Bit is clea | ared                | x = Bit is unkn  | own          |

|              |                   |                                        |                |                   |                     |                  |              |

| bit 15-12    |                   | <b>)&gt;:</b> Trigger # Ou             | -              |                   |                     |                  |              |

|              |                   | per output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev<br>ger output for ev |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | per output for ev                      |                |                   |                     |                  |              |

|              |                   | per output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              | 0100 = Trigg      | ger output for ev                      | ery 5th trigge | r event           |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              | 0000 = Trigg      | ger output for ev                      | ery trigger ev | ent               |                     |                  |              |

| bit 11-6     | -                 | nted: Read as '                        |                |                   |                     |                  |              |

| bit 5-0      | TRGSTRT<          | 5:0>: Trigger Po                       | stscaler Start | Enable Select     | bits <sup>(1)</sup> |                  |              |

|              | 111111 <b>=</b> W | aits 63 PWM cy                         | cles before g  | enerating the fir | st trigger event    | after the modu   | le is enable |

|              |                   |                                        |                |                   |                     |                  |              |

|              | •                 |                                        |                | ·                 |                     |                  |              |

|              | •                 |                                        |                | -                 |                     |                  |              |

|              | •                 |                                        |                | -                 |                     |                  |              |

|              | •<br>•<br>•       | aits 2 PW/M ava                        | les hefore co  | nerating the fire | t trigger event :   | after the module | a is anabled |

|              |                   | /aits 2 PWM cyc<br>/aits 1 PWM cyc     |                |                   |                     |                  |              |

# REGISTER 16-12: TRGCONx: PWMx TRIGGER CONTROL REGISTER

### REGISTER 17-13: QEI1LECH: QEI1 LESS THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0                                                   | R/W-0 | R/W-0          | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|---------------------------------------------------------|-------|----------------|-------|------------------------------------|-------|-----------------|-------|--|--|

|                                                         |       |                | QEILE | C<31:24>                           |       |                 |       |  |  |

| bit 15                                                  |       |                |       |                                    |       |                 | bit 8 |  |  |

|                                                         |       |                |       |                                    |       |                 |       |  |  |

| R/W-0                                                   | R/W-0 | R/W-0          | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|                                                         |       |                | QEILE | C<23:16>                           |       |                 |       |  |  |

| bit 7                                                   |       |                |       |                                    |       |                 | bit 0 |  |  |

|                                                         |       |                |       |                                    |       |                 |       |  |  |

| Legend:                                                 |       |                |       |                                    |       |                 |       |  |  |

| R = Readable                                            | bit   | W = Writable b | bit   | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |       |                |       |                                    | red   | x = Bit is unkr | nown  |  |  |

bit 15-0 QEILEC<31:16>: High Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

# REGISTER 17-14: QEI1LECL: QEI1 LESS THAN OR EQUAL COMPARE LOW WORD REGISTER

| R = Readable bitW = Writable bit-n = Value at POR'1' = Bit is set |       |       | U = Unimplen<br>'0' = Bit is cle |          | ad as '0'<br>x = Bit is unknown |       |       |

|-------------------------------------------------------------------|-------|-------|----------------------------------|----------|---------------------------------|-------|-------|

| Legend:                                                           |       |       |                                  |          |                                 |       |       |

|                                                                   |       |       |                                  |          |                                 |       |       |

| bit 7                                                             |       |       |                                  |          |                                 |       | bit   |

|                                                                   |       |       | QEIL                             | EC<7:0>  |                                 |       |       |

| R/W-0                                                             | R/W-0 | R/W-0 | R/W-0                            | R/W-0    | R/W-0                           | R/W-0 | R/W-0 |

| bit 15                                                            |       |       |                                  |          |                                 |       | bit   |

|                                                                   |       |       | QEILE                            | EC<15:8> |                                 |       |       |

| R/W-0                                                             | R/W-0 | R/W-0 | R/W-0                            | R/W-0    | R/W-0                           | R/W-0 | R/W-0 |

bit 15-0 QEILEC<15:0>: Low Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

| R/W-0                             | R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 |  |  |  |

|-----------------------------------|------------------------------------|-------|-------|------------------------------------|-----------------------------------------|-------|-------|--|--|--|

|                                   |                                    |       | INTHL | D<31:24>                           |                                         |       |       |  |  |  |

| bit 15                            |                                    |       |       |                                    |                                         |       | bit 8 |  |  |  |

|                                   |                                    |       |       |                                    |                                         |       |       |  |  |  |

| R/W-0                             | R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 |  |  |  |

|                                   |                                    |       | INTHL | D<23:16>                           |                                         |       |       |  |  |  |

| bit 7                             |                                    |       |       |                                    |                                         |       | bit 0 |  |  |  |

|                                   |                                    |       |       |                                    |                                         |       |       |  |  |  |

| Legend:                           |                                    |       |       |                                    |                                         |       |       |  |  |  |

| R = Readable bit W = Writable bit |                                    |       |       | U = Unimplemented bit, read as '0' |                                         |       |       |  |  |  |

| -n = Value at P                   | -n = Value at POR '1' = Bit is set |       |       |                                    | '0' = Bit is cleared x = Bit is unknown |       |       |  |  |  |

bit 15-0 INTHLD<31:16>: Hold Register for Reading and Writing INT1TMRH bits

## REGISTER 17-20: INT1HLDL: INTERVAL 1 TIMER HOLD LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|--|

|                                    |       |       | INTHL | .D<15:8>                                |       |       |       |  |  |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |  |  |

|                                    |       |       |       |                                         |       |       |       |  |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                    |       |       | INTH  | _D<7:0>                                 |       |       |       |  |  |

| bit 7                              |       |       |       |                                         |       |       | bit 0 |  |  |

|                                    |       |       |       |                                         |       |       |       |  |  |

| Legend:                            |       |       |       |                                         |       |       |       |  |  |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

|                                    |       |       |       |                                         |       |       |       |  |  |

bit 15-0 INTHLD<15:0>: Hold Register for Reading and Writing INT1TMRL bits

| U-0                     | U-0                                  | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

|-------------------------|--------------------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|--|--|--|

| _                       | _                                    |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |  |

| bit 15                  | <b>I</b>                             | •                                  |         |                  |                 |                 | bit 8   |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |

| U-0                     | R-1                                  | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

| _                       | ICODE6                               | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |  |  |  |

| bit 7                   |                                      |                                    |         |                  |                 |                 | bit     |  |  |  |

| Logondi                 |                                      |                                    |         |                  |                 |                 |         |  |  |  |

| Legend:<br>R = Readable | - hit                                |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |  |  |  |

| -n = Value at           |                                      | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |  |  |  |

| -n = value at           | POR                                  | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |  |  |  |

| bit 15-13               | Unimplemen                           | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 12-8                | =                                    | Filter Hit Num                     |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 1 = Reserved                       |         |                  |                 |                 |         |  |  |  |

|                         | 01111 <b>= Filte</b>                 | r 15                               |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | - 1                                |         |                  |                 |                 |         |  |  |  |

|                         | 00001 = Filte<br>00000 = Filte       |                                    |         |                  |                 |                 |         |  |  |  |

| bit 7                   |                                      | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 6-0                 | ICODE<6:0>: Interrupt Flag Code bits |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |

|                         |                                      | IFO almost full                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | eceiver overflo                    |         |                  |                 |                 |         |  |  |  |

|                         | 1000010 = K<br>1000001 = E           | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |  |  |  |

|                         | 1000000 = N                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |

|                         | •                                    | B15 buffer inte                    | inupt   |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 0001001 <b>= R</b>                   | B9 buffer inter                    | rupt    |                  |                 |                 |         |  |  |  |

|                         |                                      | B8 buffer inter                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB5 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB4 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         | 0000011 <b>= T</b>                   | RB3 buffer inte                    | errupt  |                  |                 |                 |         |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |  |  |  |

## REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

NOTES:

# 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

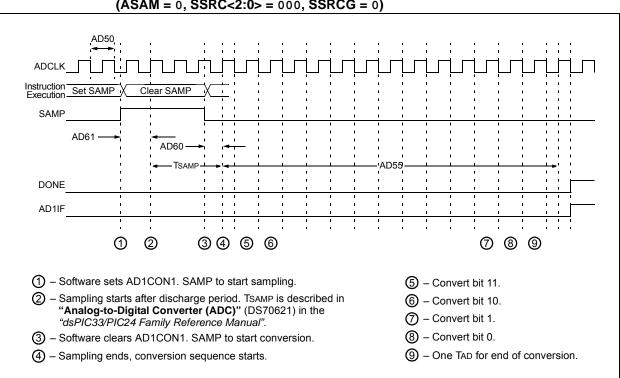

# 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

# 23.1 Key Features

## 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

### 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

# 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

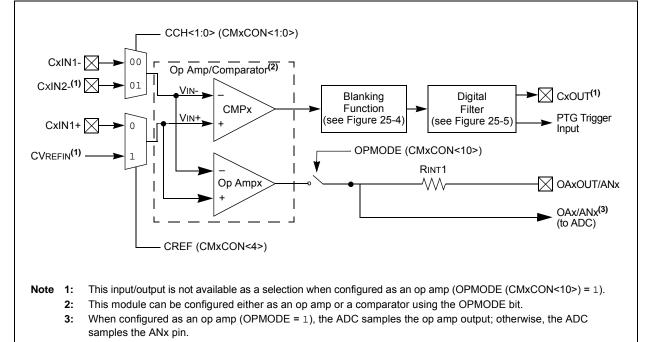

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

## FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

| AC CHARACTERISTICS |           |                                                              |                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |               |       |                                                                               |

|--------------------|-----------|--------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|-------------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                |                     | Min.                                                                                                                                                                                                                                                                              | Тур. | Max.          | Units | Conditions                                                                    |

| TB10               | TtxH      | TxCK High<br>Time                                            | Synchronous<br>mode | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                              | _    | _             | ns    | Must also meet<br>Parameter TB15,<br>N = prescale<br>value<br>(1, 8, 64, 256) |

| TB11               | TtxL      | TxCK Low<br>Time                                             | Synchronous<br>mode | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                              | _    |               | ns    | Must also meet<br>Parameter TB15,<br>N = prescale<br>value<br>(1, 8, 64, 256) |

| TB15               | TtxP      | TxCK<br>Input<br>Period                                      | Synchronous<br>mode | Greater of:<br>40 or<br>(2 Tcy + 40)/N                                                                                                                                                                                                                                            | —    | —             | ns    | N = prescale<br>value<br>(1, 8, 64, 256)                                      |

| TB20               | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                     | 0.75 Tcy + 40                                                                                                                                                                                                                                                                     | —    | 1.75 Tcy + 40 | ns    |                                                                               |

| TABLE 30-24: | TIMER2 AND TIM | IER4 (TYPE B TIMER | R) EXTERNAL CLOCK TIMING REQ | UIREMENTS |

|--------------|----------------|--------------------|------------------------------|-----------|

|--------------|----------------|--------------------|------------------------------|-----------|

Note 1: These parameters are characterized, but are not tested in manufacturing.

## TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                              |                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |               |       |                                          |

|--------------------|-----------|--------------------------------------------------------------|-----------------------------|-------------------------------------------------------|------|---------------|-------|------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                |                             | Min.                                                  | Тур. | Max.          | Units | Conditions                               |

| TC10               | TtxH      | TxCK High<br>Time                                            | Synchronous                 | Tcy + 20                                              |      |               | ns    | Must also meet<br>Parameter TC15         |

| TC11               | TtxL      | TxCK Low<br>Time                                             | Synchronous                 | Тсү + 20                                              | _    | —             | ns    | Must also meet<br>Parameter TC15         |

| TC15               | TtxP      | TxCK Input<br>Period                                         | Synchronous, with prescaler | 2 Tcy + 40                                            | —    | _             | ns    | N = prescale<br>value<br>(1, 8, 64, 256) |

| TC20               | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                             | 0.75 Tcy + 40                                         | _    | 1.75 Tcy + 40 | ns    |                                          |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

#### FIGURE 30-36: ADC CONVERSION (12-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000, SSRCG = 0)

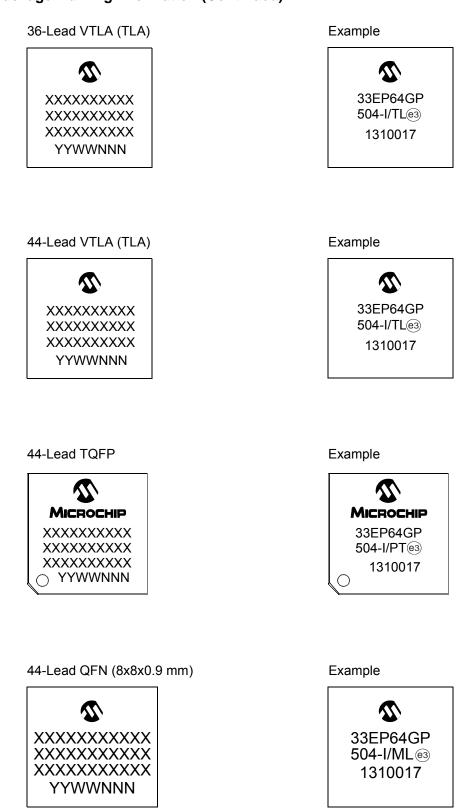

#### 33.1 Package Marking Information (Continued)