Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

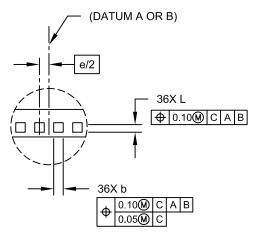

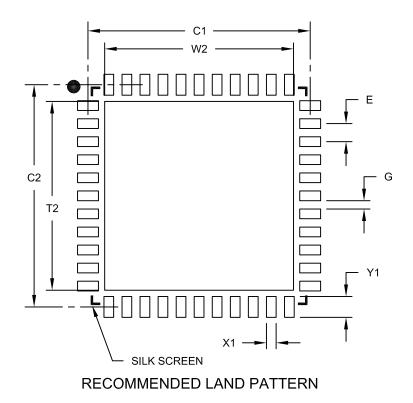

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc204-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0               | U-0                          | R/W-0                                                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |  |  |  |  |

|---------------------|------------------------------|------------------------------------------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|--|--|--|--|

| VAR                 | —                            | US1 <sup>(1)</sup>                                                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |  |  |  |  |

| bit 15              |                              |                                                                                          |                         |                             |                           |                    | bit                |  |  |  |  |

| R/W-0               | R/W-0                        | R/W-1                                                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |  |  |  |  |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>          | SATDW <sup>(1)</sup>                                                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |  |  |  |  |

| bit 7               | I                            |                                                                                          |                         |                             | I                         | 1                  | bit                |  |  |  |  |

| Legend:             |                              | C = Clearable                                                                            | e bit                   |                             |                           |                    |                    |  |  |  |  |

| R = Readabl         | e bit                        | W = Writable                                                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |  |  |  |  |

| -n = Value at       | POR                          | '1' = Bit is set                                                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |  |  |  |  |

| bit 15              | 1 = Variable                 | le Exception Pro<br>exception proce                                                      | essing latency          | is enabled                  |                           |                    |                    |  |  |  |  |

| bit 14              |                              | nted: Read as '                                                                          |                         |                             |                           |                    |                    |  |  |  |  |

| bit 13-12           | -                            | SP Multiply Uns                                                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |  |  |  |  |

|                     | 01 = DSP er<br>00 = DSP er   | ngine multiplies<br>ngine multiplies<br>ngine multiplies                                 | are unsigned are signed |                             |                           |                    |                    |  |  |  |  |

| bit 11              | •                            | O Loop Terminatives executing Dot<br>t                                                   |                         |                             | iteration                 |                    |                    |  |  |  |  |

| bit 10-8            |                              | DL<2:0>: DO Loop Nesting Level Status bits <sup>(1)</sup><br>111 = 7 DO loops are active |                         |                             |                           |                    |                    |  |  |  |  |

|                     | •                            |                                                                                          |                         |                             |                           |                    |                    |  |  |  |  |

|                     | •                            |                                                                                          |                         |                             |                           |                    |                    |  |  |  |  |

|                     | 001 = 1 DO k<br>000 = 0 DO k | oop is active<br>oops are active                                                         |                         |                             |                           |                    |                    |  |  |  |  |

| bit 7               | SATA: ACCA                   | A Saturation En                                                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |  |  |  |  |

|                     |                              | ator A saturatio<br>ator A saturatio                                                     |                         |                             |                           |                    |                    |  |  |  |  |

| bit 6               | SATB: ACCE                   | B Saturation En                                                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |  |  |  |  |

|                     |                              | ator B saturatio<br>ator B saturatio                                                     |                         |                             |                           |                    |                    |  |  |  |  |

| bit 5               | SATDW: Dat                   | ta Space Write                                                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |  |  |  |  |

|                     |                              | ace write satura<br>ace write satura                                                     |                         | I                           |                           |                    |                    |  |  |  |  |

| bit 4               |                              | cumulator Satu                                                                           |                         | elect bit <sup>(1)</sup>    |                           |                    |                    |  |  |  |  |

|                     |                              | uration (super s<br>uration (normal                                                      | ,                       |                             |                           |                    |                    |  |  |  |  |

| bit 3               |                              | nterrupt Priority                                                                        |                         |                             |                           |                    |                    |  |  |  |  |

|                     |                              | errupt Priority Le<br>errupt Priority Le                                                 |                         |                             |                           |                    |                    |  |  |  |  |

|                     | nis bit is availabl          |                                                                                          | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP                | 50X devices on     | ly.                |  |  |  |  |

| 2: Th               | nis bit is always            | reau as 0.                                                                               |                         |                             |                           |                    |                    |  |  |  |  |

# REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6      | Bit 5       | Bit 4  | Bit 3       | Bit 2        | Bit 1       | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|------------|-------------|--------|-------------|--------------|-------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF      | IC2IF       | DMA0IF | T1IF        | OC1IF        | IC1IF       | <b>INTOIF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _          | _           | INT1IF | CNIF        | CMIF         | MI2C1IF     | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      | _      | _          | _      | —      |        | _          | —      | _     | IC4IF      | IC3IF       | DMA3IF | C1IF        | C1RXIF       | SPI2IF      | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | —      |        | _          | —      | _     | _          | _           | —      | _           | MI2C2IF      | SI2C2IF     | —             | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | —      |        | _          | —      | _     | C1TXIF     | _           | —      | CRCIF       | U2EIF        | U1EIF       | —             | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | —      |        | _          | —      | _     | _          | _           | —      | _           | —            | _           | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | —          | _      | —      |        | _          | —      | _     | _          | _           | —      | _           | —            | _           | —             | 0000          |

| IFS9         | 0812  |        |        | _          | _      | _      | _      | _          | _      | _     | PTG3IF     | PTG2IF      | PTG1IF | PTG0IF      | PTGWDTIF     | PTGSTEPIF   | _             | 0000          |

| IEC0         | 0820  |        | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE      | IC2IE       | DMA0IE | T1IE        | OC1IE        | IC1IE       | INT0IE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _          | _           | INT1IE | CNIE        | CMIE         | MI2C1IE     | SI2C1IE       | 0000          |

| IEC2         | 0824  |        |        | _          | _      | _      | _      | _          | _      | _     | IC4IE      | IC3IE       | DMA3IE | C1IE        | C1RXIE       | SPI2IE      | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | —          | —      |        | _      |            | _      | _     | _          |             |        | —           | MI2C2IE      | SI2C2IE     | _             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | —      |        |        |            | _      | —     | C1TXIE     |             |        | CRCIE       | U2EIE        | U1EIE       |               | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | —          | —      |        | _      |            | _      | _     | _          |             |        | —           | _            | _           | _             | 0000          |

| IEC9         | 0832  | _      | _      | —          | —      |        | _      |            | _      | _     | PTG3IE     | PTG2IE      | PTG1IE | PTG0IE      | PTGWDTIE     | PTGSTEPIE   | _             | 0000          |

| IPC0         | 0840  |        |        | T1IP<2:0>  | >      | _      | (      | OC1IP<2:0  | >      | _     | IC1IP<2:0> |             | _      | INT0IP<2:0> |              | 4444        |               |               |

| IPC1         | 0842  |        |        | T2IP<2:0>  | >      | _      | (      | C2IP<2:0   | >      | _     |            | IC2IP<2:0>  |        | _           | DMA0IP<2:0>  |             | 4444          |               |

| IPC2         | 0844  |        | ι      | J1RXIP<2:0 | 0>     | _      | Ş      | SPI1IP<2:0 | )>     | _     |            | SPI1EIP<2:0 | >      | _           | T3IP<2:0>    |             | 4444          |               |

| IPC3         | 0846  |        |        | _          | _      | _      | C      | MA1IP<2:   | 0>     | _     |            | AD1IP<2:0>  |        | _           | U1TXIP<2:0>  |             |               | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0   | >      | _      |        | CMIP<2:0   | >      | _     | I          | WI2C1IP<2:0 | >      | _           | SI2C1IP<2:0> |             |               | 4444          |

| IPC5         | 084A  |        |        | _          | _      | _      | _      | _          | _      | _     | _          | _           | _      | _           |              | NT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  |        |        | T4IP<2:0>  | >      | _      | (      | C4IP<2:0   | >      | _     |            | OC3IP<2:0>  |        | _           | D            | MA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  |        | ι      | U2TXIP<2:( | )>     | _      | L      | I2RXIP<2:  | 0>     | _     |            | INT2IP<2:0> | •      | _           |              | T5IP<2:0>   |               | 4444          |

| IPC8         | 0850  |        |        | C1IP<2:0>  | >      | _      | C      | 1RXIP<2:   | 0>     | _     |            | SPI2IP<2:0> | •      | _           | S            | PI2EIP<2:0> |               | 4444          |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0  | >      | _     |            | IC3IP<2:0>  |        | _           | D            | MA3IP<2:0>  |               | 0444          |

| IPC11        | 0856  | _      | _      | _          | _      | _      |        | _          | —      | _     | _          | _           | —      | _           | _            | _           | _             | 0000          |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | II2C2IP<2: | 0>     | _     |            | SI2C2IP<2:0 | >      | _           | _            | _           | _             | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | )>     | _      |        | U2EIP<2:0  | >      | _     |            | U1EIP<2:0>  |        | _           | _            | _           | _             | 4440          |

| IPC17        | 0862  | _      | _      | _          | _      | _      | C      | 1TXIP<2:   | )>     | _     | _          | _           | —      | _           | _            | _           | _             | 0400          |

| IPC19        | 0866  | _      | _      | —          | _      | _      |        | _          | —      | _     |            | CTMUIP<2:0  | >      | _           | —            |             |               | 0040          |

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>     | _      |        | ICDIP<2:0  | >      | _     | _          | _           | _      | _           | —            | _           | _             | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:  | 0>     | —      | PT     | GWDTIP<    | 2:0>   | _     | PT         | GSTEPIP<2   | :0>    | _           | _            | _           | _             | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | TG3IP<2:   | )>     | _     |            | PTG2IP<2:0  | >      | _           | Р            | TG1IP<2:0>  |               | 0444          |

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

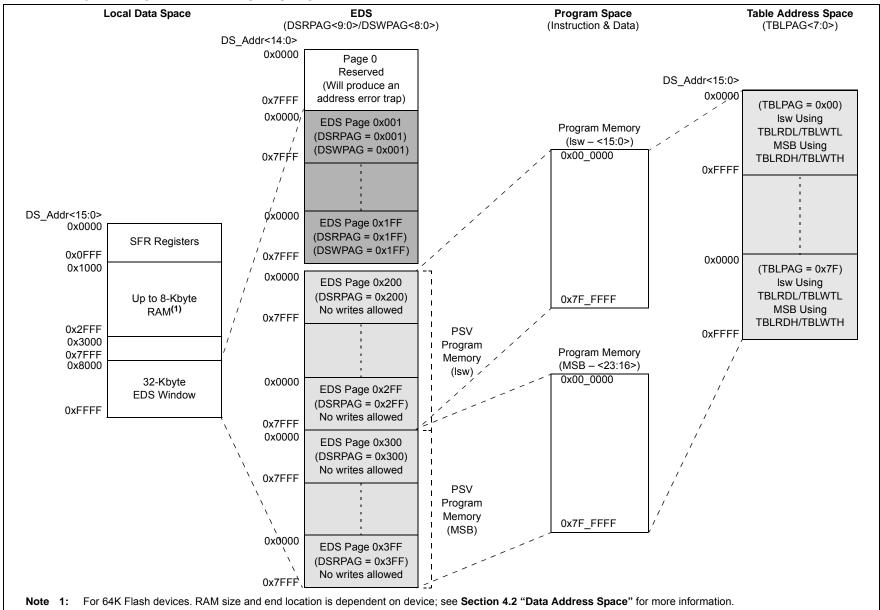

### EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

# 4.7 Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all these conditions are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^{N}$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XBREV<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume    |

|-------|--------------------------------------------|

|       | word-sized data (LSb of every EA is always |

|       | clear). The XBREVx value is scaled         |

|       | accordingly to generate compatible (byte)  |

|       | addresses.                                 |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XBREVx) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing can be enabled simultaneously using the same W register, but Bit-Reversed Addressing operation will always take precedence for data writes when enabled.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

# 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

NOTES:

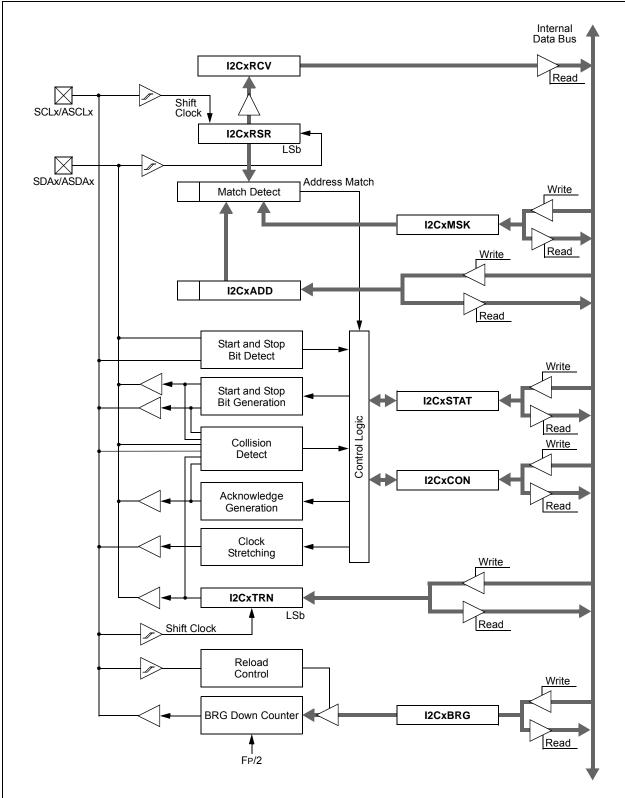

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

## REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| Legend:C = Writable bit, but only '0' can be written to clear the bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |       |       |      |        |        |       |       |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|--------|--------|-------|-------|

| bit 7 bit 0                                                                                                                             |       |       |      |        |        |       |       |

| IVRIF                                                                                                                                   | WAKIF | ERRIF | _    | FIFOIF | RBOVIF | RBIF  | TBIF  |

| R/C-0                                                                                                                                   | R/C-0 | R/C-0 | U-0  | R/C-0  | R/C-0  | R/C-0 | R/C-0 |

|                                                                                                                                         |       |       |      |        |        |       | 2 0   |

| bit 15                                                                                                                                  |       |       |      |        |        |       | bit 8 |

| _                                                                                                                                       | —     | ТХВО  | TXBP | RXBP   | TXWAR  | RXWAR | EWARN |

| U-0                                                                                                                                     | U-0   | R-0   | R-0  | R-0    | R-0    | R-0   | R-0   |

'0' = Bit is cleared

x = Bit is unknown

### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER

'1' = Bit is set

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | <b>TXBO:</b> Transmitter in Error State Bus Off bit                                                                                          |

|           | 1 = Transmitter is in Bus Off state                                                                                                          |

|           | 0 = Transmitter is not in Bus Off state                                                                                                      |

| bit 12    | <b>TXBP:</b> Transmitter in Error State Bus Passive bit                                                                                      |

|           | <ul><li>1 = Transmitter is in Bus Passive state</li><li>0 = Transmitter is not in Bus Passive state</li></ul>                                |

| bit 11    | <b>RXBP:</b> Receiver in Error State Bus Passive bit                                                                                         |

|           | 1 = Receiver is in Bus Passive state<br>0 = Receiver is not in Bus Passive state                                                             |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                                                                                                |

|           | 1 = Transmitter is in Error Warning state<br>0 = Transmitter is not in Error Warning state                                                   |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                                                                                   |

|           | 1 = Receiver is in Error Warning state<br>0 = Receiver is not in Error Warning state                                                         |

| bit 8     | EWARN: Transmitter or Receiver in Error State Warning bit                                                                                    |

|           | <ul> <li>1 = Transmitter or receiver is in Error Warning state</li> <li>0 = Transmitter or receiver is not in Error Warning state</li> </ul> |

| bit 7     | IVRIF: Invalid Message Interrupt Flag bit                                                                                                    |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                                       |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                                                                                               |

|           | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                                                                 |

| bit 5     | ERRIF: Error Interrupt Flag bit (multiple sources in CxINTF<13:8>)                                                                           |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                                       |

| bit 4     | Unimplemented: Read as '0'                                                                                                                   |

| bit 3     | FIFOIF: FIFO Almost Full Interrupt Flag bit                                                                                                  |

|           | 1 = Interrupt request has occurred                                                                                                           |

|           | 0 = Interrupt request has not occurred                                                                                                       |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                                                                                                |

|           | 1 = Interrupt request has occurred                                                                                                           |

-n = Value at POR

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0          | R/W-x                                                                                  | U-0                                        | U-0                    | U-0              | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------|--------------------------------------------|------------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| —            | WAKFIL                                                                                 |                                            | —                      |                  | SEG2PH2          | SEG2PH1         | SEG2PH0 |  |  |  |  |  |

| bit 15       |                                                                                        |                                            |                        |                  |                  |                 | bit     |  |  |  |  |  |

|              |                                                                                        |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

| R/W-x        | R/W-x                                                                                  | R/W-x                                      | R/W-x                  | R/W-x            | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |  |

| SEG2PHTS     | S SAM                                                                                  | SEG1PH2                                    | SEG1PH1                | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |  |  |  |  |  |

| bit 7        |                                                                                        |                                            |                        |                  |                  |                 | bit     |  |  |  |  |  |

| Legend:      |                                                                                        |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

| R = Readab   | le bit                                                                                 | W = Writable                               | bit                    | U = Unimpler     | nented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a |                                                                                        | '1' = Bit is set                           |                        | '0' = Bit is cle |                  | x = Bit is unkr | nown    |  |  |  |  |  |

|              |                                                                                        |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

| bit 15       | Unimplemen                                                                             | nted: Read as '                            | 0'                     |                  |                  |                 |         |  |  |  |  |  |

| bit 14       | WAKFIL: Sel                                                                            | lect CAN Bus L                             | ine Filter for V       | Vake-up bit      |                  |                 |         |  |  |  |  |  |

|              |                                                                                        | N bus line filter                          |                        |                  |                  |                 |         |  |  |  |  |  |

|              |                                                                                        | line filter is not                         |                        | e-up             |                  |                 |         |  |  |  |  |  |

| bit 13-11    | -                                                                                      | nted: Read as '                            |                        |                  |                  |                 |         |  |  |  |  |  |

| bit 10-8     | SEG2PH<2:0>: Phase Segment 2 bits                                                      |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | 111 = Length is 8 x TQ                                                                 |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | 000 = Lenath                                                                           | n is 1 x To                                |                        |                  |                  |                 |         |  |  |  |  |  |

| bit 7        | 000 = Length is 1 x To<br>SEG2PHTS: Phase Segment 2 Time Select bit                    |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | 1 = Freely programmable                                                                |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | 0 = Maximum of SEG1PHx bits or Information Processing Time (IPT), whichever is greater |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

| bit 6        | SAM: Sample                                                                            | <b>SAM:</b> Sample of the CAN Bus Line bit |                        |                  |                  |                 |         |  |  |  |  |  |

|              |                                                                                        | s sampled threes sampled once              |                        |                  |                  |                 |         |  |  |  |  |  |

| bit 5-3      | SEG1PH<2:0>: Phase Segment 1 bits                                                      |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | 111 = Length is 8 x Tq                                                                 |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      | •                                          |                        |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | 000 = Length                                                                           |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

| bit 2-0      |                                                                                        | >: Propagation                             | Time Segmen            | t bits           |                  |                 |         |  |  |  |  |  |

|              | 111 = Length                                                                           | IIS8XIQ                                    | 111 = Length is 8 x TQ |                  |                  |                 |         |  |  |  |  |  |

|              |                                                                                        |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                                                      |                                            |                        |                  |                  |                 |         |  |  |  |  |  |

# REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup> (CONTINUED)

| OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

| <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

| <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

| <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

| <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

|                                                                                                                                                                                                |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

| REGISTER 24-6: | PTGSDLIM: PTG STEP DELAY LIMIT REGISTER <sup>(1,2)</sup> |

|----------------|----------------------------------------------------------|

|                |                                                          |

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |  |  |

|----------------------------------------------------------------------------|-------|----------------|-------|--------------|------------------|----------|-------|--|--|

|                                                                            |       |                | PTGSD | LIM<15:8>    |                  |          |       |  |  |

| bit 15 bit 8                                                               |       |                |       |              |                  |          |       |  |  |

|                                                                            |       |                |       |              |                  |          |       |  |  |

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |  |  |

|                                                                            |       |                | PTGSE | )LIM<7:0>    |                  |          |       |  |  |

| bit 7                                                                      |       |                |       |              |                  |          | bit 0 |  |  |

|                                                                            |       |                |       |              |                  |          |       |  |  |

| Legend:                                                                    |       |                |       |              |                  |          |       |  |  |

| R = Readable                                                               | bit   | W = Writable b | it    | U = Unimplen | nented bit, read | d as '0' |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |                |       |              | nown             |          |       |  |  |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

**Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 24-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|

|                                   |       |                  | PTGC0 | LIM<15:8>                          |       |                 |       |  |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |  |

|                                   |       |                  |       |                                    |       |                 |       |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|                                   |       |                  | PTGC  | )LIM<7:0>                          |       |                 |       |  |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |  |

|                                   |       |                  |       |                                    |       |                 |       |  |

| Legend:                           |       |                  |       |                                    |       |                 |       |  |

| R = Readable bit W = Writable bit |       |                  | it    | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at POR '1              |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unki | nown  |  |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

- bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

- 1111 = FLT4 1110 = FLT2 1101 = PTGO19 1100 = PTGO18 1011 = Reserved 1010 = Reserved 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM3H 0100 = PWM3L 0011 = PWM2H 0010 = PWM2L 0001 = PWM1H 0000 = PWM1L

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 27-1: DEVID: DEVICE ID REGISTER

| Legend: R = Read-Only bit U = Unimplemented bit |   |   |         |                      |   |   |        |

|-------------------------------------------------|---|---|---------|----------------------|---|---|--------|

|                                                 |   |   |         |                      |   |   |        |

| bit 7                                           |   |   |         |                      |   |   | bit 0  |

|                                                 |   |   | DEVID   | <7:0> <sup>(1)</sup> |   |   |        |

| R                                               | R | R | R       | R                    | R | R | R      |

| bit 15                                          |   |   |         |                      |   |   | bit 8  |

|                                                 |   |   | DEVID<  | 15:8> <sup>(1)</sup> |   |   |        |

| R                                               | R | R | R       | R                    | R | R | R      |

| bit 23                                          |   |   |         |                      |   |   | bit 16 |

|                                                 |   |   | DEVID<2 | 23:16>(1)            |   |   |        |

| R                                               | R | R | R       | R                    | R | R | R      |

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device ID values.

### **REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER**

| R           | R             | R | R      | R                      | R          | R | R      |

|-------------|---------------|---|--------|------------------------|------------|---|--------|

|             |               |   | DEVREV | <23:16> <sup>(1)</sup> |            |   |        |

| bit 23      |               |   |        |                        |            |   | bit 16 |

|             |               |   |        |                        |            |   |        |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVREV | <15:8>(1)              |            |   |        |

| bit 15      |               |   |        |                        |            |   | bit 8  |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVRE\ | /<7:0>(1)              |            |   |        |

| bit 7       |               |   |        |                        |            |   | bit 0  |

|             |               |   |        |                        |            |   |        |

| Legend: R = | Read-only bit |   |        | U = Unimplem           | nented bit |   |        |

# bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device revision values.

# **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>    | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | -0.3V to +3.6V       |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                       |                      |

| Maximum current sunk/sourced by any 4x I/O pin                                    | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                    | 25 mA                |

| Maximum current sunk by all ports <sup>(2,4)</sup>                                | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Exceptions are: dsPIC33EPXXXGP502, dsPIC33EPXXXMC202/502 and PIC24EPXXXGP/MC202 devices, which have a maximum sink/source capability of 130 mA.

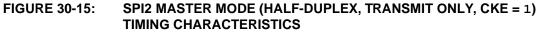

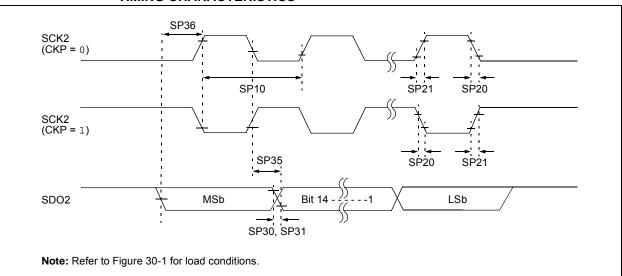

#### TABLE 30-34: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| АС СНА                                      | RACTERIST             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extend} \end{array}$ |      |                     |      |       |                                |

|---------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|--------------------------------|

| Param. Symbol Characteristic <sup>(1)</sup> |                       |                                                                                                                                                                                                                                                                                    | Min. | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP10                                        | FscP                  | Maximum SCK2 Frequency                                                                                                                                                                                                                                                             | _    | _                   | 15   | MHz   | (Note 3)                       |

| SP20                                        | TscF                  | SCK2 Output Fall Time                                                                                                                                                                                                                                                              | —    | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP21                                        | TscR                  | SCK2 Output Rise Time                                                                                                                                                                                                                                                              | —    | —                   | _    | ns    | See Parameter DO31<br>(Note 4) |

| SP30                                        | TdoF                  | SDO2 Data Output Fall Time                                                                                                                                                                                                                                                         | —    | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP31                                        | TdoR                  | SDO2 Data Output Rise Time                                                                                                                                                                                                                                                         | -    | _                   |      | ns    | See Parameter DO31<br>(Note 4) |

| SP35                                        | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge                                                                                                                                                                                                                                          | —    | 6                   | 20   | ns    |                                |

| SP36                                        | TdiV2scH,<br>TdiV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge                                                                                                                                                                                                                                       | 30   | —                   | _    | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

| AC CHARACTERISTICS   |                                          |                                             | Standard Operating<br>(unless otherwise s<br>Operating temperate | Industrial<br>or Extended |     |     |

|----------------------|------------------------------------------|---------------------------------------------|------------------------------------------------------------------|---------------------------|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                       | CKE                       | СКР | SMP |

| 15 MHz               | Table 30-42                              | _                                           | _                                                                | 0,1                       | 0,1 | 0,1 |

| 10 MHz               | _                                        | Table 30-43                                 | —                                                                | 1                         | 0,1 | 1   |

| 10 MHz               | —                                        | Table 30-44                                 | —                                                                | 0                         | 0,1 | 1   |

| 15 MHz               | —                                        | —                                           | Table 30-45                                                      | 1                         | 0   | 0   |

| 11 MHz               | —                                        | —                                           | Table 30-46                                                      | 1                         | 1   | 0   |

| 15 MHz               | _                                        | —                                           | Table 30-47                                                      | 0                         | 1   | 0   |

| 11 MHz               | _                                        | _                                           | Table 30-48                                                      | 0                         | 0   | 0   |

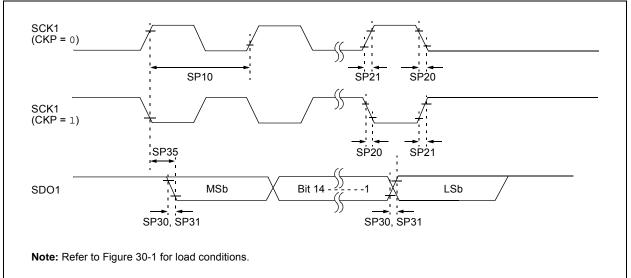

### TABLE 30-41: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

## FIGURE 30-22: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

| AC CHA              | RACTER  | ISTICS           |                           | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |             |            |                        |  |

|---------------------|---------|------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|------------------------|--|

| Param<br>No. Symbol |         | Characte         | eristic <sup>(4)</sup>    | Min. <sup>(1)</sup>                                                                                                                                                                                             | -40<br>Max. | Units      | Conditions             |  |

| IM10 TLO:SCI        |         | Clock Low Time   | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 | _           | μS         |                        |  |

|                     |         |                  | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | μS         |                        |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | μs         |                        |  |

| IM11                | THI:SCL | Clock High Time  | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 |             | μS         |                        |  |

|                     |         | Ū                | 400 kHz mode              |                                                                                                                                                                                                                 |             | μ <b>S</b> |                        |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                 |             | μ <b>S</b> |                        |  |

| IM20                | TF:SCL  | SDAx and SCLx    | 100 kHz mode              |                                                                                                                                                                                                                 | 300         | ns         | CB is specified to be  |  |

|                     |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                     | 300         | ns         | from 10 to 400 pF      |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                                 | 100         | ns         | -                      |  |

| IM21                | TR:SCL  | SDAx and SCLx    | 100 kHz mode              |                                                                                                                                                                                                                 | 1000        | ns         | CB is specified to be  |  |

|                     |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                     | 300         | ns         | from 10 to 400 pF      |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                                 | 300         | ns         | -                      |  |

| IM25                | TSU:DAT | Data Input       | 100 kHz mode              | 250                                                                                                                                                                                                             |             | ns         |                        |  |

|                     |         | Setup Time       | 400 kHz mode              | 100                                                                                                                                                                                                             | _           | ns         |                        |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                                                                                              |             | ns         | -                      |  |

| IM26                | THD:DAT | Data Input       | 100 kHz mode              | 0                                                                                                                                                                                                               | _           | μS         |                        |  |

|                     |         | Hold Time        | 400 kHz mode              | 0                                                                                                                                                                                                               | 0.9         | μS         |                        |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                                                                                             |             | μs         | -                      |  |

| IM30                | TSU:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 |             | μ <b>S</b> | Only relevant for      |  |

|                     |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 |             | μS         | Repeated Start         |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                 | _           | μs         | condition              |  |

| IM31                | THD:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 |             | μ <b>s</b> | After this period, the |  |

|                     |         | Hold Time        | 400 kHz mode              | Tcy/2 (BRG +2)                                                                                                                                                                                                  |             | μS         | first clock pulse is   |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                 | _           | μS         | generated              |  |

| IM33                | Tsu:sto | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 | _           | μs         |                        |  |

|                     |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 | _           | μs         | 1                      |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                 | —           | μS         |                        |  |

| IM34                | THD:STO | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                 | _           | μs         |                        |  |

|                     |         | Hold Time        | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                 | —           | μS         |                        |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                 | —           | μS         |                        |  |

| IM40                | TAA:SCL | Output Valid     | 100 kHz mode              |                                                                                                                                                                                                                 | 3500        | ns         |                        |  |

|                     |         | From Clock       | 400 kHz mode              | —                                                                                                                                                                                                               | 1000        | ns         | İ.                     |  |

|                     |         |                  | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                               | 400         | ns         | İ.                     |  |