Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 256KB (85.5K x 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc204t-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

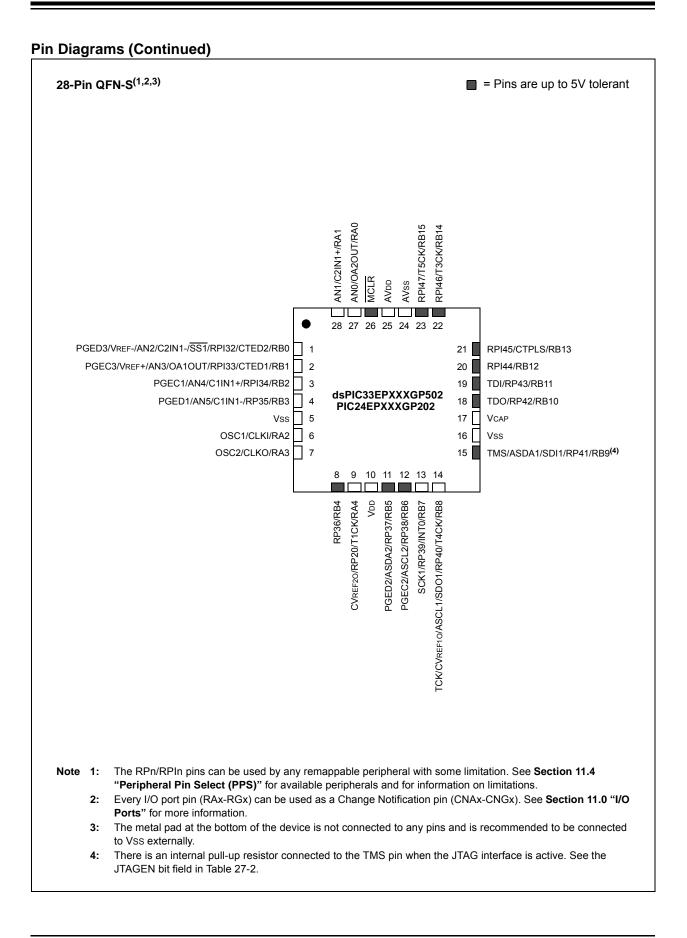

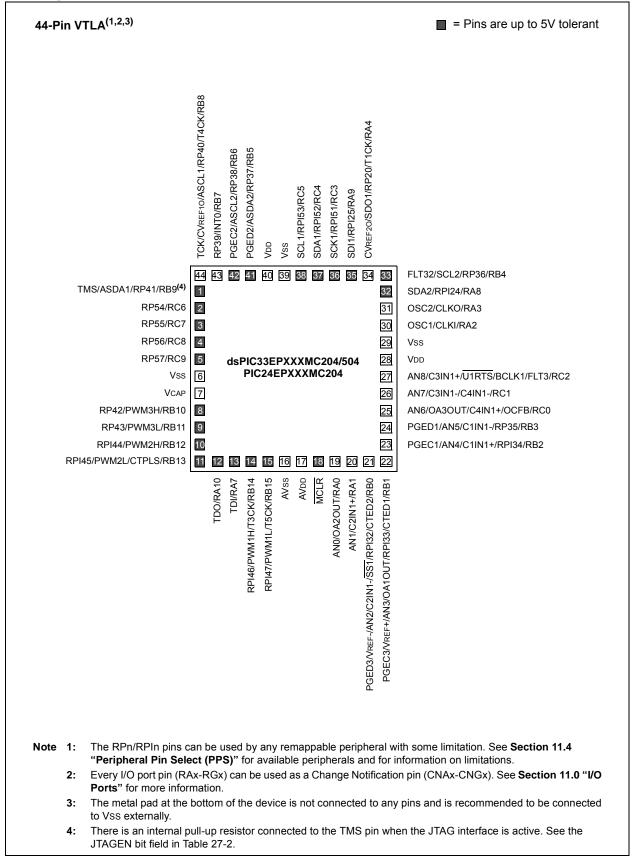

### Pin Diagrams (Continued)

### **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

# 4.4 Special Function Register Maps

# TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00   |        |        |              | 011 401    |        |       | 20/0/00/    |        |       |        |         |          |          | -     | r     |               |

|-----------|-------|--------|--------|--------|--------------|------------|--------|-------|-------------|--------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8       | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |        |        |        |              |            |        |       | W0 (WR      | EG)    |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |        |        |        |              |            |        |       | W1          |        |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |        |        |        |              |            |        |       | W2          |        |       |        |         |          |          |       |       | xxxx          |

| W3        | 0006  |        | W3 2   |        |              |            |        |       |             |        |       | xxxx   |         |          |          |       |       |               |

| W4        | 8000  |        | W4     |        |              |            |        |       |             |        |       | xxxx   |         |          |          |       |       |               |

| W5        | 000A  |        | W5     |        |              |            |        |       |             |        | xxxx  |        |         |          |          |       |       |               |

| W6        | 000C  |        |        |        |              |            |        |       | W6          |        |       |        |         |          |          |       |       | xxxx          |

| W7        | 000E  |        |        |        |              |            |        |       | W7          |        |       |        |         |          |          |       |       | xxxx          |

| W8        | 0010  |        |        |        |              |            |        |       | W8          |        |       |        |         |          |          |       |       | xxxx          |

| W9        | 0012  |        |        |        |              |            |        |       | W9          |        |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |        |        |        |              |            |        |       | W10         |        |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |        |        |        |              |            |        |       | W11         |        |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |        |        |        |              |            |        |       | W12         |        |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |        |        |        |              |            |        |       | W13         |        |       |        |         |          |          |       |       | xxxx          |

| W14       | 001C  |        | W14    |        |              |            |        |       |             | xxxx   |       |        |         |          |          |       |       |               |

| W15       | 001E  | W15    |        |        |              |            |        |       | xxxx        |        |       |        |         |          |          |       |       |               |

| SPLIM     | 0020  | SPLIM  |        |        |              |            |        |       | 0000        |        |       |        |         |          |          |       |       |               |

| ACCAL     | 0022  | ACCAL  |        |        |              |            |        |       |             | 0000   |       |        |         |          |          |       |       |               |

| ACCAH     | 0024  |        |        |        |              |            |        |       | ACCA        | H      |       |        |         |          |          |       |       | 0000          |

| ACCAU     | 0026  |        |        | Si     | gn Extensior | n of ACCA< | 39>    |       |             |        |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |        |        |        |              |            |        |       | ACCB        | L      |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |        |        |        |              |            |        |       | ACCB        | Н      |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |        |        | Si     | gn Extensior | n of ACCB< | 39>    |       |             |        |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |        |        |        |              |            |        | F     | PCL<15:0>   |        |       |        |         |          |          |       |       | 0000          |

| PCH       | 0030  | _      | _      | _      | —            | _          | _      | —     | _           | _      |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _      | _      | _      | —            | _          | _      |       |             |        |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _      |        | _      | —            |            | _      | _     |             |        |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |        |        |        |              |            |        |       | RCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DCOUNT    | 0038  |        |        |        |              |            |        |       | DCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DOSTARTL  | 003A  |        |        |        |              |            |        | DOS   | STARTL<15:1 | >      |       |        |         |          |          |       |       | 0000          |

| DOSTARTH  | 003C  | _      | —      | —      | _            | —          | —      | —     | _           | _      | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  |        |        |        |              |            |        | DO    | ENDL<15:1>  | >      |       |        |         |          |          |       |       | 0000          |

| DOENDH    | 0040  | _      | —      | —      | —            | —          | —      | _     | —           | —      | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |        |        |        |              |            |        |       |             |        |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | _      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0                             | R/W-0 | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |  |

|------------------------------------|-----------------------------------|-------|-------|-----------------------------------------|------------------|----------|-------|--|--|

|                                    |                                   |       | PAD   | <15:8>                                  |                  |          |       |  |  |

| bit 15                             |                                   |       |       |                                         |                  |          | bit 8 |  |  |

|                                    |                                   |       |       |                                         |                  |          |       |  |  |

| R/W-0                              | R/W-0                             | R/W-0 | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |  |

|                                    |                                   |       | PAE   | )<7:0>                                  |                  |          |       |  |  |

| bit 7                              |                                   |       |       |                                         |                  |          | bit 0 |  |  |

|                                    |                                   |       |       |                                         |                  |          |       |  |  |

| Legend:                            |                                   |       |       |                                         |                  |          |       |  |  |

| R = Readable                       | R = Readable bit W = Writable bit |       |       | U = Unimplen                            | nented bit, read | d as '0' |       |  |  |

| -n = Value at POR '1' = Bit is set |                                   |       |       | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

|-----------------|-------|------------------|-------|-------------------|------------------|--------------------|-------|--|

| —               |       |                  |       | CNT<              | 13:8> <b>(2)</b> |                    |       |  |

| bit 15          |       |                  |       |                   |                  |                    | bit 8 |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

|                 |       |                  | CNT<  | <7:0> <b>(2)</b>  |                  |                    |       |  |

| bit 7           |       |                  |       |                   |                  |                    | bit 0 |  |

| Legend:         |       |                  |       |                   |                  |                    |       |  |

| R = Readable b  | oit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea  | id as '0'          |       |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

| U-0                           | U-0                                                | U-0                                                                                                                         | U-0            | U-0                                | U-0  | U-0             | U-0   |  |  |  |  |

|-------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------|------|-----------------|-------|--|--|--|--|

| -                             | —                                                  | —                                                                                                                           | —              | —                                  | —    | —               | —     |  |  |  |  |

| bit 15                        |                                                    |                                                                                                                             |                |                                    |      |                 | bit 8 |  |  |  |  |

| U-0                           | U-0                                                | U-0                                                                                                                         | U-0            | R-1                                | R-1  | R-1             | R-1   |  |  |  |  |

| _                             | _                                                  | _                                                                                                                           | _              |                                    | LSTC | H<3:0>          |       |  |  |  |  |

| bit 7                         |                                                    |                                                                                                                             |                |                                    |      |                 | bit 0 |  |  |  |  |

| Legend:                       |                                                    |                                                                                                                             |                |                                    |      |                 |       |  |  |  |  |

| R = Readable bit W = Writable |                                                    |                                                                                                                             | bit            | U = Unimplemented bit, read as '0' |      |                 |       |  |  |  |  |

| -n = Value a                  | -n = Value at POR '1' = Bit is                     |                                                                                                                             |                | '0' = Bit is cle                   | ared | x = Bit is unkr | nown  |  |  |  |  |

|                               |                                                    |                                                                                                                             |                |                                    |      |                 |       |  |  |  |  |

| bit 15-4                      | Unimplemen                                         | ted: Read as '                                                                                                              | 0'             |                                    |      |                 |       |  |  |  |  |

| bit 3-0                       | LSTCH<3:0>                                         | : Last DMAC C                                                                                                               | hannel Active  | e Status bits                      |      |                 |       |  |  |  |  |

|                               | 1111 = No DI<br>1110 = Rese                        | MA transfer has<br>rved                                                                                                     | s occurred sir | nce system Res                     | set  |                 |       |  |  |  |  |

|                               | •                                                  |                                                                                                                             |                |                                    |      |                 |       |  |  |  |  |

|                               | •                                                  |                                                                                                                             |                |                                    |      |                 |       |  |  |  |  |

|                               | •                                                  |                                                                                                                             |                |                                    |      |                 |       |  |  |  |  |

|                               | 0011 <b>= Last</b> o                               | 0100 = Reserved<br>0011 = Last data transfer was handled by Channel 3<br>0010 = Last data transfer was handled by Channel 2 |                |                                    |      |                 |       |  |  |  |  |

|                               | 0001 = Last data transfer was handled by Channel 1 |                                                                                                                             |                |                                    |      |                 |       |  |  |  |  |

### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0001 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

| R/W-0           | R/W-0                                                                                                                                            | R/W-1                                                                                                               | R/W-1                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------|------------------------|--------------------|-----------------|-----------|--|--|--|--|--|

| ROI             | DOZE2 <sup>(1)</sup>                                                                                                                             | DOZE1 <sup>(1)</sup>                                                                                                | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup> | FRCDIV2            | FRCDIV1         | FRCDIV0   |  |  |  |  |  |

| bit 15          |                                                                                                                                                  |                                                                                                                     | •                    |                        |                    |                 | bit 8     |  |  |  |  |  |

|                 |                                                                                                                                                  |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

| R/W-0           | R/W-1                                                                                                                                            | U-0                                                                                                                 | R/W-0                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |  |  |

| PLLPOST1        | PLLPOST0                                                                                                                                         | —                                                                                                                   | PLLPRE4              | PLLPRE3                | PLLPRE2            | PLLPRE1         | PLLPRE0   |  |  |  |  |  |

| bit 7           |                                                                                                                                                  |                                                                                                                     |                      |                        |                    |                 | bit (     |  |  |  |  |  |

|                 |                                                                                                                                                  |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

| Legend:         |                                                                                                                                                  |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

| R = Readable    |                                                                                                                                                  | W = Writable                                                                                                        |                      | -                      | nented bit, read   |                 |           |  |  |  |  |  |

| -n = Value at F | POR                                                                                                                                              | '1' = Bit is set                                                                                                    |                      | '0' = Bit is cle       | ared               | x = Bit is unkr | nown      |  |  |  |  |  |

| h:+ 45          |                                                                                                                                                  | on Interview h                                                                                                      |                      |                        |                    |                 |           |  |  |  |  |  |

| bit 15          |                                                                                                                                                  | ROI: Recover on Interrupt bit L = Interrupts will clear the DOZEN bit                                               |                      |                        |                    |                 |           |  |  |  |  |  |

|                 |                                                                                                                                                  |                                                                                                                     |                      | EN bit                 |                    |                 |           |  |  |  |  |  |

| bit 14-12       | <ul> <li>0 = Interrupts have no effect on the DOZEN bit</li> <li>DOZE&lt;2:0&gt;: Processor Clock Reduction Select bits<sup>(1)</sup></li> </ul> |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 111 = Fcy divided by 128                                                                                                                         |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 110 = FCY divided by 64                                                                                                                          |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 101 = FCY divided by 32<br>100 = FCY divided by 16                                                                                               |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 100 = FCY divided by 16<br>011 = FCY divided by 8 (default)                                                                                      |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 010 = FCY divided by 8 (default)                                                                                                                 |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 001 = Fcy divided by 2                                                                                                                           |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 000 = Fcy div                                                                                                                                    | •                                                                                                                   |                      |                        |                    |                 |           |  |  |  |  |  |

| bit 11          |                                                                                                                                                  | e Mode Enable                                                                                                       |                      |                        |                    |                 |           |  |  |  |  |  |

|                 |                                                                                                                                                  |                                                                                                                     |                      |                        | pheral clocks a    | nd the process  | or clocks |  |  |  |  |  |

|                 |                                                                                                                                                  | -                                                                                                                   | -                    | ratio is forced to     |                    |                 |           |  |  |  |  |  |

| bit 10-8        | FRCDIV<2:0>: Internal Fast RC Oscillator Postscaler bits<br>111 = FRC divided by 256                                                             |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 111 = FRC di<br>110 = FRC di                                                                                                                     |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 101 <b>= FRC di</b>                                                                                                                              |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 100 <b>= FRC d</b> i                                                                                                                             | vided by 16                                                                                                         |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 011 = FRC di                                                                                                                                     |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 010 = FRC di                                                                                                                                     | 2                                                                                                                   |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | 001 = FRC divided by 2<br>000 = FRC divided by 1 (default)                                                                                       |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

| bit 7-6         |                                                                                                                                                  |                                                                                                                     | -                    | r Select bits (al      | so denoted as      | 'N2', PLL posts | caler)    |  |  |  |  |  |

|                 |                                                                                                                                                  | PLLPOST<1:0>: PLL VCO Output Divider Select bits (also denoted as 'N2', PLL postscaler)<br>11 = Output divided by 8 |                      |                        |                    |                 |           |  |  |  |  |  |

|                 |                                                                                                                                                  | 10 = Reserved                                                                                                       |                      |                        |                    |                 |           |  |  |  |  |  |

|                 |                                                                                                                                                  | livided by 4 (de                                                                                                    | efault)              |                        |                    |                 |           |  |  |  |  |  |

| bit 5           | 00 = Output d                                                                                                                                    | ted: Read as '                                                                                                      | o'                   |                        |                    |                 |           |  |  |  |  |  |

|                 | •                                                                                                                                                |                                                                                                                     |                      |                        |                    |                 |           |  |  |  |  |  |

|                 | e DOZE<2:0> b<br>ZE<2:0> are ig                                                                                                                  |                                                                                                                     | written to whe       | en the DOZEN           | bit is clear. If D | OZEN = 1, any   | writes to |  |  |  |  |  |

| <b>2:</b> This  | s bit is cleared                                                                                                                                 | when the ROI I                                                                                                      | oit is set and a     | an interrupt occ       | urs.               |                 |           |  |  |  |  |  |

|                 | DOJENUS                                                                                                                                          |                                                                                                                     |                      |                        | ~ ~                |                 | <i>.</i>  |  |  |  |  |  |

### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER

The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| REGISTER                           | TU-5: PIVID6                      | . PERIPHER       |                           | DISABLE C                          | UNIROL RE             | GISIER 6              |                       |

|------------------------------------|-----------------------------------|------------------|---------------------------|------------------------------------|-----------------------|-----------------------|-----------------------|

| U-0                                | U-0                               | U-0              | U-0                       | U-0                                | R/W-0                 | R/W-0                 | R/W-0                 |

| —                                  | —                                 | —                | —                         | _                                  | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |

| bit 15                             |                                   |                  |                           |                                    |                       |                       | bit 8                 |

|                                    |                                   |                  |                           |                                    |                       |                       |                       |

| U-0                                | U-0                               | U-0              | U-0                       | U-0                                | U-0                   | U-0                   | U-0                   |

|                                    |                                   |                  |                           |                                    |                       |                       |                       |

| bit 7                              |                                   |                  |                           |                                    |                       |                       | bit 0                 |

|                                    |                                   |                  |                           |                                    |                       |                       |                       |

| Legend:                            |                                   |                  |                           |                                    |                       |                       |                       |

| R = Readab                         | R = Readable bit W = Writable bit |                  | bit                       | U = Unimplemented bit, read as '0' |                       |                       |                       |

| -n = Value at POR '1' = Bit is set |                                   |                  | '0' = Bit is clea         | x = Bit is unkr                    | iown                  |                       |                       |

|                                    |                                   |                  |                           |                                    |                       |                       |                       |

| bit 15-11                          | Unimplement                       | ted: Read as '   | כ'                        |                                    |                       |                       |                       |

| bit 10                             | PWM3MD: P\                        | NM3 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |

|                                    | 1 = PWM3 mo                       | odule is disable | ed                        |                                    |                       |                       |                       |

|                                    | 0 = PWM3 mo                       | odule is enable  | d                         |                                    |                       |                       |                       |

| bit 9                              | PWM2MD: P\                        | NM2 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |

|                                    | 1 = PWM2 mo                       | odule is disable | ed                        |                                    |                       |                       |                       |

|                                    | 0 = PWM2 mo                       | odule is enable  | d                         |                                    |                       |                       |                       |

| bit 8                              | PWM1MD: P\                        | NM1 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |

|                                    |                                   | odule is disable |                           |                                    |                       |                       |                       |

|                                    | 0 = PWM1 mo                       | odule is enable  | d                         |                                    |                       |                       |                       |

| bit 7-0                            | Unimplement                       | ted: Read as '   | כ'                        |                                    |                       |                       |                       |

# REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

### REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0            | R/W-0                                                    | R/W-0          | R/W-0        | R/W-0                | R/W-0     | R/W-0 |

|--------------|------------------|----------------------------------------------------------|----------------|--------------|----------------------|-----------|-------|

|              |                  |                                                          |                | DTCMP3R<6:0  | )>                   |           |       |

| bit 15       |                  |                                                          |                |              |                      |           | bit 8 |

| U-0          | R/W-0            | R/W-0                                                    | R/W-0          | R/W-0        | R/W-0                | R/W-0     | R/W-0 |

| 0-0          | R/W-0            | R/W-0                                                    | -              | DTCMP2R<6:0  |                      | R/W-0     | R/W-U |

| bit 7        |                  |                                                          |                |              | 17                   |           | bit 0 |

| bit i        |                  |                                                          |                |              |                      |           | bit 0 |

| Legend:      |                  |                                                          |                |              |                      |           |       |

| R = Readab   | ole bit          | W = Writable                                             | bit            | U = Unimplem | nented bit, rea      | ad as '0' |       |

| -n = Value a | at POR           | '1' = Bit is set                                         | Bit is set '0' |              | '0' = Bit is cleared |           | nown  |

|              |                  |                                                          |                |              |                      |           |       |

|              |                  | nput tied to CMI                                         |                |              |                      |           |       |

| bit 7        | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |                |              |                      |           |       |

NOTES:

### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7- | 6  | DTC<1:0>: Dead-Time Control bits                                                                                                    |

|--------|----|-------------------------------------------------------------------------------------------------------------------------------------|

|        |    | 11 = Dead-Time Compensation mode                                                                                                    |

|        |    | 10 = Dead-time function is disabled                                                                                                 |

|        |    | 01 = Negative dead time is actively applied for Complementary Output mode                                                           |

|        |    | 00 = Positive dead time is actively applied for all output modes                                                                    |

| bit 5  |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                     |

|        |    | When Set to '1':                                                                                                                    |

|        |    | If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.                                                                          |

|        |    | If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                          |

|        |    | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.                                               |

|        |    | If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                          |

| bit 4  |    | Unimplemented: Read as '0'                                                                                                          |

| bit 3  |    | MTBS: Master Time Base Select bit                                                                                                   |

|        |    | 1 = PWM generator uses the secondary master time base for synchronization and as the clock source                                   |

|        |    | for the PWM generation logic (if secondary time base is available)                                                                  |

|        |    | 0 = PWM generator uses the primary master time base for synchronization and as the clock source                                     |

|        |    | for the PWM generation logic                                                                                                        |

| bit 2  |    | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                |

|        |    | 1 = Center-Aligned mode is enabled                                                                                                  |

|        |    | 0 = Edge-Aligned mode is enabled                                                                                                    |

| bit 1  |    | <b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                        |

|        |    | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base<br/>mode</li> </ul> |

|        |    | 0 = External pins do not affect PWMx time base                                                                                      |

| bit 0  |    | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                     |

|        |    | 1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate                                                      |

|        |    | <ul> <li>Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the<br/>PWMx period boundary</li> </ul>   |

| Note   | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                        |

|        | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                              |

|        | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                 |

|        | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.            |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

# 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details. The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier)

acceptance filters

- · Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

| DC CHARACTERISTICS |                               |               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                       |                 |  |  |

|--------------------|-------------------------------|---------------|-------------------------------------------------------|-----------------------|-----------------|--|--|

| Parameter<br>No.   | Тур.                          | Max.          | Units                                                 | Conditions            |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF                                       | P32MC20X/50X and PIC2 | 4EP32GP/MC20X   |  |  |

| DC60d              | 30                            | 100           | μA                                                    | -40°C                 |                 |  |  |

| DC60a              | 35                            | 100           | μA                                                    | +25°C                 | 2 2)/           |  |  |

| DC60b              | 150                           | 200           | μA                                                    | +85°C                 | 3.3V            |  |  |

| DC60c              | 250                           | 500           | μA                                                    | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                       | P64MC20X/50X and PIC2 | 4EP64GP/MC20X   |  |  |

| DC60d              | 25                            | 100           | μA                                                    | -40°C                 |                 |  |  |

| DC60a              | 30                            | 100           | μΑ                                                    | +25°C                 | 2 21/           |  |  |

| DC60b              | 150                           | 350           | μΑ                                                    | +85°C                 | 3.3V            |  |  |

| DC60c              | 350                           | 800           | μΑ                                                    | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E                                        | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |  |

| DC60d              | 30                            | 100           | μΑ                                                    | -40°C                 |                 |  |  |

| DC60a              | 35                            | 100           | μΑ                                                    | +25°C                 | 3.3V            |  |  |

| DC60b              | 150                           | 350           | μΑ                                                    | +85°C                 | 5.57            |  |  |

| DC60c              | 550                           | 1000          | μΑ                                                    | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E                                        | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |  |

| DC60d              | 35                            | 100           | μΑ                                                    | -40°C                 |                 |  |  |

| DC60a              | 40                            | 100           | μΑ                                                    | +25°C                 | 3.3V            |  |  |

| DC60b              | 250                           | 450           | μΑ                                                    | +85°C                 | 5.5 V           |  |  |

| DC60c              | 1000                          | 1200          | μΑ                                                    | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP512G | P50X, dsPIC33E                                        | P512MC20X/50X and PIC | 24EP512GP/MC20X |  |  |

| DC60d              | 40                            | 100           | μΑ                                                    | -40°C                 |                 |  |  |

| DC60a              | 45                            | 100           | μΑ                                                    | +25°C                 | 3.3V            |  |  |

| DC60b              | 350                           | 800           | μΑ                                                    | +85°C                 | 0.0 V           |  |  |

| DC60c              | 1100                          | 1500          | μA                                                    | +125°C                |                 |  |  |

### TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

| TABLE 30-23: TIME | 1 EXTERNAL CLOCK TIMING REQUI | REMENTS <sup>(1)</sup> |

|-------------------|-------------------------------|------------------------|

|-------------------|-------------------------------|------------------------|

| AC CHARACTERISTICS |           |                                                                                                    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                        |      |               |       |                                                                             |

|--------------------|-----------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Charao                                                                                             | cteristic <sup>(2)</sup>                              | Min.                                   | Тур. | Max.          | Units | Conditions                                                                  |

| TA10               | ТтхН      | T1CK High<br>Time                                                                                  | Synchronous<br>mode                                   | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                          | 35                                     | _    | —             | ns    |                                                                             |

| TA11               | ΤτχL      | T1CK Low<br>Time                                                                                   | Synchronous<br>mode                                   | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                          | 10                                     | _    | _             | ns    |                                                                             |

| TA15               | ΤτχΡ      | T1CK Input<br>Period                                                                               | Synchronous mode                                      | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | _             | ns    | N = prescale value<br>(1, 8, 64, 256)                                       |

| OS60               | Ft1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting bit, TCS<br>(T1CON<1>)) |                                                       | DC                                     |      | 50            | kHz   |                                                                             |

| TA20               | TCKEXTMRL | Delay from External T1CK<br>Clock Edge to Timer<br>Increment                                       |                                                       | 0.75 Tcy + 40                          | —    | 1.75 Tcy + 40 | ns    |                                                                             |

Note 1: Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

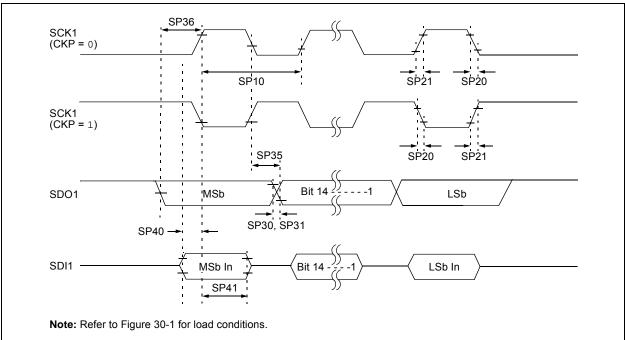

### FIGURE 30-24: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-43:SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS

| TIMINO REGORDENTO  |                       |                                               |                                                       |                     |      |       |                             |

|--------------------|-----------------------|-----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|

| AC CHARACTERISTICS |                       |                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP10               | FscP                  | Maximum SCK1 Frequency                        | _                                                     | —                   | 10   | MHz   | (Note 3)                    |

| SP20               | TscF                  | SCK1 Output Fall Time                         | —                                                     | —                   |      | ns    | See Parameter DO32 (Note 4) |

| SP21               | TscR                  | SCK1 Output Rise Time                         | —                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                    | —                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                    | —                                                     | _                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge     | —                                                     | 6                   | 20   | ns    |                             |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDO1 Data Output Setup to<br>First SCK1 Edge  | 30                                                    | —                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data<br>Input to SCK1 Edge | 30                                                    | —                   | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge     | 30                                                    |                     |      | ns    |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPI1 pins.

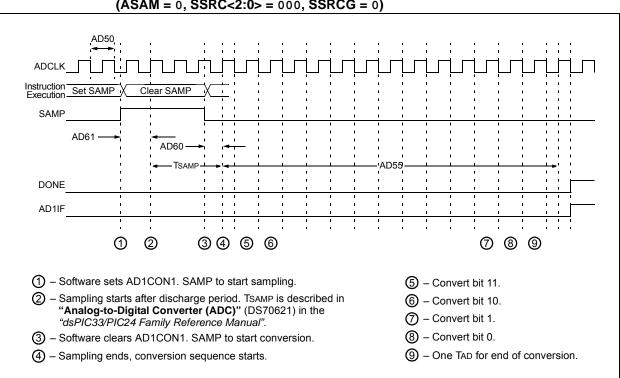

### FIGURE 30-36: ADC CONVERSION (12-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000, SSRCG = 0)

| Section Name                                                                                              | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|