Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc206-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

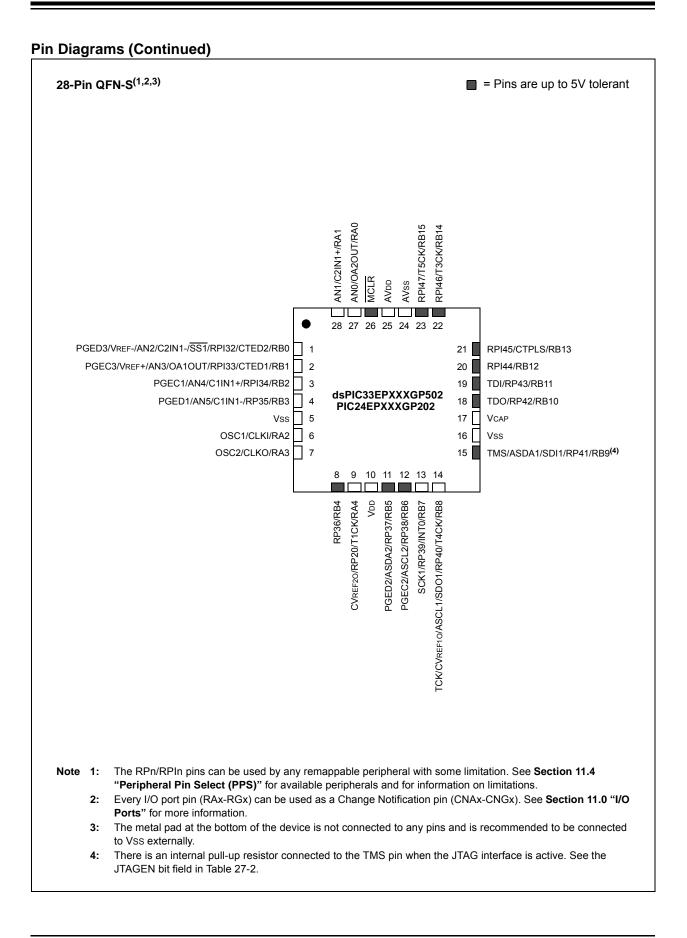

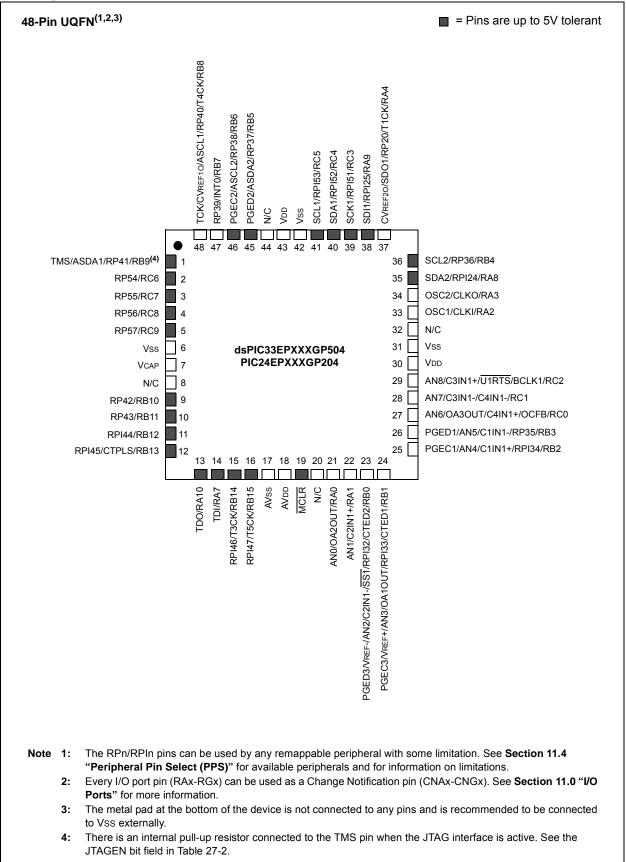

#### Pin Diagrams (Continued)

|                 |       |        |                            |         |         |         |            |         |          |         |        |       |       |        |          |          |        | All    |

|-----------------|-------|--------|----------------------------|---------|---------|---------|------------|---------|----------|---------|--------|-------|-------|--------|----------|----------|--------|--------|

| File Name       | Addr. | Bit 15 | Bit 14                     | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9   | Bit 8    | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0  | Resets |

| PTGCST          | 0AC0  | PTGEN  | —                          | PTGSIDL | PTGTOGL |         | PTGSWT     | PTGSSEN | PTGIVIS  | PTGSTRT | PTGWTO | _     | _     | —      | —        | PTGIT    | M<1:0> | 0000   |

| PTGCON          | 0AC2  | F      | PTGCLK<2                   | :0>     |         | F       | PTGDIV<4:0 | >       |          |         | PTGPWD | <3:0> |       | _      | P        | TGWDT<2: | 0>     | 0000   |

| PTGBTE          | 0AC4  |        | ADC                        | TS<4:1> |         | IC4TSS  | IC3TSS     | IC2TSS  | IC1TSS   | OC4CS   | OC3CS  | OC2CS | OC1CS | OC4TSS | OC3TSS   | OC2TSS   | OC1TSS | 0000   |

| PTGHOLD         | 0AC6  |        |                            |         |         |         |            |         | PTGHOLD  | <15:0>  |        |       |       |        |          |          |        | 0000   |

| <b>PTGT0LIM</b> | 0AC8  |        |                            |         |         |         |            |         | PTGT0LIM | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGT1LIM        | 0ACA  |        |                            |         |         |         |            |         | PTGT1LIM | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGSDLIM        | 0ACC  |        | PTGSDLIM<15:0> 000         |         |         |         |            |         |          |         |        | 0000  |       |        |          |          |        |        |

| <b>PTGC0LIM</b> | 0ACE  |        | PTGC0LIM<15:0> 00          |         |         |         |            |         |          |         |        | 0000  |       |        |          |          |        |        |

| PTGC1LIM        | 0AD0  |        |                            |         |         |         |            |         | PTGC1LIN | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGADJ          | 0AD2  |        |                            |         |         |         |            |         | PTGADJ<  | :15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGL0           | 0AD4  |        |                            |         |         |         |            |         | PTGL0<   | 15:0>   |        |       |       |        |          |          |        | 0000   |

| PTGQPTR         | 0AD6  | —      | —                          | —       | —       | _       | —          | —       | _        | —       | —      | -     |       | P      | TGQPTR<4 | 4:0>     |        | 0000   |

| PTGQUE0         | 0AD8  |        |                            |         | STEP    | 1<7:0>  |            |         |          |         |        |       | STEPO | )<7:0> |          |          |        | 0000   |

| PTGQUE1         | 0ADA  |        |                            |         | STEP    | '3<7:0> |            |         |          |         |        |       | STEP2 | 2<7:0> |          |          |        | 0000   |

| PTGQUE2         | 0ADC  |        |                            |         | STEP    | 25<7:0> |            |         |          |         |        |       | STEP4 | <7:0>  |          |          |        | 0000   |

| PTGQUE3         | 0ADE  |        |                            |         | STEP    | 7<7:0>  |            |         |          |         |        |       | STEP6 | 6<7:0> |          |          |        | 0000   |

| PTGQUE4         | 0AE0  |        |                            |         | STEP    | 9<7:0>  |            |         |          |         |        |       | STEP8 | 8<7:0> |          |          |        | 0000   |

| PTGQUE5         | 0AE2  |        | STEP11<7:0> STEP10<7:0> 00 |         |         |         |            |         |          |         | 0000   |       |       |        |          |          |        |        |

| PTGQUE6         | 0AE4  |        | STEP13<7:0> STEP12<7:0>    |         |         |         |            |         |          |         | 0000   |       |       |        |          |          |        |        |

| PTGQUE7         | 0AE6  |        |                            |         | STEP    | 15<7:0> |            |         |          |         |        |       | STEP1 | 4<7:0> |          |          |        | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

## TABLE 4-20: ADC1 REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14             | Bit 13 | Bit 12  | Bit 11     | Bit 10    | Bit 9   | Bit 8        | Bit 7    | Bit 6    | Bit 5    | Bit 4     | Bit 3  | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|--------|--------------------|--------|---------|------------|-----------|---------|--------------|----------|----------|----------|-----------|--------|----------|---------|---------|---------------|

| ADC1BUF0  | 0300  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 0  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF1  | 0302  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 1  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF2  | 0304  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 2  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF3  | 0306  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 3  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF4  | 0308  |        | ADC1 Data Buffer 4 |        |         |            |           |         |              |          |          |          | xxxx      |        |          |         |         |               |

| ADC1BUF5  | 030A  |        | ADC1 Data Buffer 5 |        |         |            |           |         |              |          |          | xxxx     |           |        |          |         |         |               |

| ADC1BUF6  | 030C  |        | ADC1 Data Buffer 6 |        |         |            |           |         |              |          |          |          | xxxx      |        |          |         |         |               |

| ADC1BUF7  | 030E  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 7  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF8  | 0310  |        |                    |        |         |            |           |         |              |          |          | xxxx     |           |        |          |         |         |               |

| ADC1BUF9  | 0312  |        | ADC1 Data Buffer 9 |        |         |            |           |         |              |          |          | xxxx     |           |        |          |         |         |               |

| ADC1BUFA  | 0314  |        |                    |        |         |            |           |         | ADC1 Data Bu | Iffer 10 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFB  | 0316  |        |                    |        |         |            |           |         | ADC1 Data Bu | uffer 11 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFC  | 0318  |        |                    |        |         |            |           |         | ADC1 Data Bu | Iffer 12 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFD  | 031A  |        |                    |        |         |            |           |         | ADC1 Data Bu | Iffer 13 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFE  | 031C  |        |                    |        |         |            |           |         | ADC1 Data Bu | Iffer 14 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFF  | 031E  |        |                    |        |         |            |           |         | ADC1 Data Bu | iffer 15 |          |          |           |        |          |         |         | xxxx          |

| AD1CON1   | 0320  | ADON   | _                  | ADSIDL | ADDMABM | _          | AD12B     | FOR     | M<1:0>       | Ś        | SRC<2:0> | <b>`</b> | SSRCG     | SIMSAM | ASAM     | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322  | ١      | VCFG<2:0>          | >      | _       | _          | CSCNA     | CHP     | S<1:0>       | BUFS     |          |          | SMPI<4:0> | >      |          | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324  | ADRC   | _                  | _      |         |            | SAMC<4:03 | >       |              |          |          |          | ADCS      | <7:0>  |          |         |         | 0000          |

| AD1CHS123 | 0326  | _      | _                  | _      | _       | _          | CH123N    | NB<1:0> | CH123SB      | —        | _        | —        | _         | _      | CH123N   | A<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328  | CH0NB  | _                  | _      |         | CH0SB<4:0> |           |         |              | CH0NA    | _        | —        |           | С      | H0SA<4:0 | >       |         | 0000          |

| AD1CSSH   | 032E  | CSS31  | CSS30              | _      | _       |            | CSS26     | CSS25   | CSS24        | _        |          | _        | —         | —      | —        | —       | —       | 0000          |

| AD1CSSL   | 0330  | CSS15  | CSS14              | CSS13  | CSS12   | CSS11      | CSS10     | CSS9    | CSS8         | CSS7     | CSS6     | CSS5     | CSS4      | CSS3   | CSS2     | CSS1    | CSS0    | 0000          |

| AD1CON4   | 0332  |        | _                  | _      | _       |            | _         | _       | ADDMAEN      | -        |          |          |           | _      | D        | MABL<2: | )>      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

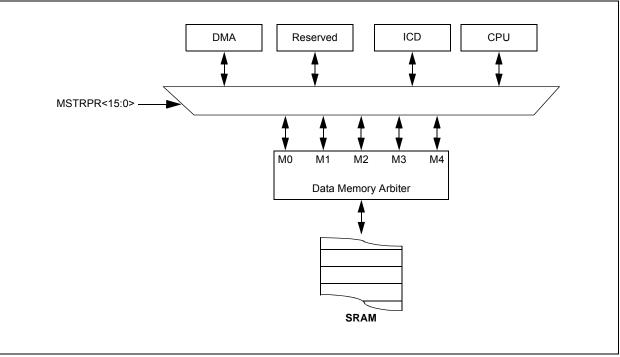

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

## FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Priority     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

## 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

#### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

## 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

#### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "*dsPIC33/PIC24 Family Reference Manual*".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

| U-0          | U-0                                                                                                 | U-0                                                              | U-0           | U-0                | U-0              | U-0             | U-0    |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|--------------------|------------------|-----------------|--------|--|--|--|--|--|

| —            | —                                                                                                   | —                                                                | —             | —                  | —                | —               | —      |  |  |  |  |  |

| bit 15       |                                                                                                     |                                                                  |               |                    |                  |                 | bit 8  |  |  |  |  |  |

|              |                                                                                                     |                                                                  |               |                    |                  |                 |        |  |  |  |  |  |

| U-0          | U-0                                                                                                 | U-0                                                              | U-0           | R-0                | R-0              | R-0             | R-0    |  |  |  |  |  |

|              |                                                                                                     | <u> </u>                                                         | _             | PWCOL3             | PWCOL2           | PWCOL1          | PWCOL0 |  |  |  |  |  |

| bit 7        |                                                                                                     |                                                                  |               |                    |                  |                 | bit 0  |  |  |  |  |  |

|              |                                                                                                     |                                                                  |               |                    |                  |                 |        |  |  |  |  |  |

| Legend:      |                                                                                                     |                                                                  |               |                    |                  |                 |        |  |  |  |  |  |

| R = Readab   | le bit                                                                                              | W = Writable                                                     | bit           | U = Unimpler       | mented bit, read | as '0'          |        |  |  |  |  |  |

| -n = Value a | t POR                                                                                               | '1' = Bit is set                                                 |               | '0' = Bit is cle   | ared             | x = Bit is unkr | nown   |  |  |  |  |  |

|              |                                                                                                     |                                                                  |               |                    |                  |                 |        |  |  |  |  |  |

| bit 15-4     | Unimplemen                                                                                          | ted: Read as '                                                   | 0'            |                    |                  |                 |        |  |  |  |  |  |

| bit 3        | PWCOL3: DI                                                                                          | MA Channel 3 F                                                   | Peripheral Wi | rite Collision Fla | ag bit           |                 |        |  |  |  |  |  |

|              |                                                                                                     | lision is detecte                                                |               |                    |                  |                 |        |  |  |  |  |  |

|              |                                                                                                     | collision is dete                                                |               |                    |                  |                 |        |  |  |  |  |  |

| bit 2        |                                                                                                     |                                                                  | •             | rite Collision Fla | ag bit           |                 |        |  |  |  |  |  |

|              |                                                                                                     | lision is detecte<br>collision is dete                           |               |                    |                  |                 |        |  |  |  |  |  |

| bit 1        |                                                                                                     |                                                                  |               | rito Collision Els | a hit            |                 |        |  |  |  |  |  |

| DILI         | <b>PWCOL1:</b> DMA Channel 1 Peripheral Write Collision Flag bit<br>1 = Write collision is detected |                                                                  |               |                    |                  |                 |        |  |  |  |  |  |

|              |                                                                                                     | 0 =  No write collision is detected                              |               |                    |                  |                 |        |  |  |  |  |  |

| bit 0        | PWCOL0: DI                                                                                          | <b>PWCOL0:</b> DMA Channel 0 Peripheral Write Collision Flag bit |               |                    |                  |                 |        |  |  |  |  |  |

|              |                                                                                                     | lision is detecte                                                | •             | -                  | <b>č</b>         |                 |        |  |  |  |  |  |

|              | 0 = No write                                                                                        | collision is dete                                                | ected         |                    |                  |                 |        |  |  |  |  |  |

|              |                                                                                                     |                                                                  |               |                    |                  |                 |        |  |  |  |  |  |

## REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

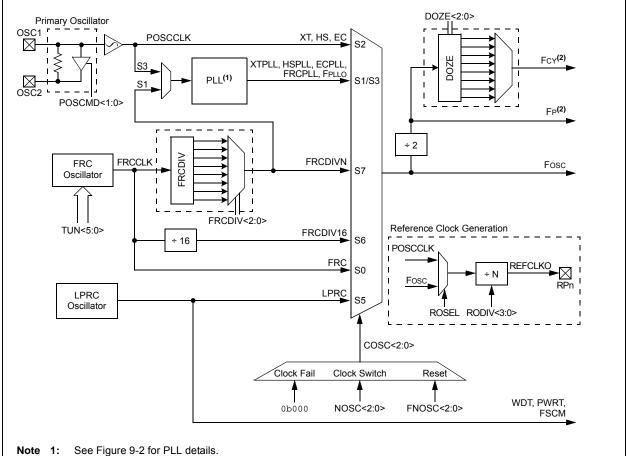

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

## **10.0 POWER-SAVING FEATURES**

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | Sleep mode |  |

|--------|-------------|---|-----|-----|--------|------|------------|--|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | Idle mode  |  |

## 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

## 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

| REGISTER     | TU-5: PIVID6                      | . PERIPHER       |                           | DISABLE C                               | UNIROL RE             | GISIER 6              |                       |  |

|--------------|-----------------------------------|------------------|---------------------------|-----------------------------------------|-----------------------|-----------------------|-----------------------|--|

| U-0          | U-0                               | U-0              | U-0                       | U-0                                     | R/W-0                 | R/W-0                 | R/W-0                 |  |

| —            | —                                 | —                | —                         | —                                       | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |  |

| bit 15       |                                   |                  |                           |                                         |                       |                       | bit 8                 |  |

|              |                                   |                  |                           |                                         |                       |                       |                       |  |

| U-0          | U-0                               | U-0              | U-0                       | U-0                                     | U-0                   | U-0                   | U-0                   |  |

|              |                                   |                  |                           |                                         |                       |                       |                       |  |

| bit 7        |                                   |                  |                           |                                         |                       |                       | bit 0                 |  |

|              |                                   |                  |                           |                                         |                       |                       |                       |  |

| Legend:      |                                   |                  |                           |                                         |                       |                       |                       |  |

| R = Readab   | R = Readable bit W = Writable bit |                  |                           |                                         | nented bit, read      | l as '0'              |                       |  |

| -n = Value a | t POR                             | '1' = Bit is set |                           | '0' = Bit is cleared x = Bit is unknown |                       |                       |                       |  |

|              |                                   |                  |                           |                                         |                       |                       |                       |  |

| bit 15-11    | Unimplement                       | ted: Read as '   | כ'                        |                                         |                       |                       |                       |  |

| bit 10       | PWM3MD: P\                        | NM3 Module D     | isable bit <sup>(1)</sup> |                                         |                       |                       |                       |  |

|              | 1 = PWM3 mo                       | odule is disable | ed                        |                                         |                       |                       |                       |  |

|              | 0 = PWM3 mo                       | odule is enable  | d                         |                                         |                       |                       |                       |  |

| bit 9        | PWM2MD: P\                        | NM2 Module D     | isable bit <sup>(1)</sup> |                                         |                       |                       |                       |  |

|              | 1 = PWM2 mo                       | odule is disable | ed                        |                                         |                       |                       |                       |  |

|              | 0 = PWM2 mo                       | odule is enable  | d                         |                                         |                       |                       |                       |  |

| bit 8        | PWM1MD: P\                        | NM1 Module D     | isable bit <sup>(1)</sup> |                                         |                       |                       |                       |  |

|              |                                   | odule is disable |                           |                                         |                       |                       |                       |  |

|              | 0 = PWM1 mo                       | odule is enable  | d                         |                                         |                       |                       |                       |  |

| bit 7-0      | Unimplement                       | ted: Read as '   | כ'                        |                                         |                       |                       |                       |  |

## REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

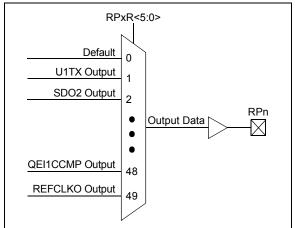

#### 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

#### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

#### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC2R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| ·                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 8                                                                                                                                                                                                                                                                                                                                                                                               |  |

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC1R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit C                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| e bit                        | W = Writable b                                                                                                                                                         | it                                                                                                                                                                                                                                                                                                                                       | U = Unimplem                                                                                                                                                                                             | nented bit, rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| POR                          | '1' = Bit is set                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                        | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| •                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | nbers)                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                              |                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |