Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc206-h-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

## 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

| IABLE 4   | -14:  | PVVIVI G | ENERA  | IUR Z R | EGIST     |          | FOR as  | PIC33EP  |            | 202/202   |         | 16246   | PXXX    |          |          | CES ONL | _ T     |               |

|-----------|-------|----------|--------|---------|-----------|----------|---------|----------|------------|-----------|---------|---------|---------|----------|----------|---------|---------|---------------|

| File Name | Addr. | Bit 15   | Bit 14 | Bit 13  | Bit 12    | Bit 11   | Bit 10  | Bit 9    | Bit 8      | Bit 7     | Bit 6   | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

| PWMCON2   | 0C40  | FLTSTAT  | CLSTAT | TRGSTAT | FLTIEN    | CLIEN    | TRGIEN  | ITB      | MDCS       | DTC       | <1:0>   | DTCP    | _       | MTBS     | CAM      | XPRES   | IUE     | 0000          |

| IOCON2    | 0C42  | PENH     | PENL   | POLH    | POLL      | PMOD     | 0<1:0>  | OVRENH   | OVRENL     | OVRDA     | \T<1:0> | FLTD    | \T<1:0> | CLDA     | AT<1:0>  | SWAP    | OSYNC   | C000          |

| FCLCON2   | 0C44  | _        |        | (       | CLSRC<4:0 | )>       |         | CLPOL    | CLMOD      |           | FLT     | SRC<4:0 | >       |          | FLTPOL   | FLTMO   | D<1:0>  | 00F8          |

| PDC2      | 0C46  |          |        |         |           |          |         |          | PDC2<15:0> |           |         |         |         |          |          |         |         | 0000          |

| PHASE2    | 0C48  |          |        |         |           |          |         | Р        | HASE2<15:0 | )>        |         |         |         |          |          |         |         | 0000          |

| DTR2      | 0C4A  | _        | _      |         |           |          |         |          | [          | DTR2<13:0 | >       |         |         |          |          |         |         | 0000          |

| ALTDTR2   | 0C4C  | _        | _      |         |           |          |         |          | AL         | TDTR2<13  | :0>     |         |         |          |          |         |         | 0000          |

| TRIG2     | 0C52  |          |        |         |           |          |         | TI       | RGCMP<15:0 | )>        |         |         |         |          |          |         |         | 0000          |

| TRGCON2   | 0C54  |          | TRGDI  | V<3:0>  |           | _        | —       | _        | _          | _         | -       |         |         | TRO      | GSTRT<5: | 0>      |         | 0000          |

| LEBCON2   | 0C5A  | PHR      | PHF    | PLR     | PLF       | FLTLEBEN | CLLEBEN | _        | _          | _         | -       | BCH     | BCL     | BPHH     | BPHL     | BPLH    | BPLL    | 0000          |

| LEBDLY2   | 0C5C  | _        | _      | _       | LEB<11:0> |          |         |          |            |           |         |         |         | 0000     |          |         |         |               |

| AUXCON2   | 0C5E  | _        | _      | —       | —         |          | BLANK   | SEL<3:0> |            | _         | —       |         | CHOPS   | SEL<3:0> |          | CHOPHEN | CHOPLEN | 0000          |

I- DIGGOEDV/VMOGOV/EGV AND DIGGOEDV/VMOGOV DEVICED ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12       | Bit 11                                       | Bit 10  | Bit 9  | Bit 8      | Bit 7     | Bit 6    | Bit 5   | Bit 4   | Bit 3 | Bit 2    | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------|---------|--------|---------|--------------|----------------------------------------------|---------|--------|------------|-----------|----------|---------|---------|-------|----------|-------|--------|---------------|

| PWMCON3   | 0C60  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN       | CLIEN                                        | TRGIEN  | ITB    | MDCS       | DTC<      | <1:0>    | DTCP    | —       | MTBS  | CAM      | XPRES | IUE    | 0000          |

| IOCON3    | 0C62  | PENH    | PENL   | POLH    | POLL         | PMOD                                         | )<1:0>  | OVRENH | OVRENL     | OVRDA     | T<1:0>   | FLTD    | AT<1:0> | CLD   | AT<1:0>  | SWAP  | OSYNC  | C000          |

| FCLCON3   | 0C64  |         |        | (       | CLSRC<4:0    | )>                                           |         | CLPOL  | CLMOD      |           | FLT      | SRC<4:0 | >       |       | FLTPOL   | FLTMO | D<1:0> | 00F8          |

| PDC3      | 0C66  |         |        |         |              |                                              |         |        | PDC3<15:0> | •         |          |         |         |       |          |       |        | 0000          |

| PHASE3    | 0C68  |         |        |         | PHASE3<15:0> |                                              |         |        |            |           |          |         | 0000    |       |          |       |        |               |

| DTR3      | 0C6A  |         | —      |         |              |                                              |         |        | [          | DTR3<13:0 | >        |         |         |       |          |       |        | 0000          |

| ALTDTR3   | 0C6C  |         | —      |         |              |                                              |         |        | AL         | TDTR3<13  | :0>      |         |         |       |          |       |        | 0000          |

| TRIG3     | 0C72  |         |        |         |              |                                              |         | Т      | RGCMP<15:  | 0>        |          |         |         |       |          |       |        | 0000          |

| TRGCON3   | 0C74  |         | TRGDI  | V<3:0>  |              | _                                            | _       | _      | _          | _         | _        |         |         | TR    | GSTRT<5: | 0>    |        | 0000          |

| LEBCON3   | 0C7A  | PHR     | PHF    | PLR     | PLF          | FLTLEBEN                                     | CLLEBEN | —      | —          |           | —        | BCH     | BCL     | BPHH  | BPHL     | BPLH  | BPLL   | 0000          |

| LEBDLY3   | 0C7C  |         | —      | _       | _            |                                              |         |        |            |           | LEB<11:0 | )>      |         |       |          |       |        | 0000          |

| AUXCON3   | 0C7E  |         | —      | —       | —            | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPL |         |        |            |           |          | CHOPLEN | 0000    |       |          |       |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

.

----

.

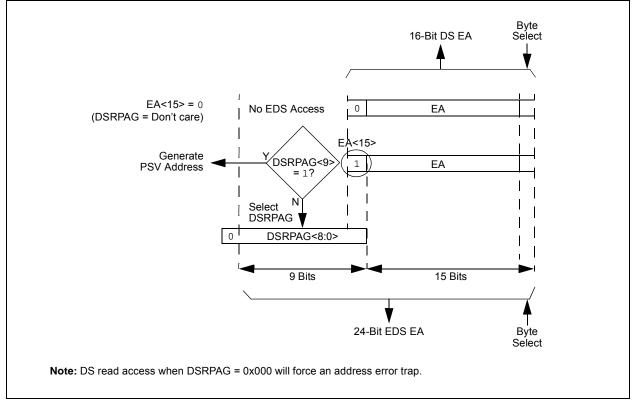

#### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

NOTES:

## REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                                                                       | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|---------------------------------------------------------------------------|------------------|----------------------------------------------------------|-------|--------------|-----------------|-----------|-------|

|                                                                           |                  |                                                          |       | DTCMP3R<6:0  | )>              |           |       |

| bit 15                                                                    |                  |                                                          |       |              |                 |           | bit 8 |

| U-0                                                                       | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

| 0-0                                                                       | R/W-0            | R/W-0                                                    | -     | DTCMP2R<6:0  |                 | R/W-0     | R/W-U |

| bit 7                                                                     |                  |                                                          |       |              | 17              |           | bit 0 |

| bit i                                                                     |                  |                                                          |       |              |                 |           | bit 0 |

| Legend:                                                                   |                  |                                                          |       |              |                 |           |       |

| R = Readab                                                                | ole bit          | W = Writable                                             | bit   | U = Unimplem | nented bit, rea | ad as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |                  |                                                          |       |              |                 |           |       |

|                                                                           |                  |                                                          |       |              |                 |           |       |

|                                                                           |                  | nput tied to CMI                                         |       |              |                 |           |       |

| bit 7                                                                     | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |       |              |                 |           |       |

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|--------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | PTGT0L | _IM<15:8>         |                 |                 |       |

| bit 15          |       |                  |        |                   |                 |                 | bit 8 |

|                 |       |                  |        |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PTGT0  | LIM<7:0>          |                 |                 |       |

| bit 7           |       |                  |        |                   |                 |                 | bit 0 |

|                 |       |                  |        |                   |                 |                 |       |

| Legend:         |       |                  |        |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit    | U = Unimplem      | ented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |        | '0' = Bit is clea | red             | x = Bit is unkr | nown  |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| PTGT1LIM<15:8> |       |       |       |       |       |       |       |  |  |  |  |

| bit 15         |       |       |       |       |       |       | bit 8 |  |  |  |  |

|                |       |       |       |       |       |       |       |  |  |  |  |

| R/W-0 | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|-------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|       | PTGT1LIM<7:0> |       |       |       |       |       |       |  |  |  |  |  |

| bit 7 |               |       |       |       |       |       | bit 0 |  |  |  |  |  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit C |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

## REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGHOL | _D<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

| R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|       | PTGHOLD<7:0> |       |       |       |       |       |       |  |  |  |  |

| bit 7 |              |       |       |       |       |       | bit 0 |  |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

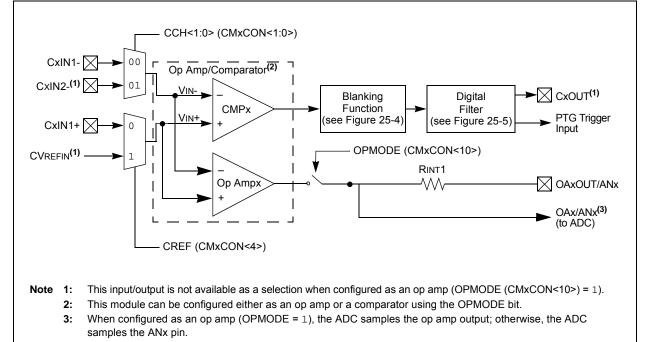

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

## FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

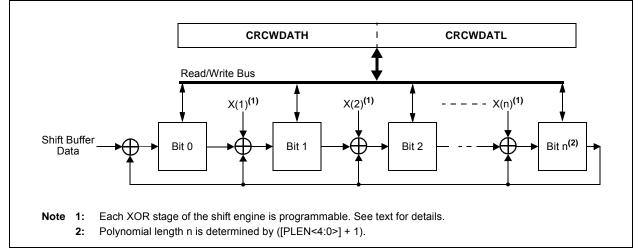

#### 26.1 Overview

The CRC module can be programmed for CRC polynomials of up to the 32nd order, using up to 32 bits. Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation; functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing the bit disables the XOR.

For example, consider two CRC polynomials, one a 16-bit equation and the other a 32-bit equation:

$$\begin{array}{c} x16+x12+x5+1\\ \text{and}\\ x32+x26+x23+x22+x16+x12+x11+x10+x8+x7\\ +x5+x4+x2+x+1 \end{array}$$

To program these polynomials into the CRC generator, set the register bits as shown in Table 26-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The 0 bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length N, it is assumed that the *N*th bit will always be used, regardless of the bit setting. Therefore, for a polynomial length of 32, there is no 32nd bit in the CRCxOR register.

# TABLE 26-1:CRC SETUP EXAMPLES FOR16 AND 32-BIT POLYNOMIAL

| CRC Control | Bit Values             |                        |  |  |  |  |

|-------------|------------------------|------------------------|--|--|--|--|

| Bits        | 16-bit<br>Polynomial   | 32-bit<br>Polynomial   |  |  |  |  |

| PLEN<4:0>   | 01111                  | 11111                  |  |  |  |  |

| X<31:16>    | 0000 0000<br>0000 000x | 0000 0100<br>1100 0001 |  |  |  |  |

| X<15:0>     | 0001 0000<br>0010 000x | 0001 1101<br>1011 011x |  |  |  |  |

## 26.2 Programmable CRC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 26.2.1 KEY RESOURCES

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed, or an SFR register is read. In these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157). For more information on instructions that take more than one instruction cycle to execute, refer to **"CPU"** (DS70359) in the *"dsPIC33/PIC24 Family Reference Manual"*, particularly the **"Instruction Flow Types"** section.

| Field               | Description                                                                          |

|---------------------|--------------------------------------------------------------------------------------|

| #text               | Means literal defined by "text"                                                      |

| (text)              | Means "content of text"                                                              |

| [text]              | Means "the location addressed by text"                                               |

| {}                  | Optional field or operation                                                          |

| $a \in \{b, c, d\}$ | a is selected from the set of values b, c, d                                         |

| <n:m></n:m>         | Register bit field                                                                   |

| .b                  | Byte mode selection                                                                  |

| .d                  | Double-Word mode selection                                                           |

| .S                  | Shadow register select                                                               |

| .w                  | Word mode selection (default)                                                        |

| Acc                 | One of two accumulators {A, B}                                                       |

| AWB                 | Accumulator write back destination address register ∈ {W13, [W13]+ = 2}              |

| bit4                | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z     | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr                | Absolute address, label or expression (resolved by the linker)                       |

| f                   | File register address ∈ {0x00000x1FFF}                                               |

| lit1                | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4                | 4-bit unsigned literal ∈ {015}                                                       |

| lit5                | 5-bit unsigned literal ∈ {031}                                                       |

| lit8                | 8-bit unsigned literal ∈ {0255}                                                      |

| lit10               | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |

| lit14               | 14-bit unsigned literal ∈ {016384}                                                   |

| lit16               | 16-bit unsigned literal ∈ {065535}                                                   |

| lit23               | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |

| None                | Field does not require an entry, can be blank                                        |

| OA, OB, SA, SB      | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |

| PC                  | Program Counter                                                                      |

| Slit10              | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16              | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6               | 6-bit signed literal ∈ {-1616}                                                       |

| Wb                  | Base W register ∈ {W0W15}                                                            |

| Wd                  | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo                 | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

#### TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

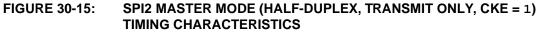

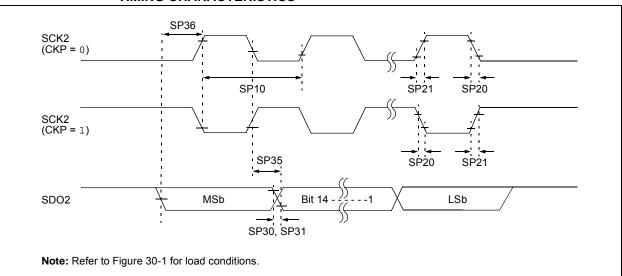

#### TABLE 30-34: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | (unless o | otherwise           | <b>stated)</b><br>ature -4 | 0°C ≤ Ta | <b>0V to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +125°C for Extended |

|--------------------|-----------------------|----------------------------------------------|-----------|---------------------|----------------------------|----------|----------------------------------------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.      | Typ. <sup>(2)</sup> | Max.                       | Units    | Conditions                                                           |

| SP10               | FscP                  | Maximum SCK2 Frequency                       | —         | _                   | 15                         | MHz      | (Note 3)                                                             |

| SP20               | TscF                  | SCK2 Output Fall Time                        | —         | —                   | _                          | ns       | See Parameter DO32<br>(Note 4)                                       |

| SP21               | TscR                  | SCK2 Output Rise Time                        | —         | —                   | _                          | ns       | See Parameter DO31<br>(Note 4)                                       |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                   | —         | —                   | _                          | ns       | See Parameter DO32<br>(Note 4)                                       |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                   | -         | _                   |                            | ns       | See Parameter DO31<br>(Note 4)                                       |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge    | —         | 6                   | 20                         | ns       |                                                                      |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge | 30        | —                   | _                          | ns       |                                                                      |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

#### FIGURE 30-16: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

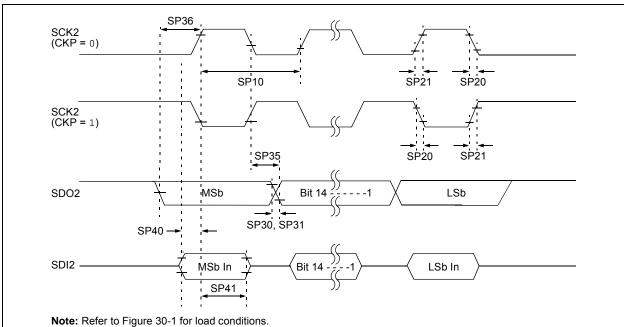

# TABLE 30-35:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS

| АС СНА | AC CHARACTERISTICS    |                                               |      | Operatin<br>otherwise<br>otemperat | <b>stated)</b><br>:ure -40° | °C ≤ TA ≤ | ′ <b>to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------|-----------------------|-----------------------------------------------|------|------------------------------------|-----------------------------|-----------|-----------------------------------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                 | Min. | Typ. <sup>(2)</sup>                | Max.                        | Units     | Conditions                                                      |

| SP10   | FscP                  | Maximum SCK2 Frequency                        | _    | _                                  | 9                           | MHz       | (Note 3)                                                        |

| SP20   | TscF                  | SCK2 Output Fall Time                         | —    | —                                  |                             | ns        | See Parameter DO32 (Note 4)                                     |

| SP21   | TscR                  | SCK2 Output Rise Time                         | —    | —                                  | —                           | ns        | See Parameter DO31 (Note 4)                                     |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                    | —    | —                                  | —                           | ns        | See Parameter DO32 (Note 4)                                     |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                    | —    | —                                  | —                           | ns        | See Parameter DO31<br>(Note 4)                                  |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge        | —    | 6                                  | 20                          | ns        |                                                                 |

| SP36   | TdoV2sc,<br>TdoV2scL  | SDO2 Data Output Setup to<br>First SCK2 Edge  | 30   |                                    | —                           | ns        |                                                                 |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge | 30   | —                                  |                             | ns        |                                                                 |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge     | 30   |                                    | _                           | ns        |                                                                 |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPI2 pins.

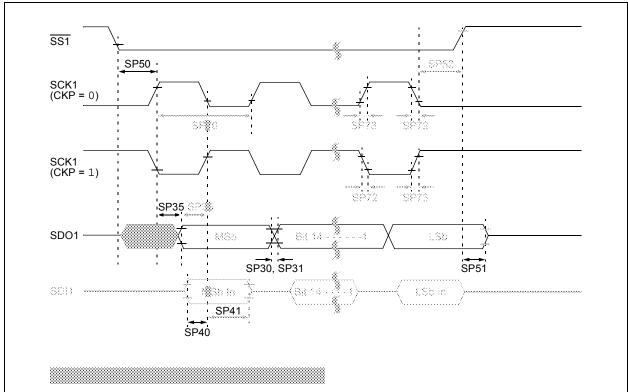

#### FIGURE 30-28: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACTERISTICS |                      | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \\ \end{array} $ |                              |                     |                              |        |                                            |

|--------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------|------------------------------|--------|--------------------------------------------|

| Param<br>No.       | Symbol               | Characteristic                                                                                                                                                                                                                                                                                     | Min.                         | Тур. <sup>(2)</sup> | Max.                         | Units  | Conditions                                 |

| Op Am              | p DC Chara           | cteristics                                                                                                                                                                                                                                                                                         |                              |                     |                              |        |                                            |

| CM40               | VCMR                 | Common-Mode Input<br>Voltage Range                                                                                                                                                                                                                                                                 | AVss                         | _                   | AVDD                         | V      |                                            |

| CM41               | CMRR                 | Common-Mode<br>Rejection Ratio <sup>(3)</sup>                                                                                                                                                                                                                                                      | —                            | 40                  | —                            | db     | VCM = AVDD/2                               |

| CM42               | VOFFSET              | Op Amp Offset<br>Voltage <sup>(3)</sup>                                                                                                                                                                                                                                                            | —                            | ±5                  | —                            | mV     |                                            |

| CM43               | Vgain                | Open-Loop Voltage<br>Gain <sup>(3)</sup>                                                                                                                                                                                                                                                           | _                            | 90                  | _                            | db     |                                            |

| CM44               | los                  | Input Offset Current                                                                                                                                                                                                                                                                               | _                            | -                   | _                            | _      | See pad leakage currents in Table 30-11    |

| CM45               | lв                   | Input Bias Current                                                                                                                                                                                                                                                                                 | —                            | _                   | _                            | _      | See pad leakage currents in Table 30-11    |

| CM46               | Ιουτ                 | Output Current                                                                                                                                                                                                                                                                                     | _                            |                     | 420                          | μA     | With minimum value of RFEEDBACK (CM48)     |

| CM48               | RFEEDBACK            | Feedback Resistance<br>Value                                                                                                                                                                                                                                                                       | 8                            | -                   | _                            | kΩ     |                                            |

| CM49a              | VOADC                | Output Voltage                                                                                                                                                                                                                                                                                     | AVss + 0.077                 |                     | AVDD - 0.077                 | V      | Ιουτ = 420 μΑ                              |

|                    |                      | Measured at OAx Using ADC <sup>(3,4)</sup>                                                                                                                                                                                                                                                         | AVss + 0.037<br>AVss + 0.018 |                     | AVDD – 0.037<br>AVDD – 0.018 | V<br>V | Ιουτ = 200 μΑ<br>Ιουτ = 100 μΑ             |

| CM49b              | Vout                 | Output Voltage                                                                                                                                                                                                                                                                                     | AVss + 0.210                 | _                   | AVDD - 0.210                 | V      | Ιουτ = 420 μΑ                              |

|                    |                      | Measured at OAxOUT<br>Pin <sup>(3,4,5)</sup>                                                                                                                                                                                                                                                       | AVss + 0.100<br>AVss + 0.050 | _                   | AVDD – 0.100<br>AVDD – 0.050 | V<br>V | Ιουτ = 200 μΑ<br>Ιουτ = 100 μΑ             |

| CM51               | RINT1 <sup>(6)</sup> | Internal Resistance 1<br>(Configuration A<br>and B) <sup>(3,4,5)</sup>                                                                                                                                                                                                                             | 198                          | 264                 | 317                          | Ω      | Min = -40°C<br>Typ = +25°C<br>Max = +125°C |

#### TABLE 30-53: OP AMP/COMPARATOR SPECIFICATIONS (CONTINUED)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** Parameter is characterized but not tested in manufacturing.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: Resistances can vary by ±10% between op amps.

| AC CHA       | ARACTER | RISTICS                                                                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |       |       |                                         |

|--------------|---------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|-------|-------|-----------------------------------------|

|              |         |                                                                                                     |                                                       |         |       |       |                                         |

| Param<br>No. | Symbol  | Characteristic                                                                                      | Min.                                                  | Тур.    | Max.  | Units | Conditions                              |

|              |         | Cloci                                                                                               | k Parame                                              | eters   |       |       |                                         |

| AD50         | TAD     | ADC Clock Period                                                                                    | 76                                                    | _       | _     | ns    |                                         |

| AD51         | tRC     | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                    |                                                       | 250     | _     | ns    |                                         |

|              |         | Conv                                                                                                | version F                                             | Rate    |       | •     |                                         |

| AD55         | tCONV   | Conversion Time                                                                                     |                                                       | 12 Tad  | _     |       |                                         |

| AD56         | FCNV    | Throughput Rate                                                                                     | _                                                     | —       | 1.1   | Msps  | Using simultaneous sampling             |

| AD57a        | TSAMP   | Sample Time when Sampling any ANx Input                                                             | 2 Tad                                                 | —       | _     | —     |                                         |

| AD57b        | TSAMP   | Sample Time when Sampling the Op Amp Outputs (Configuration A and Configuration B) <sup>(4,5)</sup> | 4 Tad                                                 | _       | —     | —     |                                         |

|              |         | Timin                                                                                               | g Param                                               | eters   |       |       |                                         |

| AD60         | tPCS    | Conversion Start from Sample<br>Trigger <sup>(2,3)</sup>                                            | 2 Tad                                                 | —       | 3 Tad | _     | Auto-convert trigger is<br>not selected |

| AD61         | tPSS    | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2,3))</sup>                                    | 2 Tad                                                 | —       | 3 Tad | —     |                                         |

| AD62         | tcss    | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2,3)</sup>                                | _                                                     | 0.5 Tad |       | —     |                                         |

| AD63         | tdpu    | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup>                           |                                                       | —       | 20    | μs    | (Note 6)                                |

## TABLE 30-61: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

## TABLE 30-62: DMA MODULE TIMING REQUIREMENTS

|              |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |            |

|--------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No. | Characteristic                 | Min.                                                                                                                                                                                                                                                                                  | Тур. <sup>(1)</sup> | Max. | Units | Conditions |

| DM1          | DMA Byte/Word Transfer Latency | 1 Tcy <b>(2)</b>                                                                                                                                                                                                                                                                      | -                   | _    | ns    |            |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because DMA transfers use the CPU data bus, this time is dependent on other functions on the bus.

<sup>© 2011-2013</sup> Microchip Technology Inc.

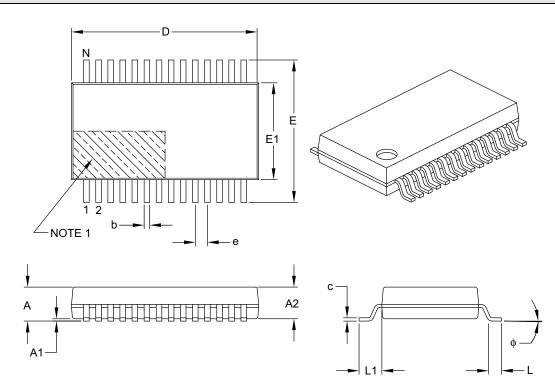

#### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units         |          |          | 6     |  |

|--------------------------|---------------|----------|----------|-------|--|

| Dime                     | ension Limits | MIN      | NOM      | MAX   |  |

| Number of Pins           | N             |          | 28       |       |  |

| Pitch                    | е             |          | 0.65 BSC |       |  |

| Overall Height           | A             | -        | -        | 2.00  |  |

| Molded Package Thickness | A2            | 1.65     | 1.75     | 1.85  |  |

| Standoff                 | A1            | 0.05     | -        | -     |  |

| Overall Width            | E             | 7.40     | 7.80     | 8.20  |  |

| Molded Package Width     | E1            | 5.00     | 5.30     | 5.60  |  |

| Overall Length           | D             | 9.90     | 10.20    | 10.50 |  |

| Foot Length              | L             | 0.55     | 0.75     | 0.95  |  |

| Footprint                | L1            | 1.25 REF |          |       |  |

| Lead Thickness           | С             | 0.09     | -        | 0.25  |  |

| Foot Angle               | ф             | 0°       | 4°       | 8°    |  |

| Lead Width               | b             | 0.22     | -        | 0.38  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

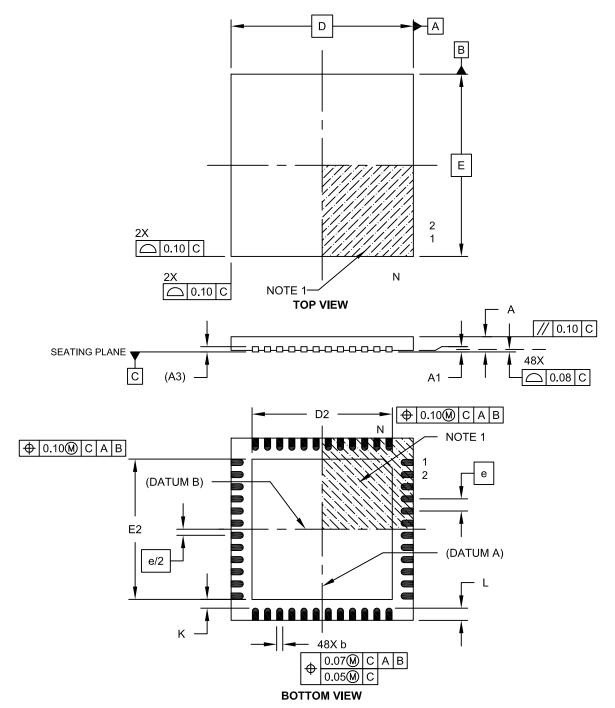

#### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2

64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

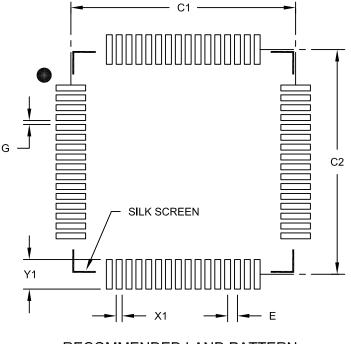

RECOMMENDED LAND PATTERN

|                          | N  | <b>ILLIMETER</b> | S        |      |

|--------------------------|----|------------------|----------|------|

| Dimension Limits         |    | MIN              | NOM      | MAX  |

| Contact Pitch            | E  |                  | 0.50 BSC |      |

| Contact Pad Spacing      | C1 |                  | 11.40    |      |

| Contact Pad Spacing      | C2 |                  | 11.40    |      |

| Contact Pad Width (X64)  | X1 |                  |          | 0.30 |

| Contact Pad Length (X64) | Y1 |                  |          | 1.50 |

| Distance Between Pads    | G  | 0.20             |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

## APPENDIX A: REVISION HISTORY

## **Revision A (April 2011)**

This is the initial released version of the document.

## Revision B (July 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-1.

## TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                                                     | Update Description                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Digital Signal Controllers<br>and Microcontrollers" | Changed all pin diagrams references of VLAP to TLA.                                                                                                                                                                                                                                                                     |

| Section 4.0 "Memory<br>Organization"                                             | Updated the All Resets values for CLKDIV and PLLFBD in the System Control Register Map (see Table 4-35).                                                                                                                                                                                                                |

| Section 5.0 "Flash Program<br>Memory"                                            | Updated "one word" to "two words" in the first paragraph of <b>Section 5.2 "RTSP Operation</b> ".                                                                                                                                                                                                                       |

| Section 9.0 "Oscillator<br>Configuration"                                        | Updated the PLL Block Diagram (see Figure 9-2).<br>Updated the Oscillator Mode, Fast RC Oscillator (FRC) with divide-by-N and PLL<br>(FRCPLL), by changing (FRCDIVN + PLL) to (FRCPLL).                                                                                                                                 |

|                                                                                  | Changed (FRCDIVN + PLL) to (FRCPLL) for COSC<2:0> = 001 and NOSC<2:0> = 001 in the Oscillator Control Register (see Register 9-1).                                                                                                                                                                                      |

|                                                                                  | Changed the POR value from 0 to 1 for the DOZE<1:0> bits, from 1 to 0 for the FRCDIV<0> bit, and from 0 to 1 for the PLLPOST<0> bit; Updated the default definitions for the DOZE<2:0> and FRCDIV<2:0> bits and updated all bit definitions for the PLLPOST<1:0> bits in the Clock Divisor Register (see Register 9-2). |

|                                                                                  | Changed the POR value from 0 to 1 for the PLLDIV<5:4> bits and updated the default definitions for all PLLDIV<8:0> bits in the PLL Feedback Division Register (see Register 9-2).                                                                                                                                       |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                            | Updated the bit definitions for the IRNG<1:0> bits in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                            |

| Section 25.0 "Op amp/<br>Comparator Module"                                      | Updated the voltage reference block diagrams (see Figure 25-1 and Figure 25-2).                                                                                                                                                                                                                                         |