Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256KB (85.5K x 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

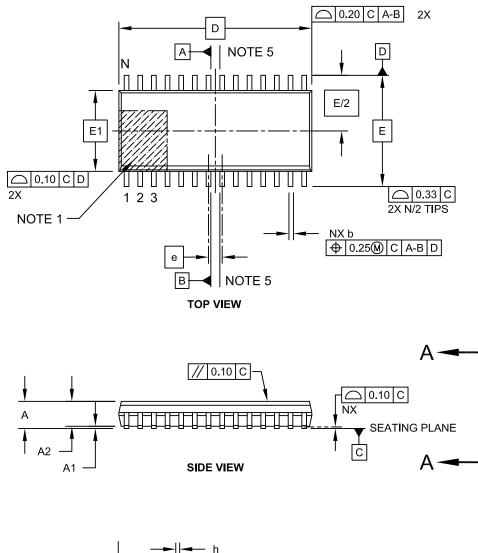

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc206t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE        | 4-2:  | CPU C  | CORE RE | EGISTER | R MAP F | FOR PIC | 24EPX) | XGP/M | C20X D   | EVICES   | ONLY   |       |           |          |       |       |       |               |

|--------------|-------|--------|---------|---------|---------|---------|--------|-------|----------|----------|--------|-------|-----------|----------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7    | Bit 6  | Bit 5 | Bit 4     | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| W0           | 0000  |        |         |         |         |         |        |       | W0 (WR   | EG)      |        |       |           |          |       |       |       | xxxx          |

| W1           | 0002  |        |         |         |         |         |        |       | W1       |          |        |       |           |          |       |       |       | xxxx          |

| W2           | 0004  |        |         |         |         |         |        |       | W2       |          |        |       |           |          |       |       |       | xxxx          |

| W3           | 0006  |        |         |         |         |         |        |       | W3       |          |        |       |           |          |       |       |       | xxxx          |

| W4           | 0008  |        |         |         |         |         |        |       | W4       |          |        |       |           |          |       |       |       | xxxx          |

| W5           | 000A  |        |         |         |         |         |        |       | W5       |          |        |       |           |          |       |       |       | xxxx          |

| W6           | 000C  |        |         |         |         |         |        |       | W6       |          |        |       |           |          |       |       |       | xxxx          |

| W7           | 000E  |        |         |         |         |         |        |       | W7       |          |        |       |           |          |       |       |       | xxxx          |

| W8           | 0010  |        |         |         |         |         |        |       | W8       |          |        |       |           |          |       |       |       | xxxx          |

| W9           | 0012  |        |         |         |         |         |        |       | W9       |          |        |       |           |          |       |       |       | xxxx          |

| W10          | 0014  |        |         |         |         |         |        |       | W10      |          |        |       |           |          |       |       |       | xxxx          |

| W11          | 0016  |        |         |         |         |         |        |       | W11      |          |        |       |           |          |       |       |       | xxxx          |

| W12          | 0018  |        |         |         |         |         |        |       | W12      |          |        |       |           |          |       |       |       | xxxx          |

| W13          | 001A  |        |         |         |         |         |        |       | W13      |          |        |       |           |          |       |       |       | xxxx          |

| W14          | 001C  |        |         |         |         |         |        |       | W14      |          |        |       |           |          |       |       |       | xxxx          |

| W15          | 001E  |        |         |         |         |         |        |       | W15      |          |        |       |           |          |       |       |       | xxxx          |

| SPLIM        | 0020  |        |         |         |         |         |        |       | SPLIM<1  | 5:0>     |        |       |           |          |       |       |       | 0000          |

| PCL          | 002E  |        |         |         |         |         |        | P     | CL<15:1> |          |        |       |           |          |       |       | —     | 0000          |

| PCH          | 0030  | —      | -       | _       | _       | —       | —      | —     | —        | _        |        |       |           | PCH<6:0> |       |       |       | 0000          |

| DSRPAG       | 0032  | —      | -       | _       | _       | —       | —      |       |          |          |        | DSRPA | G<9:0>    |          |       |       |       | 0001          |

| DSWPAG       | 0034  | _      |         |         |         | _       |        | _     |          |          |        | DS    | SWPAG<8:0 | >        |       |       |       | 0001          |

| RCOUNT       | 0036  |        |         |         |         |         |        |       | RCOUNT<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

| SR           | 0042  | _      |         |         |         | —       |        | —     | DC       | IPL2     | IPL1   | IPL0  | RA        | N        | OV    | Z     | С     | 0000          |

| CORCON       | 0044  | VAR    | _       | -       | _       | —       |        | —     | _        | -        | _      | —     | -         | IPL3     | SFA   | —     | _     | 0020          |

| DISICNT      | 0052  | _      | _       |         |         |         |        |       |          | DISICNT< | :13:0> |       |           |          |       |       |       | 0000          |

| TBLPAG       | 0054  | _      | _       | -       | _       | —       |        | —     | _        |          |        |       | TBLPA     | G<7:0>   |       |       |       | 0000          |

| MSTRPR       | 0058  |        |         |         |         |         |        |       | MSTRPR<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

#### **D** I -4.0 - -

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4   | -14:  | PVVIVI G | ENERA  | IUR Z R | EGIST     |          | FOR as  | PIC33EP  |            | 202/202   |          | 16246   | PXXX    |          |          | CES ONL | _ T     |               |

|-----------|-------|----------|--------|---------|-----------|----------|---------|----------|------------|-----------|----------|---------|---------|----------|----------|---------|---------|---------------|

| File Name | Addr. | Bit 15   | Bit 14 | Bit 13  | Bit 12    | Bit 11   | Bit 10  | Bit 9    | Bit 8      | Bit 7     | Bit 6    | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

| PWMCON2   | 0C40  | FLTSTAT  | CLSTAT | TRGSTAT | FLTIEN    | CLIEN    | TRGIEN  | ITB      | MDCS       | DTC       | <1:0>    | DTCP    | _       | MTBS     | CAM      | XPRES   | IUE     | 0000          |

| IOCON2    | 0C42  | PENH     | PENL   | POLH    | POLL      | PMOD     | 0<1:0>  | OVRENH   | OVRENL     | OVRDA     | \T<1:0>  | FLTD    | \T<1:0> | CLDA     | AT<1:0>  | SWAP    | OSYNC   | C000          |

| FCLCON2   | 0C44  | _        |        | (       | CLSRC<4:0 | )>       |         | CLPOL    | CLMOD      |           | FLT      | SRC<4:0 | >       |          | FLTPOL   | FLTMO   | D<1:0>  | 00F8          |

| PDC2      | 0C46  |          |        |         |           |          |         |          | PDC2<15:0> |           |          |         |         |          |          |         |         | 0000          |

| PHASE2    | 0C48  |          |        |         |           |          |         | Р        | HASE2<15:0 | )>        |          |         |         |          |          |         |         | 0000          |

| DTR2      | 0C4A  | _        | _      |         |           |          |         |          | [          | DTR2<13:0 | >        |         |         |          |          |         |         | 0000          |

| ALTDTR2   | 0C4C  | _        | _      |         |           |          |         |          | AL         | TDTR2<13  | :0>      |         |         |          |          |         |         | 0000          |

| TRIG2     | 0C52  |          |        |         |           |          |         | TI       | RGCMP<15:0 | )>        |          |         |         |          |          |         |         | 0000          |

| TRGCON2   | 0C54  |          | TRGDI  | V<3:0>  |           | _        | —       | _        | _          | _         | -        |         |         | TRO      | GSTRT<5: | 0>      |         | 0000          |

| LEBCON2   | 0C5A  | PHR      | PHF    | PLR     | PLF       | FLTLEBEN | CLLEBEN | _        | _          | _         | -        | BCH     | BCL     | BPHH     | BPHL     | BPLH    | BPLL    | 0000          |

| LEBDLY2   | 0C5C  | _        | _      | _       | _         |          |         |          |            |           | LEB<11:0 | )>      |         |          |          |         |         | 0000          |

| AUXCON2   | 0C5E  | _        | _      | —       | —         |          | BLANK   | SEL<3:0> |            | _         | —        |         | CHOPS   | SEL<3:0> |          | CHOPHEN | CHOPLEN | 0000          |

I- DIGGOEDV/VMOGOV/EGV AND DIGGAEDV/VMOGOV DEVICED ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13       | Bit 12                                                | Bit 11   | Bit 10  | Bit 9    | Bit 8     | Bit 7     | Bit 6    | Bit 5 | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|--------|--------------|-------------------------------------------------------|----------|---------|----------|-----------|-----------|----------|-------|---------|----------|----------|---------|---------|---------------|

| PWMCON3   | 0C60  | FLTSTAT | CLSTAT | TRGSTAT      | FLTIEN                                                | CLIEN    | TRGIEN  | ITB      | MDCS      | DTC<      | <1:0>    | DTCP  | —       | MTBS     | CAM      | XPRES   | IUE     | 0000          |

| IOCON3    | 0C62  | PENH    | PENL   | POLH         | POLL                                                  | PMOD     | )<1:0>  | OVRENH   | OVRENL    | OVRDA     | T<1:0>   | FLTD  | AT<1:0> | CLD      | AT<1:0>  | SWAP    | OSYNC   | C000          |

| FCLCON3   | 0C64  |         |        | (            | CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0> |          |         |          |           |           |          |       |         |          | D<1:0>   | 00F8    |         |               |

| PDC3      | 0C66  |         |        |              | PDC3<15:0>                                            |          |         |          |           |           |          |       |         |          |          | 0000    |         |               |

| PHASE3    | 0C68  |         |        | PHASE3<15:0> |                                                       |          |         |          |           |           |          |       | 0000    |          |          |         |         |               |

| DTR3      | 0C6A  |         | —      |              |                                                       |          |         |          | [         | DTR3<13:0 | >        |       |         |          |          |         |         | 0000          |

| ALTDTR3   | 0C6C  |         | —      |              |                                                       |          |         |          | AL        | TDTR3<13  | :0>      |       |         |          |          |         |         | 0000          |

| TRIG3     | 0C72  |         |        |              |                                                       |          |         | Т        | RGCMP<15: | 0>        |          |       |         |          |          |         |         | 0000          |

| TRGCON3   | 0C74  |         | TRGDI  | V<3:0>       |                                                       | _        | _       | _        | _         | _         | _        |       |         | TR       | GSTRT<5: | 0>      |         | 0000          |

| LEBCON3   | 0C7A  | PHR     | PHF    | PLR          | PLF                                                   | FLTLEBEN | CLLEBEN | —        | —         |           | —        | BCH   | BCL     | BPHH     | BPHL     | BPLH    | BPLL    | 0000          |

| LEBDLY3   | 0C7C  |         | —      | _            | _                                                     |          |         |          |           |           | LEB<11:0 | )>    |         |          |          |         |         | 0000          |

| AUXCON3   | 0C7E  |         | —      | —            | —                                                     |          | BLANK   | SEL<3:0> |           |           | —        |       | CHOPS   | SEL<3:0> | •        | CHOPHEN | CHOPLEN | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

.

----

.

## TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                    | Bit 8 | Bit 7 | Bit 6 | Bit 5     | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|--------------------------|-------|-------|-------|-----------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | —       | —      | —       | —      | —      | —      | —                        | _     |       |       |           | I2C1 Recei   | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202  | _       | _      | _       | _      | —      | _      | —                        | _     |       |       |           | I2C1 Transi  | mit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204  | _       | _      | _       | _      | _      | _      | _                        |       |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                   | SMEN  | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                   | ADD10 | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      | I2C1 Address Register 00 |       |       |       |           |              |              |       |       |       | 0000          |

| I2C1MSK      | 020C  | _       | _      | _       | _      | _      | _      |                          |       |       |       | I2C1 Add  | dress Mask   |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | _       | _      | _       | _      | _      | _      | _                        | _     |       |       |           | I2C2 Recei   | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | _       | _      | _       | _      | _      | _      | _                        | _     |       |       |           | I2C2 Transi  | mit Register |       |       |       | OOFF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | _      | _                        |       |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                   | SMEN  | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT                   | ADD10 | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | _       | _      | —      | _      |                          |       |       |       | I2C2 Addr | ess Register | r            |       |       |       | 0000          |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | _      |                          |       |       |       | I2C2 Add  | dress Mask   |              |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                      | Bit 14 | Bit 13   | Bit 12                   | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7      | Bit 6    | Bit 5 | Bit 4      | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|---------------------------------------------|--------|----------|--------------------------|--------|--------|-------|----------|------------|----------|-------|------------|----------|-------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN                                      | —      | USIDL    | IREN                     | RTSMD  | _      | UEN<  | :1:0>    | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1                                    | UTXINV | UTXISEL0 | _                        | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _                                           | _      | _        |                          |        |        |       |          |            |          |       |            |          |       | xxxx   |       |               |

| U1RXREG     | 0226  | _                                           | _      | _        | UART1 Receive Register 0 |        |        |       |          |            |          |       |            |          | 0000  |        |       |               |

| U1BRG       | 0228  |                                             |        |          |                          |        |        | Baud  | Rate Gen | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

| U2MODE      | 0230  | UARTEN                                      | _      | USIDL    | IREN                     | RTSMD  | _      | UEN<  | :1:0>    | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1                                    | UTXINV | UTXISEL0 | _                        | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _                                           | _      | _        | _                        | _      | _      | _     |          |            |          | UART2 | Transmit F | Register |       |        |       | xxxx          |

| U2RXREG     | 0236  | 36 — — — — — — — — UART2 Receive Register 0 |        |          |                          |        |        |       |          |            |          |       | 0000       |          |       |        |       |               |

| U2BRG       | 0238  |                                             |        |          |                          |        |        | Baud  | Rate Gen | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        | _      |        |        | RP35   | R<5:0> |       |       | _     | —     |       |       | RP20F | ₹<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        |        | RP37   | R<5:0> |       |       |       | —     |       |       | RP36F | <5:0>  |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |        | RP39   | R<5:0> |       |       |       | —     |       |       | RP38F | <5:0>  |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        |        | RP41   | R<5:0> |       |       |       | —     |       |       | RP40F | <5:0>  |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |        | RP43   | R<5:0> |       |       |       | —     |       |       | RP42F | <5:0>  |       |       | 0000          |

| RPOR5        | 068A  | _      | —      |        |        | RP55   | R<5:0> |       |       | _     | —     |       |       | RP54F | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  | _      | —      |        |        | RP57   | R<5:0> |       |       | _     | —     |       |       | RP56F | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|-------------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        |             | RP35F  | R<5:0> |       |       | _     | _     |       | •     | RP20F | R<5:0> |       | •     | 0000          |

| RPOR1        | 0682  | _      |        |        | RP37R<5:0>  |        |        |       |       |       | _     |       |       | RP36  | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | —      |        | RP39R<5:0>  |        |        |       |       |       | _     |       |       | RP38  | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | —      |        |             | RP41F  | २<5:0> |       |       | _     | _     |       |       | RP40  | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |             | RP43F  | २<5:0> |       |       | —     | _     |       |       | RP42  | R<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |        |             | RP55F  | २<5:0> |       |       | —     | _     |       |       | RP54  | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  | _      | _      |        |             | RP57F  | २<5:0> |       |       | —     | _     |       |       | RP56  | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |        | RP97R<5:0>  |        |        |       |       |       | _     | _     | _     | _     | _      | _     | _     | 0000          |

| RPOR8        | 0690  |        | _      |        | RP118R<5:0> |        |        |       |       |       | _     | —     | _     | —     | _      | —     | _     | 0000          |

| RPOR9        | 0692  | —      | _      | _      | _           | _      | _      | _     | _     | _     | _     |       |       | RP120 | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| -n = Value at F | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, rea | id as '0'       |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

|                 |       |                  |       |                  |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit C |

|                 |       |                  | NVMAD | )R<23:16>        |                 |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| _               | —     | —                | —     | —                | _               | —               | —     |

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0             | U-0             | U-0   |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADR<23:16>:** Nonvolatile Memory Write Address High bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-3: NVMADRL: NONVOLATILE MEMORY ADDRESS REGISTER LOW

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | NVMA  | DR<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | NVMA  | DR<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 NVMADR<15:0>: Nonvolatile Memory Write Address Low bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY

| U-0             | U-0 | U-0              | U-0  | U-0              | U-0             | U-0             | U-0   |

|-----------------|-----|------------------|------|------------------|-----------------|-----------------|-------|

| —               | —   | —                | _    | —                | —               | —               | —     |

| bit 15          |     |                  |      |                  |                 |                 | bit 8 |

|                 |     |                  |      |                  |                 |                 |       |

| W-0             | W-0 | W-0              | W-0  | W-0              | W-0             | W-0             | W-0   |

|                 |     |                  | NVMK | EY<7:0>          |                 |                 |       |

| bit 7           |     |                  |      |                  |                 |                 | bit 0 |

|                 |     |                  |      |                  |                 |                 |       |

| Legend:         |     |                  |      |                  |                 |                 |       |

| R = Readable I  | bit | W = Writable     | bit  | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                       | U-0              | U-0             | U-0              | U-0              | U-0             | R/W-0   |

|-----------------|-------------------------------------------|------------------|-----------------|------------------|------------------|-----------------|---------|

| _               | —                                         | —                |                 | —                | —                | —               | PLLDIV8 |

| bit 15          |                                           |                  |                 |                  |                  |                 | bit 8   |

|                 |                                           |                  |                 |                  |                  |                 |         |

| R/W-0           | R/W-0                                     | R/W-1            | R/W-1           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| PLLDIV7         | PLLDIV6                                   | PLLDIV5          | PLLDIV4         | PLLDIV3          | PLLDIV2          | PLLDIV1         | PLLDIV0 |

| bit 7           |                                           |                  |                 |                  |                  |                 | bit 0   |

|                 |                                           |                  |                 |                  |                  |                 |         |

| Legend:         |                                           |                  |                 |                  |                  |                 |         |

| R = Readable    | bit                                       | W = Writable     | bit             | U = Unimpler     | mented bit, read | as '0'          |         |

| -n = Value at P | OR                                        | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                 |                                           |                  |                 |                  |                  |                 |         |

| bit 15-9        | Unimplemen                                | ted: Read as '   | 0'              |                  |                  |                 |         |

| bit 8-0         | PLLDIV<8:0>                               | : PLL Feedba     | ck Divisor bits | (also denoted    | as 'M', PLL mul  | tiplier)        |         |

|                 | 111111111 =                               | = 513            |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | 000110000 =                               | = 50 (default)   |                 |                  |                  |                 |         |

|                 |                                           |                  |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | 000000010 =<br>000000001 =<br>000000000 = | = 3              |                 |                  |                  |                 |         |

|                 |                                           |                  |                 |                  |                  |                 |         |

#### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

## 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

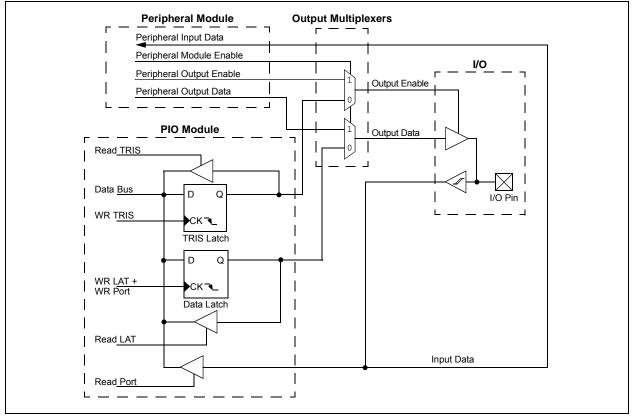

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

#### 11.7 **Peripheral Pin Select Registers**

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|-------|------------|-------|-------|-------|-------|-------|--|--|--|

| —      |       | INT1R<6:0> |       |       |       |       |       |  |  |  |

| bit 15 |       |            |       |       |       |       | bit 8 |  |  |  |

|        |       |            |       |       |       |       |       |  |  |  |

| U-0    | U-0   | U-0        | U-0   | U-0   | U-0   | U-0   | U-0   |  |  |  |

| —      | —     | —          | —     | —     | _     | _     | —     |  |  |  |

| bit 7  |       | •          |       | •     |       |       | bit 0 |  |  |  |

|        |       |            |       |       |       |       |       |  |  |  |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

| R/W-0                          | U-0                                                                        | U-0                                                                                                                        | U-0                                                              | U-0              | U-0                       | R/W-0           | R/W-0   |

|--------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------|---------------------------|-----------------|---------|

| CHPCLKEN                       | —                                                                          | —                                                                                                                          | —                                                                | —                | —                         | CHOPC           | LK<9:8> |

| bit 15                         |                                                                            |                                                                                                                            |                                                                  |                  |                           |                 | bit 8   |

|                                |                                                                            |                                                                                                                            |                                                                  |                  |                           |                 |         |

| R/W-0                          | R/W-0                                                                      | R/W-0                                                                                                                      | R/W-0                                                            | R/W-0            | R/W-0                     | R/W-0           | R/W-0   |

|                                |                                                                            |                                                                                                                            | CHOPC                                                            | LK<7:0>          |                           |                 |         |

| bit 7                          |                                                                            |                                                                                                                            |                                                                  |                  |                           |                 | bit 0   |

|                                |                                                                            |                                                                                                                            |                                                                  |                  |                           |                 |         |

| Legend:                        |                                                                            |                                                                                                                            |                                                                  |                  |                           |                 |         |

| R = Readable I                 | bit                                                                        | W = Writable                                                                                                               | bit                                                              | U = Unimplei     | mented bit, read          | as '0'          |         |

| -n = Value at P                | OR                                                                         | '1' = Bit is set                                                                                                           |                                                                  | '0' = Bit is cle | eared                     | x = Bit is unkr | nown    |

| bit 15<br>bit 14-10<br>bit 9-0 | 1 = Chop clos<br>0 = Chop clos<br>Unimplemen<br>CHOPCLK<9<br>The frequence | Enable Chop<br>ck generator is<br>ck generator is<br>ted: Read as '<br>9:0>: Chop Clo<br>y of the chop c<br>ncy = (FP/PCL) | enabled<br>disabled<br>0'<br>ck Divider bits<br>lock signal is g | given by the fo  | ollowing expressi<br>+ 1) | on:             |         |

## REGISTER 16-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

### REGISTER 16-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |

|-----------------|-------|------------------|-------|------------------|-----------------|--------------------|-------|--|

|                 |       |                  | MDC   | <15:8>           |                 |                    |       |  |

| bit 15          |       |                  |       |                  |                 |                    | bit 8 |  |

|                 |       |                  |       |                  |                 |                    |       |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |

|                 |       |                  | MD    | C<7:0>           |                 |                    |       |  |

| bit 7           |       |                  |       |                  |                 |                    | bit 0 |  |

|                 |       |                  |       |                  |                 |                    |       |  |

| Legend:         |       |                  |       |                  |                 |                    |       |  |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimpler     | mented bit, rea | ad as '0'          |       |  |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unknown |       |  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

| R/W-0         | R/W-0       | R/W-0                                           | U-0          | U-0              | U-0             | U-0               | U-0    |  |  |  |  |

|---------------|-------------|-------------------------------------------------|--------------|------------------|-----------------|-------------------|--------|--|--|--|--|

| FRMEN         | SPIFSD      | FRMPOL                                          | —            | —                | _               | —                 | _      |  |  |  |  |

| bit 15        |             |                                                 |              |                  |                 |                   | bit 8  |  |  |  |  |

|               |             |                                                 |              |                  |                 |                   |        |  |  |  |  |

| U-0           | U-0         | U-0                                             | U-0          | U-0              | U-0             | R/W-0             | R/W-0  |  |  |  |  |

| _             | —           | —                                               | _            |                  | _               | FRMDLY            | SPIBEN |  |  |  |  |

| bit 7         |             |                                                 |              |                  |                 |                   | bit 0  |  |  |  |  |

|               |             |                                                 |              |                  |                 |                   |        |  |  |  |  |

| Legend:       |             |                                                 |              |                  |                 |                   |        |  |  |  |  |

| R = Readable  | e bit       | W = Writable b                                  | pit          | U = Unimpler     | nented bit, rea | ad as '0'         |        |  |  |  |  |

| -n = Value at | POR         | '1' = Bit is set                                |              | '0' = Bit is cle | ared            | x = Bit is unkr   | nown   |  |  |  |  |

|               |             |                                                 |              |                  |                 |                   |        |  |  |  |  |

| bit 15        | FRMEN: Fra  | med SPIx Suppo                                  | ort bit      |                  |                 |                   |        |  |  |  |  |

|               |             | SPIx support is e<br>SPIx support is d          |              | x pin is used as | Frame Sync      | oulse input/outpu | it)    |  |  |  |  |

| bit 14        | SPIFSD: Fra | me Sync Pulse [                                 | Direction Co | ontrol bit       |                 |                   |        |  |  |  |  |

|               |             | ync pulse input (<br>ync pulse output           |              |                  |                 |                   |        |  |  |  |  |

| bit 13        | FRMPOL: Fr  | ame Sync Pulse                                  | Polarity bit | t                |                 |                   |        |  |  |  |  |

|               |             | ync pulse is activ                              | •            |                  |                 |                   |        |  |  |  |  |

|               |             | ync pulse is activ                              |              |                  |                 |                   |        |  |  |  |  |

| bit 12-2      | -           | nted: Read as '0                                |              |                  |                 |                   |        |  |  |  |  |

| bit 1         |             | ame Sync Pulse                                  | -            |                  |                 |                   |        |  |  |  |  |

|               |             | ync pulse coincio<br>ync pulse preceo           |              |                  |                 |                   |        |  |  |  |  |

| bit 0         | SPIBEN: En  | hanced Buffer Er                                | nable bit    |                  |                 |                   |        |  |  |  |  |

|               |             | d buffer is enable                              |              |                  |                 |                   |        |  |  |  |  |

|               | 0 = Enhance | d buffer is disabl                              | ed (Standa   | rd mode)         |                 |                   |        |  |  |  |  |

|               |             | 0 = Enhanced buffer is disabled (Standard mode) |              |                  |                 |                   |        |  |  |  |  |

#### REGISTER 18-3: SPIXCON2: SPIX CONTROL REGISTER 2

## REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | PTGA  | DJ<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PTGA  | DJ<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGADD command.

## REGISTER 24-11: PTGL0: PTG LITERAL 0 REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | PTGL0 | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | PTGL  | )<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 15-0 PTGL0<15:0>: PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the  ${\tt PTGCTRL}$  Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

NOTES:

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed, or an SFR register is read. In these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157). For more information on instructions that take more than one instruction cycle to execute, refer to **"CPU"** (DS70359) in the *"dsPIC33/PIC24 Family Reference Manual"*, particularly the **"Instruction Flow Types"** section.

| Field               | Description                                                                          |

|---------------------|--------------------------------------------------------------------------------------|

| #text               | Means literal defined by "text"                                                      |

| (text)              | Means "content of text"                                                              |

| [text]              | Means "the location addressed by text"                                               |

| {}                  | Optional field or operation                                                          |

| $a \in \{b, c, d\}$ | a is selected from the set of values b, c, d                                         |

| <n:m></n:m>         | Register bit field                                                                   |

| .b                  | Byte mode selection                                                                  |

| .d                  | Double-Word mode selection                                                           |

| .S                  | Shadow register select                                                               |

| .w                  | Word mode selection (default)                                                        |

| Acc                 | One of two accumulators {A, B}                                                       |

| AWB                 | Accumulator write back destination address register ∈ {W13, [W13]+ = 2}              |

| bit4                | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z     | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr                | Absolute address, label or expression (resolved by the linker)                       |

| f                   | File register address ∈ {0x00000x1FFF}                                               |

| lit1                | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4                | 4-bit unsigned literal ∈ {015}                                                       |

| lit5                | 5-bit unsigned literal ∈ {031}                                                       |

| lit8                | 8-bit unsigned literal ∈ {0255}                                                      |

| lit10               | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |

| lit14               | 14-bit unsigned literal ∈ {016384}                                                   |

| lit16               | 16-bit unsigned literal ∈ {065535}                                                   |

| lit23               | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |

| None                | Field does not require an entry, can be blank                                        |

| OA, OB, SA, SB      | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |

| PC                  | Program Counter                                                                      |

| Slit10              | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16              | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6               | 6-bit signed literal ∈ {-1616}                                                       |

| Wb                  | Base W register ∈ {W0W15}                                                            |

| Wd                  | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo                 | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

#### TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| DC CHARACTERISTICS |                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                 |                       |                 |  |

|--------------------|-------------------------------|-------------------------------------------------------|-----------------|-----------------------|-----------------|--|

| Parameter<br>No.   | Тур.                          | Max.                                                  | Units           | Conditions            |                 |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI                                         | P50X, dsPIC33EF | P32MC20X/50X and PIC2 | 4EP32GP/MC20X   |  |

| DC60d              | 30                            | 100                                                   | μA              | -40°C                 |                 |  |

| DC60a              | 35                            | 100                                                   | μA              | +25°C                 | 3.3V            |  |

| DC60b              | 150                           | 200                                                   | μA              | +85°C                 | 3.3V            |  |

| DC60c              | 250                           | 500                                                   | μA              | +125°C                |                 |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI                                         | P50X, dsPIC33EF | P64MC20X/50X and PIC2 | 4EP64GP/MC20X   |  |

| DC60d              | 25                            | 100                                                   | μA              | -40°C                 |                 |  |

| DC60a              | 30                            | 100                                                   | μA              | +25°C                 | 3.3V            |  |

| DC60b              | 150                           | 350                                                   | μΑ              | +85°C                 |                 |  |

| DC60c              | 350                           | 800                                                   | μΑ              | +125°C                |                 |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G                                         | P50X, dsPIC33E  | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |

| DC60d              | 30                            | 100                                                   | μΑ              | -40°C                 |                 |  |

| DC60a              | 35                            | 100                                                   | μΑ              | +25°C                 | 3.3V            |  |

| DC60b              | 150                           | 350                                                   | μΑ              | +85°C                 | 5.57            |  |

| DC60c              | 550                           | 1000                                                  | μΑ              | +125°C                |                 |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G                                         | P50X, dsPIC33E  | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |

| DC60d              | 35                            | 100                                                   | μΑ              | -40°C                 |                 |  |

| DC60a              | 40                            | 100                                                   | μΑ              | +25°C                 | 3.3V            |  |

| DC60b              | 250                           | 450                                                   | μΑ              | +85°C                 | 3.3V            |  |

| DC60c              | 1000                          | 1200                                                  | μΑ              | +125°C                |                 |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP512G                                         | P50X, dsPIC33E  | P512MC20X/50X and PIC | 24EP512GP/MC20X |  |

| DC60d              | 40                            | 100                                                   | μΑ              | -40°C                 |                 |  |

| DC60a              | 45                            | 100                                                   | μΑ              | +25°C                 | 3.3V            |  |

| DC60b              | 350                           | 800                                                   | μΑ              | +85°C                 |                 |  |

| DC60c              | 1100                          | 1500                                                  | μA              | +125°C                |                 |  |

### TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

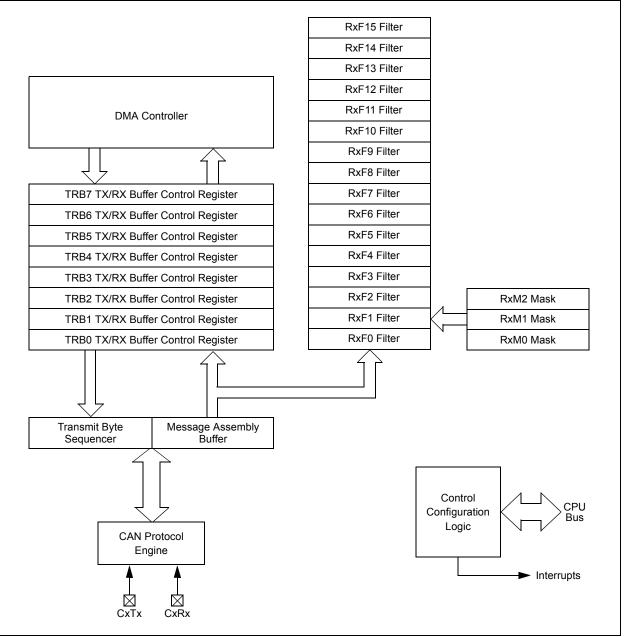

### FIGURE 30-19: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

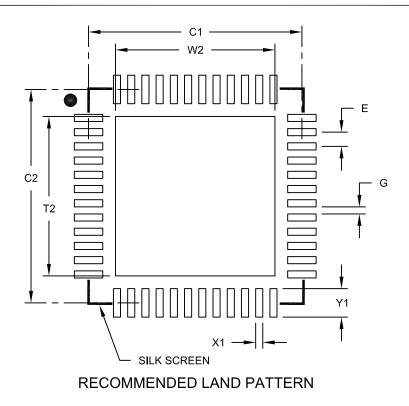

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.40 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 4.45 |

| Optional Center Pad Length | T2 |             |      | 4.45 |

| Contact Pad Spacing        | C1 |             | 6.00 |      |

| Contact Pad Spacing        | C2 |             | 6.00 |      |

| Contact Pad Width (X28)    | X1 |             |      | 0.20 |

| Contact Pad Length (X28)   | Y1 |             |      | 0.80 |

| Distance Between Pads      | G  | 0.20        |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A

## **Revision C (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 20.1 "UART Helpful Tips" and Section 3.6 "CPU Resources". All occurrences of TLA were updated to VTLA throughout the document, with the exception of the pin diagrams (updated diagrams were not available at time of publication).

A new chapter, Section 31.0 "DC and AC Device Characteristics Graphs", was added.

All other major changes are referenced by their respective section in Table A-2.

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>256-Kbyte Flash and<br>32-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | The content on the first page of this section was extensively reworked to provide the reader with the key features and functionality of this device family in an "at-a-glance" format.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 1.0 "Device<br>Overview"                                                                                                                                        | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X Block Diagram (see Figure 1-1), which now contains a CPU<br>block and a reference to the CPU diagram.<br>Updated the description and Note references in the Pinout I/O Descriptions for these                                                                                                                                                                                                                                                                                                                                                              |

| Section 2.0 "Guidelines for<br>Getting Started with 16-bit<br>Digital Signal Controllers<br>and Microcontrollers"                                                       | pins: C1IN2-, C2IN2-, C3IN2-, OA1OUT, OA2OUT, and OA3OUT (see Table 1-1).<br>Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Section 3.0 "CPU"                                                                                                                                                       | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X CPU Block Diagram (see Figure 3-1).<br>Updated the Status register definition in the Programmer's Model (see Figure 3-2).                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Section 4.0 "Memory<br>Organization"                                                                                                                                    | Updated the Data Memory Maps (see Figure 4-6 and Figure 4-11).<br>Removed the DCB<1:0> bits from the OC1CON2, OC2CON2, OC3CON2, and<br>OC4CON2 registers in the Output Compare 1 Through Output Compare 4 Register<br>Map (see Table 4-10).<br>Added the TRIG1 and TRGCON1 registers to the PWM Generator 1 Register Map<br>(see Table 4-13).<br>Added the TRIG2 and TRGCON2 registers to the PWM Generator 2 Register Map<br>(see Table 4-14).<br>Added the TRIG3 and TRGCON3 registers to the PWM Generator 3 Register Map<br>(see Table 4-15).<br>Updated the second note in Section 4.7.1 "Bit-Reversed Addressing<br>Implementation". |

| Section 8.0 "Direct Memory<br>Access (DMA)"                                                                                                                             | Updated the DMA Controller diagram (see Figure 8-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Section 14.0 "Input<br>Capture"                                                                                                                                         | Updated the bit values for the ICx clock source of the ICTSEL<12:10> bits in the ICxCON1 register (see Register 14-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 15.0 "Output<br>Compare"                                                                                                                                        | Updated the bit values for the OCx clock source of the OCTSEL<2:0> bits in the OCxCON1 register (see Register 15-1).<br>Removed the DCB<1:0> bits from the Output Compare x Control Register 2 (see Register 15-2).                                                                                                                                                                                                                                                                                                                                                                                                                        |

TABLE A-2: MAJOR SECTION UPDATES