Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc502-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

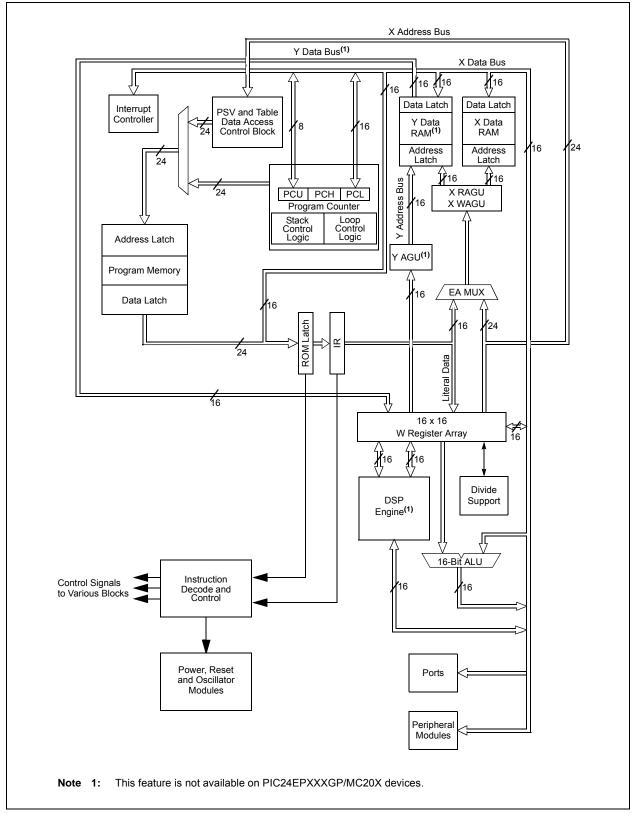

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

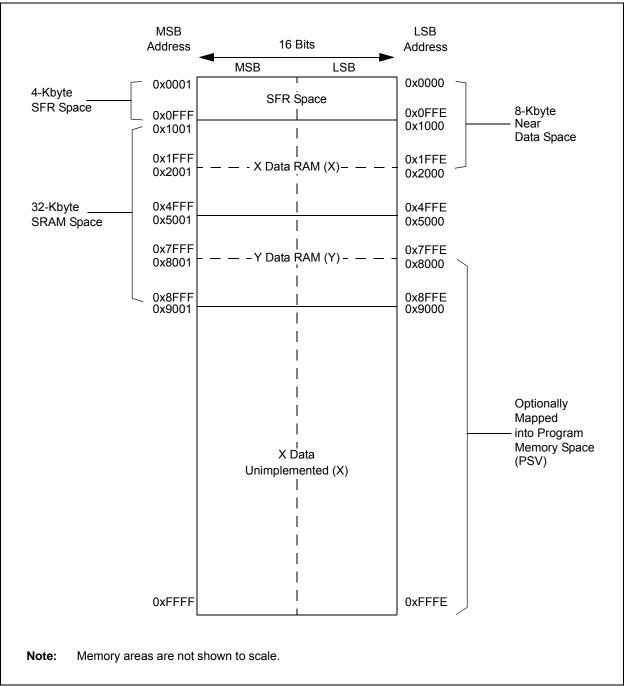

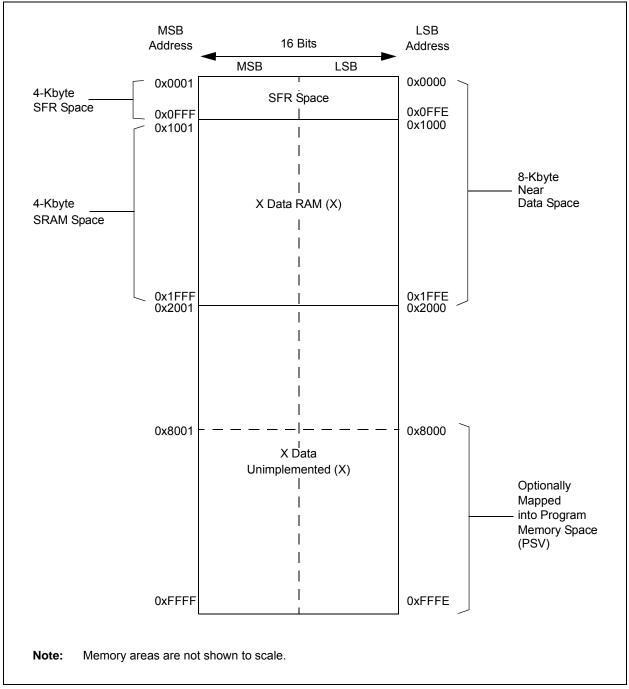

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

## TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|--------|--------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|-------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN  | _      | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |        |        |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN  | _      | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264  | FRMEN  | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  |        |        |         |        |        |        | SPI2 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-56: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      |        | _      | _     | TRISA8 | _     | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | —      | _     | —      | _     | —     | —     | ANSA4  | —      | —      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | -       | _       | -       | —       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | —      | —     | TRISC8 | _     | _     |       | _     |       | -     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  |        |        | -      | -      | -      | —      | _     | RC8    | —     | -     |       | _     |       |       | RC1    | RC0    | xxxx          |

| LATC         | 0E24  |        |        | _      | _      | _      | _      | _     | LATC8  | _     | _     | _     | _     | _     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  |        |        | _      | _      | _      | _      | _     | ODCC8  | _     | _     | _     | _     | _     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | _      | -      | _      |        | _      | _     | CNIEC8 | —     |       |       | _     |       |       | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  |        |        | _      | _      | _      | _      | _     | CNPUC8 | _     | _     | _     | _     | _     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  |        |        | _      | _      | _      | _      | _     | CNPDC8 | _     | _     | _     | _     | _     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | -      | _      | _      | _      | _      | —      | —     | _      | —     |       | _     | _     | _     |       | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

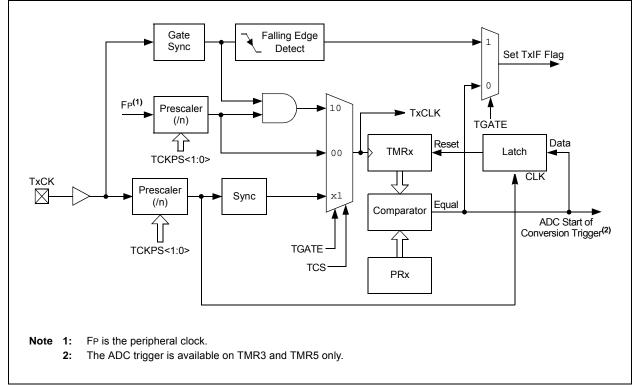

#### FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

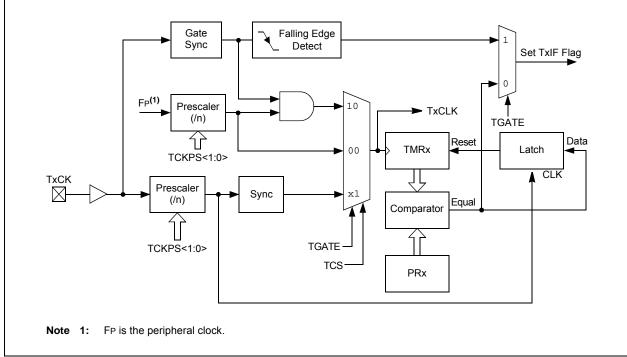

# FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

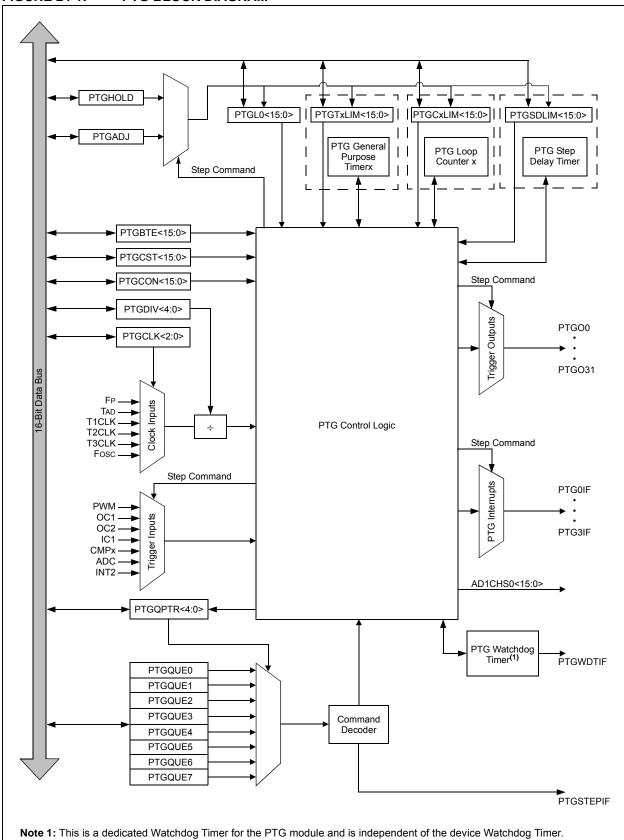

# 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER      | 25-3: CM40        | CON: COMPA                                                | RATOR 4 CO          | ONTROL RE        | GISTER             |                                          |                     |

|---------------|-------------------|-----------------------------------------------------------|---------------------|------------------|--------------------|------------------------------------------|---------------------|

| R/W-0         | R/W-0             | R/W-0                                                     | U-0                 | U-0              | U-0                | R/W-0                                    | R/W-0               |

| CON           | COE               | CPOL                                                      |                     |                  | _                  | CEVT                                     | COUT                |

| bit 15        |                   |                                                           | •                   | ·                |                    |                                          | bit 8               |

| R/W-0         | R/W-0             | U-0                                                       | R/W-0               | U-0              | U-0                | R/W-0                                    | R/W-0               |

| EVPOL1        | EVPOL0            | 0-0                                                       | CREF <sup>(1)</sup> | 0-0              | 0-0                | CCH1 <sup>(1)</sup>                      | CCH0 <sup>(1)</sup> |

| bit 7         | EVPOLU            | _                                                         | UREF /              | _                | —                  |                                          | bit 0               |

|               |                   |                                                           |                     |                  |                    |                                          |                     |

| Legend:       |                   |                                                           |                     |                  |                    |                                          |                     |

| R = Readable  | e bit             | W = Writable                                              | bit                 | U = Unimple      | mented bit, rea    | d as '0'                                 |                     |

| -n = Value at | POR               | '1' = Bit is se                                           | t                   | '0' = Bit is cle | eared              | x = Bit is unkn                          | iown                |

|               |                   |                                                           |                     |                  |                    |                                          |                     |

| bit 15        | =                 | arator Enable b                                           | it                  |                  |                    |                                          |                     |

|               |                   | ator is enabled<br>ator is disabled                       |                     |                  |                    |                                          |                     |

| bit 14        | COE: Compa        | arator Output E                                           | nable bit           |                  |                    |                                          |                     |

|               |                   | ator output is pr<br>ator output is in                    |                     | xOUT pin         |                    |                                          |                     |

| bit 13        | CPOL: Com         | parator Output                                            | Polarity Select     | bit              |                    |                                          |                     |

|               | 1 = Compara       | ator output is in                                         | verted              |                  |                    |                                          |                     |

|               | 0 = Compara       | ator output is no                                         | ot inverted         |                  |                    |                                          |                     |

| bit 12-10     | Unimpleme         | nted: Read as                                             | 0'                  |                  |                    |                                          |                     |

| bit 9         | CEVT: Comp        | parator Event b                                           | it                  |                  |                    |                                          |                     |

|               | interrupt         | ator event acc<br>ts until the bit is<br>ator event did r | cleared             | POL<1:0> set     | tings occurred;    | disables future                          | triggers and        |

| bit 8         | •                 | parator Output                                            |                     |                  |                    |                                          |                     |

|               |                   | . = 0 (non-inver                                          |                     |                  |                    |                                          |                     |

|               | 1 = VIN + > V     |                                                           | teu polanty).       |                  |                    |                                          |                     |

|               | 0 = VIN+ < V      | ÍN-                                                       |                     |                  |                    |                                          |                     |

|               | When CPOL         | . = 1 (inverted p                                         | olarity):           |                  |                    |                                          |                     |

|               | 1 = VIN+ < V      |                                                           |                     |                  |                    |                                          |                     |

|               | 0 = VIN + > V     |                                                           |                     |                  |                    |                                          |                     |

| bit 7-6       |                   | >: Trigger/Even                                           |                     | -                |                    |                                          |                     |

|               | 10 = Trigger      |                                                           | generated only      |                  |                    | or output (while (<br>e polarity selecte |                     |

|               |                   | L = 1 (inverted)<br>-high transition                      |                     | ator output.     |                    |                                          |                     |

|               |                   | L = 0 (non-inve<br>-low transition                        |                     | ator output.     |                    |                                          |                     |

|               |                   | /event/interrupt<br>(while CEVT = 0                       |                     | on low-to-higi   | n transition of th | e polarity selecte                       | ed comparator       |

|               |                   | L = 1 (inverted)<br>-low transition                       |                     | ator output.     |                    |                                          |                     |

|               | If CPO            | <u>L = 0 (non-inve</u><br>-high transition                | rted polarity):     |                  |                    |                                          |                     |

|               |                   | /event/interrupt                                          | =                   | -                |                    |                                          |                     |

| Note 1: Inj   | puts that are sel | lected and not a                                          | available will be   | e tied to Vss. S | see the "Pin Dia   | agrams" sectior                          | n for available     |

#### -----

Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

# 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EP instruction set is almost identical to that of the dsPIC30F and dsPIC33F. The PIC24EP instruction set is almost identical to that of the PIC24F and PIC24H.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

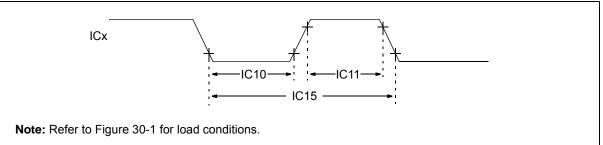

## FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHA        | RACTERI | STICS                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                  |                                  |

|---------------|---------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|----------------------------------|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                    | Max. | Units | Con                              | ditions                          |

| IC10          | TccL    | ICx Input Low Time             | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                          |      | ns    | Must also meet<br>Parameter IC15 |                                  |

| IC11          | ТссН    | ICx Input High Time            | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                          | —    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |

| IC15          | TccP    | ICx Input Period               | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50                                                                                                                                                                                                                                           | _    | ns    |                                  |                                  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

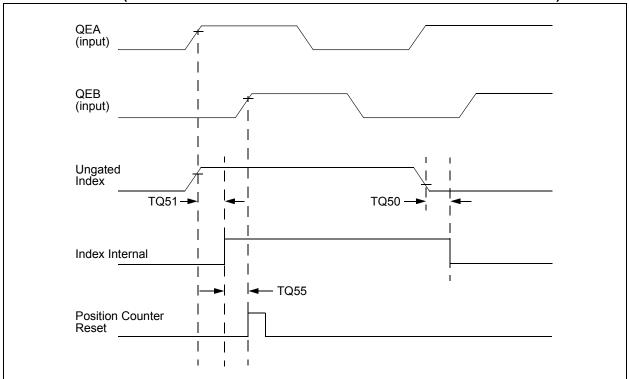

#### FIGURE 30-13: QEI MODULE INDEX PULSE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

## TABLE 30-32: QEI INDEX PULSE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| АС СНА       | RACTERI | STICS                                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                                         |  |  |  |  |

|--------------|---------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------------------|--|--|--|--|

| Param<br>No. | Symbol  | Characteristic <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                                                                   | Max. | Units | Conditions                                              |  |  |  |  |

| TQ50         | TqiL    | Filter Time to Recognize Low, with Digital Filter                   | 3 * N * Tcy                                                                                                                                                                                                                                                                            | _    | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |  |  |  |  |

| TQ51         | TqiH    | Filter Time to Recognize High,<br>with Digital Filter               | 3 * N * Tcy                                                                                                                                                                                                                                                                            | —    | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |  |  |  |  |

| TQ55         | Tqidxr  | Index Pulse Recognized to Position<br>Counter Reset (ungated index) | 3 TCY                                                                                                                                                                                                                                                                                  | —    | ns    |                                                         |  |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Alignment of index pulses to QEA and QEB is shown for position counter Reset timing only. Shown for forward direction only (QEA leads QEB). Same timing applies for reverse direction (QEA lags QEB) but index pulse recognition occurs on the falling edge.

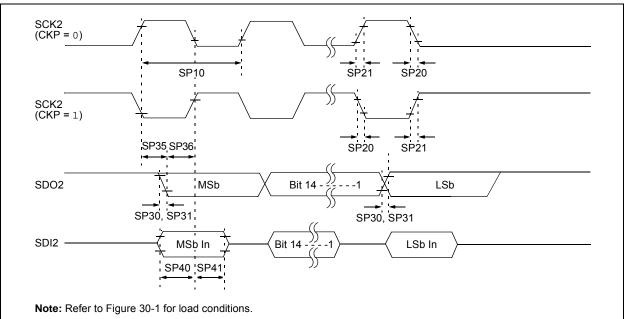

#### FIGURE 30-17: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-36:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHA | RACTERIST             | ICS                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                             |  |  |  |  |

|--------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|--|--|--|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |  |  |  |

| SP10   | FscP                  | Maximum SCK2 Frequency                        |                                                                                                                                                                                                                                                                                         | —                   | 9    | MHz   | -40°C to +125°C<br>(Note 3) |  |  |  |  |

| SP20   | TscF                  | SCK2 Output Fall Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |  |  |  |

| SP21   | TscR                  | SCK2 Output Rise Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |  |  |  |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |  |  |  |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |  |  |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge     | _                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                             |  |  |  |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge  | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |  |  |  |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |  |  |  |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge     | 30                                                                                                                                                                                                                                                                                      | —                   |      | ns    |                             |  |  |  |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

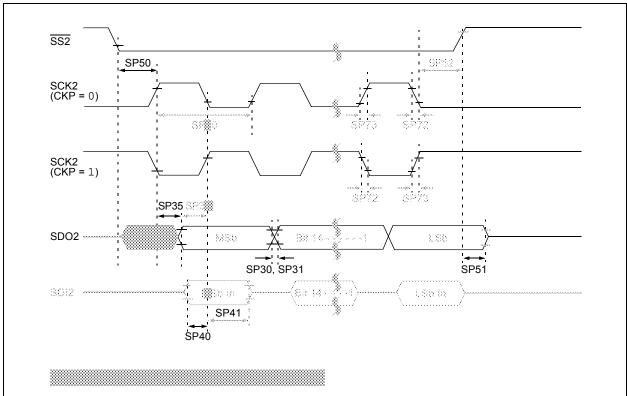

#### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

| AC CHA       | RACTER  | ISTICS           |                           | Standard Operatin<br>(unless otherwise<br>Operating tempera | stated)<br>iture -40 | )°C ≤ Ta ≤ | +85°C for Industrial   |

|--------------|---------|------------------|---------------------------|-------------------------------------------------------------|----------------------|------------|------------------------|

| Param<br>No. | Symbol  | Characte         | eristic <sup>(4)</sup>    | Min. <sup>(1)</sup>                                         | -40<br>Max.          | Units      | Conditions             |

| IM10         | TLO:SCL | Clock Low Time   | 100 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μS         |                        |

|              |         |                  | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μ <b>S</b> |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μs         |                        |

| IM11         | THI:SCL | Clock High Time  | 100 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μS         |                        |

|              |         |                  | 400 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μs         |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             | _                    | μS         |                        |

| IM20         | TF:SCL  | SDAx and SCLx    | 100 kHz mode              | _                                                           | 300                  | ns         | CB is specified to be  |

|              |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns         | from 10 to 400 pF      |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                           | 100                  | ns         |                        |

| IM21         | TR:SCL  | SDAx and SCLx    | 100 kHz mode              | _                                                           | 1000                 | ns         | CB is specified to be  |

|              |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns         | from 10 to 400 pF      |

|              |         |                  | 1 MHz mode <sup>(2)</sup> |                                                             | 300                  | ns         |                        |

| IM25         | TSU:DAT | Data Input       | 100 kHz mode              | 250                                                         |                      | ns         |                        |

|              |         | Setup Time       | 400 kHz mode              | 100                                                         |                      | ns         |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 40                                                          |                      | ns         |                        |

| IM26         | THD:DAT | Data Input       | 100 kHz mode              | 0                                                           |                      | μS         |                        |

|              |         | Hold Time        | 400 kHz mode              | 0                                                           | 0.9                  | μs         |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.2                                                         |                      | μS         |                        |

| IM30         | TSU:STA | Start Condition  | 100 kHz mode              | TCY/2 (BRG + 2)                                             | _                    | μS         | Only relevant for      |

|              |         | Setup Time       | 400 kHz mode              | TCY/2 (BRG + 2)                                             | _                    | μS         | Repeated Start         |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             |                      | μS         | condition              |

| IM31         | THD:STA | Start Condition  | 100 kHz mode              | TCY/2 (BRG + 2)                                             | _                    | μS         | After this period, the |

|              |         | Hold Time        | 400 kHz mode              | TCY/2 (BRG +2)                                              | —                    | μS         | first clock pulse is   |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μS         | generated              |

| IM33         | Tsu:sto | Stop Condition   | 100 kHz mode              | TCY/2 (BRG + 2)                                             | _                    | μS         |                        |

|              |         | Setup Time       | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

| IM34         | THD:STO | Stop Condition   | 100 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

|              |         | Hold Time        | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

| IM40         | TAA:SCL | Output Valid     | 100 kHz mode              | —                                                           | 3500                 | ns         |                        |

|              |         | From Clock       | 400 kHz mode              |                                                             | 1000                 | ns         |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> |                                                             | 400                  | ns         |                        |

| IM45         | TBF:SDA | Bus Free Time    | 100 kHz mode              | 4.7                                                         |                      | μS         | Time the bus must be   |

|              |         |                  | 400 kHz mode              | 1.3                                                         |                      | μS         | free before a new      |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.5                                                         | —                    | μS         | transmission can star  |

| IM50         | Св      | Bus Capacitive L | oading                    | —                                                           | 400                  | pF         |                        |

| IM51         | Tpgd    | Pulse Gobbler De | elay                      | 65                                                          | 390                  | ns         | (Note 3)               |

### TABLE 30-49: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the l<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to "Inter-Integrated Circuit (l<sup>2</sup>C<sup>™</sup>)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site for the latest family reference manual sections.

- 2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

- **3:** Typical value for this parameter is 130 ns.

- 4: These parameters are characterized, but not tested in manufacturing.

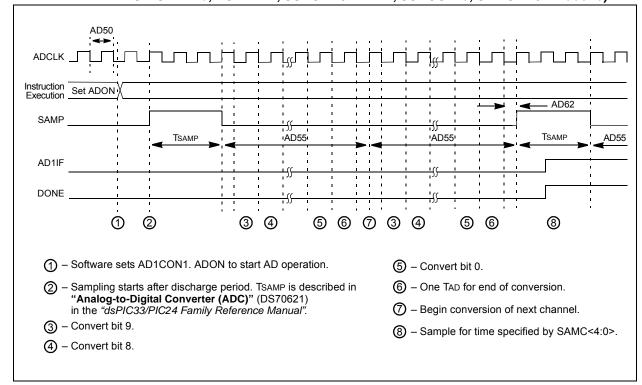

#### FIGURE 30-38: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)

DS70000657H-page 464

| DC CHAF | RACTERIS | STICS                                                       | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |      |      |       |                                                                    |  |  |  |

|---------|----------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------------------------------------------------------|--|--|--|

| Param.  | Symbol   | Characteristic                                              | Min.                                                                                                                              | Тур. | Max. | Units | Conditions                                                         |  |  |  |

| HDO10   | Vol      | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                                                                                                                                   |      | 0.4  | V     | IOL ≤ 5 mA, VDD = 3.3V<br>(Note 1)                                 |  |  |  |

|         |          | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | —                                                                                                                                 | _    | 0.4  | V     | IOL ≤ 8 mA, VDD = 3.3V<br>(Note 1)                                 |  |  |  |

| HDO20   | Vон      | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                               |      | —    | V     | IOH ≥ -10 mA, VDD = 3.3V<br>(Note 1)                               |  |  |  |

|         |          | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                               | _    | —    | V     | ІОн ≥ 15 mA, VDD = 3.3V<br>(Note 1)                                |  |  |  |

| HDO20A  | Vон1     | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 1.5                                                                                                                               | _    | —    | V     | IOH ≥ -3.9 mA, VDD = 3.3V<br>(Note 1)                              |  |  |  |

|         |          |                                                             | 2.0                                                                                                                               | _    | —    |       | $IOH \ge -3.7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$<br>(Note 1)  |  |  |  |

|         |          |                                                             | 3.0                                                                                                                               |      | —    |       | IOH ≥ -2 mA, VDD = 3.3V<br>(Note 1)                                |  |  |  |

|         |          | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 1.5                                                                                                                               |      | _    | V     | IOH ≥ -7.5 mA, VDD = 3.3V<br>(Note 1)                              |  |  |  |

|         |          |                                                             | 2.0                                                                                                                               | _    | —    |       | $IOH \ge -6.8 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$<br>(Note 1) |  |  |  |

|         |          |                                                             | 3.0                                                                                                                               | _    | —    |       | IOH ≥ -3 mA, VDD = 3.3V<br>(Note 1)                                |  |  |  |

## TABLE 31-8: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<15:7> and RC3

For 64-pin devices: RA4, RA9, RB<15:7>, RC3 and RC15

#### 31.2 **AC Characteristics and Timing Parameters**

The information contained in this section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X AC characteristics and timing parameters for high-temperature devices. However, all AC timing specifications in this section are the same as those in Section 30.2 "AC Characteristics and Timing Parameters", with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter OS53 in Section 30.2 "AC Characteristics and Timing Parameters" is the Industrial and Extended temperature equivalent of HOS53.

## TABLE 31-9: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

| AC CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated) |  |  |

|--------------------|--------------------------------------------------------------------------|--|--|

| AC CHARACTERIO NOC | Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$            |  |  |

|                    | Operating voltage VDD range as described in Table 31-1.                  |  |  |

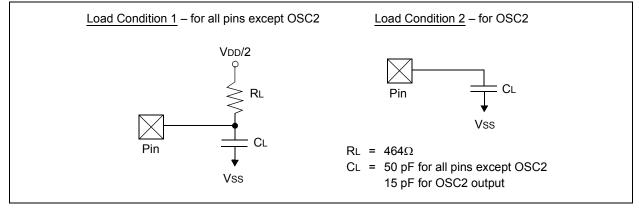

#### **FIGURE 31-1:** LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 31-10: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |     |     |       |                             |

|--------------------|--------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------------------------|

| Param<br>No.       | Symbol | Characteristic                         | Min                                                                                                                                    | Тур | Max | Units | Conditions                  |

| HOS53              | DCLK   | CLKO Stability (Jitter) <sup>(1)</sup> | -5                                                                                                                                     | 0.5 | 5   | %     | Measured over 100 ms period |

These parameters are characterized by similarity, but are not tested in manufacturing. This specification is Note 1: based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases or communication clocks use this formula:

$$Peripheral Clock Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Peripheral Bit Rate Clock}}}$$

For example: FOSC = 32 MHz, DCLK = 5%, SPIx bit rate clock (i.e., SCKx) is 2 MHz. Г

$$SPI SCK Jitter = \left\lfloor \frac{D_{CLK}}{\sqrt{\left(\frac{32 MHz}{2 MHz}\right)}} \right\rfloor = \left\lfloor \frac{5\%}{\sqrt{16}} \right\rfloor = \left\lfloor \frac{5\%}{4} \right\rfloor = 1.25\%$$

٦

© 2011-2013 Microchip Technology Inc.