#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc502-e-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

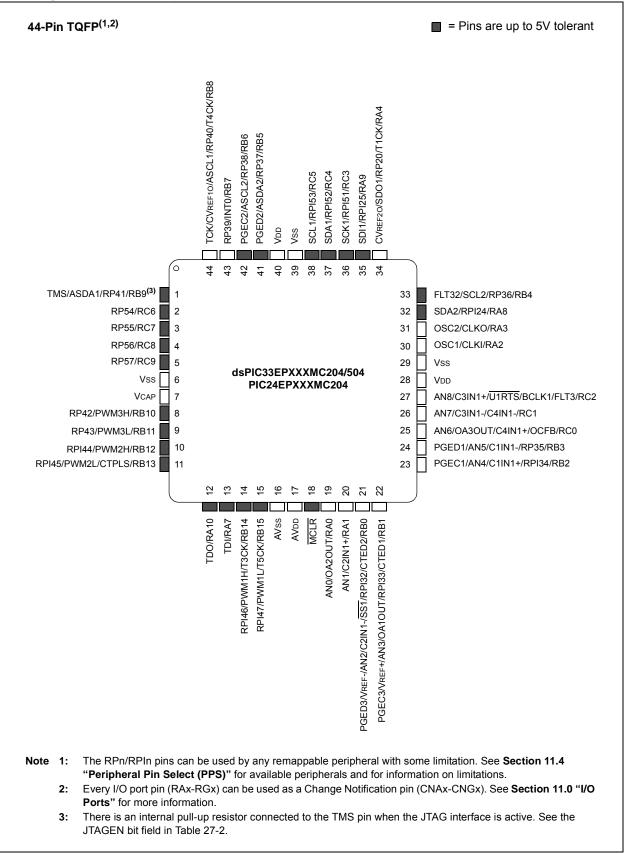

## Pin Diagrams (Continued)

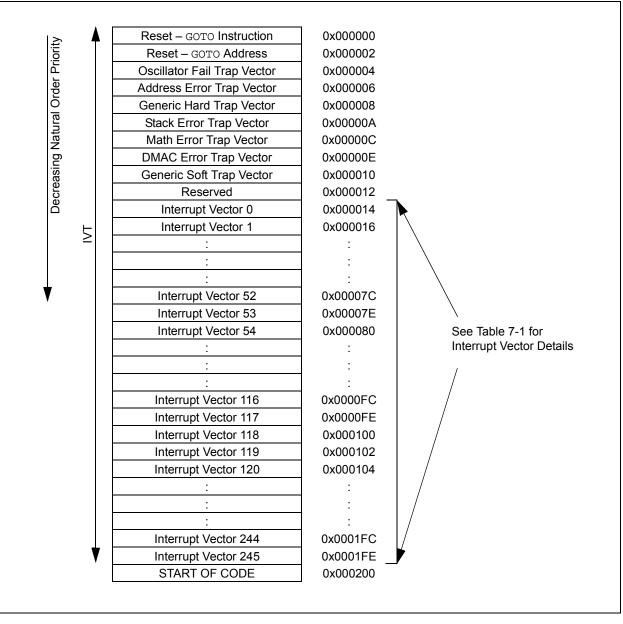

## FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                               | U-0                                                               | U-0   | U-0   | U-0                                | U-0   | U-0   | U-0   |

|-----------------------------------|-------------------------------------------------------------------|-------|-------|------------------------------------|-------|-------|-------|

| —                                 | —                                                                 | —     | —     | —                                  | —     | —     | —     |

| bit 15                            |                                                                   |       |       |                                    | •     |       | bit 8 |

|                                   |                                                                   |       |       |                                    |       |       |       |

| R/W-0                             | R/W-0                                                             | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                   |                                                                   |       | STB<  | 23:16>                             |       |       |       |

| bit 7                             |                                                                   |       |       |                                    |       |       | bit 0 |

|                                   |                                                                   |       |       |                                    |       |       |       |

| Legend:                           |                                                                   |       |       |                                    |       |       |       |

| R = Readable bit W = Writable bit |                                                                   |       | bit   | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at P                   | e at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |       | nown                               |       |       |       |

|                                   |                                                                   |       |       |                                    |       |       |       |

## REGISTER 8-5: DMAXSTBH: DMA CHANNEL X START ADDRESS REGISTER B (HIGH)

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: Secondary Start Address bits (source or destination)

## REGISTER 8-6: DMAXSTBL: DMA CHANNEL X START ADDRESS REGISTER B (LOW)

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|-------------------|-------|-----------------|-------|

|                                   |       |                  | STB                                | <15:8>            |       |                 |       |

| bit 15                            |       |                  |                                    |                   |       |                 | bit 8 |

|                                   |       |                  |                                    |                   |       |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                                   |       |                  | STE                                | 3<7:0>            |       |                 |       |

| bit 7                             |       |                  |                                    |                   |       |                 | bit 0 |

| Legend:                           |       |                  |                                    |                   |       |                 |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                   |       |                 |       |

| -n = Value at POR '1' = Bit is se |       | '1' = Bit is set |                                    | '0' = Bit is clea | ared  | x = Bit is unkı | nown  |

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

| R/W-0           | R/W-0                                                                                                | R/W-1                             | R/W-1                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------|------------------------|--------------------|-----------------|-----------|--|--|--|

| ROI             | DOZE2 <sup>(1)</sup>                                                                                 | DOZE1 <sup>(1)</sup>              | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup> | FRCDIV2            | FRCDIV1         | FRCDIV0   |  |  |  |

| bit 15          |                                                                                                      |                                   | •                    |                        |                    |                 | bit 8     |  |  |  |

|                 |                                                                                                      |                                   |                      |                        |                    |                 |           |  |  |  |

| R/W-0           | R/W-1                                                                                                | U-0                               | R/W-0                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |

| PLLPOST1        | PLLPOST0                                                                                             | —                                 | PLLPRE4              | PLLPRE3                | PLLPRE2            | PLLPRE1         | PLLPRE0   |  |  |  |

| bit 7           |                                                                                                      |                                   |                      |                        |                    |                 | bit (     |  |  |  |

|                 |                                                                                                      |                                   |                      |                        |                    |                 |           |  |  |  |

| Legend:         |                                                                                                      |                                   |                      |                        |                    |                 |           |  |  |  |

| R = Readable    |                                                                                                      | W = Writable                      |                      | -                      | nented bit, read   |                 |           |  |  |  |

| -n = Value at F | POR                                                                                                  | '1' = Bit is set                  |                      | '0' = Bit is cle       | ared               | x = Bit is unkr | nown      |  |  |  |

| h:+ 45          |                                                                                                      | on Interview h                    |                      |                        |                    |                 |           |  |  |  |

| bit 15          |                                                                                                      | on Interrupt bis will clear the l |                      |                        |                    |                 |           |  |  |  |

|                 |                                                                                                      | s have no effect                  |                      | EN bit                 |                    |                 |           |  |  |  |

| bit 14-12       | •                                                                                                    | Processor Clo                     |                      |                        |                    |                 |           |  |  |  |

|                 | 111 = Fcy div                                                                                        |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 110 = FCY divided by 128                                                                             |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 101 = FCY divided by 32                                                                              |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 100 = FCY divided by 16                                                                              |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 011 = FCY divided by 8 (default)<br>010 = FCY divided by 4                                           |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 001 = FCY divided by 2                                                                               |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 000 = Fcy div                                                                                        | •                                 |                      |                        |                    |                 |           |  |  |  |

| bit 11          |                                                                                                      | e Mode Enable                     |                      |                        |                    |                 |           |  |  |  |

|                 |                                                                                                      |                                   |                      |                        | pheral clocks a    | nd the process  | or clocks |  |  |  |

|                 |                                                                                                      | -                                 | -                    | ratio is forced to     |                    |                 |           |  |  |  |

| bit 10-8        |                                                                                                      |                                   | RC Oscillator        | r Postscaler bit       | S                  |                 |           |  |  |  |

|                 | 111 = FRC divided by 256<br>110 = FRC divided by 64                                                  |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 101 = FRC divided by 84                                                                              |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 100 = FRC divided by 16                                                                              |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 011 = FRC divided by 8                                                                               |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 010 = FRC divided by 4                                                                               |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 001 = FRC divided by 2<br>000 = FRC divided by 1 (default)                                           |                                   |                      |                        |                    |                 |           |  |  |  |

| bit 7-6         | <b>PLLPOST&lt;1:0&gt;:</b> PLL VCO Output Divider Select bits (also denoted as 'N2', PLL postscaler) |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 11 = Output divided by 8                                                                             |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 10 = Reserved                                                                                        |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 01 = Output divided by 4 (default)<br>00 = Output divided by 2                                       |                                   |                      |                        |                    |                 |           |  |  |  |

| bit 5           | -                                                                                                    | ted: Read as '                    | o'                   |                        |                    |                 |           |  |  |  |

|                 | •                                                                                                    |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | e DOZE<2:0> b<br>ZE<2:0> are ig                                                                      |                                   | written to whe       | en the DOZEN           | bit is clear. If D | OZEN = 1, any   | writes to |  |  |  |

| <b>2:</b> This  | s bit is cleared                                                                                     | when the ROI I                    | oit is set and a     | an interrupt occ       | urs.               |                 |           |  |  |  |

|                 | DOJENUS                                                                                              |                                   |                      |                        | ~ ~                |                 | <i>.</i>  |  |  |  |

### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER

The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | <u>R 10-2: PMD</u> 2                    | 2: PERIPHER                                                                                  | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |

|--------------|-----------------------------------------|----------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|

| U-0          | U-0                                     | U-0                                                                                          | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

| _            |                                         | —                                                                                            |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |

| bit 15       |                                         |                                                                                              |                 |                   |                 |                 | bit   |  |  |  |

| U-0          | U-0                                     | U-0                                                                                          | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|              |                                         |                                                                                              |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |

| bit 7        |                                         |                                                                                              |                 |                   |                 |                 | bit   |  |  |  |

|              |                                         |                                                                                              |                 |                   |                 |                 |       |  |  |  |

| Legend:      | 1.1.1                                   |                                                                                              |                 |                   |                 |                 |       |  |  |  |

| R = Readab   |                                         | W = Writable b                                                                               | Dit             | •                 | nented bit, rea |                 |       |  |  |  |

| -n = Value a | at POR                                  | '1' = Bit is set                                                                             |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |

| bit 15-12    | Unimplemen                              | ted: Read as '0                                                                              | ,               |                   |                 |                 |       |  |  |  |

| bit 11       | -                                       | t Capture 4 Mod                                                                              |                 |                   |                 |                 |       |  |  |  |

|              | •                                       | ture 4 module is                                                                             |                 |                   |                 |                 |       |  |  |  |

|              | 0 = Input Cap                           | oture 4 module is                                                                            | s enabled       |                   |                 |                 |       |  |  |  |

| bit 10       | IC3MD: Input                            | t Capture 3 Mod                                                                              | ule Disable bit |                   |                 |                 |       |  |  |  |

|              | 1 = Input Capture 3 module is disabled  |                                                                                              |                 |                   |                 |                 |       |  |  |  |

|              |                                         | oture 3 module is                                                                            |                 |                   |                 |                 |       |  |  |  |

| bit 9        |                                         | Capture 2 Mod                                                                                |                 |                   |                 |                 |       |  |  |  |

|              |                                         | oture 2 module is<br>oture 2 module is                                                       |                 |                   |                 |                 |       |  |  |  |

| bit 8        | IC1MD: Input                            | t Capture 1 Mod                                                                              | ule Disable bit |                   |                 |                 |       |  |  |  |

|              | 1 = Input Cap                           | oture 1 module is<br>oture 1 module is                                                       | s disabled      |                   |                 |                 |       |  |  |  |

| bit 7-4      |                                         | ted: Read as '0                                                                              |                 |                   |                 |                 |       |  |  |  |

| bit 3        | OC4MD: Out                              | put Compare 4                                                                                | Module Disable  | e bit             |                 |                 |       |  |  |  |

|              | 1 = Output Compare 4 module is disabled |                                                                                              |                 |                   |                 |                 |       |  |  |  |

|              | 0 = Output Compare 4 module is enabled  |                                                                                              |                 |                   |                 |                 |       |  |  |  |

| bit 2        |                                         | put Compare 3                                                                                |                 | e bit             |                 |                 |       |  |  |  |

|              | 1 = Output Compare 3 module is disabled |                                                                                              |                 |                   |                 |                 |       |  |  |  |

| L:1 4        | 0 = Output Compare 3 module is enabled  |                                                                                              |                 |                   |                 |                 |       |  |  |  |

| bit 1        |                                         | <b>OC2MD:</b> Output Compare 2 Module Disable bit<br>1 = Output Compare 2 module is disabled |                 |                   |                 |                 |       |  |  |  |

|              | $\perp$ – Output Co                     | ompare z mouu                                                                                |                 |                   |                 |                 |       |  |  |  |

|              | 0 = Output Co                           | ompare 2 modul                                                                               | le is enabled   |                   |                 |                 |       |  |  |  |

| bit 0        |                                         | ompare 2 modul<br>put Compare 1                                                              |                 | e bit             |                 |                 |       |  |  |  |

| bit 0        | OC1MD: Out                              | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul                                          | Module Disable  | e bit             |                 |                 |       |  |  |  |

#### ~

#### 11.7 **Peripheral Pin Select Registers**

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | _     | _     | —     |

| bit 7  |       | •     |       | •          |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

## REGISTER 11-16: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38 (dsPIC33EPXXXMC20X AND PIC24EPXXXMC20X DEVICES ONLY)

|              | -         |                                      |       |                      |                   | -                  |                |

|--------------|-----------|--------------------------------------|-------|----------------------|-------------------|--------------------|----------------|

| U-0          | R/W-0     | R/W-0                                | R/W-0 | R/W-0                | R/W-0             | R/W-0              | R/W-0          |

|              |           |                                      |       | DTCMP1R<6:           | 0>                |                    |                |

| bit 15       |           |                                      |       |                      |                   |                    | bit 8          |

|              |           |                                      |       |                      |                   |                    |                |

| U-0          | U-0       | U-0                                  | U-0   | U-0                  | U-0               | U-0                | U-0            |

| —            | —         | —                                    | _     |                      | _                 | —                  | —              |

| bit 7        |           |                                      |       |                      |                   |                    | bit C          |

|              |           |                                      |       |                      |                   |                    |                |

| Legend:      |           |                                      |       |                      |                   |                    |                |

| R = Readal   | ole bit   | W = Writable                         | bit   | U = Unimpler         | mented bit, read  | d as '0'           |                |

| -n = Value a | at POR    | '1' = Bit is set                     | :     | '0' = Bit is cleared |                   | x = Bit is unknown |                |

|              |           |                                      |       |                      |                   |                    |                |

| bit 15       | Unimpleme | nted: Read as '                      | 0'    |                      |                   |                    |                |

| bit 14-8     |           | 6:0>: Assign PV<br>1-2 for input pin |       | •                    | on Input 1 to the | e Corresponding    | g RPn Pin bits |

|              | 1111001 = | Input tied to RP                     | 1121  |                      |                   |                    |                |

|              | •         |                                      |       |                      |                   |                    |                |

|              | •         |                                      |       |                      |                   |                    |                |

|              |           | Input tied to CM                     | P1    |                      |                   |                    |                |

|              |           | Input tied to Vss                    |       |                      |                   |                    |                |

| bit 7-0      |           | nted: Read as '                      |       |                      |                   |                    |                |

|              |           |                                      | -     |                      |                   |                    |                |

# 12.2 Timer1 Control Register

| R/W-0              | U-0                                                            | R/W-0                        | U-0            | U-0              | U-0                      | U-0                | U-0                |  |  |  |

|--------------------|----------------------------------------------------------------|------------------------------|----------------|------------------|--------------------------|--------------------|--------------------|--|--|--|

| TON <sup>(1)</sup> | —                                                              | TSIDL                        | —              | _                | —                        | _                  | _                  |  |  |  |

| bit 15             |                                                                |                              |                |                  |                          |                    | bit 8              |  |  |  |

|                    |                                                                |                              |                |                  |                          |                    |                    |  |  |  |

| U-0                | R/W-0                                                          | R/W-0                        | R/W-0          | U-0              | R/W-0                    | R/W-0              | U-0                |  |  |  |

|                    | TGATE                                                          | TCKPS1                       | TCKPS0         | _                | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> |                    |  |  |  |

| bit 7              |                                                                |                              |                |                  |                          |                    | bit (              |  |  |  |

| Legend:            |                                                                |                              |                |                  |                          |                    |                    |  |  |  |

| R = Readable       | e bit                                                          | W = Writable                 | bit            | U = Unimplei     | mented bit, read         | l as '0'           |                    |  |  |  |

| -n = Value at      | POR                                                            | '1' = Bit is set             |                | '0' = Bit is cle | ared                     | x = Bit is unkno   | own                |  |  |  |

|                    |                                                                | o                            |                |                  |                          |                    |                    |  |  |  |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16-                           |                              |                |                  |                          |                    |                    |  |  |  |

|                    | 0 = Stops 16-                                                  |                              |                |                  |                          |                    |                    |  |  |  |

| bit 14             | Unimplemen                                                     | ted: Read as '               | 0'             |                  |                          |                    |                    |  |  |  |

| bit 13             | TSIDL: Timer                                                   | 1 Stop in Idle N             | /lode bit      |                  |                          |                    |                    |  |  |  |

|                    | 1 = Discontinues module operation when device enters Idle mode |                              |                |                  |                          |                    |                    |  |  |  |

|                    |                                                                | s module opera               |                | ode              |                          |                    |                    |  |  |  |

| bit 12-7           | -                                                              | ted: Read as '               |                |                  |                          |                    |                    |  |  |  |

| bit 6              |                                                                | r1 Gated Time                | Accumulation   | h Enable bit     |                          |                    |                    |  |  |  |

|                    | When TCS = 1:<br>This bit is ignored.                          |                              |                |                  |                          |                    |                    |  |  |  |

|                    | When TCS = $0$ :                                               |                              |                |                  |                          |                    |                    |  |  |  |

|                    |                                                                | e accumulatio                |                |                  |                          |                    |                    |  |  |  |

|                    |                                                                | e accumulatio                |                | 0.1.1.1.1.1      |                          |                    |                    |  |  |  |

| bit 5-4            |                                                                | : Timer1 Input               | Clock Prescal  | e Select bits    |                          |                    |                    |  |  |  |

|                    | 11 = 1:256<br>10 = 1:64                                        |                              |                |                  |                          |                    |                    |  |  |  |

|                    | 01 = 1:8                                                       |                              |                |                  |                          |                    |                    |  |  |  |

|                    | 00 = 1:1                                                       |                              |                |                  |                          |                    |                    |  |  |  |

| bit 3              | -                                                              | ted: Read as '               |                |                  |                          |                    |                    |  |  |  |

| bit 2              |                                                                | er1 External Clo             | ock Input Synd | chronization S   | elect bit <sup>(1)</sup> |                    |                    |  |  |  |

|                    | When TCS = 1:                                                  |                              |                |                  |                          |                    |                    |  |  |  |

|                    | 1 = Synchronizes external clock input                          |                              |                |                  |                          |                    |                    |  |  |  |

|                    | 0 = Does not synchronize external clock input<br>When TCS = 0: |                              |                |                  |                          |                    |                    |  |  |  |

|                    | This bit is ignored.                                           |                              |                |                  |                          |                    |                    |  |  |  |

| bit 1              | TCS: Timer1 Clock Source Select bit <sup>(1)</sup>             |                              |                |                  |                          |                    |                    |  |  |  |

|                    | 1 = External c<br>0 = Internal cl                              | clock is from pi<br>ock (FP) | n, T1CK (on th | ne rising edge)  | •                        |                    |                    |  |  |  |

| bit 0              | Unimplemen                                                     | ted: Read as '               | 0'             |                  |                          |                    |                    |  |  |  |

|                    | nen Timer1 is er<br>empts by user s                            |                              |                |                  |                          | SYNC = 1, TON      | <b>\ =</b> 1), any |  |  |  |

## REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

© 2011-2013 Microchip Technology Inc.

## 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

## 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | <b>`</b>              |                                            |                                |                          |                  |                 |                 |  |  |  |  |

|---------------|-----------------------|--------------------------------------------|--------------------------------|--------------------------|------------------|-----------------|-----------------|--|--|--|--|

| R/W-0         | R-0                   | R-0                                        | R-0                            | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |

| TXENn         | TXABTn                | TXLARBn                                    | TXERRn                         | TXREQn                   | RTRENn           | TXnPRI1         | TXnPRI0         |  |  |  |  |

| bit 15        |                       |                                            |                                |                          |                  |                 | bit 8           |  |  |  |  |

| R/W-0         | R-0                   | R-0                                        | R-0                            | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |

| TXENm         | TXABTm <sup>(1)</sup> | TXLARBm <sup>(1)</sup>                     | TXERRm <sup>(1)</sup>          | TXREQm                   | RTRENm           | TXmPRI1         | TXmPRI0         |  |  |  |  |

| bit 7         |                       | 1                                          | 1                              |                          |                  |                 | bit (           |  |  |  |  |

| Legend:       |                       |                                            |                                |                          |                  |                 |                 |  |  |  |  |

| R = Readable  | e bit                 | W = Writable                               | bit                            | U = Unimpler             | mented bit, read | d as '0'        |                 |  |  |  |  |

| -n = Value at | POR                   | '1' = Bit is set                           |                                | '0' = Bit is cle         | ared             | x = Bit is unkr | nown            |  |  |  |  |

| bit 15-8      | See Dofinition        | n for bits<7:0>,                           | Controls Ruffs                 | ar n                     |                  |                 |                 |  |  |  |  |

| bit 7         |                       | RX Buffer Sele                             |                                |                          |                  |                 |                 |  |  |  |  |

|               |                       | RA Buller Sele                             |                                |                          |                  |                 |                 |  |  |  |  |

|               |                       | RBn is a receive                           |                                |                          |                  |                 |                 |  |  |  |  |

| bit 6         | TXABTm: M             | TXABTm: Message Aborted bit <sup>(1)</sup> |                                |                          |                  |                 |                 |  |  |  |  |

|               |                       | 1 = Message was aborted                    |                                |                          |                  |                 |                 |  |  |  |  |

|               | •                     | completed trar                             | nsmission succ                 | essfully                 |                  |                 |                 |  |  |  |  |

| bit 5         | TXLARBm: N            | Message Lost A                             | Arbitration bit <sup>(1)</sup> | )                        |                  |                 |                 |  |  |  |  |

|               |                       | lost arbitration                           |                                |                          |                  |                 |                 |  |  |  |  |

|               | 0 = Message           | did not lose ar                            | bitration while                | being sent               |                  |                 |                 |  |  |  |  |

| bit 4         | TXERRm: Er            | ror Detected D                             | uring Transmis                 | ssion bit <sup>(1)</sup> |                  |                 |                 |  |  |  |  |

|               |                       | or occurred wh                             | •                              | •                        |                  |                 |                 |  |  |  |  |

|               |                       | or did not occu                            |                                | ssage was bei            | ing sent         |                 |                 |  |  |  |  |

| bit 3         |                       | essage Send F                              | -                              |                          |                  |                 |                 |  |  |  |  |

|               | sent                  |                                            | -                              |                          | -                | n the message   | is successfully |  |  |  |  |

|               |                       | the bit to '0' wh                          | •                              | 0                        | abort            |                 |                 |  |  |  |  |

| bit 2         |                       | uto-Remote Tra                             |                                |                          |                  |                 |                 |  |  |  |  |

|               |                       | emote transmit<br>emote transmit           |                                |                          |                  |                 |                 |  |  |  |  |

| bit 1-0       | TXmPRI<1:0            | >: Message Tra                             | ansmission Pri                 | ority bits               |                  |                 |                 |  |  |  |  |

|               |                       | message prior                              |                                |                          |                  |                 |                 |  |  |  |  |

|               |                       | ermediate mes                              |                                |                          |                  |                 |                 |  |  |  |  |

|               |                       | ermediate mess<br>message priori           |                                |                          |                  |                 |                 |  |  |  |  |

|               | 00 – Lowesi           | messaye priori                             | ıy                             |                          |                  |                 |                 |  |  |  |  |

| Note 1: Th    | nis bit is cleared    | when TXREQ i                               | s set.                         |                          |                  |                 |                 |  |  |  |  |

|               |                       |                                            |                                |                          |                  |                 |                 |  |  |  |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

## REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit C |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

# REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|

|        | PTGHOLD<15:8> |       |       |       |       |       |       |  |  |  |

| bit 15 |               |       |       |       |       |       | bit 8 |  |  |  |

| R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | PTGHOLD<7:0> |       |       |       |       |       |       |  |  |  |

| bit 7 |              |       |       |       |       |       | bit 0 |  |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)</li> </ul> |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                      |

|         | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)                                                                                                                             |

|         | If CPOL = 1 (inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>Low-to-high transition of the comparator output                                                                                                                                                                       |

|         | 00 = Trigger/event/interrupt generation is disabled                                                                                                                                                                                                           |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 4   | <b>CREF:</b> Comparator Reference Select bit (VIN+ input) <sup>(1)</sup>                                                                                                                                                                                      |

|         | <ul> <li>1 = VIN+ input connects to internal CVREFIN voltage<sup>(2)</sup></li> <li>0 = VIN+ input connects to CxIN1+ pin</li> </ul>                                                                                                                          |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 1-0 | CCH<1:0>: Op Amp/Comparator Channel Select bits <sup>(1)</sup>                                                                                                                                                                                                |

|         | <ul> <li>11 = Unimplemented</li> <li>10 = Unimplemented</li> <li>01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup></li> <li>00 = Inverting input of the op amp/comparator connects to the CxIN1- pin</li> </ul>                 |

|         |                                                                                                                                                                                                                                                               |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

NOTES:

| Bit Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCP                    | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = Code protection is enabled for the entire program memory space                                                                                                                                                                                                                                                                                     |

| GWRP                   | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                           |

| IESO                   | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start up device with user-selected oscillator source</li> </ul>                                                                                                                                                                                           |

| PWMLOCK <sup>(1)</sup> | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                        |

| FNOSC<2:0>             | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Fast RC Oscillator with Divide-by-16 (FRCDIV16)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use<br>011 = Primary Oscillator with PLL module (XT + PLL, HS + PLL, EC + PLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |

| FCKSM<1:0>             | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                           |

| IOL1WAY                | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                                        |

| OSCIOFNC               | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                                          |

| POSCMD<1:0>            | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                           |

| FWDTEN                 | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                                                 |

| WINDIS                 | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                                              |

| PLLKEN                 | PLL Lock Enable bit<br>1 = PLL lock is enabled<br>0 = PLL lock is disabled<br>nly available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.                                                                                                                                                                                                                                                                                           |

## TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

## 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EP instruction set is almost identical to that of the dsPIC30F and dsPIC33F. The PIC24EP instruction set is almost identical to that of the PIC24F and PIC24H.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

| Base<br>Instr<br># | Assembly<br>Mnemonic |        |                                                                | Description                                       | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected        |

|--------------------|----------------------|--------|----------------------------------------------------------------|---------------------------------------------------|---------------|-------------------------------|---------------------------------|

| 53                 | NEG                  | NEG    | <sub>Acc</sub> (1)                                             | Negate Accumulator                                | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

|                    |                      | NEG    | f                                                              | $f = \overline{f} + 1$                            | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG    | f,WREG                                                         | WREG = $\overline{f}$ + 1                         | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG    | Ws,Wd                                                          | $Wd = \overline{Ws} + 1$                          | 1             | 1                             | C,DC,N,OV,Z                     |

| 54                 | NOP                  | NOP    | · · · · · · · · · · · · · · · · · · ·                          | No Operation                                      | 1             | 1                             | None                            |

|                    |                      | NOPR   |                                                                | No Operation                                      | 1             | 1                             | None                            |

| 55                 | POP                  | POP    | f                                                              | Pop f from Top-of-Stack (TOS)                     | 1             | 1                             | None                            |

|                    |                      | POP    | Wdo                                                            | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1                             | None                            |

|                    |                      | POP.D  | Wnd                                                            | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2                             | None                            |

|                    |                      | POP.S  |                                                                | Pop Shadow Registers                              | 1             | 1                             | All                             |

| 56                 | PUSH                 | PUSH   | f                                                              | Push f to Top-of-Stack (TOS)                      | 1             | 1                             | None                            |

|                    |                      | PUSH   | Wso                                                            | Push Wso to Top-of-Stack (TOS)                    | 1             | 1                             | None                            |

|                    |                      | PUSH.D | Wns                                                            | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2                             | None                            |

|                    |                      | PUSH.S |                                                                | Push Shadow Registers                             | 1             | 1                             | None                            |

| 57                 | PWRSAV               | PWRSAV | #lit1                                                          | Go into Sleep or Idle mode                        | 1             | 1                             | WDTO,Sleep                      |

| 58                 | RCALL                | RCALL  | Expr                                                           | Relative Call                                     | 1             | 4                             | SFA                             |

|                    |                      | RCALL  | Wn                                                             | Computed Call                                     | 1             | 4                             | SFA                             |

| 59                 | REPEAT               | REPEAT | #lit15                                                         | Repeat Next Instruction lit15 + 1 times           | 1             | 1                             | None                            |

|                    |                      | REPEAT | Wn                                                             | Repeat Next Instruction (Wn) + 1 times            | 1             | 1                             | None                            |

| 60                 | RESET                | RESET  |                                                                | Software device Reset                             | 1             | 1                             | None                            |

| 61                 | RETFIE               | RETFIE |                                                                | Return from interrupt                             | 1             | 6 (5)                         | SFA                             |

| 62                 | RETLW                | RETLW  | #lit10,Wn                                                      | Return with literal in Wn                         | 1             | 6 (5)                         | SFA                             |

| 63                 | RETURN               | RETURN |                                                                | Return from Subroutine                            | 1             | 6 (5)                         | SFA                             |

| 64                 | RLC                  | RLC    | f                                                              | f = Rotate Left through Carry f                   | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC    | f,WREG                                                         | WREG = Rotate Left through Carry f                | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC    | Ws,Wd                                                          | Wd = Rotate Left through Carry Ws                 | 1             | 1                             | C,N,Z                           |

| 65                 | RLNC                 | RLNC   | f                                                              | f = Rotate Left (No Carry) f                      | 1             | 1                             | N,Z                             |

|                    |                      | RLNC   | f,WREG                                                         | WREG = Rotate Left (No Carry) f                   | 1             | 1                             | N,Z                             |

|                    |                      | RLNC   | Ws,Wd                                                          | Wd = Rotate Left (No Carry) Ws                    | 1             | 1                             | N,Z                             |

| 66                 | RRC                  | RRC    | f                                                              | f = Rotate Right through Carry f                  | 1             | 1                             | C,N,Z                           |

|                    |                      | RRC    | f,WREG                                                         | WREG = Rotate Right through Carry f               | 1             | 1                             | C,N,Z                           |