#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc502-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

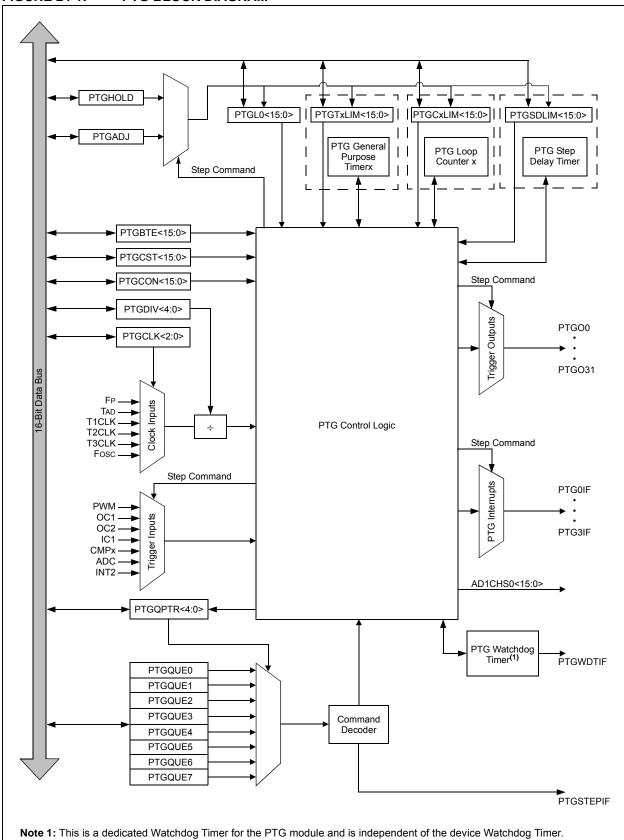

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

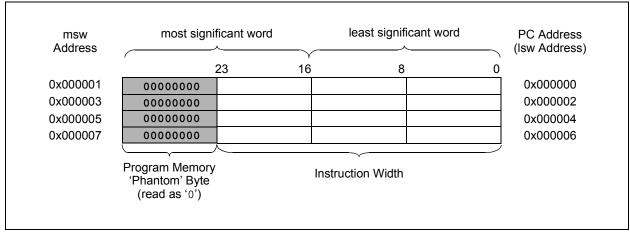

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

## FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|------------|-------|--------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        |        |        |            | RP35   | R<5:0> |       |       | _     | —     |            |       | RP20F  | ₹<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        |            | RP37   | R<5:0> |       |       |       | —     |            |       | RP36F  | <5:0>  |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |            | RP39   | R<5:0> |       |       |       | —     | RP38R<5:0> |       |        |        |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        |            | RP41   | R<5:0> |       |       |       | —     | RP40R<5:0> |       |        |        |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |            | RP43   | R<5:0> |       |       |       | —     |            |       | RP42F  | <5:0>  |       |       | 0000          |

| RPOR5        | 068A  | _      | —      |        | RP55R<5:0> |        |        |       |       | _     | —     | RP54R<5:0> |       |        |        |       | 0000  |               |

| RPOR6        | 068C  | _      | —      |        | RP57R<5:0> |        |        |       | _     | —     |       |            | RP56F | R<5:0> |        |       | 0000  |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6       | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|-------------|--------|--------|-------|-------|-------|-------------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        |             | RP35F  | R<5:0> |       |       | _     | _           |            | •     | RP20F | R<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      |        |        |             | RP37F  | R<5:0> |       |       | _     | _           |            |       | RP36  | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | —      |        |             | RP39F  | २<5:0> |       |       | _     | _           |            |       | RP38  | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | —      |        |             | RP41F  | २<5:0> |       |       | _     | _           | RP40R<5:0> |       |       |        |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |             | RP43F  | २<5:0> |       |       | —     | _           | RP42R<5:0> |       |       |        |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |        |             | RP55F  | २<5:0> |       |       | —     | _           | RP54R<5:0> |       |       |        |       |       | 0000          |

| RPOR6        | 068C  | _      | _      |        |             | RP57F  | २<5:0> |       |       | —     | _           |            |       | RP56  | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |        |             | RP97F  | २<5:0> |       |       | —     | _           | _          | _     | _     | _      | _     | _     | 0000          |

| RPOR8        | 0690  |        | _      |        | RP118R<5:0> |        |        |       |       | _     | _           |            |       |       |        |       | 0000  |               |

| RPOR9        | 0692  | —      | _      |        |             |        |        | _     | _     | _     | RP120R<5:0> |            |       |       |        | 0000  |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-56: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      |        | _      | _     | TRISA8 | _     | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | —      | —      | _      | —      | _      | —      | _     | —      | _     | —     | —     | ANSA4  | —      | —      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | -       | _       | -       | —       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | —      | —     | TRISC8 | _     | -     |       | _     |       | -     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  |        |        | -      | -      | -      | —      | _     | RC8    | —     | -     |       | _     |       |       | RC1    | RC0    | xxxx          |

| LATC         | 0E24  |        |        | _      | _      | _      | _      | _     | LATC8  | _     | _     | _     | _     | _     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  |        |        | _      | _      | _      | _      | _     | ODCC8  | _     | _     | _     | _     | _     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | _      | -      | _      |        | _      | _     | CNIEC8 | —     |       |       | _     |       |       | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  |        |        | _      | _      | _      | _      | _     | CNPUC8 | _     | _     | _     | _     | _     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  |        |        | _      | _      | _      | _      | _     | CNPDC8 | _     | _     | _     | _     | _     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | -      | _      | _      | _      | _      | —      | —     | —      | —     |       | _     | _     | _     |       | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|--------|-------|-------|--------|---------------------|-----|-------|-------|

| VAR    | —     | US1   | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15 | -     | •     |        |                     |     |       | bit 8 |

|        |       |       |        |                     |     |       |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7  |       | •     |        |                     |     |       | bit 0 |

|        |       |       |        |                     |     |       |       |

|        |       |       |        |                     |     |       |       |

## **REGISTER 7-2:** CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                      |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared | x = Bit is unknown |

bit

| VAR: Variable Exception Processing Latency Control                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>1 = Variable exception processing is enabled</li> </ol>                                                              |

| 0 = Fixed exception processing is enabled                                                                                     |

| IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                                |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

|                                                                                                                               |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### 11.7 **Peripheral Pin Select Registers**

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | _     | _     | —     |

| bit 7  |       | •     |       | •          |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                                                                                                                           | R/W-0            | R/W-0      | R/W-0             | R/W-0                        | R/W-0           | R/W-0 |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|-------------------|------------------------------|-----------------|-------|--|--|

| —               | —                                                                                                                                             |                  |            | RP57              | R<5:0>                       |                 |       |  |  |

| bit 15          |                                                                                                                                               |                  |            |                   |                              |                 | bit 8 |  |  |

|                 |                                                                                                                                               |                  |            |                   |                              |                 |       |  |  |

| U-0             | U-0                                                                                                                                           | R/W-0            | R/W-0      | R/W-0             | R/W-0                        | R/W-0           | R/W-0 |  |  |

| _               | —                                                                                                                                             |                  | RP56R<5:0> |                   |                              |                 |       |  |  |

| bit 7           |                                                                                                                                               |                  |            |                   |                              |                 | bit 0 |  |  |

|                 |                                                                                                                                               |                  |            |                   |                              |                 |       |  |  |

| Legend:         |                                                                                                                                               |                  |            |                   |                              |                 |       |  |  |

| R = Readable I  | bit                                                                                                                                           | W = Writable     | bit        | U = Unimplen      | implemented bit, read as '0' |                 |       |  |  |

| -n = Value at P | OR                                                                                                                                            | '1' = Bit is set | :          | '0' = Bit is clea | ared                         | x = Bit is unkr | iown  |  |  |

|                 |                                                                                                                                               |                  |            |                   |                              |                 |       |  |  |

| bit 15-14       | Unimplemen                                                                                                                                    | ted: Read as '   | 0'         |                   |                              |                 |       |  |  |

| bit 13-8        | 13-8 <b>RP57R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers) |                  |            |                   |                              |                 |       |  |  |

| bit 7-6         | Unimplemented: Read as '0'                                                                                                                    |                  |            |                   |                              |                 |       |  |  |

## REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

## REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|--|

| —      | —   |       | RP97R<5:0> |       |       |       |       |  |  |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |  |  |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                                    |  |  |  |

|-------------------|------------------|-----------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | I = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown                 |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

## 13.2 Timer Control Registers

| R/W-0         | U-0                                     | R/W-0                                                          | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |  |  |  |

|---------------|-----------------------------------------|----------------------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| TON           |                                         | TSIDL                                                          | —              | _                |                 |                 | _     |  |  |  |  |  |  |

| bit 15        |                                         |                                                                |                |                  |                 |                 | bit 8 |  |  |  |  |  |  |

|               |                                         |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |

| U-0           | R/W-0                                   | R/W-0                                                          | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |  |  |  |

| _             | TGATE                                   | TCKPS1                                                         | TCKPS0         | T32              | _               | TCS             | _     |  |  |  |  |  |  |

| bit 7         |                                         |                                                                |                |                  |                 |                 | bit ( |  |  |  |  |  |  |

| <u> </u>      |                                         |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |

| Legend:       | - 1-:4                                  |                                                                |                | II II.           |                 |                 |       |  |  |  |  |  |  |

| R = Readable  |                                         | W = Writable                                                   |                | -                | nented bit, rea |                 |       |  |  |  |  |  |  |

| -n = Value at | PUR                                     | '1' = Bit is set                                               |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |  |  |  |  |  |  |

| bit 15        | TON: Timerx                             | On hit                                                         |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | When T32 = 2                            |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 1 = Starts 32-                          | bit Timerx/y                                                   |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 0 = Stops 32-                           |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                         | When $T32 = 0$ :                                               |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                         | 1 = Starts 16-bit Timerx<br>0 = Stops 16-bit Timerx            |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 14        | Unimplemen                              | Unimplemented: Read as '0'                                     |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 13        | TSIDL: Timer                            | x Stop in Idle M                                               | lode bit       |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                         | 1 = Discontinues module operation when device enters Idle mode |                |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                         | s module opera                                                 |                | ode              |                 |                 |       |  |  |  |  |  |  |

| bit 12-7      | -                                       | ted: Read as '                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 6         |                                         | erx Gated Time                                                 | Accumulation   | Enable bit       |                 |                 |       |  |  |  |  |  |  |

|               | When TCS =<br>This bit is igno          |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | •                                       | When TCS = 0:                                                  |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 1 = Gated time accumulation is enabled  |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 0 = Gated time accumulation is disabled |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 5-4       |                                         | : Timerx Input                                                 | Clock Prescal  | e Select bits    |                 |                 |       |  |  |  |  |  |  |

|               | 11 = 1:256<br>10 = 1:64                 |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 01 = 1:8                                |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |

|               | 00 = 1:1                                |                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 3         | T32: 32-Bit Ti                          | mer Mode Sele                                                  | ect bit        |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                         | nd Timery form<br>nd Timery act as                             |                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 2         | Unimplemen                              | ted: Read as '                                                 | )'             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 1         | TCS: Timerx                             | Clock Source S                                                 | elect bit      |                  |                 |                 |       |  |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl       | clock is from pir<br>lock (FP)                                 | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |  |  |  |  |

| bit 0         | Unimplomon                              | ted: Read as '                                                 | ı'             |                  |                 |                 |       |  |  |  |  |  |  |

## REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

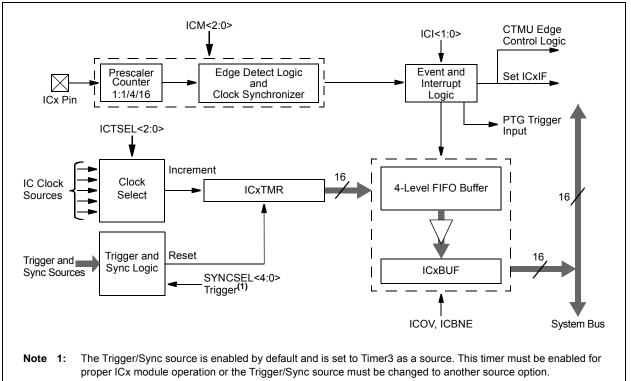

## 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

NOTES:

## REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

- bit 7-3 FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator # bits 11111 = Fault 32 (default) 11110 = Reserved . . 01100 = Reserved 01011 = Comparator 4 01010 = Op Amp/Comparator 3

- 01001 = Op Amp/Comparator 2

- 01000 = Op Amp/Comparator 1

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = Reserved

- 00011 = Fault 4

- 00010 = Fault 3

- 00001 = Fault 2 00000 = Fault 1

- bit 2 **FLTPOL:** Fault Polarity for PWM Generator # bit<sup>(2)</sup>

- 1 = The selected Fault source is active-low

- 0 = The selected Fault source is active-high

- bit 1-0 **FLTMOD<1:0>:** Fault Mode for PWM Generator # bits

- 11 = Fault input is disabled

- 10 = Reserved

- 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

- 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

- **Note 1:** If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

- 2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

## REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

| bit 1 | BUFM: Buffer Fill Mode Select bit                                                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Starts the buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on next interrupt</li> <li>0 = Always starts filling the buffer from the start address.</li> </ul> |

| bit 0 | ALTS: Alternate Input Sample Mode Select bit                                                                                                                                                                                    |

1 = Uses channel input selects for Sample MUXA on first sample and Sample MUXB on next sample 0 = Always uses channel input selects for Sample MUXA

## REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)</li> </ul> |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                      |

|         | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)                                                                                                                             |

|         | If CPOL = 1 (inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>Low-to-high transition of the comparator output                                                                                                                                                                       |

|         | 00 = Trigger/event/interrupt generation is disabled                                                                                                                                                                                                           |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 4   | <b>CREF:</b> Comparator Reference Select bit (VIN+ input) <sup>(1)</sup>                                                                                                                                                                                      |

|         | <ul> <li>1 = VIN+ input connects to internal CVREFIN voltage<sup>(2)</sup></li> <li>0 = VIN+ input connects to CxIN1+ pin</li> </ul>                                                                                                                          |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 1-0 | CCH<1:0>: Op Amp/Comparator Channel Select bits <sup>(1)</sup>                                                                                                                                                                                                |

|         | <ul> <li>11 = Unimplemented</li> <li>10 = Unimplemented</li> <li>01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup></li> <li>00 = Inverting input of the op amp/comparator connects to the CxIN1- pin</li> </ul>                 |

|         |                                                                                                                                                                                                                                                               |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

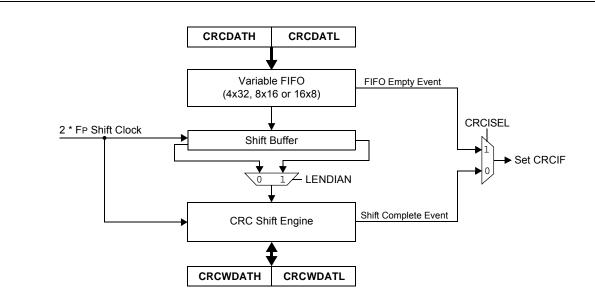

## 26.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Cyclic Redundancy Check (CRC)" (DS70346) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-programmable (up to 32nd order) polynomial CRC equation

- Interrupt output

- Data FIFO

The programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- Configurable interrupt output

- Data FIFO

A simplified block diagram of the CRC generator is shown in Figure 26-1. A simple version of the CRC shift engine is shown in Figure 26-2.

## FIGURE 26-1: CRC BLOCK DIAGRAM

| DC CHARACTERISTICS |        |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                                                                                                                                            |  |

|--------------------|--------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic                                              | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions                                                                                                                                                                                 |  |

| DO10 Vol           |        | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                                                                                                                                                                                                                                                                                       |      | 0.4  | V     | VDD = 3.3V,<br>$IOL \le 6 \text{ mA}$ , $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$<br>$IOL \le 5 \text{ mA}$ , $+85^{\circ}\text{C} < \text{TA} \le +125^{\circ}\text{C}$ |  |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                                                                                                                                                                                                                                                                                     |      | 0.4  | V     |                                                                                                                                                                                            |  |

| DO20               | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                                                                                                                                                                   |      | _    | V     | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                                      |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                                                                                                                                                                                   | _    | —    | V     | $IOH \ge -15 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                                      |  |

| DO20A              | Von1   | Output High Voltage                                         | 1.5(1)                                                                                                                                                                                                                                                                                | _    |      | V     | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                                       |  |

|                    |        | 4x Source Driver Pins <sup>(2)</sup>                        | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                    | _    | _    |       | $IOH \geq -12 ~mA, ~VDD = 3.3 V$                                                                                                                                                           |  |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                                | _    |      |       | $IOH \geq -7 \; mA,  VDD = 3.3 V$                                                                                                                                                          |  |

|                    |        | Output High Voltage                                         | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                                                                    | _    | —    | V     | $IOH \geq \textbf{-22 mA, VDD} = 3.3V$                                                                                                                                                     |  |

|                    |        | 8x Source Driver Pins <sup>(3)</sup>                        | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                    | _    | —    | 1     | IOH $\geq$ -18 mA, VDD = 3.3V                                                                                                                                                              |  |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                                | _    | —    | 1     | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                                       |  |

## TABLE 30-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<7:15> and RC3

For 64-pin devices: RA4, RA9, RB<7:15>, RC3 and RC15

## TABLE 30-13: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |      |       |                        |

|--------------------|--------|-------------------------------------------------------|---------------------|------|------|-------|------------------------|

| Param<br>No.       | Symbol | Characteristic                                        | Min. <sup>(2)</sup> | Тур. | Max. | Units | Conditions             |

| BO10               | VBOR   | BOR Event on VDD Transition<br>High-to-Low            | 2.65                | _    | 2.95 | V     | VDD<br>(Notes 2 and 3) |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance.

**2:** Parameters are for design guidance only and are not tested in manufacturing.

3: The VBOR specification is relative to VDD.

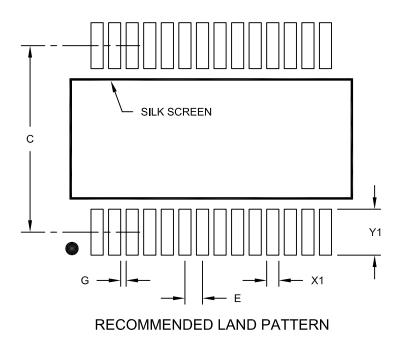

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |      |          |      |  |

|--------------------------|------------------|------|----------|------|--|

| Dimensior                | Dimension Limits |      |          | MAX  |  |

| Contact Pitch            | E                |      | 0.65 BSC |      |  |

| Contact Pad Spacing      | С                |      | 7.20     |      |  |

| Contact Pad Width (X28)  | X1               |      |          | 0.45 |  |

| Contact Pad Length (X28) | Y1               |      |          | 1.75 |  |

| Distance Between Pads    | G                | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

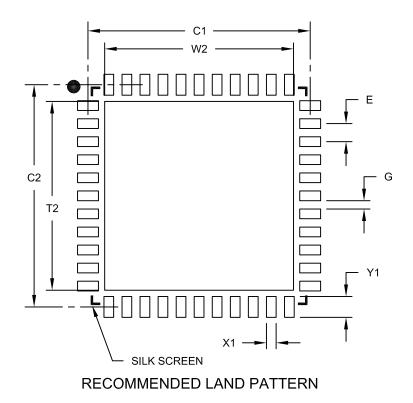

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.65 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 6.60 |

| Optional Center Pad Length | T2 |             |      | 6.60 |

| Contact Pad Spacing        | C1 |             | 8.00 |      |

| Contact Pad Spacing        | C2 |             | 8.00 |      |

| Contact Pad Width (X44)    | X1 |             |      | 0.35 |

| Contact Pad Length (X44)   | Y1 |             |      | 0.85 |

| Distance Between Pads      | G  | 0.25        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

NOTES: