Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc502-h-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0               | U-0                          | R/W-0                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |

|---------------------|------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|

| VAR                 | —                            | US1 <sup>(1)</sup>                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |

| bit 15              |                              |                                                          |                         |                             |                           |                    | bit                |

| R/W-0               | R/W-0                        | R/W-1                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>          | SATDW <sup>(1)</sup>                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |

| bit 7               | I                            |                                                          |                         |                             | I                         | 1                  | bit                |

| Legend:             |                              | C = Clearable                                            | e bit                   |                             |                           |                    |                    |

| R = Readabl         | e bit                        | W = Writable                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |

| -n = Value at       | POR                          | '1' = Bit is set                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |

| bit 15              | 1 = Variable                 | le Exception Pro<br>exception proce                      | essing latency          | is enabled                  |                           |                    |                    |

| bit 14              |                              | nted: Read as '                                          |                         |                             |                           |                    |                    |

| bit 13-12           | -                            | SP Multiply Uns                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |

|                     | 01 = DSP er<br>00 = DSP er   | ngine multiplies<br>ngine multiplies<br>ngine multiplies | are unsigned are signed |                             |                           |                    |                    |

| bit 11              | •                            | O Loop Terminatives executing Dot<br>t                   |                         |                             | iteration                 |                    |                    |

| bit 10-8            |                              | Loop Nesting<br>oops are active                          |                         | (1)                         |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | 001 = 1 DO k<br>000 = 0 DO k | oop is active<br>oops are active                         |                         |                             |                           |                    |                    |

| bit 7               | SATA: ACCA                   | A Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator A saturatio<br>ator A saturatio                     |                         |                             |                           |                    |                    |

| bit 6               | SATB: ACCE                   | B Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator B saturatio<br>ator B saturatio                     |                         |                             |                           |                    |                    |

| bit 5               | SATDW: Dat                   | ta Space Write                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |

|                     |                              | ace write satura<br>ace write satura                     |                         | I                           |                           |                    |                    |

| bit 4               |                              | cumulator Satu                                           |                         | elect bit <sup>(1)</sup>    |                           |                    |                    |

|                     |                              | uration (super s<br>uration (normal                      | ,                       |                             |                           |                    |                    |

| bit 3               |                              | nterrupt Priority                                        |                         |                             |                           |                    |                    |

|                     |                              | errupt Priority Le<br>errupt Priority Le                 |                         |                             |                           |                    |                    |

|                     | nis bit is availabl          |                                                          | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP                | 50X devices on     | ly.                |

| 2: Th               | nis bit is always            | reau as 0.                                               |                         |                             |                           |                    |                    |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| IABLE 4-2  | 23: E | CAN1 I | REGIST | ER MA  | P WHE  | N WIN  | (CICIE | <l1<0></l1<0> | •) = 1 FC | OR dsPIC | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|-------|--------|--------|--------|--------|--------|--------|---------------|-----------|----------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | 046E  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF12SID | 0470  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF13SID | 0474  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF14SID | 0478  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF15SID | 047C  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF15EID | 047E  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | —      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | —      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | _      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### EXAMPLE 4-3: PAGED DATA MEMORY SPACE

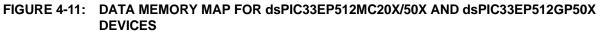

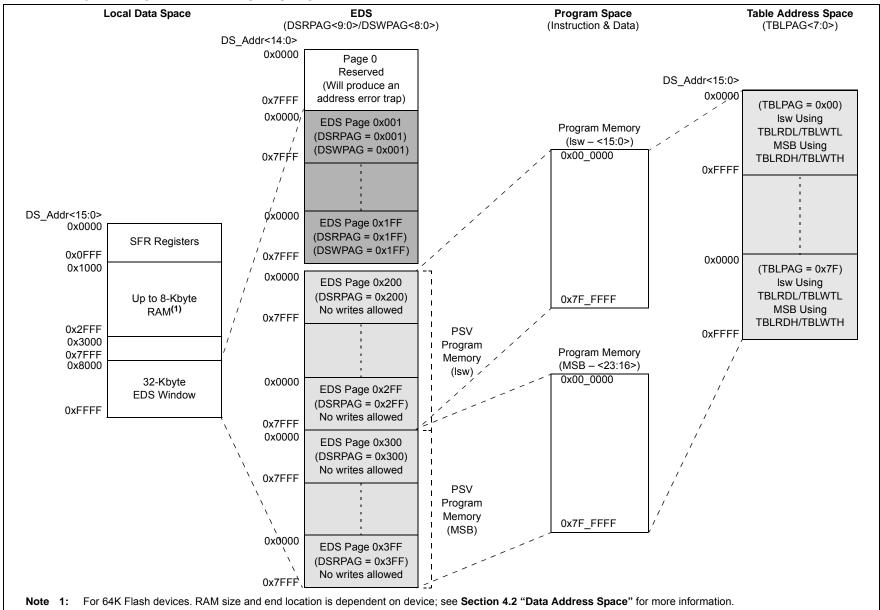

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

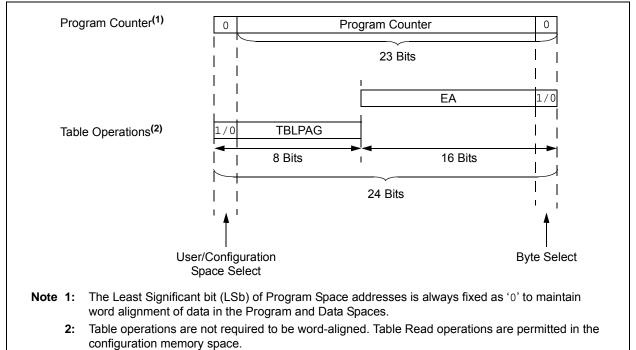

### 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

### TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address     |            |                     |        |     |  |  |  |  |

|------------------------|---------------|---------------------------|------------|---------------------|--------|-----|--|--|--|--|

| Access Type            | Space         | <23>                      | <22:16>    | <15>                | <14:1> | <0> |  |  |  |  |

| Instruction Access     | User          | 0 PC<22:1>                |            |                     |        |     |  |  |  |  |

| (Code Execution)       |               |                           | 0xx xxxx x | xxx xxx             |        |     |  |  |  |  |

| TBLRD/TBLWT            | User          | TBLPAG<7:0> Data EA<15:0> |            |                     |        |     |  |  |  |  |

| (Byte/Word Read/Write) |               | 0                         | xxx xxxx   | xxxx xxxx xxxx xxxx |        |     |  |  |  |  |

|                        | Configuration | TB                        | LPAG<7:0>  | Data EA<15:0>       |        |     |  |  |  |  |

|                        |               | 1                         | xxx xxxx   | XXXX XX             | ***    |     |  |  |  |  |

### FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

### 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "*dsPIC33/PIC24 Family Reference Manual*".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0          | U-0          | U-0                                    | U-0           | U-0                | U-0              | U-0             | U-0    |

|--------------|--------------|----------------------------------------|---------------|--------------------|------------------|-----------------|--------|

| —            | —            | —                                      | —             | —                  | —                | —               | —      |

| bit 15       |              |                                        |               |                    |                  |                 | bit 8  |

|              |              |                                        |               |                    |                  |                 |        |

| U-0          | U-0          | U-0                                    | U-0           | R-0                | R-0              | R-0             | R-0    |

|              | <u> </u>     | <u> </u>                               | _             | PWCOL3             | PWCOL2           | PWCOL1          | PWCOL0 |

| bit 7        |              |                                        |               |                    |                  |                 | bit 0  |

|              |              |                                        |               |                    |                  |                 |        |

| Legend:      |              |                                        |               |                    |                  |                 |        |

| R = Readab   | le bit       | W = Writable                           | bit           | U = Unimpler       | mented bit, read | as '0'          |        |

| -n = Value a | t POR        | '1' = Bit is set                       |               | '0' = Bit is cle   | ared             | x = Bit is unkr | nown   |

|              |              |                                        |               |                    |                  |                 |        |

| bit 15-4     | Unimplemen   | ted: Read as '                         | 0'            |                    |                  |                 |        |

| bit 3        | PWCOL3: DI   | MA Channel 3 F                         | Peripheral Wi | rite Collision Fla | ag bit           |                 |        |

|              |              | lision is detecte                      |               |                    |                  |                 |        |

|              |              | collision is dete                      |               |                    |                  |                 |        |

| bit 2        |              |                                        | •             | rite Collision Fla | ag bit           |                 |        |

|              |              | lision is detecte<br>collision is dete |               |                    |                  |                 |        |

| bit 1        |              |                                        |               | rite Collision Fla | a hit            |                 |        |

| DILI         |              | lision is detecte                      | •             |                    |                  |                 |        |

|              |              | collision is dete                      |               |                    |                  |                 |        |

| bit 0        | PWCOL0: DI   | MA Channel 0 F                         | Peripheral Wi | rite Collision Fla | ag bit           |                 |        |

|              |              | lision is detecte                      | •             | -                  | <b>č</b>         |                 |        |

|              | 0 = No write | collision is dete                      | ected         |                    |                  |                 |        |

|              |              |                                        |               |                    |                  |                 |        |

## REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

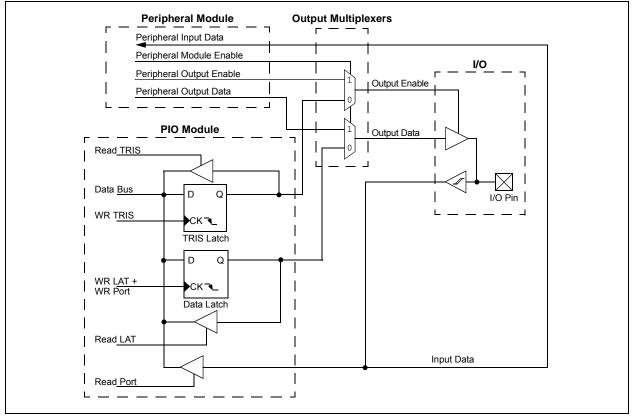

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

# 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

NOTES:

### 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | R/W-0                                                                    | R/W-0                                                | R/W-0                           | U-0               | U-0              | U-0                    | R/W-0        |

|------------|--------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-------------------|------------------|------------------------|--------------|

| FLTMD      | FLTOUT                                                                   | FLTTRIEN                                             | OCINV                           | —                 | _                | —                      | OC32         |

| bit 15     | ·                                                                        |                                                      |                                 |                   | ·                |                        | bit          |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| R/W-0      | R/W-0, HS                                                                | R/W-0                                                | R/W-0                           | R/W-1             | R/W-1            | R/W-0                  | R/W-0        |

| OCTRIC     | G TRIGSTAT                                                               | OCTRIS                                               | SYNCSEL4                        | SYNCSEL3          | SYNCSEL2         | SYNCSEL1               | SYNCSEL      |

| bit 7      |                                                                          |                                                      |                                 |                   |                  |                        | bit          |

| Legend:    |                                                                          | HS = Hardwa                                          | re Settable bit                 |                   |                  |                        |              |

| R = Reada  | able bit                                                                 | W = Writable                                         | bit                             | U = Unimplem      | nented bit, read | l as '0'               |              |

| -n = Value | at POR                                                                   | '1' = Bit is set                                     |                                 | '0' = Bit is clea | ared             | x = Bit is unkn        | iown         |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| bit 15     | 1 = Fault mo<br>cleared i                                                | t Mode Select b<br>ode is maintain<br>n software and | ed until the Fa<br>a new PWM pe | eriod starts      |                  |                        |              |

|            |                                                                          | de is maintaine                                      | d until the Faul                | t source is rem   | loved and a ne   | w PWM period           | starts       |

| bit 14     | FLTOUT: Fau                                                              |                                                      | . –                             |                   |                  |                        |              |

|            |                                                                          | tput is driven hi<br>tput is driven lo               |                                 |                   |                  |                        |              |

| bit 13     |                                                                          | ault Output Sta                                      |                                 |                   |                  |                        |              |

|            |                                                                          | is tri-stated on                                     |                                 | 'n                |                  |                        |              |

|            | •                                                                        | I/O state is defi                                    |                                 |                   | ault condition   |                        |              |

| bit 12     | OCINV: Outp                                                              | ut Compare x I                                       | nvert bit                       |                   |                  |                        |              |

|            |                                                                          | out is inverted<br>out is not invert                 | ed                              |                   |                  |                        |              |

| bit 11-9   | Unimplemen                                                               | ted: Read as '                                       | כי                              |                   |                  |                        |              |

| bit 8      | OC32: Casca                                                              | ide Two OCx M                                        | odules Enable                   | bit (32-bit oper  | ration)          |                        |              |

|            |                                                                          | module operate module operate                        |                                 |                   |                  |                        |              |

| bit 7      |                                                                          | tput Compare x                                       |                                 | Select bit        |                  |                        |              |

|            |                                                                          | OCx from the s                                       |                                 |                   | CSELx bits       |                        |              |

|            |                                                                          | nizes OCx with                                       |                                 |                   |                  | S                      |              |

| bit 6      | TRIGSTAT: T                                                              | imer Trigger St                                      | atus bit                        |                   |                  |                        |              |

|            |                                                                          | urce has been <sup>.</sup><br>urce has not be        |                                 |                   | d clear          |                        |              |

| bit 5      |                                                                          | put Compare x                                        |                                 | •                 |                  |                        |              |

|            | 1 = OCx is tr                                                            | • •                                                  | ·                               |                   |                  |                        |              |

|            | 0 = Output C                                                             | ompare x mod                                         | ule drives the C                | OCx pin           |                  |                        |              |

| Note 1:    | Do not use the O                                                         | Cx module as i                                       | ts own Svnchro                  | nization or Tric  | aaer source.     |                        |              |

|            | When the OCy m                                                           |                                                      | -                               |                   |                  | module uses t          | he OCv       |

|            | module as a Trigg                                                        |                                                      |                                 |                   |                  |                        |              |

| 3:         | Each Output Con<br><b>"Peripheral Trig</b><br>PTGO0 = OC1<br>PTGO1 = OC2 |                                                      |                                 |                   |                  | n source. See <b>S</b> | Section 24.0 |

|            | PTGO2 = OC3 $PTGO3 = OC4$                                                |                                                      |                                 |                   |                  |                        |              |

### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

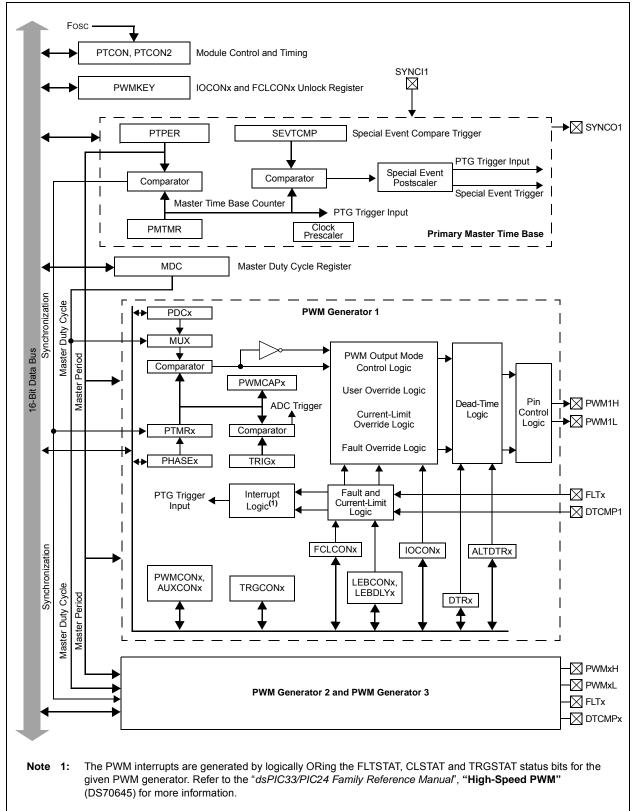

#### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

| R/W-1           | R/W-1              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           | R/W-0  |

|-----------------|--------------------|----------------------------------------|----------------------------|----------------------|---------------------------|-----------------|--------|

| PENH            | PENL               | POLH                                   | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>      | OVRENH          | OVRENL |

| bit 15          |                    | •                                      |                            |                      |                           |                 | bit    |

| R/W-0           | R/W-0              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           |        |

| -               | -                  | -                                      |                            | -                    | -                         | -               | R/W-0  |

| OVRDAT1         | OVRDAT0            | FLTDAT1                                | FLTDAT0                    | CLDAT1               | CLDAT0                    | SWAP            | OSYNC  |

| bit 7           |                    |                                        |                            |                      |                           |                 | bit    |

| Legend:         |                    |                                        |                            |                      |                           |                 |        |

| R = Readable    | bit                | W = Writable                           | bit                        | U = Unimpler         | nented bit, read          | l as '0'        |        |

| -n = Value at F | POR                | '1' = Bit is set                       |                            | '0' = Bit is cle     | ared                      | x = Bit is unkr | nown   |

| bit 15          |                    | xH Output Pin                          | Ownorshin hit              |                      |                           |                 |        |

| bit 15          |                    | odule controls                         | •                          |                      |                           |                 |        |

|                 |                    | dule controls F                        |                            |                      |                           |                 |        |

| bit 14          |                    | L Output Pin                           | •                          |                      |                           |                 |        |

|                 | 1 = PWMx mo        | odule controls                         | PWMxL pin                  |                      |                           |                 |        |

|                 | 0 = GPIO mo        | dule controls F                        | WMxL pin                   |                      |                           |                 |        |

| bit 13          | POLH: PWM          | xH Output Pin                          | Polarity bit               |                      |                           |                 |        |

|                 |                    | oin is active-low                      |                            |                      |                           |                 |        |

|                 |                    | oin is active-hig                      | •                          |                      |                           |                 |        |

| bit 12          |                    | L Output Pin F                         | •                          |                      |                           |                 |        |

|                 |                    | in is active-low<br>in is active-hig   |                            |                      |                           |                 |        |

| bit 11-10       | PMOD<1:0>:         | PWMx # I/O F                           | in Mode bits <sup>(1</sup> | )                    |                           |                 |        |

|                 | 11 = Reserve       | ,                                      |                            |                      |                           |                 |        |

|                 |                    | /O pin pair is ir<br>/O pin pair is ir |                            |                      |                           |                 |        |

|                 |                    | O pin pair is in<br>O pin pair is ir   |                            |                      |                           |                 |        |

| bit 9           |                    | verride Enable                         | •                          |                      |                           |                 |        |

|                 |                    | <1> controls or                        |                            |                      |                           |                 |        |

|                 |                    | nerator contro                         | •                          | •                    |                           |                 |        |

| bit 8           | OVRENL: Ov         | erride Enable                          | for PWMxL Pir              | n bit                |                           |                 |        |

|                 | 1 = OVRDAT         | <0> controls or                        | utput on PWM               | xL pin               |                           |                 |        |

|                 | •                  | nerator contro                         |                            |                      |                           |                 |        |

| bit 7-6         |                    |                                        |                            |                      | de is Enabled b           |                 |        |

|                 |                    |                                        |                            |                      | by OVRDAT<<br>by OVRDAT<0 |                 |        |

| bit 5-4         | FLTDAT<1:0         | >: Data for PW                         | MxH and PWN                | ۰<br>MxL Pins if FLT | MOD is Enable             | ed bits         |        |

|                 | If Fault is active | ve, PWMxH is                           | driven to the s            | tate specified       | by FLTDAT<1>.             |                 |        |

|                 | If Fault is active | ve, PWMxL is                           | driven to the s            | tate specified b     | by FLTDAT<0>.             |                 |        |

| bit 3-2         | CLDAT<1:0>         | : Data for PWN                         | /IxH and PWM               | xL Pins if CLM       | 10D is Enabled            | bits            |        |

|                 |                    |                                        |                            | •                    | ecified by CLDA           |                 |        |

|                 |                    | IS AULIVE. F VVI                       |                            |                      |                           |                 |        |

| Note 1: The     |                    |                                        |                            |                      | enabled (PTEN             |                 |        |

# REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | R/W-x                        | U-0                                     | U-0             | U-0              | R/W-x            | R/W-x           | R/W-x   |

|---------------|------------------------------|-----------------------------------------|-----------------|------------------|------------------|-----------------|---------|

| _             | WAKFIL                       | _                                       | —               |                  | SEG2PH2          | SEG2PH1         | SEG2PH0 |

| bit 15        |                              |                                         |                 |                  |                  |                 | bit     |

| R/W-x         | R/W-x                        | R/W-x                                   | R/W-x           | R/W-x            | R/W-x            | R/W-x           | R/W-x   |

|               |                              |                                         |                 | 1                |                  | 1               |         |

| SEG2PHTS      | SAM                          | SEG1PH2                                 | SEG1PH1         | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |

| bit 7         |                              |                                         |                 |                  |                  |                 | bit     |

| Legend:       |                              |                                         |                 |                  |                  |                 |         |

| R = Readable  | e bit                        | W = Writable                            | bit             | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value at | POR                          | '1' = Bit is set                        |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|               |                              |                                         |                 |                  |                  |                 |         |

| bit 15        | Unimplemer                   | nted: Read as '                         | 0'              |                  |                  |                 |         |

| bit 14        |                              | lect CAN Bus L                          |                 | Vake-up bit      |                  |                 |         |

|               |                              | N bus line filter<br>line filter is not |                 | e-up             |                  |                 |         |

| bit 13-11     | Unimplemer                   | nted: Read as '                         | 0'              |                  |                  |                 |         |

| bit 10-8      | SEG2PH<2:0                   | 0>: Phase Segr                          | nent 2 bits     |                  |                  |                 |         |

|               | 111 = Length                 | -                                       |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | 000 = Length                 | n is 1 x Tq                             |                 |                  |                  |                 |         |

| bit 7         |                              | Phase Segmer                            | nt 2 Time Sele  | ct bit           |                  |                 |         |

|               | 1 = Freely pr<br>0 = Maximun | ogrammable<br>n of SEG1PHx I            | oits or Informa | tion Processin   | g Time (IPT), w  | hichever is gre | ater    |

| bit 6         | SAM: Sample                  | e of the CAN B                          | us Line bit     |                  |                  | -               |         |

|               |                              | is sampled three<br>is sampled once     |                 |                  |                  |                 |         |

| bit 5-3       | SEG1PH<2:0                   | 0>: Phase Segr                          | nent 1 bits     | -                |                  |                 |         |

|               | 111 = Length                 | n is 8 x Tq                             |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               | 000 = Length                 |                                         |                 |                  |                  |                 |         |

| bit 2-0       |                              | >: Propagation                          | Time Segmen     | t bits           |                  |                 |         |

|               | 111 = Length                 | n is 8 x Tq                             |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

|               |                              |                                         |                 |                  |                  |                 |         |

|               | •                            |                                         |                 |                  |                  |                 |         |

### REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

### 22.2 CTMU Control Registers

| REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1                                                                                                                    |                            |                  |       |                      |          |                        |        |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|-------|----------------------|----------|------------------------|--------|--|

| R/W-0                                                                                                                                                               | U-0                        | R/W-0            | R/W-0 | R/W-0                | R/W-0    | R/W-0                  | R/W-0  |  |

| CTMUEN —                                                                                                                                                            |                            | CTMUSIDL         | TGEN  | EDGEN                | EDGSEQEN | IDISSEN <sup>(1)</sup> | CTTRIG |  |

| bit 15                                                                                                                                                              |                            |                  |       |                      |          |                        | bit 8  |  |

|                                                                                                                                                                     |                            |                  |       |                      |          |                        |        |  |

| U-0                                                                                                                                                                 | U-0                        | U-0              | U-0   | U-0                  | U-0      | U-0                    | U-0    |  |

| _                                                                                                                                                                   |                            |                  | _     |                      | <u> </u> |                        | _      |  |

| bit 7                                                                                                                                                               |                            |                  |       |                      |          |                        | bit 0  |  |

|                                                                                                                                                                     |                            |                  |       |                      |          |                        |        |  |

| Legend:                                                                                                                                                             |                            |                  |       |                      |          |                        |        |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                                                                                                  |                            |                  |       |                      |          |                        |        |  |

| -n = Value at POR                                                                                                                                                   |                            | '1' = Bit is set |       | '0' = Bit is cleared |          | x = Bit is unknown     |        |  |

| bit 15 CTMUEN: CTMU Enable bit<br>1 = Module is enabled<br>0 = Module is disabled                                                                                   |                            |                  |       |                      |          |                        |        |  |

| bit 14                                                                                                                                                              | Unimplemented: Read as '0' |                  |       |                      |          |                        |        |  |

| bit 13 <b>CTMUSIDL:</b> CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |                            |                  |       |                      |          |                        |        |  |

| bit 12 <b>TGEN:</b> Time Generation Enable bit                                                                                                                      |                            |                  |       |                      |          |                        |        |  |

#### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

| Base<br>Instr<br># Assembly<br>Mnemonic |        |             |                                           | Description                                                | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|-----------------------------------------|--------|-------------|-------------------------------------------|------------------------------------------------------------|---------------|-------------------------------|--------------------------|

| 9                                       | BTG    | BTG f,#bit4 |                                           | Bit Toggle f                                               | 1             | 1                             | None                     |

|                                         |        | BTG         | Ws,#bit4                                  | Bit Toggle Ws                                              | 1             | 1                             | None                     |

| 10                                      | BTSC   | BTSC        | f,#bit4                                   | Bit Test f, Skip if Clear                                  | 1             | 1<br>(2 or 3)                 | None                     |

|                                         |        | BTSC        | Ws,#bit4                                  | Bit Test Ws, Skip if Clear                                 | 1             | 1<br>(2 or 3)                 | None                     |

| 11                                      | BTSS   | BTSS        | f,#bit4                                   | Bit Test f, Skip if Set                                    | 1             | 1<br>(2 or 3)                 | None                     |

|                                         |        | BTSS        | Ws,#bit4                                  | Bit Test Ws, Skip if Set                                   | 1             | 1<br>(2 or 3)                 | None                     |

| 12                                      | BTST   | BTST        | f,#bit4                                   | Bit Test f                                                 | 1             | 1                             | Z                        |

|                                         |        | BTST.C      | Ws,#bit4                                  | Bit Test Ws to C                                           | 1             | 1                             | С                        |

|                                         |        | BTST.Z      | Ws,#bit4                                  | Bit Test Ws to Z                                           | 1             | 1                             | Z                        |

|                                         |        | BTST.C      | Ws,Wb                                     | Bit Test Ws <wb> to C</wb>                                 | 1             | 1                             | С                        |

|                                         |        | BTST.Z      | Ws,Wb                                     | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1                             | Z                        |

| 13                                      | BTSTS  | BTSTS       | f,#bit4                                   | Bit Test then Set f                                        | 1             | 1                             | Z                        |

|                                         |        | BTSTS.C     | Ws,#bit4                                  | Bit Test Ws to C, then Set                                 | 1             | 1                             | С                        |

|                                         |        | BTSTS.Z     | Ws,#bit4                                  | Bit Test Ws to Z, then Set                                 | 1             | 1                             | Z                        |

| 14                                      | CALL   | CALL        | lit23                                     | Call subroutine                                            | 2             | 4                             | SFA                      |

|                                         |        | CALL        | Wn                                        | Call indirect subroutine                                   | 1             | 4                             | SFA                      |

|                                         |        | CALL.L      | Wn                                        | Call indirect subroutine (long address)                    | 1             | 4                             | SFA                      |

| 15                                      | CLR    | CLR         | f                                         | f = 0x0000                                                 | 1             | 1                             | None                     |

|                                         |        | CLR         | WREG                                      | WREG = 0x0000                                              | 1             | 1                             | None                     |

|                                         |        | CLR         | Ws                                        | Ws = 0x0000                                                | 1             | 1                             | None                     |

|                                         |        | CLR         | Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Clear Accumulator                                          | 1             | 1                             | OA,OB,SA,SB              |

| 16                                      | CLRWDT | CLRWDT      |                                           | Clear Watchdog Timer                                       | 1             | 1                             | WDTO,Sleep               |

| 17 сом                                  |        | COM         | f                                         | f = f                                                      | 1             | 1                             | N,Z                      |

|                                         |        | COM         | f,WREG                                    | WREG = f                                                   | 1             | 1                             | N,Z                      |

|                                         |        | COM         | Ws,Wd                                     | $Wd = \overline{Ws}$                                       | 1             | 1                             | N,Z                      |

| 18                                      | CP     | CP          | f                                         | Compare f with WREG                                        | 1             | 1                             | C,DC,N,OV,Z              |

| -                                       |        | CP          | Wb,#lit8                                  | Compare Wb with lit8                                       | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | CP          | Wb,Ws                                     | Compare Wb with Ws (Wb – Ws)                               | 1             | 1                             | C,DC,N,OV,Z              |

| 19                                      | CP0    | CPO         | f                                         | Compare f with 0x0000                                      | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | CPO         | Ws                                        | Compare Ws with 0x0000                                     | 1             | 1                             | C,DC,N,OV,Z              |

| 20                                      | CPB    | CPB         | f                                         | Compare f with WREG, with Borrow                           | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | CPB         | Wb,#lit8                                  | Compare Wb with lit8, with Borrow                          | 1             | 1                             | C,DC,N,OV,Z              |

|                                         |        | CPB         | Wb,Ws                                     | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

| 21                                      | CPSEQ  | CPSEQ       | Wb,Wn                                     | Compare Wb with Wn, skip if =                              | 1             | 1<br>(2 or 3)                 | None                     |

|                                         | CPBEQ  | CPBEQ       | Wb,Wn,Expr                                | Compare Wb with Wn, branch if =                            | 1             | 1 (5)                         | None                     |

| 22                                      | CPSGT  | CPSGT       | Wb,Wn                                     | Compare Wb with Wn, skip if >                              | 1             | 1<br>(2 or 3)                 | None                     |

|                                         | CPBGT  | CPBGT       | Wb,Wn,Expr                                | Compare Wb with Wn, branch if >                            | 1             | 1 (5)                         | None                     |

| 23                                      | CPSLT  | CPSLT       | Wb,Wn                                     | Compare Wb with Wn, skip if <                              | 1             | 1<br>(2 or 3)                 | None                     |

|                                         | CPBLT  | CPBLT       | Wb,Wn,Expr                                | Compare Wb with Wn, branch if <                            | 1             | 1 (5)                         | None                     |

| 24                                      | CPSNE  | CPSNE       | Wb,Wn                                     | Compare Wb with Wn, skip if ≠                              | 1             | 1<br>(2 or 3)                 | None                     |

| ľ                                       | CPBNE  | CPBNE       | Wb,Wn,Expr                                | Compare Wb with Wn, branch if ≠                            | 1             | 1 (5)                         | None                     |

| <b>TABLE 28-2:</b> | <b>INSTRUCTION SET OVERVIEW (</b> | CONTINUED) | ) |

|--------------------|-----------------------------------|------------|---|

|                    |                                   | CONTINUED  | , |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction