Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc502-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1 (General Purpose Families) and Table 2 (Motor Control Families). Their pinout diagrams appear on the following pages.

|                   | â                              | (se                           |             |                      | Rei           | nappa          | ble Pe | eriphe             | rals                          |                                    |      |               |                              |                     |      |          |          |           |                                |

|-------------------|--------------------------------|-------------------------------|-------------|----------------------|---------------|----------------|--------|--------------------|-------------------------------|------------------------------------|------|---------------|------------------------------|---------------------|------|----------|----------|-----------|--------------------------------|

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbyte) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | UART   | SPI <sup>(2)</sup> | ECAN <sup>TM</sup> Technology | External Interrupts <sup>(3)</sup> | I²C™ | CRC Generator | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | РТС      | I/O Pins | Pins      | Packages                       |

| PIC24EP32GP202    | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           |                                |

| PIC24EP64GP202    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           | SPDIP,                         |

| PIC24EP128GP202   | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | —                             | 3                                  | 2    | 1             | 6                            | 2/3(1)              | Yes  | Yes      | 21       | 28        | SOIC,<br>SSOP <sup>(4)</sup> , |

| PIC24EP256GP202   | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           | QFN-S                          |

| PIC24EP512GP202   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           |                                |

| PIC24EP32GP203    | 512                            | 32                            | 4           | 5                    | 4             | 4              | 2      | 2                  |                               | 3                                  | 2    | 1             | 8                            | 3/4                 | Vaa  | Vaa      | 25       | 36        | VTLA                           |

| PIC24EP64GP203    | 1024                           | 64                            | 8           | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    |               | 0                            | 3/4                 | Yes  | Yes      | 25       | 30        | VILA                           |

| PIC24EP32GP204    | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           |                                |

| PIC24EP64GP204    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           | VTLA <sup>(4)</sup> ,          |

| PIC24EP128GP204   | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    | 1             | 9                            | 3/4                 | Yes  | Yes      | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| PIC24EP256GP204   | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           | UQFN                           |

| PIC24EP512GP204   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           |                                |

| PIC24EP64GP206    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           |                                |

| PIC24EP128GP206   | 1024                           | 128                           | 16          | _                    |               |                |        |                    |                               |                                    | -    |               |                              | ~ ~ ~               |      |          |          | ~ /       | TQFP.                          |

| PIC24EP256GP206   | 1024                           | 256                           | 32          | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    | 1             | 16                           | 3/4                 | Yes  | Yes      | 53       | 64        | QFN                            |

| PIC24EP512GP206   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           |                                |

| dsPIC33EP32GP502  | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           |                                |

| dsPIC33EP64GP502  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           | SPDIP,                         |

| dsPIC33EP128GP502 | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 6                            | 2/3(1)              | Yes  | Yes      | 21       | 28        | SOIC,<br>SSOP <sup>(4)</sup> . |

| dsPIC33EP256GP502 | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           | QFN-S                          |

| dsPIC33EP512GP502 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           |                                |

| dsPIC33EP32GP503  | 512                            | 32                            | 4           | _                    | _             | _              | _      | _                  |                               | _                                  | _    |               | _                            |                     |      |          |          |           |                                |

| dsPIC33EP64GP503  | 1024                           | 64                            | 8           | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 8                            | 3/4                 | Yes  | Yes      | 25       | 36        | VTLA                           |

| dsPIC33EP32GP504  | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              | İ                   |      |          |          |           |                                |

| dsPIC33EP64GP504  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           | VTLA <sup>(4)</sup> ,          |

| dsPIC33EP128GP504 | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 9                            | 3/4                 | Yes  | Yes      | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| dsPIC33EP256GP504 | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          | 40        | UQFN,<br>UQFN                  |

| dsPIC33EP512GP504 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           |                                |

| dsPIC33EP64GP506  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              | 1                   |      |          |          |           |                                |

| dsPIC33EP128GP506 | 1024                           | 128                           | 16          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           | TQFP,                          |

| dsPIC33EP256GP506 | 1024                           | 256                           | 32          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 2 1           | 16 3                         | 3/4 Yes             | Yes  | es Yes 5 | 53       | 64        | 64 QFN                         |

| dsPIC33EP512GP506 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |          |          |           |                                |

|                   |                                | 1                             |             |                      |               | 1              | 1      | 1                  |                               |                                    | 1    | 1             | 1                            |                     |      |          |          |           |                                |

#### TABLE 1: dsPIC33EPXXXGP50X and PIC24EPXXXGP20X GENERAL PURPOSE FAMILIES

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

Only SPI2 is remappable.

INT0 is not remappable.

4: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

### **Table of Contents**

| 1.0   | Device Overview                                                                                    |     |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             |     |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           |     |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

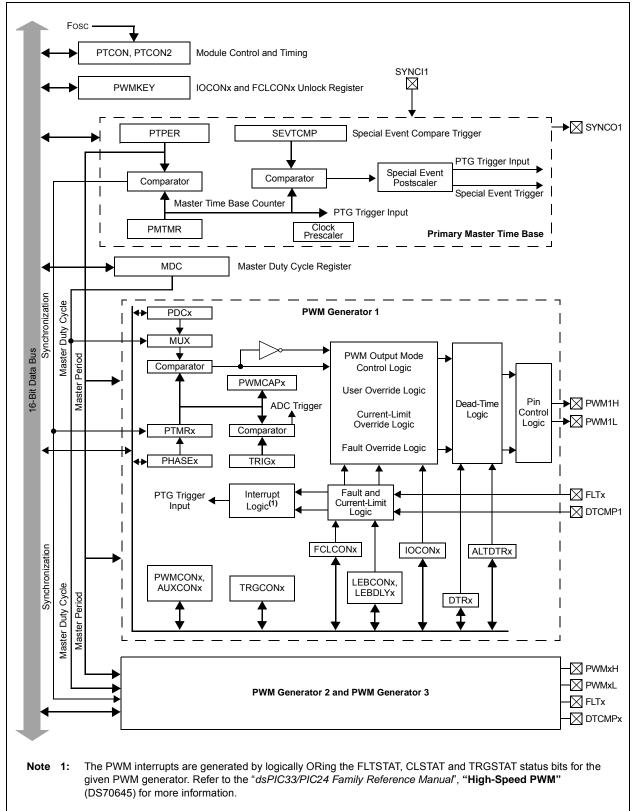

|       | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     |     |

|       | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) |     |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

|       | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      |     |

|       | Universal Asynchronous Receiver Transmitter (UART)                                                 |     |

|       | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    |     |

|       | Charge Time Measurement Unit (CTMU)                                                                |     |

|       | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    |     |

|       | Peripheral Trigger Generator (PTG) Module                                                          |     |

| 25.0  | Op Amp/Comparator Module                                                                           |     |

|       | Programmable Cyclic Redundancy Check (CRC) Generator                                               |     |

| 27.0  |                                                                                                    |     |

|       |                                                                                                    |     |

| 29.0  | Development Support                                                                                |     |

|       | Electrical Characteristics                                                                         |     |

|       | High-Temperature Electrical Characteristics                                                        |     |

|       | DC and AC Device Characteristics Graphs                                                            |     |

|       | Packaging Information                                                                              |     |

|       | ndix A: Revision History                                                                           |     |

|       | (                                                                                                  |     |

|       | Vicrochip Web Site                                                                                 |     |

|       | omer Change Notification Service                                                                   |     |

|       | omer Support                                                                                       |     |

| Produ | uct Identification System                                                                          | 527 |

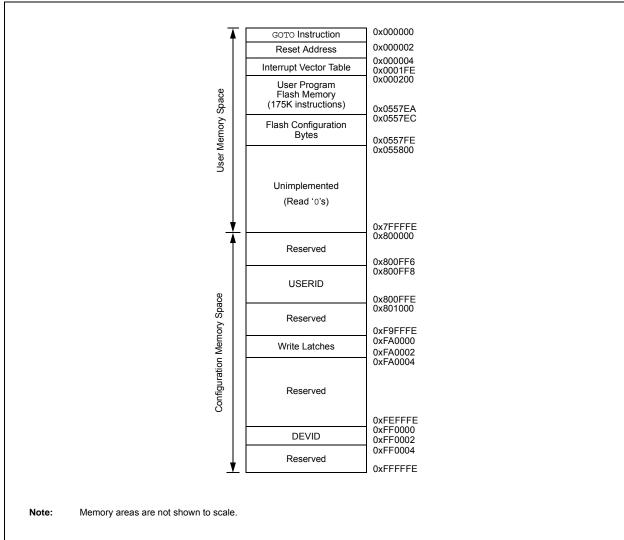

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

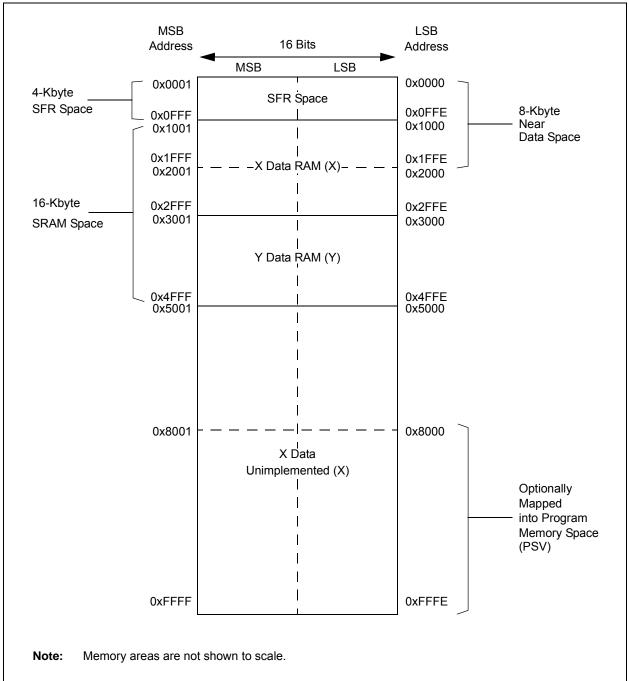

# FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC23        | 086E  |        | F      | PWM2IP<2:0 | )>      |         | Р      | WM1IP<2:   | 0>    |          |         | _           |         | —       | _      | -           |        | 4400          |

| IPC24        | 0870  |        | _      | _          | _       | -       | _      | _          | _     | _        | _       | _           | _       | _       | F      | WM3IP<2:0>  |        | 0004          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >       | -       |        | ICDIP<2:0  | >     | _        | _       | _           | _       | _       | _      | _           | _      | 4400          |

| IPC36        | 0888  |        | I      | PTG0IP<2:0 | )>      | -       | PT     | GWDTIP<    | 2:0>  | _        | P       | GSTEPIP<2:  | :0>     | _       | _      | _           | _      | 4440          |

| IPC37        | 088A  | _      | _      |            | —       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | •       | —       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | _       | _      | _          |       |          |         | _           |         | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      |            | —       | _       | _      | _          |       |          |         | DAE         | DOOVR   | _       | —      | _           |        | 0000          |

| INTCON4      | 08C6  | _      | _      |            | —       | _       | _      | _          | _     | _        |         | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | —      | -          | —       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | JM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                                     | U-0                                    | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |

|---------------|-------------------------------------------|----------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|

| TRAPF         | R IOPUWR                                  | —                                      | _             | VREGSF                | —                 | CM               | VREGS         |

| bit 15        |                                           |                                        |               |                       |                   |                  | bit 8         |

|               |                                           | DANIO                                  | DAA/ O        | DAMA                  | DAMO              |                  |               |

| R/W-0         |                                           | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR<br>bit 7 | SWR                                       | SWDTEN <sup>(2)</sup>                  | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |

|               |                                           |                                        |               |                       |                   |                  | bit (         |

| Legend:       |                                           |                                        |               |                       |                   |                  |               |

| R = Reada     | able bit                                  | W = Writable I                         | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |

| -n = Value    | at POR                                    | '1' = Bit is set                       |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |

|               |                                           |                                        |               |                       |                   |                  |               |

| bit 15        | •                                         | Reset Flag bit                         |               |                       |                   |                  |               |

|               |                                           | onflict Reset ha<br>onflict Reset ha   |               | d                     |                   |                  |               |

| bit 14        | •                                         | gal Opcode or                          |               |                       | et Flag bit       |                  |               |

|               |                                           | I opcode detec                         |               |                       | •                 | lized W registe  | er used as ar |

|               |                                           | Pointer caused                         |               |                       |                   |                  |               |

|               | -                                         | l opcode or Uni                        |               | egister Reset h       | as not occurred   | d                |               |

| bit 13-12     | -                                         | ted: Read as '                         |               |                       | . 1.9             |                  |               |

| bit 11        |                                           | ash Voltage Reg<br>Itage regulator i   |               |                       | p bit             |                  |               |

|               |                                           | ltage regulator (                      |               | •                     | ing Sleep         |                  |               |

| bit 10        |                                           | ted: Read as '                         | -             | ,,                    | <b>5 F</b>        |                  |               |

| bit 9         | CM: Configur                              | ation Mismatch                         | Flag bit      |                       |                   |                  |               |

|               | 1 = A Configu                             | uration Mismatc<br>uration Mismatc     | h Reset has   |                       |                   |                  |               |

| bit 8         | VREGS: Volta                              | age Regulator S                        | Standby Durir | ng Sleep bit          |                   |                  |               |

|               | •                                         | egulator is active<br>egulator goes in | •             | •                     | еер               |                  |               |

| bit 7         | EXTR: Extern                              | nal Reset (MCL                         | R) Pin bit    |                       |                   |                  |               |

|               |                                           | Clear (pin) Res<br>Clear (pin) Res     |               |                       |                   |                  |               |

| bit 6         | SWR: Softwa                               | re RESET (Instr                        | uction) Flag  | bit                   |                   |                  |               |

|               |                                           | instruction has instruction has        |               |                       |                   |                  |               |

| bit 5         | SWDTEN: So                                | oftware Enable/                        | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |

|               | 1 = WDT is e<br>0 = WDT is di             |                                        |               |                       |                   |                  |               |

| bit 4         | WDTO: Watc                                | hdog Timer Tim                         | e-out Flag bi | it                    |                   |                  |               |

|               |                                           | e-out has occur<br>e-out has not oc    |               |                       |                   |                  |               |

| Note 1:       | All of the Reset sta<br>cause a device Re |                                        | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir     | onfiguration bit i                     | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

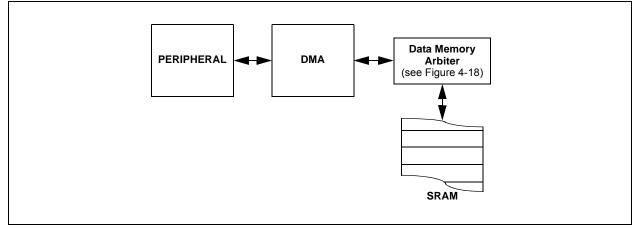

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

### FIGURE 8-1: DMA CONTROLLER MODULE

### 12.1 Timer1 Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

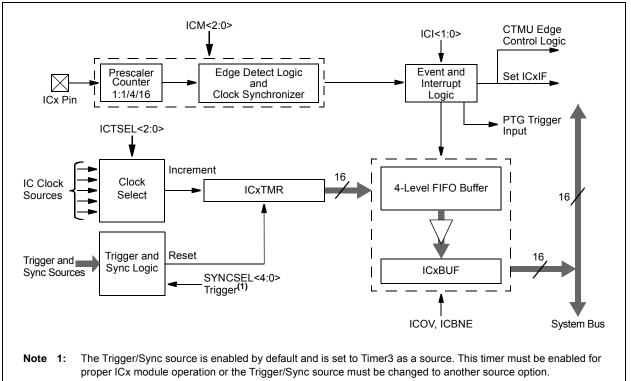

# 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

# 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit HS = Hardware Settable bit |                           |                    |  |

|-------------------|--------------------------------------------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                                       | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set                                       | '0' = Bit is cleared      | x = Bit is unknown |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

#### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

| U-0                   | U-0                                | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

|-----------------------|------------------------------------|------------------------------------|------------------|------------------|------------------|-----------------------|----------|

| _                     | —                                  | PCHEQIRQ                           | PCHEQIEN         | PCLEQIRQ         | PCLEQIEN         | POSOVIRQ              | POSOVIEN |

| bit 15                |                                    |                                    |                  |                  |                  |                       | bit 8    |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| HS, R/C-0             | R/W-0                              | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

| PCIIRQ <sup>(1)</sup> | PCIIEN                             | VELOVIRQ                           | VELOVIEN         | HOMIRQ           | HOMIEN           | IDXIRQ                | IDXIEN   |

| bit 7                 |                                    |                                    |                  |                  |                  |                       | bit 0    |

| r                     |                                    |                                    |                  |                  |                  |                       |          |

| Legend:               |                                    | HS = Hardware                      |                  | C = Clearable    |                  |                       |          |

| R = Readable I        |                                    | W = Writable b                     | bit              | •                | nented bit, rea  |                       |          |

| -n = Value at P       | OR                                 | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr       | iown     |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| bit 15-14             | -                                  | ted: Read as '0                    |                  |                  |                  | .,                    |          |

| bit 13                |                                    | Position Counte                    | er Greater Tha   | n or Equal Cor   | npare Status b   | it                    |          |

|                       |                                    | T ≥ QEI1GEC<br>T < QEI1GEC         |                  |                  |                  |                       |          |

| bit 12                |                                    | Position Counte                    | r Greater Tha    | n or Equal Con   | npare Interrupt  | Enable bit            |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    | s disabled                         |                  |                  |                  |                       |          |

| bit 11                |                                    | Position Counte                    | r Less Than o    | r Equal Compa    | are Status bit   |                       |          |

|                       | 1 = POS1CN                         |                                    |                  |                  |                  |                       |          |

| bit 10                |                                    | Position Counte                    | r Less Than or   | - Equal Compa    | ire Interrunt En | ahla hit              |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 9                 | POSOVIRQ:                          | Position Counte                    | er Overflow Sta  | itus bit         |                  |                       |          |

|                       | 1 = Overflow                       |                                    |                  |                  |                  |                       |          |

|                       |                                    | ow has occurred                    |                  |                  |                  |                       |          |

| bit 8                 |                                    | Position Counte                    | r Overflow Inte  | errupt Enable b  | Dit              |                       |          |

|                       | 1 = Interrupt i<br>0 = Interrupt i |                                    |                  |                  |                  |                       |          |

| bit 7                 | •                                  | tion Counter (H                    | oming) Initializ | ation Process    | Complete Stat    | us bit <sup>(1)</sup> |          |

|                       |                                    | T was reinitialize                 | •                |                  | · · · · · · · ·  |                       |          |

|                       | 0 = POS1CN                         | T was not reiniti                  | alized           |                  |                  |                       |          |

| bit 6                 | PCIIEN: Posi                       | tion Counter (He                   | oming) Initializ | ation Process    | Complete inter   | rupt Enable bit       |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 5                 | 0 = Interrupt i                    |                                    | r Overflow Sta   | tuo hit          |                  |                       |          |

| DIL 5                 | 1 = Overflow                       | Velocity Counter                   | I Overnow Sta    |                  |                  |                       |          |

|                       |                                    | ow has not occu                    | irred            |                  |                  |                       |          |

| bit 4                 | VELOVIEN:                          | /elocity Counter                   | Overflow Inte    | rrupt Enable bi  | it               |                       |          |

|                       | 1 = Interrupt i                    | s enabled                          |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 3                 |                                    | atus Flag for Ho                   |                  | us bit           |                  |                       |          |

|                       |                                    | ent has occurred<br>event has occu |                  |                  |                  |                       |          |

|                       |                                    |                                    |                  |                  |                  |                       |          |

#### REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER

**Note 1:** This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

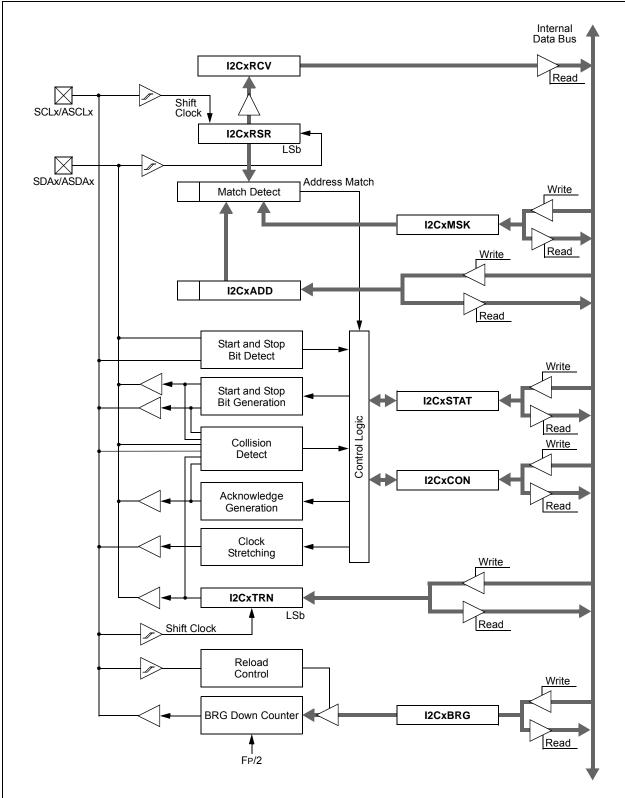

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                             | R/W-0    | R/W-0            | U-0             | R/W-0, HC        | R/W-0                | R-0             | R-1            |  |

|-----------------------------------|----------|------------------|-----------------|------------------|----------------------|-----------------|----------------|--|

| UTXISEL1                          | UTXINV   | UTXISEL0         | —               | UTXBRK           | UTXEN <sup>(1)</sup> | UTXBF           | TRMT           |  |

| bit 15                            |          |                  |                 |                  |                      |                 | bit 8          |  |

|                                   |          |                  |                 |                  |                      |                 |                |  |

| R/W-0                             | R/W-0    | R/W-0            | R-1             | R-0              | R-0                  | R/C-0           | R-0            |  |

| URXISEL1                          | URXISEL0 | ADDEN            | RIDLE           | PERR             | FERR                 | OERR            | URXDA          |  |

| bit 7                             |          |                  |                 |                  |                      |                 | bit C          |  |

|                                   |          |                  |                 |                  |                      |                 |                |  |

| Legend:                           |          | HC = Hardward    | e Clearable bit | C = Clearable    | e bit                |                 |                |  |

| R = Readable bit W = Writable bit |          |                  |                 | U = Unimpler     | mented bit, read     | d as '0'        |                |  |

| -n = Value at                     | POR      | '1' = Bit is set |                 | '0' = Bit is cle | ared                 | x = Bit is unki | Bit is unknown |  |

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

- $\frac{\text{If IREN = 0:}}{1 = \text{UxTX Idle state is '0'}}$

- 0 = UxTX Idle state is '1'

- If IREN = 1:

- 1 = IrDA encoded, UxTX Idle state is '1'

- 0 = IrDA encoded, UxTX Idle state is '0'

- bit 12 Unimplemented: Read as '0'

- bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Sync Break transmission is disabled or completed

- bit 10 UTXEN: UARTx Transmit Enable bit<sup>(1)</sup> 1 = Transmit is enabled, UxTX pin is controlled by UARTx

- 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset; UxTX pin is controlled by the PORT

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 TRMT: Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- **Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0              | R/W-0                                                                                                                                        | U-0              | U-0                  | U-0                                | R/W-0   | U-0                | U-0            |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|------------------------------------|---------|--------------------|----------------|--|--|--|

|                  | CVR2OE <sup>(1)</sup>                                                                                                                        | _                |                      | _                                  | VREFSEL | _                  | _              |  |  |  |

| bit 15           |                                                                                                                                              |                  |                      |                                    |         |                    | bit            |  |  |  |

| <b>D</b> 444 0   | DAALO                                                                                                                                        | DAALO            | <b>D</b> 444.0       | DAMO                               | DAALO   | DANA               | <b>D</b> 444 0 |  |  |  |

| R/W-0            | R/W-0                                                                                                                                        | R/W-0            | R/W-0                | R/W-0                              | R/W-0   | R/W-0              | R/W-0          |  |  |  |

| CVREN            | CVR10E <sup>(1)</sup>                                                                                                                        | CVRR             | CVRSS <sup>(2)</sup> | CVR3                               | CVR2    | CVR1               | CVR0           |  |  |  |

| bit 7            |                                                                                                                                              |                  |                      |                                    |         |                    | bit            |  |  |  |

| Legend:          |                                                                                                                                              |                  |                      |                                    |         |                    |                |  |  |  |

| R = Readable bit |                                                                                                                                              | W = Writable bit |                      | U = Unimplemented bit, read as '0' |         |                    |                |  |  |  |

| -n = Value at F  | POR                                                                                                                                          | '1' = Bit is set |                      | '0' = Bit is cleared               |         | x = Bit is unknown |                |  |  |  |

|                  |                                                                                                                                              |                  |                      |                                    |         |                    |                |  |  |  |

| bit 15           | Unimplemented: Read as '0'                                                                                                                   |                  |                      |                                    |         |                    |                |  |  |  |

| bit 14           | <b>CVR2OE:</b> Comparator Voltage Reference 2 Output Enable bit <sup>(1)</sup>                                                               |                  |                      |                                    |         |                    |                |  |  |  |

|                  | <ol> <li>= (AVDD – AVSS)/2 is connected to the CVREF20 pin</li> <li>= (AVDD – AVSS)/2 is disconnected from the CVREF20 pin</li> </ol>        |                  |                      |                                    |         |                    |                |  |  |  |

| bit 13-11        | Unimplemented: Read as '0'                                                                                                                   |                  |                      |                                    |         |                    |                |  |  |  |

| bit 10           | VREFSEL: Comparator Voltage Reference Select bit                                                                                             |                  |                      |                                    |         |                    |                |  |  |  |

|                  | 1 = CVREFIN = VREF+                                                                                                                          |                  |                      |                                    |         |                    |                |  |  |  |

|                  | 0 = CVREFIN is generated by the resistor network                                                                                             |                  |                      |                                    |         |                    |                |  |  |  |

| bit 9-8          | Unimplement                                                                                                                                  | ted: Read as '   | 0'                   |                                    |         |                    |                |  |  |  |

| bit 7            | CVREN: Comparator Voltage Reference Enable bit                                                                                               |                  |                      |                                    |         |                    |                |  |  |  |

|                  | <ul> <li>1 = Comparator voltage reference circuit is powered on</li> <li>0 = Comparator voltage reference circuit is powered down</li> </ul> |                  |                      |                                    |         |                    |                |  |  |  |

| bit 6            | <b>CVR1OE:</b> Comparator Voltage Reference 1 Output Enable bit <sup>(1)</sup>                                                               |                  |                      |                                    |         |                    |                |  |  |  |

|                  | <ul> <li>1 = Voltage level is output on the CVREF10 pin</li> <li>0 = Voltage level is disconnected from then CVREF10 pin</li> </ul>          |                  |                      |                                    |         |                    |                |  |  |  |

| bit 5            | <b>CVRR:</b> Comparator Voltage Reference Range Selection bit                                                                                |                  |                      |                                    |         |                    |                |  |  |  |

|                  | 1 = CVRsRc/24 step-size<br>0 = CVRsRc/32 step-size                                                                                           |                  |                      |                                    |         |                    |                |  |  |  |

| bit 4            | CVRSS: Comparator Voltage Reference Source Selection bit <sup>(2)</sup>                                                                      |                  |                      |                                    |         |                    |                |  |  |  |

|                  | 1 = Comparator voltage reference source, CVRSRC = (VREF+) – (AVSS)<br>0 = Comparator voltage reference source, CVRSRC = AVDD – AVSS          |                  |                      |                                    |         |                    |                |  |  |  |

| bit 3-0          | <b>CVR&lt;3:0&gt;</b> Comparator Voltage Reference Value Selection $0 \le \text{CVR}<3:0> \le 15$ bits                                       |                  |                      |                                    |         |                    |                |  |  |  |

|                  | When $CVRR = 1$ :<br>$CVREFIN = (CVR<3:0>/24) \bullet (CVRSRC)$                                                                              |                  |                      |                                    |         |                    |                |  |  |  |

|                  | $\frac{\text{When CVRR} = 0}{\text{CVRsRc/4}} + (\text{CVR}<3:0>/32) \bullet (\text{CVRsRc})$                                                |                  |                      |                                    |         |                    |                |  |  |  |

#### REGISTER 25-7: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

- 2: In order to operate with CVRSS = 1, at least one of the comparator modules must be enabled.

#### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

| AC CHARACTERISTICS   |                                          |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |

| 15 MHz               | Table 30-33                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                | _                                        | Table 30-34                                 | —                                                     | 1   | 0,1 | 1   |  |

| 9 MHz                | —                                        | Table 30-35                                 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 30-36                                           | 1   | 0   | 0   |  |

| 11 MHz               | _                                        | —                                           | Table 30-37                                           | 1   | 1   | 0   |  |

| 15 MHz               | —                                        | —                                           | Table 30-38                                           | 0   | 1   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 30-39                                           | 0   | 0   | 0   |  |

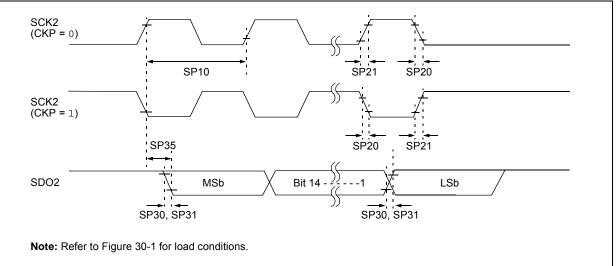

#### TABLE 30-33: SPI2 MAXIMUM DATA/CLOCK RATE SUMMARY

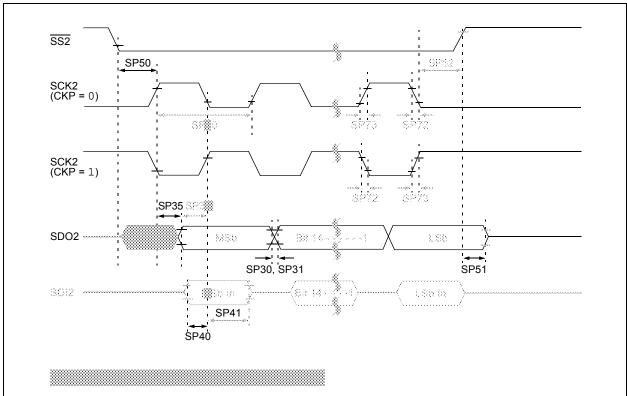

#### FIGURE 30-14: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

#### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Microchip Tradema<br>Architecture —<br>Flash Memory Fam<br>Program Memory S<br>Product Group —<br>Pin Count —<br>Tape and Reel Flag<br>Temperature Range<br>Package<br>Pattern | rk<br>ily<br>iize (Kb<br>(if app                   | oyte)  |                                                                                                                                                                                      | Examples:<br>dsPIC33EP64MC504-I/PT:<br>dsPIC33, Enhanced Performance,<br>64-Kbyte Program Memory,<br>Motor Control, 44-Pin,<br>Industrial Temperature,<br>TQFP package. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture:                                                                                                                                                                  | 33<br>24                                           | =<br>= | 16-bit Digital Signal Controller<br>16-bit Microcontroller                                                                                                                           |                                                                                                                                                                         |

| Flash Memory Family:                                                                                                                                                           | EP                                                 | =      | Enhanced Performance                                                                                                                                                                 |                                                                                                                                                                         |

| Product Group:                                                                                                                                                                 | GP<br>MC                                           | =<br>= | General Purpose family<br>Motor Control family                                                                                                                                       |                                                                                                                                                                         |