Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

|                            | •                                                                                |

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc502-i-ss |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

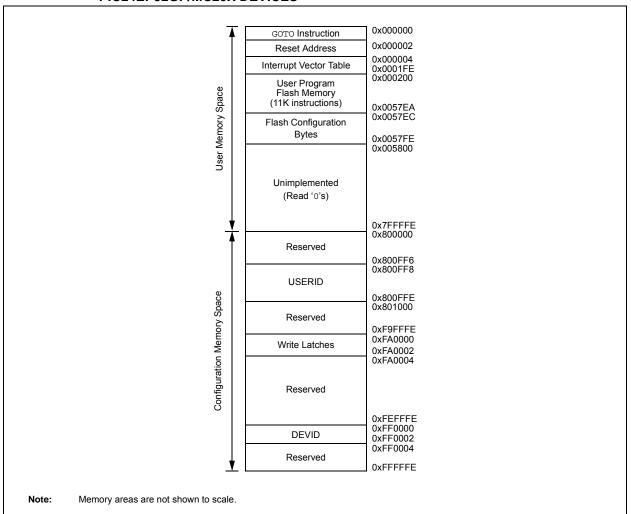

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

## 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in **Section 4.8 "Interfacing Program and Data Memory Spaces**".

User application access to the program memory space is restricted to the lower half of the address range (0x0000000 to 0x7FFFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

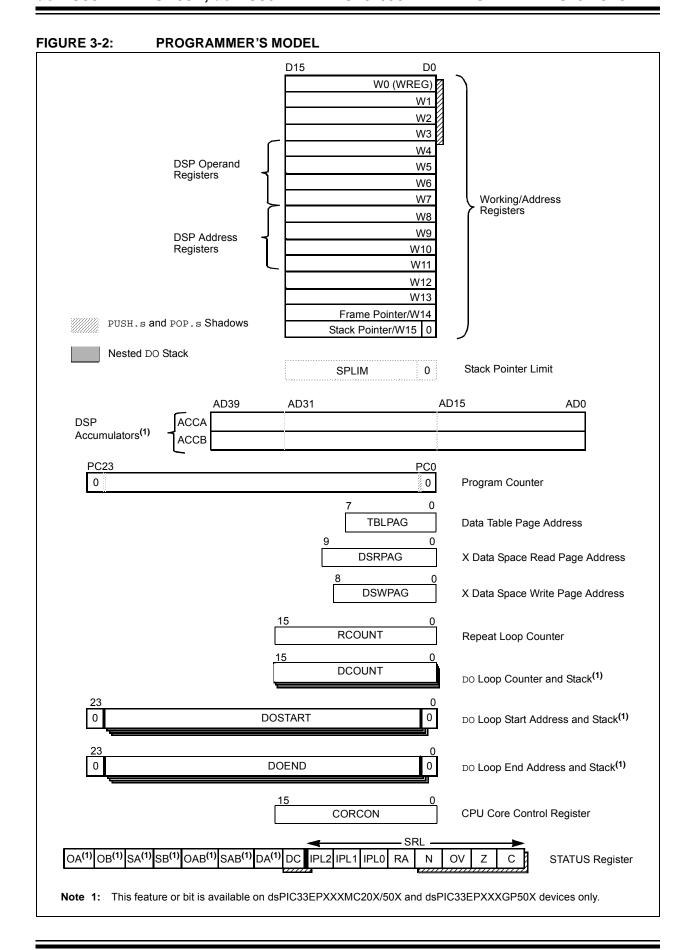

# 4.4 Special Function Register Maps

# TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

| IADLL     | ••    | 0, 0 0           |        |        | · ···· ·    | 011 001    | .000   | 7070701110 | _0/4/00/1 | 7 ti ti b | 0000  | ,,,,,,, | O. 0071  |          |          | •     |       |               |

|-----------|-------|------------------|--------|--------|-------------|------------|--------|------------|-----------|-----------|-------|---------|----------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15           | Bit 14 | Bit 13 | Bit 12      | Bit 11     | Bit 10 | Bit 9      | Bit 8     | Bit 7     | Bit 6 | Bit 5   | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |                  |        |        |             |            |        |            | W0 (WRI   | EG)       |       |         |          |          |          |       |       | xxxx          |

| W1        | 0002  |                  |        |        |             |            |        |            | W1        |           |       |         |          |          |          |       |       | xxxx          |

| W2        | 0004  |                  |        |        |             |            |        |            | W2        |           |       |         |          |          |          |       |       | xxxx          |

| W3        | 0006  |                  |        |        |             |            |        |            | W3        |           |       |         |          |          |          |       |       | xxxx          |

| W4        | 8000  |                  |        |        |             |            |        |            | W4        |           |       |         |          |          |          |       |       | xxxx          |

| W5        | 000A  |                  |        |        |             |            |        |            | W5        |           |       |         |          |          |          |       |       | xxxx          |

| W6        | 000C  |                  |        |        |             |            |        |            | W6        |           |       |         |          |          |          |       |       | xxxx          |

| W7        | 000E  |                  | W7     |        |             |            |        |            |           |           |       |         | xxxx     |          |          |       |       |               |

| W8        | 0010  |                  |        |        |             |            |        |            | W8        |           |       |         |          |          |          |       |       | xxxx          |

| W9        | 0012  |                  |        |        |             |            |        |            | W9        |           |       |         |          |          |          |       |       | xxxx          |

| W10       | 0014  |                  |        |        |             |            |        |            | W10       |           |       |         |          |          |          |       |       | xxxx          |

| W11       | 0016  |                  |        |        |             |            |        |            | W11       |           |       |         |          |          |          |       |       | xxxx          |

| W12       | 0018  |                  |        |        |             |            |        |            | W12       |           |       |         |          |          |          |       |       | xxxx          |

| W13       | 001A  |                  |        |        |             |            |        |            | W13       |           |       |         |          |          |          |       |       | xxxx          |

| W14       | 001C  |                  |        |        |             |            |        |            | W14       |           |       |         |          |          |          |       |       | xxxx          |

| W15       | 001E  |                  |        |        |             |            |        |            | W15       |           |       |         |          |          |          |       |       | xxxx          |

| SPLIM     | 0020  |                  |        |        |             |            |        |            | SPLIN     | 1         |       |         |          |          |          |       |       | 0000          |

| ACCAL     | 0022  |                  |        |        |             |            |        |            | ACCA      | L         |       |         |          |          |          |       |       | 0000          |

| ACCAH     | 0024  |                  |        |        |             |            |        |            | ACCA      | Н         |       |         |          |          |          |       |       | 0000          |

| ACCAU     | 0026  |                  |        | Sig    | gn Extensio | n of ACCA< | 39>    |            |           |           |       |         | AC       | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |                  |        |        |             |            |        |            | ACCB      | L         |       |         |          |          |          |       |       | 0000          |

| ACCBH     | 002A  |                  |        |        |             |            |        |            | ACCBI     | Н         |       |         |          |          |          |       |       | 0000          |

| ACCBU     | 002C  |                  |        | Sig    | gn Extensio | n of ACCB< | 39>    |            |           |           |       |         | AC       | CBU      |          |       |       | 0000          |

| PCL       | 002E  |                  |        |        |             |            |        | Р          | CL<15:0>  |           |       |         |          |          |          |       | _     | 0000          |

| PCH       | 0030  | _                | _      | _      | _           | _          | _      | _          | _         | _         |       |         |          | PCH<6:0> |          |       | •     | 0000          |

| DSRPAG    | 0032  | _                | _      | _      | _           | _          | _      |            |           |           |       | DSRPAC  | G<9:0>   |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _                | _      | _      | _           | _          | _      | _          |           |           |       | DS      | SWPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  | RCOUNT<15:0>     |        |        |             |            |        |            |           | 0000      |       |         |          |          |          |       |       |               |

| DCOUNT    | 0038  | DCOUNT<15:0>     |        |        |             |            |        |            |           | 0000      |       |         |          |          |          |       |       |               |

| DOSTARTL  | 003A  | DOSTARTL<15:1> — |        |        |             |            |        |            |           | 0000      |       |         |          |          |          |       |       |               |

| DOSTARTH  | 003C  | _                | _      | _      | _           | _          | _      | _          | _         | _         | _     |         |          | DOSTAR   | RTH<5:0> |       | •     | 0000          |

| DOENDL    | 003E  | DOENDL<15:1>     |        |        |             |            |        |            |           | 0000      |       |         |          |          |          |       |       |               |

| DOENDH    | 0040  | _                | _      | _      | _           | _          | _      | _          | _         | _         | _     |         |          | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |                  | D 1    |        |             | (a) D      |        |            |           |           |       |         |          |          |          |       |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

bit 3

SLEEP: Wake-up from Sleep Flag bit

1 = Device has been in Sleep mode

0 = Device has not been in Sleep mode

bit 2

IDLE: Wake-up from Idle Flag bit

1 = Device was in Idle mode

0 = Device was not in Idle mode

bit 1

BOR: Brown-out Reset Flag bit

1 = A Brown-out Reset has occurred

0 = A Brown-out Reset has not occurred

bit 0

POR: Power-on Reset Flag bit

1 = A Power-on Reset has occurred

0 = A Power-on Reset has not occurred

**Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

**2:** If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

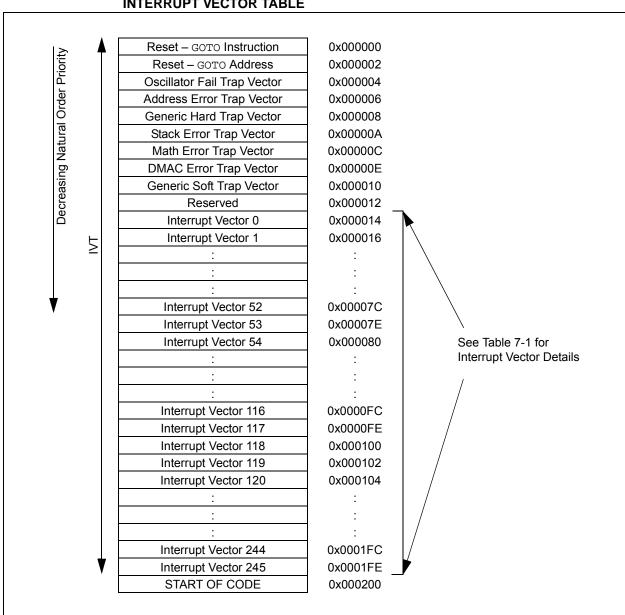

FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-------|-------|-----|-----|-----|-------|

| _     | _   | DAE   | DOOVR | _   | _   | _   | _     |

| bit 7 |     |       |       |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 Unimplemented: Read as '0'

bit 5 DAE: DMA Address Error Soft Trap Status bit

1 = DMA address error soft trap has occurred 0 = DMA address error soft trap has not occurred

bit 4 DOOVR: DO Stack Overflow Soft Trap Status bit

1 = DO stack overflow soft trap has occurred 0 = DO stack overflow soft trap has not occurred

bit 3-0 **Unimplemented:** Read as '0'

## REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   |     | _   | -   | _   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   |     | _   | _   | _   | SGHT  |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-1 **Unimplemented:** Read as '0'

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

## 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | _   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _   | _     |

| bit 15 | _   |        |         |         | _       |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| _     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit HS = Hardware Settable bit |                                    | į –                |  |  |

|-------------------|--------------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                       | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                       | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13 ICSIDL: Input Capture Stop in Idle Control bit

1 = Input capture will Halt in CPU Idle mode

0 = Input capture will continue to operate in CPU Idle mode

bit 12-10 ICTSEL<2:0>: Input Capture Timer Select bits

111 = Peripheral clock (FP) is the clock source of the ICx

110 = Reserved 101 = Reserved

100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)

011 = T5CLK is the clock source of the ICx 010 = T4CLK is the clock source of the ICx

001 = T2CLK is the clock source of the ICx

000 = T3CLK is the clock source of the ICx

bit 9-7 Unimplemented: Read as '0'

bit 6-5 ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture buffer overflow occurred0 = No input capture buffer overflow occurred

bit 3 **ICBNE:** Input Capture Buffer Not Empty Status bit (read-only)

1 = Input capture buffer is not empty, at least one more capture value can be read

0 = Input capture buffer is empty

bit 2-0 ICM<2:0>: Input Capture Mode Select bits

111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)

110 = Unused (module is disabled)

101 = Capture mode, every 16th rising edge (Prescaler Capture mode)

100 = Capture mode, every 4th rising edge (Prescaler Capture mode)

011 = Capture mode, every rising edge (Simple Capture mode)

010 = Capture mode, every falling edge (Simple Capture mode)

001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)

000 = Input capture module is turned off

# REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

- bit 6-4 **INTDIV<2:0>:** Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select)<sup>(3)</sup>

- 111 = 1:128 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

- bit 3 CNTPOL: Position and Index Counter/Timer Direction Select bit

- 1 = Counter direction is negative unless modified by external up/down signal

- 0 = Counter direction is positive unless modified by external up/down signal

- bit 2 GATEN: External Count Gate Enable bit

- 1 = External gate signal controls position counter operation

- 0 = External gate signal does not affect position counter/timer operation

- bit 1-0 **CCM<1:0>:** Counter Control Mode Selection bits

- 11 = Internal Timer mode with optional external count is selected

- 10 = External clock count with optional external count is selected

- 01 = External clock count with external up/down direction is selected

- 00 = Quadrature Encoder Interface (x4 mode) Count mode is selected

- Note 1: When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

## REGISTER 21-5: CxFIFO: ECANx FIFO STATUS REGISTER

| U-0    | U-0 | R-0  | R-0  | R-0  | R-0  | R-0  | R-0   |

|--------|-----|------|------|------|------|------|-------|

| _      | _   | FBP5 | FBP4 | FBP3 | FBP2 | FBP1 | FBP0  |

| bit 15 |     |      |      |      |      |      | bit 8 |

| U-0   | U-0 | R-0   | R-0   | R-0   | R-0   | R-0   | R-0   |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | FNRB5 | FNRB4 | FNRB3 | FNRB2 | FNRB1 | FNRB0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 **FBP<5:0>:** FIFO Buffer Pointer bits

011111 = RB31 buffer 011110 = RB30 buffer

•

•

000001 = TRB1 buffer 000000 = TRB0 buffer

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 FNRB<5:0>: FIFO Next Read Buffer Pointer bits

011111 = RB31 buffer 011110 = RB30 buffer

•

.

000001 = TRB1 buffer 000000 = TRB0 buffer

### 27.6 JTAG Interface

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

Note:

Refer to "**Programming and Diagnostics**" (DS70608) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of the JTAG interface.

## 27.7 In-Circuit Serial Programming

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- · PGEC2 and PGED2

- · PGEC3 and PGED3

## 27.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE™ is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- · PGEC2 and PGED2

- · PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

# 27.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and PIC24EPXXXGP/MC20X devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to "CodeGuard™ Security" (DS70634) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| .,,,               | _L Z0-Z.             |         | COCTION SET OVERVIEW                      | T (GONTINGED)                                 |               |                               |                          |  |  |  |

|--------------------|----------------------|---------|-------------------------------------------|-----------------------------------------------|---------------|-------------------------------|--------------------------|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax                           | Description                                   | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |  |  |  |

| 9                  | BTG                  | BTG     | f,#bit4                                   | Bit Toggle f                                  | 1             | 1                             | None                     |  |  |  |

|                    |                      | BTG     | Ws,#bit4                                  | Bit Toggle Ws                                 | 1             | 1                             | None                     |  |  |  |

| 10                 | BTSC                 | BTSC    | f,#bit4                                   | Bit Test f, Skip if Clear                     | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    |                      | BTSC    | Ws,#bit4                                  | Bit Test Ws, Skip if Clear                    | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

| 11                 | BTSS                 | BTSS    | f,#bit4                                   | Bit Test f, Skip if Set                       | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    |                      | BTSS    | Ws,#bit4                                  | Bit Test Ws, Skip if Set                      | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

| 12                 | BTST                 | BTST    | f,#bit4                                   | Bit Test f                                    | 1             | 1                             | Z                        |  |  |  |

|                    |                      | BTST.C  | Ws,#bit4                                  | Bit Test Ws to C                              | 1             | 1                             | С                        |  |  |  |

|                    |                      | BTST.Z  | Ws,#bit4                                  | Bit Test Ws to Z                              | 1             | 1                             | Z                        |  |  |  |

|                    |                      | BTST.C  | Ws,Wb                                     | Bit Test Ws <wb> to C</wb>                    | 1             | 1                             | С                        |  |  |  |

|                    |                      | BTST.Z  | Ws,Wb                                     | Bit Test Ws <wb> to Z</wb>                    | 1             | 1                             | Z                        |  |  |  |

| 13                 | BTSTS                | BTSTS   | f,#bit4                                   | Bit Test then Set f                           | 1             | 1                             | Z                        |  |  |  |

|                    |                      | BTSTS.C | Ws,#bit4                                  | Bit Test Ws to C, then Set                    | 1             | 1                             | С                        |  |  |  |

|                    |                      | BTSTS.Z | Ws,#bit4                                  | Bit Test Ws to Z, then Set                    | 1             | 1                             | Z                        |  |  |  |

| 14                 | CALL                 | CALL    | lit23                                     | Call subroutine                               | 2             | 4                             | SFA                      |  |  |  |

|                    |                      | CALL    | Wn                                        | Call indirect subroutine                      | 1             | 4                             | SFA                      |  |  |  |

|                    |                      | CALL.L  | Wn                                        | Call indirect subroutine (long address)       | 1             | 4                             | SFA                      |  |  |  |

| 15                 | CLR                  | CLR     | f                                         | f = 0x0000                                    | 1             | 1                             | None                     |  |  |  |

|                    |                      | CLR     | WREG                                      | WREG = 0x0000                                 | 1             | 1                             | None                     |  |  |  |

|                    |                      | CLR     | Ws                                        | Ws = 0x0000                                   | 1             | 1                             | None                     |  |  |  |

|                    |                      | CLR     | Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Clear Accumulator                             | 1             | 1                             | OA,OB,SA,SB              |  |  |  |

| 16                 | CLRWDT               | CLRWDT  |                                           | Clear Watchdog Timer                          | 1             | 1                             | WDTO,Sleep               |  |  |  |

| 17                 | COM                  | COM     | f                                         | f = Ī                                         | 1             | 1                             | N,Z                      |  |  |  |

|                    |                      | COM     | f,WREG                                    | WREG = f                                      | 1             | 1                             | N,Z                      |  |  |  |

|                    |                      | COM     | Ws, Wd                                    | Wd = Ws                                       | 1             | 1                             | N,Z                      |  |  |  |

| 18                 | CP                   | CP      | f                                         | Compare f with WREG                           | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

|                    |                      | CP      | Wb,#lit8                                  | Compare Wb with lit8                          | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

|                    |                      | CP      | Wb,Ws                                     | Compare Wb with Ws (Wb – Ws)                  | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

| 19                 | CP0                  | CP0     | f                                         | Compare f with 0x0000                         | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

|                    |                      | CP0     | Ws                                        | Compare Ws with 0x0000                        | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

| 20                 | CPB                  | CPB     | f                                         | Compare f with WREG, with Borrow              | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

|                    |                      | CPB     | Wb,#lit8                                  | Compare Wb with lit8, with Borrow             | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

|                    |                      | CPB     | Wb,Ws                                     | Compare Wb with Ws, with Borrow (Wb – Ws – C) | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

| 21                 | CPSEQ                | CPSEQ   | Wb,Wn                                     | Compare Wb with Wn, skip if =                 | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    | CPBEQ                | CPBEQ   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if =               | 1             | 1 (5)                         | None                     |  |  |  |

| 22                 | CPSGT                | CPSGT   | Wb,Wn                                     | Compare Wb with Wn, skip if >                 | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    | CPBGT                | CPBGT   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if >               | 1             | 1 (5)                         | None                     |  |  |  |

| 23                 | CPSLT                | CPSLT   | Wb,Wn                                     | Compare Wb with Wn, skip if <                 | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    | CPBLT                | CPBLT   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if <               | 1             | 1 (5)                         | None                     |  |  |  |

| 24                 | CPSNE                | CPSNE   | Wb,Wn                                     | Compare Wb with Wn, skip if ≠                 | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    | CPBNE                | CPBNE   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if ≠               | 1             | 1 (5)                         | None                     |  |  |  |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

<sup>2:</sup> Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

### 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>TM</sup> Object Linker/ MPLIB<sup>TM</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

# 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows®, Linux and Mac OS® X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

#### Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

OSC1

OS20

OS25

OS41

OS41

OS41

OS41

FIGURE 30-2: EXTERNAL CLOCK TIMING

**TABLE 30-17: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHARACTERISTICS |               |                                                                                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$ for Extended |                     |             |            |                               |

|--------------------|---------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|------------|-------------------------------|

| Param<br>No.       | Symb          | Characteristic                                                                     | Min.                                                                                                                                                                                                                                                 | Typ. <sup>(1)</sup> | Max.        | Units      | Conditions                    |

| OS10               | FIN           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                                                                                                                                   | _                   | 60          | MHz        | EC                            |

|                    |               | Oscillator Crystal Frequency                                                       | 3.5<br>10                                                                                                                                                                                                                                            | _                   | 10<br>25    | MHz<br>MHz | XT<br>HS                      |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                      | 8.33                                                                                                                                                                                                                                                 | _                   | DC          | ns         | +125°C                        |

|                    |               | Tosc = 1/Fosc                                                                      | 7.14                                                                                                                                                                                                                                                 | _                   | DC          | ns         | +85°C                         |

| OS25               | TCY           | Instruction Cycle Time <sup>(2)</sup>                                              | 16.67                                                                                                                                                                                                                                                | _                   | DC          | ns         | +125°C                        |

|                    |               | Instruction Cycle Time <sup>(2)</sup>                                              | 14.28                                                                                                                                                                                                                                                | _                   | DC          | ns         | +85°C                         |

| OS30               | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                       | 0.45 x Tosc                                                                                                                                                                                                                                          | _                   | 0.55 x Tosc | ns         | EC                            |

| OS31               | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                      | _                                                                                                                                                                                                                                                    | _                   | 20          | ns         | EC                            |

| OS40               | TckR          | CLKO Rise Time <sup>(3,4)</sup>                                                    | _                                                                                                                                                                                                                                                    | 5.2                 | _           | ns         |                               |

| OS41               | TckF          | CLKO Fall Time <sup>(3,4)</sup>                                                    | _                                                                                                                                                                                                                                                    | 5.2                 | _           | ns         |                               |

| OS42               | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | _                                                                                                                                                                                                                                                    | 12                  | _           | mA/V       | HS, VDD = 3.3V,<br>TA = +25°C |

|                    |               |                                                                                    | _                                                                                                                                                                                                                                                    | 6                   | _           | mA/V       | XT, VDD = 3.3V,<br>TA = +25°C |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 2: Instruction cycle period (TcY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Minimum" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Maximum" cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: This parameter is characterized, but not tested in manufacturing.

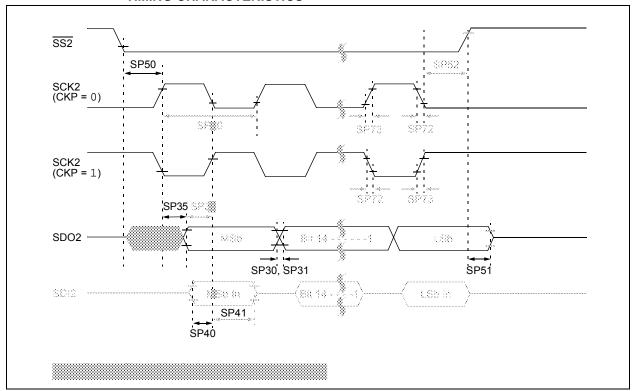

FIGURE 30-21: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

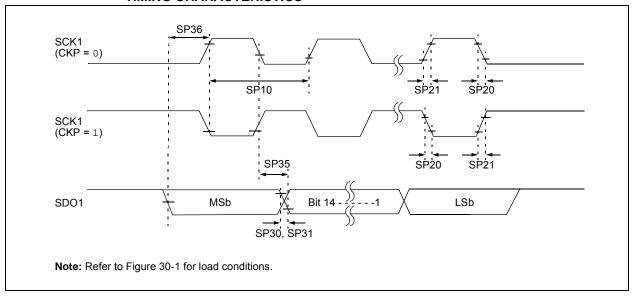

FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                             |  |

|--------------------|-----------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>             | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10               | FscP                  | Maximum SCK1 Frequency                    | _                                                                                                                                                                                                                                                | _                   | 15   | MHz   | (Note 3)                    |  |

| SP20               | TscF                  | SCK1 Output Fall Time                     | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                  | SCK1 Output Rise Time                     | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                | _                                                                                                                                                                                                                                                |                     | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after SCK1 Edge    | _                                                                                                                                                                                                                                                | 6                   | 20   | ns    |                             |  |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO1 Data Output Setup to First SCK1 Edge | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |  |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 3: The minimum clock period for SCK1 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

TABLE 30-53: OP AMP/COMPARATOR SPECIFICATIONS

| DC CHARACTERISTICS |                              |                                                      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> |                     |      |        |                                                    |  |  |

|--------------------|------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------|------|--------|----------------------------------------------------|--|--|

| DC CIT             | ANACILNIC                    | 51103                                                | Operating to                                                                         | emperatur           |      |        | for Industrial<br>C for Extended                   |  |  |

| Param<br>No.       | Symbol                       | Characteristic                                       | Min.                                                                                 | Typ. <sup>(2)</sup> | Max. | Units  | Conditions                                         |  |  |

| Compa              | omparator AC Characteristics |                                                      |                                                                                      |                     |      |        |                                                    |  |  |

| CM10               | TRESP                        | Response Time <sup>(3)</sup>                         | _                                                                                    | 19                  | _    | ns     | V+ input step of 100 mV,<br>V- input held at VDD/2 |  |  |

| CM11               | TMC2OV                       | Comparator Mode<br>Change to Output Valid            | ı                                                                                    | _                   | 10   | μs     |                                                    |  |  |

| Compa              | rator DC Ch                  | naracteristics                                       |                                                                                      |                     |      |        |                                                    |  |  |

| CM30               | VOFFSET                      | Comparator Offset<br>Voltage                         | _                                                                                    | ±10                 | 40   | mV     |                                                    |  |  |

| CM31               | VHYST                        | Input Hysteresis<br>Voltage <sup>(3)</sup>           | _                                                                                    | 30                  | _    | mV     |                                                    |  |  |

| CM32               | TRISE/<br>TFALL              | Comparator Output Rise/<br>Fall Time <sup>(3)</sup>  | ı                                                                                    | 20                  | _    | ns     | 1 pF load capacitance on input                     |  |  |

| CM33               | VGAIN                        | Open-Loop Voltage<br>Gain <sup>(3)</sup>             |                                                                                      | 90                  | _    | db     |                                                    |  |  |

| CM34               | VICM                         | Input Common-Mode Voltage                            | AVss                                                                                 | _                   | AVDD | V      |                                                    |  |  |

| Op Am              | p AC Chara                   | cteristics                                           |                                                                                      |                     |      |        |                                                    |  |  |

| CM20               | SR                           | Slew Rate <sup>(3)</sup>                             | _                                                                                    | 9                   | _    | V/µs   | 10 pF load                                         |  |  |

| CM21a              | Рм                           | Phase Margin<br>(Configuration A) <sup>(3,4)</sup>   | _                                                                                    | 55                  | _    | Degree | G = 100V/V; 10 pF load                             |  |  |

| CM21b              | Рм                           | Phase Margin<br>(Configuration B) <sup>(3,5)</sup>   | _                                                                                    | 40                  | _    | Degree | G = 100V/V; 10 pF load                             |  |  |

| CM22               | Gм                           | Gain Margin <sup>(3)</sup>                           | _                                                                                    | 20                  | _    | db     | G = 100V/V; 10 pF load                             |  |  |

| CM23a              | GBW                          | Gain Bandwidth<br>(Configuration A) <sup>(3,4)</sup> | _                                                                                    | 10                  |      | MHz    | 10 pF load                                         |  |  |

| CM23b              | GBW                          | Gain Bandwidth<br>(Configuration B) <sup>(3,5)</sup> | _                                                                                    | 6                   | _    | MHz    | 10 pF load                                         |  |  |

- Note 1: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** Parameter is characterized but not tested in manufacturing.

- **4:** See Figure 25-6 for configuration information.

- **5:** See Figure 25-7 for configuration information.

- **6:** Resistances can vary by ±10% between op amps.

TABLE 30-59: ADC MODULE SPECIFICATIONS (10-BIT MODE)

| AC CHARACTERISTICS |        |                                               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |          |           |       |                                                                      |

|--------------------|--------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|-------|----------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                | Min.                                                                                                                                                                                                                  | Тур.     | Max.      | Units | Conditions                                                           |

|                    |        | ADC A                                         | ccuracy (                                                                                                                                                                                                             | 10-Bit N | lode)     |       |                                                                      |

| AD20b              | Nr     | Resolution                                    | 10                                                                                                                                                                                                                    | Data B   | its       | bits  |                                                                      |

| AD21b              | INL    | Integral Nonlinearity                         | -0.625                                                                                                                                                                                                                | _        | 0.625     | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                                          |

|                    |        |                                               | -1.5                                                                                                                                                                                                                  |          | 1.5       | LSb   | +85°C < TA ≤ +125°C ( <b>Note 2</b> )                                |

| AD22b              | DNL    | Differential Nonlinearity                     | -0.25                                                                                                                                                                                                                 | -        | 0.25      | LSb   | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ (Note 2) |

|                    |        |                                               | -0.25                                                                                                                                                                                                                 | 1        | 0.25      | LSb   | $+85^{\circ}C < TA \le +125^{\circ}C$ (Note 2)                       |

| AD23b              | GERR   | Gain Error                                    | -2.5                                                                                                                                                                                                                  | _        | 2.5       | LSb   | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ (Note 2) |

|                    |        |                                               | -2.5                                                                                                                                                                                                                  | _        | 2.5       | LSb   | $+85^{\circ}C < TA \le +125^{\circ}C$ (Note 2)                       |

| AD24b              | Eoff   | Offset Error                                  | -1.25                                                                                                                                                                                                                 | _        | 1.25      | LSb   | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ (Note 2) |

|                    |        |                                               | -1.25                                                                                                                                                                                                                 | _        | 1.25      | LSb   | $+85^{\circ}C < TA \le +125^{\circ}C$ (Note 2)                       |

| AD25b              | _      | Monotonicity                                  | _                                                                                                                                                                                                                     | _        |           |       | Guaranteed                                                           |

|                    |        | Dynamic P                                     | erforman                                                                                                                                                                                                              | ce (10-E | Bit Mode) |       |                                                                      |

| AD30b              | THD    | Total Harmonic Distortion <sup>(3)</sup>      | _                                                                                                                                                                                                                     | 64       | _         | dB    |                                                                      |

| AD31b              | SINAD  | Signal to Noise and Distortion <sup>(3)</sup> | _                                                                                                                                                                                                                     | 57       | _         | dB    |                                                                      |

| AD32b              | SFDR   | Spurious Free Dynamic<br>Range <sup>(3)</sup> | _                                                                                                                                                                                                                     | 72       | _         | dB    |                                                                      |

| AD33b              | FNYQ   | Input Signal Bandwidth <sup>(3)</sup>         | _                                                                                                                                                                                                                     | 550      |           | kHz   |                                                                      |

| AD34b              | ENOB   | Effective Number of Bits <sup>(3)</sup>       | _                                                                                                                                                                                                                     | 9.4      | _         | bits  |                                                                      |

Note 1: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

- 3: Parameters are characterized but not tested in manufacturing.

TABLE A-5: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                           | Update Description                                                                                                                                                             |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 30.0 "Electrical                               | Throughout: qualifies all footnotes relating to the operation of analog modules below                                                                                          |

| Characteristics"                                       | VDDMIN (replaces "will have" with "may have")                                                                                                                                  |

|                                                        | Throughout: changes all references of SPI timing parameter symbol "TscP" to "FscP"                                                                                             |

|                                                        | Table 30-1: changes VDD range to 3.0V to 3.6V                                                                                                                                  |

|                                                        | Table 30-4: removes Parameter DC12 (RAM Retention Voltage)                                                                                                                     |

|                                                        | Table 30-7: updates Maximum values at 10 and 20 MIPS                                                                                                                           |

|                                                        | Table 30-8: adds Maximum IPD values, and removes all ΔIWDT entries                                                                                                             |

|                                                        | <ul> <li>Adds new Table 30-9 (Watchdog Timer Delta Current) with consolidated values<br/>removed from Table 30-8. All subsequent tables are renumbered accordingly.</li> </ul> |

|                                                        | <ul> <li>Table 30-10: adds footnote for all parameters for 1:2 Doze ratio</li> <li>Table 30-11:</li> </ul>                                                                     |

|                                                        | - changes Minimum and Maximum values for D120 and D130                                                                                                                         |

|                                                        | - adds Minimum and Maximum values for D131                                                                                                                                     |

|                                                        | <ul> <li>adds Minimum and Maximum values for D150 through D156, and removes</li> <li>Typical values</li> </ul>                                                                 |

|                                                        | • Table 30-12:                                                                                                                                                                 |

|                                                        | - reformats table for readability                                                                                                                                              |

|                                                        | - changes IoL conditions for DO10                                                                                                                                              |

|                                                        | Table 30-14: adds footnote to D135                                                                                                                                             |

|                                                        | Table 30-17: changes Minimum and Maximum values for OS30                                                                                                                       |

|                                                        | • Table 30-19:                                                                                                                                                                 |

|                                                        | - splits temperature range and adds new values for F20a                                                                                                                        |

|                                                        | <ul> <li>reduces temperature range for F20b to extended temperatures only</li> <li>Table 30-20:</li> </ul>                                                                     |

|                                                        | - splits temperature range and adds new values for F21a                                                                                                                        |

|                                                        | reduces temperature range for F20b to extended temperatures only                                                                                                               |

|                                                        | • Table 30-53:                                                                                                                                                                 |

|                                                        | - adds Maximum value to CM30                                                                                                                                                   |

|                                                        | - adds footnote ("Parameter characterized") to multiple parameters                                                                                                             |

|                                                        | Table 30-55: adds Minimum and Maximum values for all CTMUI specifications, and                                                                                                 |

|                                                        | removes Typical values                                                                                                                                                         |

|                                                        | Table 30-57: adds new footnote to AD09  Table 30-50:                                                                                                                           |

|                                                        | • Table 30-58:                                                                                                                                                                 |

|                                                        | <ul> <li>removes all specifications for accuracy with external voltage references</li> <li>removes Typical values for AD23a and AD24a</li> </ul>                               |

|                                                        | - replaces Minimum and Maximum values for AD21a, AD22a, AD23a and AD24a                                                                                                        |

|                                                        | with new values, split by Industrial and Extended temperatures                                                                                                                 |

|                                                        | removes Maximum value of AD30     removes Minimum values from AD31a and AD32a                                                                                                  |

|                                                        |                                                                                                                                                                                |

|                                                        | <ul> <li>adds or changes Typical values for AD30, AD31a, AD32a and AD33a</li> <li>Table 30-59:</li> </ul>                                                                      |

|                                                        | - removes all specifications for accuracy with external voltage references - removes Maximum value of AD30                                                                     |

|                                                        | - removes Typical values for AD23b and AD24b                                                                                                                                   |

|                                                        | - replaces Minimum and Maximum values for AD21b, AD22b, AD23b and AD24b                                                                                                        |

|                                                        | with new values, split by Industrial and Extended temperatures                                                                                                                 |

|                                                        | - removes Minimum and Maximum values from AD31b, AD32b, AD33b and AD34b                                                                                                        |

|                                                        | - adds or changes Typical values for AD30, AD31a, AD32a and AD33a                                                                                                              |

|                                                        | Table 30-61: Adds footnote to AD51                                                                                                                                             |

| Section 32.0 "DC and AC Device Characteristics Graphs" | <ul> <li>Updates Figure 32-6 (Typical IDD @ 3.3V) with individual current vs. processor speed<br/>curves for the different program memory sizes</li> </ul>                     |

| Section 33.0 "Packaging Information"                   | <ul> <li>Replaces drawing C04-149C (64-pin QFN, 7.15 x 7.15 exposed pad) with C04-154A<br/>(64-pin QFN, 5.4 x 5.4 exposed pad)</li> </ul>                                      |