#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

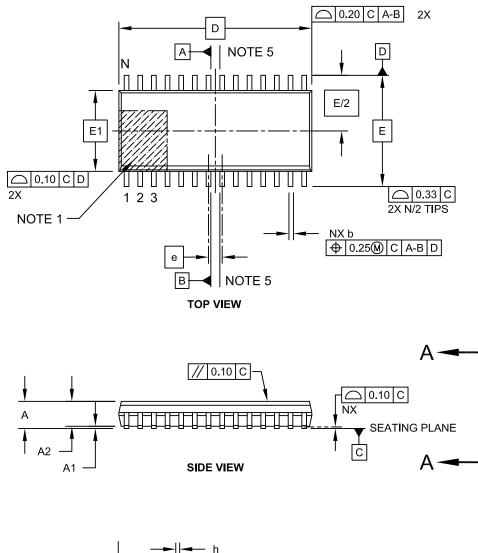

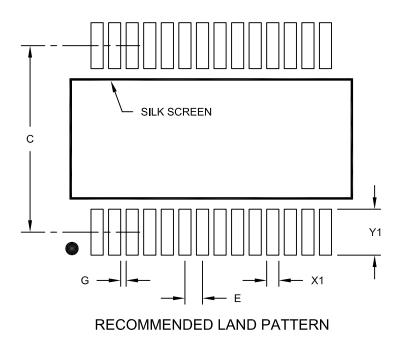

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc504-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-1        | R/W-0         | R/W-0                                                            | U-0           | U-0              | U-0              | U-0             | U-0    |  |

|--------------|---------------|------------------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|--|

| GIE          | DISI          | SWTRAP                                                           |               |                  |                  | _               |        |  |

| bit 15       |               |                                                                  |               |                  |                  |                 | bit 8  |  |

|              |               |                                                                  |               |                  |                  |                 |        |  |

| U-0          | U-0           | U-0                                                              | U-0           | U-0              | R/W-0            | R/W-0           | R/W-0  |  |

|              | —             |                                                                  |               |                  | INT2EP           | INT1EP          | INT0EP |  |

| bit 7        |               |                                                                  |               |                  |                  |                 | bit C  |  |

| Legend:      |               |                                                                  |               |                  |                  |                 |        |  |

| R = Readab   | le bit        | W = Writable                                                     | bit           | U = Unimpler     | mented bit, read | l as '0'        |        |  |

| -n = Value a |               | '1' = Bit is set                                                 |               | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |

|              |               |                                                                  |               |                  |                  |                 |        |  |

| bit 15       | GIE: Global   | Interrupt Enable                                                 | e bit         |                  |                  |                 |        |  |

|              | 1 = Interrupt | s and associate                                                  | d IE bits are | enabled          |                  |                 |        |  |

|              |               | s are disabled, I                                                | •             | still enabled    |                  |                 |        |  |

| bit 14       | DISI: DISI    | nstruction Statu                                                 | s bit         |                  |                  |                 |        |  |

|              |               | struction is active<br>struction is not a                        | -             |                  |                  |                 |        |  |

| bit 13       | SWTRAP: S     | Software Trap St                                                 | atus bit      |                  |                  |                 |        |  |

|              |               | e trap is enabled<br>e trap is disabled                          |               |                  |                  |                 |        |  |

| bit 12-3     | Unimpleme     | nted: Read as '                                                  | 0'            |                  |                  |                 |        |  |

| bit 2        | INT2EP: Ext   | ternal Interrupt 2                                               | 2 Edge Detec  | t Polarity Selec | t bit            |                 |        |  |

|              |               | 1 = Interrupt on negative edge<br>0 = Interrupt on positive edge |               |                  |                  |                 |        |  |

| bit 1        |               |                                                                  |               |                  |                  |                 |        |  |

|              |               | on negative edg                                                  |               |                  |                  |                 |        |  |

| bit 0        | INTOEP: Ext   | ternal Interrupt C                                               | Edge Detec    | t Polarity Selec | t bit            |                 |        |  |

|              |               | on negative edg                                                  |               |                  |                  |                 |        |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

## 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

### REGISTER 11-16: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38 (dsPIC33EPXXXMC20X AND PIC24EPXXXMC20X DEVICES ONLY)

|                                | -         |                                      |       |                      |                   | -                  |                |

|--------------------------------|-----------|--------------------------------------|-------|----------------------|-------------------|--------------------|----------------|

| U-0                            | R/W-0     | R/W-0                                | R/W-0 | R/W-0                | R/W-0             | R/W-0              | R/W-0          |

|                                |           |                                      |       | DTCMP1R<6:           | 0>                |                    |                |

| bit 15                         |           |                                      |       |                      |                   |                    | bit 8          |

|                                |           |                                      |       |                      |                   |                    |                |

| U-0                            | U-0       | U-0                                  | U-0   | U-0                  | U-0               | U-0                | U-0            |

| —                              | —         | —                                    | _     |                      | _                 | —                  | —              |

| bit 7                          |           |                                      |       |                      |                   |                    | bit C          |

|                                |           |                                      |       |                      |                   |                    |                |

| Legend:                        |           |                                      |       |                      |                   |                    |                |

| R = Readal                     | ole bit   | W = Writable                         | bit   | U = Unimpler         | mented bit, read  | d as '0'           |                |

| -n = Value a                   | at POR    | '1' = Bit is set                     |       | '0' = Bit is cleared |                   | x = Bit is unknown |                |

|                                |           |                                      |       |                      |                   |                    |                |

| bit 15                         | Unimpleme | nted: Read as '                      | 0'    |                      |                   |                    |                |

| bit 14-8                       |           | 6:0>: Assign PV<br>1-2 for input pin |       | •                    | on Input 1 to the | e Corresponding    | g RPn Pin bits |

| 1111001 = Input tied to RPI121 |           |                                      |       |                      |                   |                    |                |

|                                | •         |                                      |       |                      |                   |                    |                |

|                                | •         |                                      |       |                      |                   |                    |                |

|                                |           | Input tied to CM                     | P1    |                      |                   |                    |                |

|                                |           | Input tied to Vss                    |       |                      |                   |                    |                |

| bit 7-0                        |           | nted: Read as '                      |       |                      |                   |                    |                |

|                                |           |                                      | -     |                      |                   |                    |                |

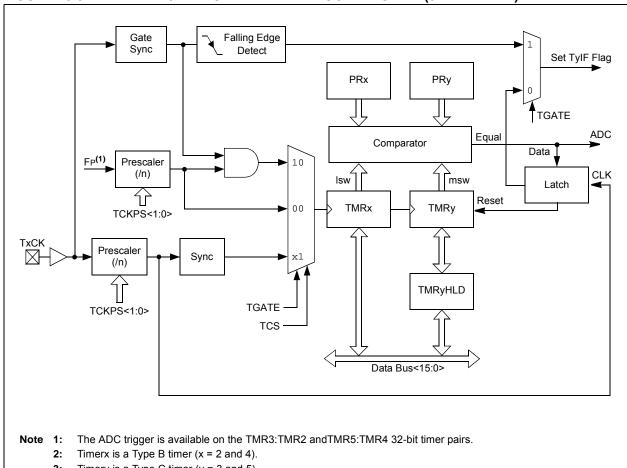

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0              | R/W-0                                                                       | R/W-0                              | R/W-0           | R/W-0             | R/W-0                          | R/W-0                | R/W-0           |  |  |  |  |

|------------------|-----------------------------------------------------------------------------|------------------------------------|-----------------|-------------------|--------------------------------|----------------------|-----------------|--|--|--|--|

| _                | CLSRC4                                                                      | CLSRC3                             | CLSRC2          | CLSRC1            | CLSRC0                         | CLPOL <sup>(2)</sup> | CLMOD           |  |  |  |  |

| bit 15           |                                                                             |                                    | •               |                   |                                |                      | bit 8           |  |  |  |  |

|                  | <b>D</b> 4 4                                                                | D 0.01 4                           | <b>D</b> 444    |                   | DAMA                           | DAMA                 | DAMO            |  |  |  |  |

| R/W-1            | R/W-1                                                                       | R/W-1                              | R/W-1           | R/W-1             | R/W-0<br>FLTPOL <sup>(2)</sup> | R/W-0                | R/W-0           |  |  |  |  |

| FLTSRC4<br>bit 7 | FLTSRC3                                                                     | FLTSRC2                            | FLTSRC1         | FLTSRC0           | FLIPOL-                        | FLTMOD1              | FLTMOD0<br>bit  |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      | DI              |  |  |  |  |

| Legend:          |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

| R = Readable     | bit                                                                         | W = Writable                       | bit             | U = Unimpler      | mented bit, read               | l as '0'             |                 |  |  |  |  |

| -n = Value at I  | POR                                                                         | '1' = Bit is set                   |                 | '0' = Bit is cle  | ared                           | x = Bit is unkr      | nown            |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

| bit 15           | Unimplemen                                                                  | ted: Read as '                     | 0'              |                   |                                |                      |                 |  |  |  |  |

| bit 14-10        | CLSRC<4:0>                                                                  | Current-Limit                      | Control Signa   | al Source Seleo   | ct for PWM Ger                 | nerator # bits       |                 |  |  |  |  |

|                  | 11111 = Fault 32                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 11110 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | •                                                                           |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | •<br>01100 = Reserved                                                       |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 01000 – Reserved<br>01011 = Comparator 4                                    |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             | Amp/Comparat                       | or 3            |                   |                                |                      |                 |  |  |  |  |

|                  | 01001 = Op Amp/Comparator 2                                                 |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 01000 = Op Amp/Comparator 1                                                 |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00111 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00110 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00101 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00100 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00011 = Fault 4                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00010 = Fault 3                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00001 = Fault 2                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00000 <b>= Fau</b>                                                          | ( <i>)</i>                         |                 |                   | ~                              |                      |                 |  |  |  |  |

| bit 9            | <b>CLPOL:</b> Current-Limit Polarity for PWM Generator # bit <sup>(2)</sup> |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 1 = The selected current-limit source is active-low                         |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 0 = The selec                                                               | cted current-lim                   | it source is ac | tive-high         |                                |                      |                 |  |  |  |  |

| bit 8            | CLMOD: Current-Limit Mode Enable for PWM Generator # bit                    |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             | imit mode is er<br>imit mode is di |                 |                   |                                |                      |                 |  |  |  |  |

|                  | ne PWMLOCK                                                                  |                                    |                 | <6>) is a '1', th | e IOCONx regi                  | ster can only be     | e written aftei |  |  |  |  |

| the              | unlock sequen                                                               | ce has been ex                     | ecuted.         |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

# REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

# 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

### 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0          | R/W-x                                                                                  | U-0                           | U-0              | U-0              | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------|-------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| —            | WAKFIL                                                                                 |                               | —                |                  | SEG2PH2          | SEG2PH1         | SEG2PH0 |  |  |  |  |

| bit 15       |                                                                                        |                               |                  |                  |                  |                 | bit     |  |  |  |  |

|              |                                                                                        |                               |                  |                  |                  |                 |         |  |  |  |  |

| R/W-x        | R/W-x                                                                                  | R/W-x                         | R/W-x            | R/W-x            | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

| SEG2PHTS     | S SAM                                                                                  | SEG1PH2                       | SEG1PH1          | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |  |  |  |  |

| bit 7        |                                                                                        |                               |                  |                  |                  |                 | bit     |  |  |  |  |

| Legend:      |                                                                                        |                               |                  |                  |                  |                 |         |  |  |  |  |

| R = Readab   | le bit                                                                                 | W = Writable                  | bit              | U = Unimpler     | nented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value a |                                                                                        | '1' = Bit is set              |                  | '0' = Bit is cle |                  | x = Bit is unkr | nown    |  |  |  |  |

|              |                                                                                        |                               |                  |                  |                  |                 |         |  |  |  |  |

| bit 15       | Unimplemen                                                                             | nted: Read as '               | 0'               |                  |                  |                 |         |  |  |  |  |

| bit 14       | WAKFIL: Sel                                                                            | lect CAN Bus L                | ine Filter for V | Vake-up bit      |                  |                 |         |  |  |  |  |

|              |                                                                                        | N bus line filter             |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                                        | line filter is not            |                  | e-up             |                  |                 |         |  |  |  |  |

| bit 13-11    | -                                                                                      | nted: Read as '               |                  |                  |                  |                 |         |  |  |  |  |

| bit 10-8     | SEG2PH<2:0>: Phase Segment 2 bits                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 111 = Length is 8 x To                                                                 |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 000 = Lenath                                                                           | n is 1 x To                   |                  |                  |                  |                 |         |  |  |  |  |

| bit 7        | 000 = Length is 1 x TQ<br>SEG2PHTS: Phase Segment 2 Time Select bit                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 1 = Freely programmable                                                                |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 0 = Maximum of SEG1PHx bits or Information Processing Time (IPT), whichever is greater |                               |                  |                  |                  |                 |         |  |  |  |  |

| bit 6        | SAM: Sample of the CAN Bus Line bit                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                                        | s sampled threes sampled once |                  |                  |                  |                 |         |  |  |  |  |

| bit 5-3      | SEG1PH<2:0>: Phase Segment 1 bits                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 111 = Length is 8 x To                                                                 |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 000 = Length                                                                           |                               |                  |                  |                  |                 |         |  |  |  |  |

| bit 2-0      |                                                                                        | >: Propagation                | Time Segmen      | t bits           |                  |                 |         |  |  |  |  |

|              | 111 = Length                                                                           | 111 = Length is 8 x TQ        |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                                        |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

### REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

#### 22.2 **CTMU Control Registers**

| REGISTER                                                                                                                                                     | 22-1: CTM                         | UCON1: CTM       | J CONTROI | - REGISTER                          | 1                |                        |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|-----------|-------------------------------------|------------------|------------------------|--------|

| R/W-0                                                                                                                                                        | U-0                               | R/W-0            | R/W-0     | R/W-0                               | R/W-0            | R/W-0                  | R/W-0  |

| CTMUEN                                                                                                                                                       | _                                 | CTMUSIDL         | TGEN      | EDGEN                               | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |

| bit 15                                                                                                                                                       |                                   |                  |           |                                     |                  |                        | bit 8  |

|                                                                                                                                                              |                                   |                  |           |                                     |                  |                        |        |

| U-0                                                                                                                                                          | U-0                               | U-0              | U-0       | U-0                                 | U-0              | U-0                    | U-0    |

|                                                                                                                                                              | _                                 |                  | _         | <u> </u>                            | <u> </u>         |                        | _      |

| bit 7                                                                                                                                                        |                                   |                  |           |                                     |                  |                        | bit 0  |

|                                                                                                                                                              |                                   |                  |           |                                     |                  |                        |        |

| Legend:                                                                                                                                                      |                                   |                  |           |                                     |                  |                        |        |

| R = Readable                                                                                                                                                 | e bit                             | W = Writable b   | bit       | U = Unimplen                        | nented bit, read | as '0'                 |        |

| -n = Value at                                                                                                                                                | POR                               | '1' = Bit is set |           | '0' = Bit is cleared x = Bit is unk |                  |                        | own    |

| bit 15 CTMUEN: CTMU Enable bit<br>1 = Module is enabled<br>0 = Module is disabled                                                                            |                                   |                  |           |                                     |                  |                        |        |

| bit 14                                                                                                                                                       | bit 14 Unimplemented: Read as '0' |                  |           |                                     |                  |                        |        |

| bit 13 CTMUSIDL: CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |                                   |                  |           |                                     |                  |                        |        |

| bit 12                                                                                                                                                       | TGEN: Time Generation Enable bit  |                  |           |                                     |                  |                        |        |

#### DECISTED

| bit 9 | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                               |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|       | <ul><li>1 = Analog current source output is grounded</li><li>0 = Analog current source output is not grounded</li></ul> |  |  |  |  |

| bit 8 | CTTRIG: ADC Trigger Control bit                                                                                         |  |  |  |  |

|       | <ul><li>1 = CTMU triggers ADC start of conversion</li><li>0 = CTMU does not trigger ADC start of conversion</li></ul>   |  |  |  |  |

EDGSEQEN: Edge Sequence Enable bit

0 = No edge sequence is needed

1 = Enables edge delay generation 0 = Disables edge delay generation

EDGEN: Edge Enable bit

bit 7-0 Unimplemented: Read as '0'

bit 11

bit 10

Note 1: The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.) 0 = Software is used to trigger edges (manual set of EDGxSTAT)

1 = Edge 1 event must occur before Edge 2 event can occur

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                    | Description                        | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |  |

|--------------------|----------------------|-----------------|--------------------|------------------------------------|---------------|-------------------------------|--------------------------|--|

| 72 SL              |                      | SL f            |                    | f = Left Shift f                   | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | SL              | f,WREG             | WREG = Left Shift f                | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | SL              | Ws,Wd              | Wd = Left Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | SL              | Wb,Wns,Wnd         | Wnd = Left Shift Wb by Wns         | 1             | 1                             | N,Z                      |  |

|                    |                      | SL              | Wb,#lit5,Wnd       | Wnd = Left Shift Wb by lit5        | 1             | 1                             | N,Z                      |  |

| 73                 | SUB                  | SUB             | <sub>ACC</sub> (1) | Subtract Accumulators              | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

|                    |                      | SUB             | £                  | f = f – WREG                       | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUB             | f,WREG             | WREG = f – WREG                    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUB             | #lit10,Wn          | Wn = Wn - lit10                    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUB             | Wb,Ws,Wd           | Wd = Wb – Ws                       | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUB             | Wb,#lit5,Wd        | Wd = Wb – lit5                     | 1             | 1                             | C,DC,N,OV,Z              |  |

| 74                 | SUBB                 | SUBB            | f                  | $f = f - WREG - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBB            | f,WREG             | WREG = $f - WREG - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBB            | #lit10,Wn          | Wn = Wn – lit10 – $(\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBB            | Wb,Ws,Wd           | $Wd = Wb - Ws - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBB            | Wb,#lit5,Wd        | $Wd = Wb - lit5 - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |  |

| 75                 | SUBR                 | SUBR            | f                  | f = WREG – f                       | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBR            | f,WREG             | WREG = WREG – f                    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBR            | Wb,Ws,Wd           | Wd = Ws – Wb                       | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBR            | Wb,#lit5,Wd        | Wd = lit5 – Wb                     | 1             | 1                             | C,DC,N,OV,Z              |  |

| 76                 | SUBBR                | SUBBR           | f                  | $f = WREG - f - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBBR           | f,WREG             | WREG = WREG – f – $(\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBBR           | Wb,Ws,Wd           | $Wd = Ws - Wb - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBBR           | Wb,#lit5,Wd        | $Wd = lit5 - Wb - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |  |

| 77                 | SWAP                 | SWAP.b          | Wn                 | Wn = nibble swap Wn                | 1             | 1                             | None                     |  |

|                    |                      | SWAP            | Wn                 | Wn = byte swap Wn                  | 1             | 1                             | None                     |  |

| 78                 | TBLRDH               | TBLRDH          | Ws,Wd              | Read Prog<23:16> to Wd<7:0>        | 1             | 5                             | None                     |  |

| 79                 | TBLRDL               | TBLRDL          | Ws,Wd              | Read Prog<15:0> to Wd              | 1             | 5                             | None                     |  |

| 80                 | TBLWTH               | TBLWTH          | Ws,Wd              | Write Ws<7:0> to Prog<23:16>       | 1             | 2                             | None                     |  |

| 81                 | TBLWTL               | TBLWTL          | Ws,Wd              | Write Ws to Prog<15:0>             | 1             | 2                             | None                     |  |

| 82                 | ULNK                 | ULNK            |                    | Unlink Frame Pointer               | 1             | 1                             | SFA                      |  |

| 83                 | XOR                  | XOR             | f                  | f = f .XOR. WREG                   | 1             | 1                             | N,Z                      |  |

|                    |                      | XOR             | f,WREG             | WREG = f .XOR. WREG                | 1             | 1                             | N,Z                      |  |

|                    |                      | XOR             | #lit10,Wn          | Wd = lit10 .XOR. Wd                | 1             | 1                             | N,Z                      |  |

|                    |                      | XOR             | Wb,Ws,Wd           | Wd = Wb .XOR. Ws                   | 1             | 1                             | N,Z                      |  |

|                    |                      | XOR             | Wb,#lit5,Wd        | Wd = Wb .XOR. lit5                 | 1             | 1                             | N,Z                      |  |

| 84                 | ZE                   | ZE              | Ws,Wnd             | Wnd = Zero-extend Ws               | 1             | 1                             | C,Z,N                    |  |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACTERISTICS |                       |                                                     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |       |                                                                |  |

|--------------------|-----------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol Characteristic |                                                     |                                                                                                                                                                                                      | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                     |  |

|                    |                       | Program Flash Memory                                |                                                                                                                                                                                                      |                     |      |       |                                                                |  |

| D130               | Eр                    | Cell Endurance                                      | 10,000                                                                                                                                                                                               | —                   | _    | E/W   | -40°C to +125°C                                                |  |

| D131               | Vpr                   | VDD for Read                                        | 3.0                                                                                                                                                                                                  | —                   | 3.6  | V     |                                                                |  |

| D132b              | VPEW                  | VDD for Self-Timed Write                            | 3.0                                                                                                                                                                                                  | —                   | 3.6  | V     |                                                                |  |

| D134               | TRETD                 | Characteristic Retention                            | 20                                                                                                                                                                                                   | _                   |      | Year  | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP                  | Supply Current during<br>Programming <sup>(2)</sup> | —                                                                                                                                                                                                    | 10                  |      | mA    |                                                                |  |

| D136               | IPEAK                 | Instantaneous Peak Current<br>During Start-up       | —                                                                                                                                                                                                    | —                   | 150  | mA    |                                                                |  |

| D137a              | TPE                   | Page Erase Time                                     | 17.7                                                                                                                                                                                                 | —                   | 22.9 | ms    | TPE = 146893 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>     |  |

| D137b              | Тре                   | Page Erase Time                                     | 17.5                                                                                                                                                                                                 | —                   | 23.1 | ms    | TPE = 146893 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>    |  |

| D138a              | Tww                   | Word Write Cycle Time                               | 41.7                                                                                                                                                                                                 | —                   | 53.8 | μs    | Tww = 346 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>        |  |

| D138b              | Tww                   | Word Write Cycle Time                               | 41.2                                                                                                                                                                                                 | —                   | 54.4 | μs    | Tww = 346 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>       |  |

### TABLE 30-14: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

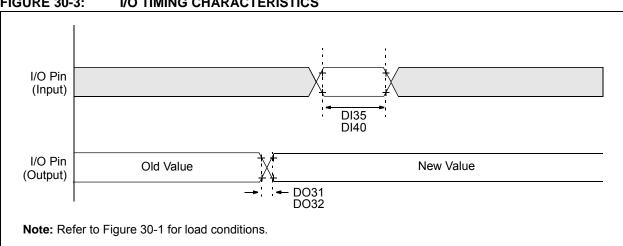

#### **FIGURE 30-3: I/O TIMING CHARACTERISTICS**

### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |    |     |            |

|--------------------|--------|-----------------------------------|-------------------------------------------------------|---|----|-----|------------|

| Param<br>No.       | Symbol | Characteristic                    | Min. Typ. <sup>(1)</sup> Max. Units Conditions        |   |    |     | Conditions |

| DO31               | TioR   | Port Output Rise Time             |                                                       | 5 | 10 | ns  |            |

| DO32               | TIOF   | Port Output Fall Time             | _                                                     | 5 | 10 | ns  |            |

| DI35               | TINP   | INTx Pin High or Low Time (input) | 20                                                    | — | _  | ns  |            |

| DI40               | Trbp   | CNx High or Low Time (input)      | 2                                                     | _ | _  | Тсү |            |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

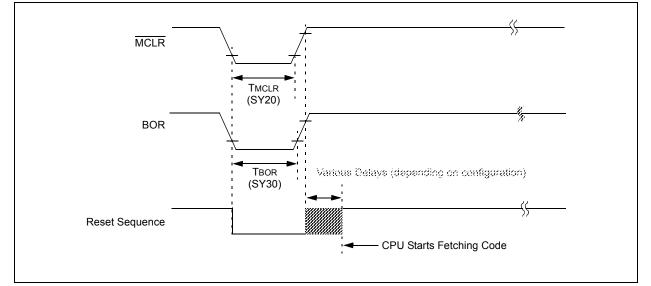

#### FIGURE 30-4: BOR AND MASTER CLEAR RESET TIMING CHARACTERISTICS

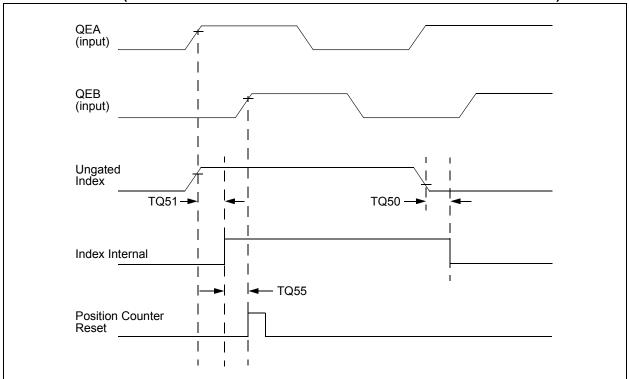

### FIGURE 30-13: QEI MODULE INDEX PULSE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

### TABLE 30-32: QEI INDEX PULSE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |    |                                                         |  |

|--------------------|--------|---------------------------------------------------------------------|-------------------------------------------------------|---|----|---------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                       | Min. Max. Units Conditions                            |   |    |                                                         |  |

| TQ50               | TqiL   | Filter Time to Recognize Low,<br>with Digital Filter                | 3 * N * Tcy                                           | _ | ns | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |  |

| TQ51               | TqiH   | Filter Time to Recognize High,<br>with Digital Filter               | 3 * N * Tcy                                           | _ | ns | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |  |

| TQ55               | Tqidxr | Index Pulse Recognized to Position<br>Counter Reset (ungated index) | 3 TCY                                                 | — | ns |                                                         |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Alignment of index pulses to QEA and QEB is shown for position counter Reset timing only. Shown for forward direction only (QEA leads QEB). Same timing applies for reverse direction (QEA lags QEB) but index pulse recognition occurs on the falling edge.

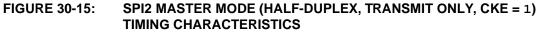

### TABLE 30-34: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS                          |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |

|---------------------------------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param. Symbol Characteristic <sup>(1)</sup> |                       |                                              | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP10                                        | FscP                  | Maximum SCK2 Frequency                       | _                                                                                                                                                                                                                                                                                       | _                   | 15   | MHz   | (Note 3)                       |

| SP20                                        | TscF                  | SCK2 Output Fall Time                        | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP21                                        | TscR                  | SCK2 Output Rise Time                        | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31<br>(Note 4) |

| SP30                                        | TdoF                  | SDO2 Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP31                                        | TdoR                  | SDO2 Data Output Rise Time                   | -                                                                                                                                                                                                                                                                                       | _                   |      | ns    | See Parameter DO31<br>(Note 4) |

| SP35                                        | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge    | —                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                                |

| SP36                                        | TdiV2scH,<br>TdiV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

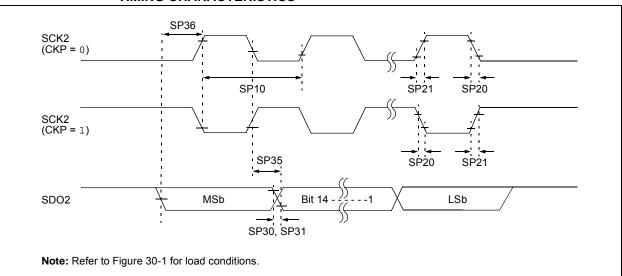

### FIGURE 30-17: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-36:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |  |

|--------------------|-----------------------|-----------------------------------------------|------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                 | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10               | FscP                  | Maximum SCK2 Frequency                        |                                                      | —                   | 9    | MHz   | -40°C to +125°C<br>(Note 3) |  |

| SP20               | TscF                  | SCK2 Output Fall Time                         | _                                                    | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                  | SCK2 Output Rise Time                         | _                                                    | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                    | _                                                    | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                    | _                                                    | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge        | _                                                    | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge  | 30                                                   | —                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge | 30                                                   | —                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge     | 30                                                   | —                   |      | ns    |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

# 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |