Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc504-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name <sup>(4)</sup>                   | Pin<br>Type | Buffer<br>Type | PPS | Description                                                    |

|-------------------------------------------|-------------|----------------|-----|----------------------------------------------------------------|

| U2CTS                                     | - 1         | ST             | No  | UART2 Clear-To-Send.                                           |

| U2RTS                                     | 0           | _              | No  | UART2 Ready-To-Send.                                           |

| U2RX                                      | - 1         | ST             | Yes | UART2 receive.                                                 |

| U2TX                                      | 0           | _              | Yes | UART2 transmit.                                                |

| BCLK2                                     | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                     |

| SCK1                                      | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                |

| SDI1                                      | I           | ST             | No  | SPI1 data in.                                                  |

| SDO1                                      | 0           | _              | No  | SPI1 data out.                                                 |

| SS1                                       | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                 |

| SCK2                                      | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                |

| SDI2                                      | I           | ST             | Yes | SPI2 data in.                                                  |

| SDO2                                      | 0           | _              | Yes | SPI2 data out.                                                 |

| SS2                                       | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.                 |

| SCL1                                      | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                |

| SDA1                                      | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                 |

| ASCL1                                     | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.      |

| ASDA1                                     | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.       |

| SCL2                                      | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                |

| SDA2                                      | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                 |

| ASCL2                                     | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.      |

| ASDA2                                     | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.       |

| TMS <sup>(5)</sup>                        | - 1         | ST             | No  | JTAG Test mode select pin.                                     |

| TCK                                       | I           | ST             | No  | JTAG test clock input pin.                                     |

| TDI                                       | I           | ST             | No  | JTAG test data input pin.                                      |

| TDO                                       | 0           | _              | No  | JTAG test data output pin.                                     |

| C1RX <sup>(2)</sup>                       | - 1         | ST             | Yes | ECAN1 bus receive pin.                                         |

| C1TX <sup>(2)</sup>                       | 0           | _              | Yes | ECAN1 bus transmit pin.                                        |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup> | - 1         | ST             | Yes | PWM Fault Inputs 1 and 2.                                      |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup> | - 1         | ST             | No  | PWM Fault Inputs 3 and 4.                                      |

| FLT32 <sup>(1,3)</sup>                    | - 1         | ST             | No  | PWM Fault Input 32 (Class B Fault).                            |

| DTCMP1-DTCMP3 <sup>(1)</sup>              | - 1         | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                 |

| PWM1L-PWM3L <sup>(1)</sup>                | 0           | _              | No  | PWM Low Outputs 1 through 3.                                   |

| PWM1H-PWM3H <sup>(1)</sup>                | 0           | _              | No  | PWM High Outputs 1 through 3.                                  |

| SYNCI1 <sup>(1)</sup>                     | - 1         | ST             | Yes | PWM Synchronization Input 1.                                   |

| SYNCO1 <sup>(1)</sup>                     | 0           | _              | Yes | PWM Synchronization Output 1.                                  |

| INDX1 <sup>(1)</sup>                      | I           | ST             | Yes | Quadrature Encoder Index1 pulse input.                         |

| HOME1 <sup>(1)</sup>                      | - 1         | ST             | Yes | Quadrature Encoder Home1 pulse input.                          |

| QEA1 <sup>(1)</sup>                       | - 1         | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer |

| (4)                                       |             |                |     | external clock/gate input in Timer mode.                       |

| QEB1 <sup>(1)</sup>                       | I           | ST             | Yes | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer |

| ONTO 45 (1)                               |             |                | .,  | external clock/gate input in Timer mode.                       |

| CNTCMP1 <sup>(1)</sup>                    | 0           | _              | Yes | Quadrature Encoder Compare Output 1.                           |

Legend:CMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levels<br/>PPS = Peripheral Pin SelectAnalog = Analog input<br/>O = Output<br/>TTL = TTL input bufferP = Power<br/>I = Input

- Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

- 3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

- 4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

- 5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup>

111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled

110 = CPU Interrupt Priority Level is 6 (14)

101 = CPU Interrupt Priority Level is 5 (13)

100 = CPU Interrupt Priority Level is 4 (12)

011 = CPU Interrupt Priority Level is 3 (11)

010 = CPU Interrupt Priority Level is 2 (10)

001 = CPU Interrupt Priority Level is 1 (9)

000 = CPU Interrupt Priority Level is 0 (8)

bit 4 RA: REPEAT Loop Active bit

1 = REPEAT loop in progress

0 = REPEAT loop not in progress

bit 3 N: MCU ALU Negative bit

1 = Result was negative

0 = Result was non-negative (zero or positive)

bit 2 OV: MCU ALU Overflow bit

This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.

1 = Overflow occurred for signed arithmetic (in this arithmetic operation)

0 = No overflow occurred

bit 1 Z: MCU ALU Zero bit

1 = An operation that affects the Z bit has set it at some time in the past

0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)

bit 0 C: MCU ALU Carry/Borrow bit

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

TABLE 4-11: PTG REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                              | Bit 13  | Bit 12  | Bit 11  | Bit 10    | Bit 9   | Bit 8    | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3               | Bit 2    | Bit 1    | Bit 0  | AII<br>Resets |

|-----------|-------|--------|-------------------------------------|---------|---------|---------|-----------|---------|----------|---------|--------|-------|-------|---------------------|----------|----------|--------|---------------|

| PTGCST    | 0AC0  | PTGEN  | _                                   | PTGSIDL | PTGTOGL | _       | PTGSWT    | PTGSSEN | PTGIVIS  | PTGSTRT | PTGWTO | _     | _     | _                   | _        | PTGITI   | M<1:0> | 0000          |

| PTGCON    | 0AC2  | Р      | TGCLK<2                             | :0>     |         | P       | TGDIV<4:0 | >       |          |         | PTGPWD | <3:0> |       | _                   | P        | TGWDT<2: | 0>     | 0000          |

| PTGBTE    | 0AC4  |        | ADCTS<4:1> IC4TSS IC3TSS IC2TSS IC1 |         |         |         |           |         |          |         | OC3CS  | OC2CS | OC1CS | OC4TSS              | OC3TSS   | OC2TSS   | OC1TSS | 0000          |

| PTGHOLD   | 0AC6  |        |                                     |         |         |         |           |         | PTGHOLD  | <15:0>  |        |       |       |                     |          |          |        | 0000          |

| PTGT0LIM  | 0AC8  |        |                                     |         |         |         |           |         | PTGT0LIM | <15:0>  |        |       |       |                     |          |          |        | 0000          |

| PTGT1LIM  | 0ACA  |        |                                     |         |         |         |           |         | PTGT1LIM | <15:0>  |        |       |       |                     |          |          |        | 0000          |

| PTGSDLIM  | 0ACC  |        |                                     |         |         |         |           |         | PTGSDLIM | 1<15:0> |        |       |       |                     |          |          |        | 0000          |

| PTGC0LIM  | 0ACE  |        |                                     |         |         |         |           |         | PTGC0LIN | l<15:0> |        |       |       |                     |          |          |        | 0000          |

| PTGC1LIM  | 0AD0  |        |                                     |         |         |         |           |         | PTGC1LIN | l<15:0> |        |       |       |                     |          |          |        | 0000          |

| PTGADJ    | 0AD2  |        |                                     |         |         |         |           |         | PTGADJ<  | :15:0>  |        |       |       |                     |          |          |        | 0000          |

| PTGL0     | 0AD4  |        |                                     |         |         |         |           |         | PTGL0<   | 15:0>   |        |       |       |                     |          |          |        | 0000          |

| PTGQPTR   | 0AD6  | _      | _                                   | _       | _       | _       | _         | _       | _        | _       | _      | _     |       | P                   | TGQPTR<4 | 1:0>     |        | 0000          |

| PTGQUE0   | 0AD8  |        |                                     |         | STEP    | 1<7:0>  |           |         |          |         |        |       | STEP  | )<7:0>              |          |          |        | 0000          |

| PTGQUE1   | 0ADA  |        |                                     |         | STEP    | 3<7:0>  |           |         |          |         |        |       | STEP2 | 2<7:0>              |          |          |        | 0000          |

| PTGQUE2   | 0ADC  |        |                                     |         | STEP    | 5<7:0>  |           |         |          |         |        |       | STEP4 | <b>4&lt;7:0&gt;</b> |          |          |        | 0000          |

| PTGQUE3   | 0ADE  |        |                                     |         | STEP    | 7<7:0>  |           |         |          |         |        |       | STEP  | 6<7:0>              |          |          |        | 0000          |

| PTGQUE4   | 0AE0  |        | STEP9<7:0>                          |         |         |         |           |         |          |         |        |       | STEP8 | 3<7:0>              |          |          |        | 0000          |

| PTGQUE5   | 0AE2  |        |                                     |         | STEP    | 11<7:0> |           |         |          |         |        |       | STEP1 | 0<7:0>              |          |          |        | 0000          |

| PTGQUE6   | 0AE4  |        |                                     |         | STEP    | 13<7:0> |           |         |          |         |        |       | STEP1 | 2<7:0>              |          |          |        | 0000          |

| PTGQUE7   | 0AE6  |        | STEP15<7:0> STEP14<7:0> 000         |         |         |         |           |         |          |         |        | 0000  |       |                     |          |          |        |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | 1      | _      | 1      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | -     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  | 1      | -      | _      | _      | _      | RA10    | RA9    | RA8    | RA7    | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | 1      | -      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | 1      | -      | _      | _      | _      | ODCA10  | ODCA9  | ODCA8  | ODCA7  | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | 1      | -      | _      | _      | _      | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | 1      | -      | _      | _      | _      | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | 1      | -      | _      | _      | _      | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | -      | 1      | _      | ı      | 1      | _       | _      | _      | _      | ı     | -     | ANSA4  | -      | _      | ANSA1  | ANSA0  | 0013          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | _      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | -      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | -      | _      |        | _      |        | 1      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | -      | _      |        | _      |        | 1      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | _      | _      | ı      |        | ı      | -      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | -      | _      |        | _      |        | 1      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | -      | _      | -      | -      | -      | _      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | -      | _      | -      | _      | _      | _      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

W = Writable bit

| R/W-0  | R/W-0                 | R/W-0                 | R/W-0                  | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

|--------|-----------------------|-----------------------|------------------------|------------------------|----------------------|----------------------|----------------------|

| NSTDIS | OVAERR <sup>(1)</sup> | OVBERR <sup>(1)</sup> | COVAERR <sup>(1)</sup> | COVBERR <sup>(1)</sup> | OVATE <sup>(1)</sup> | OVBTE <sup>(1)</sup> | COVTE <sup>(1)</sup> |

| bit 15 | •                     |                       |                        |                        |                      |                      | bit 8                |

| R/W-0                   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|-------------------------|---------|---------|---------|---------|--------|---------|-------|

| SFTACERR <sup>(1)</sup> | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL | _     |

| bit 7                   |         |         |         |         |        |         | bit 0 |

U = Unimplemented bit, read as '0'

x = Bit is unknown

| -n = Value at Po | OR '1' = Bit is set                                                                                                     | '0' = Bit is cleared                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| bit 15           | <b>NSTDIS:</b> Interrupt Nesting Disable bit 1 = Interrupt nesting is disabled                                          |                                          |

|                  | 0 = Interrupt nesting is enabled                                                                                        |                                          |

| bit 14           | <b>OVAERR:</b> Accumulator A Overflow Trap                                                                              | · · · · · · · · · · · · · · · · · · ·    |

|                  | <ul><li>1 = Trap was caused by overflow of Acc</li><li>0 = Trap was not caused by overflow of</li></ul>                 |                                          |

| bit 13           | <b>OVBERR:</b> Accumulator B Overflow Tra                                                                               | p Flag bit <sup>(1)</sup>                |

|                  | <ul><li>1 = Trap was caused by overflow of Acc</li><li>0 = Trap was not caused by overflow of</li></ul>                 |                                          |

| bit 12           | <b>COVAERR:</b> Accumulator A Catastrophi 1 = Trap was caused by catastrophic ov 0 = Trap was not caused by catastrophi | erflow of Accumulator A                  |

| bit 11           | COVBERR: Accumulator B Catastrophi                                                                                      | ic Overflow Trap Flag bit <sup>(1)</sup> |

|                  | 1 = Trap was caused by catastrophic ov 0 = Trap was not caused by catastrophi                                           | ic overflow of Accumulator B             |

| bit 10           | <b>OVATE:</b> Accumulator A Overflow Trap I                                                                             | Enable bit <sup>(1)</sup>                |

|                  | <ul><li>1 = Trap overflow of Accumulator A</li><li>0 = Trap is disabled</li></ul>                                       |                                          |

| bit 9            | <b>OVBTE:</b> Accumulator B Overflow Trap                                                                               | Enable bit <sup>(1)</sup>                |

|                  | <ul><li>1 = Trap overflow of Accumulator B</li><li>0 = Trap is disabled</li></ul>                                       |                                          |

| bit 8            | COVTE: Catastrophic Overflow Trap Er                                                                                    | nable bit <sup>(1)</sup>                 |

|                  | <ul><li>1 = Trap on catastrophic overflow of Ac</li><li>0 = Trap is disabled</li></ul>                                  | cumulator A or B is enabled              |

| bit 7            | SFTACERR: Shift Accumulator Error St                                                                                    |                                          |

|                  | 1 = Math error trap was caused by an ir<br>0 = Math error trap was not caused by a                                      |                                          |

| bit 6            | <b>DIV0ERR:</b> Divide-by-Zero Error Status                                                                             |                                          |

|                  | 1 = Math error trap was caused by a div<br>0 = Math error trap was not caused by a                                      | -                                        |

| bit 5            | DMACERR: DMAC Trap Flag bit                                                                                             |                                          |

|                  |                                                                                                                         |                                          |

1 = DMAC trap has occurred0 = DMAC trap has not occurred

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

Legend:

R = Readable bit

### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      | _   | _   | _   | IC4MD | IC3MD | IC2MD | IC1MD |

| bit 15 |     |     |     |       |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | OC4MD | OC3MD | OC2MD | OC1MD |

| bit 7 |     |     |     |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0'

bit 11 IC4MD: Input Capture 4 Module Disable bit

1 = Input Capture 4 module is disabled

0 = Input Capture 4 module is enabled

bit 10 IC3MD: Input Capture 3 Module Disable bit

1 = Input Capture 3 module is disabled0 = Input Capture 3 module is enabled

bit 9 IC2MD: Input Capture 2 Module Disable bit

1 = Input Capture 2 module is disabled0 = Input Capture 2 module is enabled

bit 8 IC1MD: Input Capture 1 Module Disable bit

1 = Input Capture 1 module is disabled0 = Input Capture 1 module is enabled

bit 7-4 **Unimplemented:** Read as '0'

bit 3 OC4MD: Output Compare 4 Module Disable bit

1 = Output Compare 4 module is disabled0 = Output Compare 4 module is enabled

bit 2 OC3MD: Output Compare 3 Module Disable bit

1 = Output Compare 3 module is disabled

0 = Output Compare 3 module is enabled

bit 1 OC2MD: Output Compare 2 Module Disable bit

1 = Output Compare 2 module is disabled0 = Output Compare 2 module is enabled

bit 0 OC1MD: Output Compare 1 Module Disable bit

1 = Output Compare 1 module is disabled

0 = Output Compare 1 module is enabled

# REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      |       |       |       | FLT2R<6:0> | •     |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

| U-0   | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|------------|-------|-------|-------|-------|-------|-------|

| _     | FLT1R<6:0> |       |       |       |       |       |       |

| bit 7 |            |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 FLT2R<6:0>: Assign PWM Fault 2 (FLT2) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

•

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 FLT1R<6:0>: Assign PWM Fault 1 (FLT1) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

| dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X |

|-----------------------------------------------------------------|

| NOTES:                                                          |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

bit 6-4

SYNCSRC<2:0>: Synchronous Source Selection bits<sup>(1)</sup>

111 = Reserved

100 = Reserved

011 = PTGO17<sup>(2)</sup>

010 = PTGO16<sup>(2)</sup>

001 = Reserved

000 = SYNCI1 input from PPS

bit 3-0

SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits<sup>(1)</sup>

1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event

0001 = 1:2 Postscaler generates Special Event Trigger on every second compare match event

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

0000 = 1:1 Postscaler generates Special Event Trigger on every compare match event

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

bit 2 HOMIEN: Home Input Event Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 1 IDXIRQ: Status Flag for Index Event Status bit

1 = Index event has occurred0 = No Index event has occurred

bit 0 IDXIEN: Index Input Event Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

#### REGISTER 17-19: INT1HLDH: INTERVAL 1 TIMER HOLD HIGH WORD REGISTER

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| INTHLD<31:24> |       |       |       |       |       |       |       |

| bit 15        |       |       |       |       |       |       | bit 8 |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| INTHLD<23:16> |       |       |       |       |       |       |       |  |

| bit 7         |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 INTHLD<31:16>: Hold Register for Reading and Writing INT1TMRH bits

### REGISTER 17-20: INT1HLDL: INTERVAL 1 TIMER HOLD LOW WORD REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| INTHLD<15:8> |       |       |       |       |       |       |       |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| INTHLD<7:0> |       |       |       |       |       |       |       |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **INTHLD<15:0>:** Hold Register for Reading and Writing INT1TMRL bits

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID5   | EID4  | EID3  | EID2  | EID1  | EID0  | RTR   | RB1   |

| bit 15 |       |       |       |       |       |       | bit 8 |

| U-x   | U-x | U-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-------|-------|-------|-------|-------|

| _     | _   | _   | RB0   | DLC3  | DLC2  | DLC1  | DLC0  |

| bit 7 |     |     |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **EID<5:0>:** Extended Identifier bits

bit 9 RTR: Remote Transmission Request bit

When IDE = 1:

1 = Message will request remote transmission

0 = Normal message When IDE = 0:

The RTR bit is ignored.

bit 8 RB1: Reserved Bit 1

User must set this bit to '0' per CAN protocol.

bit 7-5 **Unimplemented:** Read as '0'

bit 4 RB0: Reserved Bit 0

User must set this bit to '0' per CAN protocol.

bit 3-0 **DLC<3:0>:** Data Length Code bits

## BUFFER 21-4: ECAN™ MESSAGE BUFFER WORD 3

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |

|--------|-------|-------|-------|-------|-------|-------|-------|--|

| Byte 1 |       |       |       |       |       |       |       |  |

| bit 15 |       |       |       |       |       |       | bit 8 |  |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | Byt   | e 0   |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Byte 1<15:8>:** ECAN Message Byte 1 bits bit 7-0 **Byte 0<7:0>:** ECAN Message Byte 0 bits

## 23.4 ADC Control Registers

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0  | R/W-0   | U-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|--------|---------|-----|-------|-------|-------|

| ADON   | _   | ADSIDL | ADDMABM | _   | AD12B | FORM1 | FORM0 |

| bit 15 |     |        |         |     |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0, HC, HS | R/C-0, HC, HS       |

|-------|-------|-------|-------|--------|-------|---------------|---------------------|

| SSRC2 | SSRC1 | SSRC0 | SSRCG | SIMSAM | ASAM  | SAMP          | DONE <sup>(3)</sup> |

| bit 7 |       |       |       |        |       |               | bit 0               |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit  | C = Clearable bit  |

|-------------------|-----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 ADON: ADC1 Operating Mode bit

1 = ADC module is operating

0 = ADC is off

bit 14 **Unimplemented:** Read as '0'

bit 13 ADSIDL: ADC1 Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 ADDMABM: DMA Buffer Build Mode bit

1 = DMA buffers are written in the order of conversion; the module provides an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer

0 = DMA buffers are written in Scatter/Gather mode; the module provides a Scatter/Gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

bit 11 **Unimplemented:** Read as '0'

bit 10 AD12B: ADC1 10-Bit or 12-Bit Operation Mode bit

1 = 12-bit, 1-channel ADC operation

0 = 10-bit, 4-channel ADC operation

bit 9-8 **FORM<1:0>:** Data Output Format bits

For 10-Bit Operation:

11 = Signed fractional (Dout = sddd dddd dd00 0000, where s = .NOT.d<9>)

10 = Fractional (Dout = dddd dddd dd00 0000)

01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)

00 = Integer (Dout = 0000 00dd dddd dddd)

For 12-Bit Operation:

11 = Signed fractional (Dout = sddd dddd dddd 0000, where s = .NOT.d<11>)

10 = Fractional (Dout = dddd dddd dddd 0000)

01 = Signed integer (Dout = ssss sddd dddd, where s = .NOT.d<11>)

00 = Integer (Dout = 0000 dddd dddd dddd)

Note 1: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

3: Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

#### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

| R/W-0  | U-0 | U-0                       | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|---------------------------|-------|-----------------------|-----------------------|-----------------------|-----------------------|

| CH0NB  | _   | - CH0SB4 <sup>(1)</sup> C |       | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup> | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |

| bit 15 |     |                           |       |                       |                       |                       | bit 8                 |

| R/W-0 | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| CH0NA | _   | _   | CH0SA4 <sup>(1)</sup> | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup> | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CHONB: Channel 0 Negative Input Select for Sample MUXB bit

1 = Channel 0 negative input is AN1(1)

0 = Channel 0 negative input is VREFL

bit 14-13 Unimplemented: Read as '0'

bit 12-8 CH0SB<4:0>: Channel 0 Positive Input Select for Sample MUXB bits<sup>(1)</sup>

11111 = Open; use this selection with CTMU capacitive and time measurement

11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP)

11101 = Reserved

11100 = Reserved

11011 = Reserved

11010 = Channel 0 positive input is the output of OA3/AN6(2,3)

11001 = Channel 0 positive input is the output of OA2/AN0<sup>(2)</sup>

11000 = Channel 0 positive input is the output of OA1/AN3<sup>(2)</sup>

10111 = Reserved

٠

\_

10000 = Reserved

01111 = Channel 0 positive input is AN15<sup>(3)</sup>

01110 = Channel 0 positive input is AN14<sup>(3)</sup>

01101 = Channel 0 positive input is AN13<sup>(3)</sup>

•

.

00010 = Channel 0 positive input is AN2<sup>(3)</sup>

00001 = Channel 0 positive input is AN1(3)

00000 = Channel 0 positive input is AN0<sup>(3)</sup>

bit 7 CHONA: Channel 0 Negative Input Select for Sample MUXA bit

1 = Channel 0 negative input is AN1<sup>(1)</sup>

0 = Channel 0 negative input is VREFL

bit 6-5 **Unimplemented:** Read as '0'

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- 3: See the "Pin Diagrams" section for the available analog channels for each device.

# REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| HLMS   | _   | OCEN  | OCNEN | OBEN  | OBNEN | OAEN  | OANEN |

| bit 15 |     |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| NAGS  | PAGS  | ACEN  | ACNEN | ABEN  | ABNEN | AAEN  | AANEN |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| -n = Value at | POR '1' = Bit is set                                                                                | '0' = Bit is cleared                                                                                   | x = Bit is unknown |

|---------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------|

| bit 15        | - · · · · · · · · · · · · · · · · · · ·                                                             | king Select bits<br>tion will prevent any asserted ('0') co<br>tion will prevent any asserted ('1') co |                    |

| bit 14        | Unimplemented: Read as '0'                                                                          | , , ,                                                                                                  |                    |

| bit 13        | OCEN: OR Gate C Input Enable                                                                        | e bit                                                                                                  |                    |

|               | 1 = MCI is connected to OR gat<br>0 = MCI is not connected to OR                                    | re                                                                                                     |                    |

| bit 12        | OCNEN: OR Gate C Input Inve                                                                         | rted Enable bit                                                                                        |                    |

|               | <ul><li>1 = Inverted MCI is connected t</li><li>0 = Inverted MCI is not connect</li></ul>           | •                                                                                                      |                    |

| bit 11        | OBEN: OR Gate B Input Enable                                                                        | e bit                                                                                                  |                    |

|               | <ul><li>1 = MBI is connected to OR gat</li><li>0 = MBI is not connected to OR</li></ul>             |                                                                                                        |                    |

| bit 10        | OBNEN: OR Gate B Input Inve                                                                         | rted Enable bit                                                                                        |                    |

|               | <ul><li>1 = Inverted MBI is connected t</li><li>0 = Inverted MBI is not connect</li></ul>           | •                                                                                                      |                    |

| bit 9         | OAEN: OR Gate A Input Enable                                                                        | e bit                                                                                                  |                    |

|               | <ul><li>1 = MAI is connected to OR gat</li><li>0 = MAI is not connected to OR</li></ul>             |                                                                                                        |                    |

| bit 8         | OANEN: OR Gate A Input Inve                                                                         | rted Enable bit                                                                                        |                    |

|               | <ul><li>1 = Inverted MAI is connected t</li><li>0 = Inverted MAI is not connect</li></ul>           | •                                                                                                      |                    |

| bit 7         | NAGS: AND Gate Output Inver<br>1 = Inverted ANDI is connected<br>0 = Inverted ANDI is not connected | to OR gate                                                                                             |                    |

| bit 6         | PAGS: AND Gate Output Enab 1 = ANDI is connected to OR gate 0 = ANDI is not connected to O          | ate                                                                                                    |                    |

| bit 5         | ACEN: AND Gate C Input Enable 1 = MCI is connected to AND go 0 = MCI is not connected to AN         | ate                                                                                                    |                    |

| bit 4         | ACNEN: AND Gate C Input Inv<br>1 = Inverted MCI is connected t<br>0 = Inverted MCI is not connect   | o AND gate                                                                                             |                    |

## 26.3 Programmable CRC Registers

#### REGISTER 26-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0  | U-0            | R/W-0 | R-0    | R-0    | R-0    | R-0    | R-0   |

|--------|----------------|-------|--------|--------|--------|--------|-------|

| CRCEN  | — CSIDL VWORD4 |       | VWORD3 | VWORD2 | VWORD1 | VWORD0 |       |

| bit 15 |                |       |        |        |        |        | bit 8 |

| R-0    | R-1    | R/W-0   | R/W-0 | R/W-0   | U-0 | U-0 | U-0   |

|--------|--------|---------|-------|---------|-----|-----|-------|

| CRCFUL | CRCMPT | CRCISEL | CRCGO | LENDIAN | _   | _   | _     |

| bit 7  |        |         |       |         |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15 CRCEN: CRC Enable bit

1 = CRC module is enabled

0 = CRC module is disabled; all state machines, pointers and CRCWDAT/CRCDAT are reset, other SFRs are not reset

bit 14 **Unimplemented:** Read as '0'

bit 13 CSIDL: CRC Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-8 **VWORD<4:0>:** Pointer Value bits

Indicates the number of valid words in the FIFO. Has a maximum value of 8 when PLEN<4:0> > 7

or 16 when PLEN<4:0>  $\leq$  7.

bit 7 CRCFUL: CRC FIFO Full bit

1 = FIFO is full 0 = FIFO is not full

bit 6 CRCMPT: CRC FIFO Empty Bit

1 = FIFO is empty

0 = FIFO is not empty

bit 5 CRCISEL: CRC Interrupt Selection bit

1 = Interrupt on FIFO is empty; final word of data is still shifting through CRC

0 = Interrupt on shift is complete and CRCWDAT results are ready

bit 4 CRCGO: Start CRC bit

bit 3

1 = Starts CRC serial shifter0 = CRC serial shifter is turned off

LENDIAN: Data Word Little-Endian Configuration bit

1 = Data word is shifted into the CRC starting with the LSb (little endian)

0 = Data word is shifted into the CRC starting with the MSb (big endian)

bit 2-0 **Unimplemented:** Read as '0'

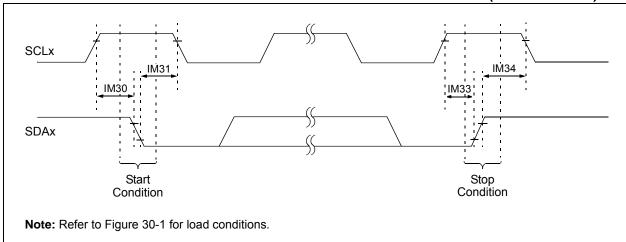

## FIGURE 30-30: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (MASTER MODE)

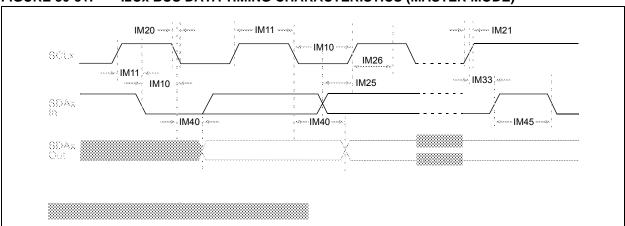

## FIGURE 30-31: I2Cx BUS DATA TIMING CHARACTERISTICS (MASTER MODE)

TABLE 31-8: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHAF   | DC CHARACTERISTICS                                          |                                                             |                                 | otherwi | ting Co<br>se state<br>erature | ed)                               | s: 3.0V to 3.6V<br>≤ TA ≤ +150°C               |

|-----------|-------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|---------|--------------------------------|-----------------------------------|------------------------------------------------|

| Param.    | Symbol                                                      | Characteristic                                              | Min. Typ. Max. Units Conditions |         |                                |                                   | Conditions                                     |

| HDO10     | Vol                                                         | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    | _                               | _       | 0.4                            | V                                 | IOL ≤ 5 mA, VDD = 3.3V (Note 1)                |

|           |                                                             | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                               | _       | 0.4                            | V                                 | IOL ≤ 8 mA, VDD = 3.3V (Note 1)                |

| HDO20 Voh | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                         | _                               | _       | V                              | IOH ≥ -10 mA, VDD = 3.3V (Note 1) |                                                |

|           |                                                             | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                             | _       | _                              | V                                 | IOH ≥ 15 mA, VDD = 3.3V (Note 1)               |

| HDO20A    | Vон1                                                        | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 1.5                             | _       | _                              | V                                 | IOH ≥ -3.9 mA, VDD = 3.3V (Note 1)             |

|           |                                                             |                                                             | 2.0                             | _       | _                              |                                   | IOH ≥ -3.7 mA, VDD = 3.3V (Note 1)             |

|           |                                                             |                                                             | 3.0                             | _       | _                              |                                   | IOH ≥ -2 mA, VDD = 3.3V (Note 1)               |

|           |                                                             | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 1.5                             | _       | _                              | V                                 | IOH ≥ -7.5 mA, VDD = 3.3V (Note 1)             |

|           |                                                             |                                                             | 2.0                             | _       | _                              |                                   | $IOH \ge -6.8 \text{ mA}, VDD = 3.3V$ (Note 1) |

|           |                                                             |                                                             | 3.0                             | _       | _                              |                                   | $IOH \ge -3 \text{ mA}, VDD = 3.3V$ (Note 1)   |

Note 1: Parameters are characterized, but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

3: Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<15:7> and RC3

For 64-pin devices: RA4, RA9, RB<15:7>, RC3 and RC15

| Remappable Input for U1RX                |     | Memory Map for PIC24EP256GP/MC20X/50X   |     |

|------------------------------------------|-----|-----------------------------------------|-----|

| Reset System                             |     | Devices                                 | 60  |

| Shared Port Structure                    |     | Memory Map for PIC24EP32GP/MC20X/50X    |     |

| Single-Phase Synchronous Buck Converter  |     | Devices                                 | 57  |

| SPIx Module                              |     | Memory Map for PIC24EP512GP/MC20X/50X   | _   |

| Suggested Oscillator Circuit Placement   |     | Devices                                 | 6′  |

| Type B Timer (Timer2 and Timer4)         |     | Memory Map for PIC24EP64GP/MC20X/50X    |     |

| Type B/Type C Timer Pair (32-Bit Timer)  |     | Devices                                 |     |

| Type C Timer (Timer3 and Timer5)         |     | Near Data Space                         |     |

| UARTx Module                             |     | Organization, Alignment                 |     |

| User-Programmable Blanking Function      |     | SFR Space                               |     |

| Watchdog Timer (WDT)                     |     | Width                                   | 51  |

| Brown-out Reset (BOR)                    | 384 | Data Memory                             |     |

| С                                        |     | Arbitration and Bus Master Priority     | 110 |

|                                          |     | Data Space                              | 404 |

| C Compilers                              | 200 | Extended X                              |     |

| MPLAB XC Compilers                       | 398 | Paged Memory Scheme                     | 105 |

| Charge Time Measurement Unit. See CTMU.  |     | DC and AC Characteristics               |     |

| Code Examples                            |     | Graphs                                  | 4/5 |

| IC1 Connection to QEI1 Input on          | 176 | DC Characteristics                      | 44. |

| Pin 43 of dsPIC33EPXXXMC206              |     | BOR                                     |     |

| Port Write/Read                          | 174 | CTMU Current Source Requirements        |     |

| PWMx Write-Protected Register            | 000 | Doze Current (IDOZE)40                  |     |

| Unlock Sequence                          |     | High Temperature                        |     |

| PWRSAV Instruction Syntax                |     | I/O Pin Input Specifications            |     |

| Code Protection                          |     | I/O Pin Output Specifications41         |     |

| CodeGuard Security                       |     | Idle Current (IDLE)                     |     |

| Configuration Bits                       |     | Op Amp/Comparator Requirements          | 455 |

| Description                              |     | Op Amp/Comparator Voltage Reference     |     |

| Configuration Byte Register Map          |     | Requirements                            |     |

| Configuring Analog and Digital Port Pins | 174 | Operating Current (IDD)40               |     |

| CPU                                      |     | Operating MIPS vs. Voltage40            |     |

| Addressing Modes                         |     | Power-Down Current (IPD)40              |     |

| Clocking System Options                  |     | Program Memory                          |     |

| Fast RC (FRC) Oscillator                 |     | Temperature and Voltage                 |     |

| FRC Oscillator with PLL                  |     | Temperature and Voltage Specifications  |     |

| FRC Oscillator with Postscaler           |     | Thermal Operating Conditions            |     |

| Low-Power RC (LPRC) Oscillator           |     | Watchdog Timer Delta Current            | 407 |

| Primary (XT, HS, EC) Oscillator          |     | Demo/Development Boards, Evaluation and |     |

| Primary Oscillator with PLL              |     | Starter Kits                            |     |

| Control Registers                        |     | Development Support                     |     |

| Data Space Addressing                    |     | Third-Party Tools                       | 400 |

| Instruction Set                          |     | DMA Controller                          |     |

| Resources                                | 39  | Channel to Peripheral Associations      |     |

| CTMU                                     |     | Control Registers                       |     |

| Control Registers                        |     | DMAxCNT                                 |     |

| Resources                                |     | DMAxCON                                 | 14′ |

| Customer Change Notification Service     |     | DMAxPAD                                 |     |

| Customer Notification Service            |     | DMAxREQ                                 | 141 |

| Customer Support                         | 524 | DMAxSTA                                 | 141 |

| D                                        |     | DMAxSTB                                 |     |

| _                                        |     | Resources                               |     |

| Data Address Space                       | 51  | Supported Peripherals                   | 139 |

| Memory Map for dsPIC33EP128MC20X/50X,    |     | Doze Mode                               |     |

| dsPIC33EP128GP50X Devices                | 54  | DSP Engine                              | 44  |

| Memory Map for dsPIC33EP256MC20X/50X,    |     | _                                       |     |

| dsPIC33EP256GP50X Devices                | 55  | E                                       |     |

| Memory Map for dsPIC33EP32MC20X/50X,     |     | ECAN Message Buffers                    |     |

| dsPIC33EP32GP50X Devices                 | 52  | Word 0                                  |     |

| Memory Map for dsPIC33EP512MC20X/50X,    |     | Word 1                                  | 310 |

| dsPIC33EP512GP50X Devices                | 56  | Word 2                                  | 31′ |

| Memory Map for dsPIC33EP64MC20X/50X,     |     | Word 3                                  | 31′ |

| dsPIC33EP64GP50X Devices                 | 53  | Word 4                                  | 312 |

| Memory Map for PIC24EP128GP/MC20X/50X    |     | Word 5                                  | 312 |

| Devices                                  | 59  | Word 6                                  |     |

|                                          |     | Word 7                                  | 313 |

| dsPIC33EPXXXGP5 | 0X, dsPIC33EPXXXN | 1C20X/50X AND P | IC24EPXXXGP/M | C20X |

|-----------------|-------------------|-----------------|---------------|------|

| NOTES:          |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |