Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 48-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc504-i-mv |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X PRODUCT FAMILIES

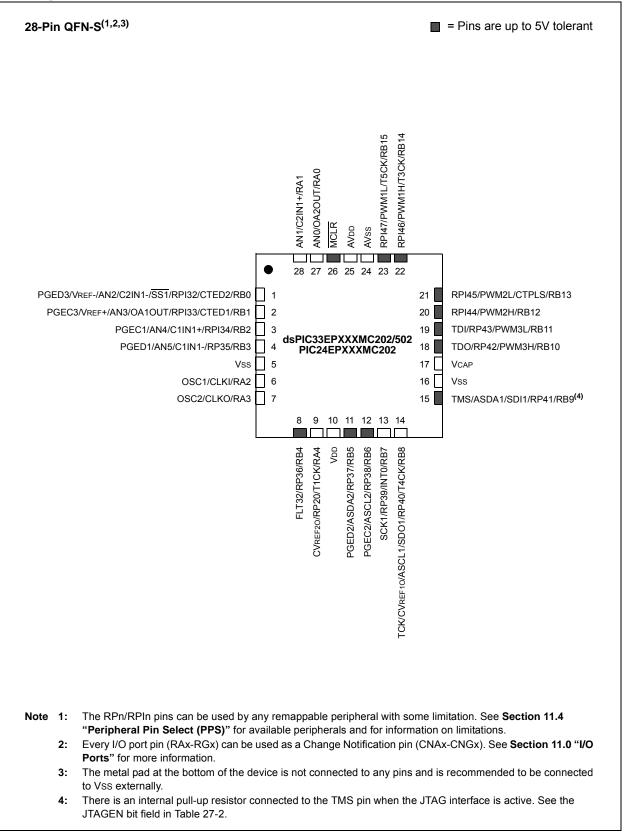

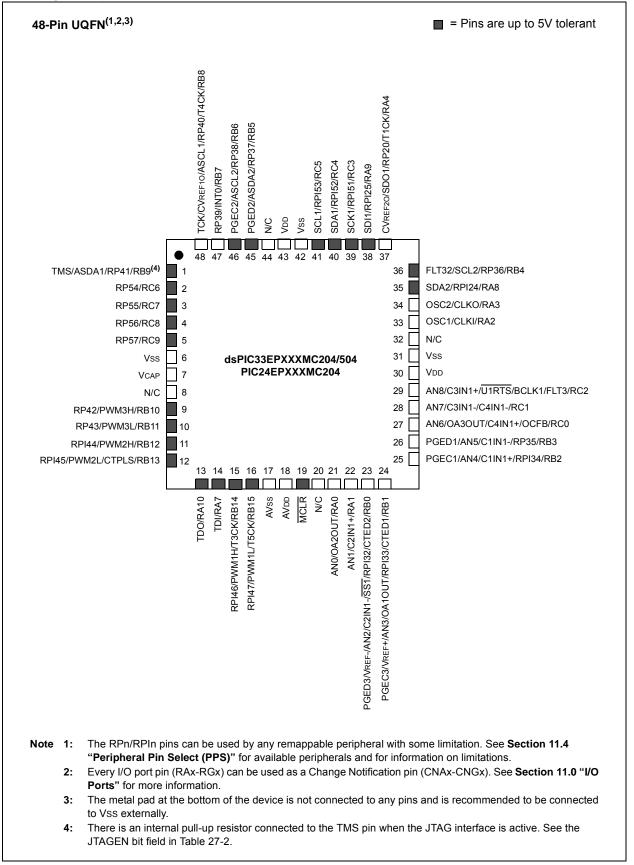

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1 (General Purpose Families) and Table 2 (Motor Control Families). Their pinout diagrams appear on the following pages.

|                   | â                              | (se                           |             |                      | Rei           | nappa          | ble Pe | eriphe             | rals                          |                                    |      |               |                              |                     |        |         |           |               |                                |

|-------------------|--------------------------------|-------------------------------|-------------|----------------------|---------------|----------------|--------|--------------------|-------------------------------|------------------------------------|------|---------------|------------------------------|---------------------|--------|---------|-----------|---------------|--------------------------------|

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbyte) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | UART   | SPI <sup>(2)</sup> | ECAN <sup>TM</sup> Technology | External Interrupts <sup>(3)</sup> | I²C™ | CRC Generator | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU   | РТС     | I/O Pins  | Pins          | Packages                       |

| PIC24EP32GP202    | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               |                                |

| PIC24EP64GP202    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               | SPDIP,                         |

| PIC24EP128GP202   | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | —                             | 3                                  | 2    | 1             | 6                            | 2/3(1)              | Yes    | Yes     | 21        | 28            | SOIC,<br>SSOP <sup>(4)</sup> , |

| PIC24EP256GP202   | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               | QFN-S                          |

| PIC24EP512GP202   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               |                                |

| PIC24EP32GP203    | 512                            | 32                            | 4           | 5                    | 4             | 4              | 2      | 2                  |                               | 3                                  | 2    | 1             | 8                            | 3/4                 | Vaa    | Vaa     | 25        | 36            | VTLA                           |

| PIC24EP64GP203    | 1024                           | 64                            | 8           | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    |               | 0                            | 3/4                 | Yes    | Yes     | 25        | 30            | VILA                           |

| PIC24EP32GP204    | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               |                                |

| PIC24EP64GP204    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               | VTLA <sup>(4)</sup> ,          |

| PIC24EP128GP204   | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    | 1             | 9 3/4                        | Yes                 | es Yes | 35      | 44/<br>48 | TQFP,<br>QFN, |                                |

| PIC24EP256GP204   | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           | 40            | UQFN                           |

| PIC24EP512GP204   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               |                                |

| PIC24EP64GP206    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               |                                |

| PIC24EP128GP206   | 1024                           | 128                           | 16          | _                    |               |                |        |                    |                               |                                    | -    |               |                              | ~ ~ ~               |        |         |           | ~ /           | TQFP.                          |

| PIC24EP256GP206   | 1024                           | 256                           | 32          | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    | 1             | 16                           | 3/4                 | Yes    | Yes     | 53        | 64            | QFN                            |

| PIC24EP512GP206   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               |                                |

| dsPIC33EP32GP502  | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               |                                |

| dsPIC33EP64GP502  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               | SPDIP,                         |

| dsPIC33EP128GP502 | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 6                            | 2/3(1)              | Yes    | Yes     | 21        | 28            | SOIC,<br>SSOP <sup>(4)</sup> . |

| dsPIC33EP256GP502 | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               | QFN-S                          |

| dsPIC33EP512GP502 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               |                                |

| dsPIC33EP32GP503  | 512                            | 32                            | 4           | _                    | _             | _              | _      | _                  |                               | _                                  | _    |               | _                            |                     |        |         |           |               |                                |

| dsPIC33EP64GP503  | 1024                           | 64                            | 8           | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 8                            | 3/4                 | Yes    | Yes     | 25        | 36            | VTLA                           |

| dsPIC33EP32GP504  | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              | İ                   |        |         |           |               |                                |

| dsPIC33EP64GP504  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               | VTLA <sup>(4)</sup> ,          |

| dsPIC33EP128GP504 | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 9                            | 3/4                 | Yes    | Yes     | 35        | 44/<br>48     | TQFP,<br>QFN,                  |

| dsPIC33EP256GP504 | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           | 40            | UQFN,<br>UQFN                  |

| dsPIC33EP512GP504 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               |                                |

| dsPIC33EP64GP506  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              | 1                   |        |         |           |               |                                |

| dsPIC33EP128GP506 | 1024                           | 128                           | 16          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               | TQFP,                          |

| dsPIC33EP256GP506 | 1024                           | 256                           | 32          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 1 3                                | 3 2  | 2 1 16        | 16                           | 16 3/4              | 4 Yes  | s Yes 5 | 53        | 64            | TQFP,<br>QFN                   |

| dsPIC33EP512GP506 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |        |         |           |               |                                |

|                   |                                | 1                             |             |                      |               | 1              | 1      | 1                  |                               |                                    | 1    | 1             | 1                            |                     |        |         |           |               |                                |

#### TABLE 1: dsPIC33EPXXXGP50X and PIC24EPXXXGP20X GENERAL PURPOSE FAMILIES

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

Only SPI2 is remappable.

INT0 is not remappable.

4: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

#### Pin Diagrams (Continued)

## Pin Diagrams (Continued)

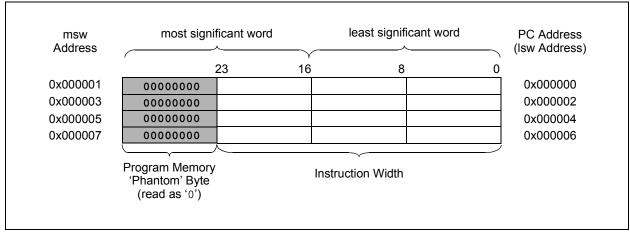

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

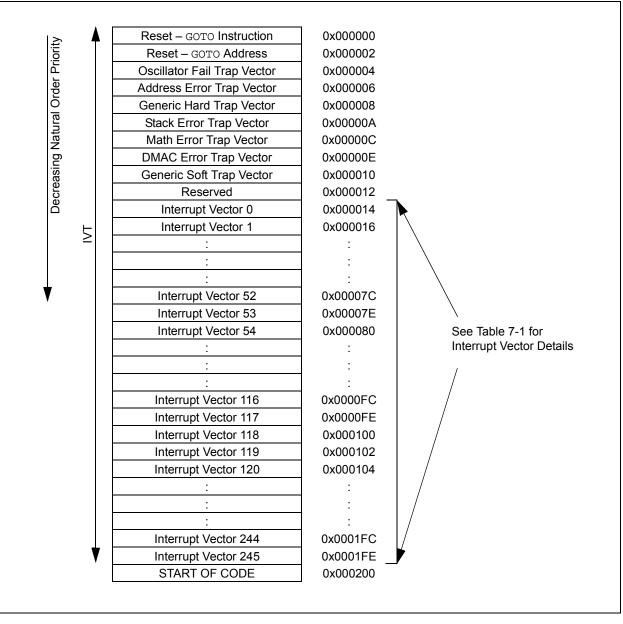

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

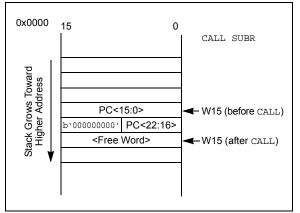

#### 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack               |

|-------|---------------------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the hardware. |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-19 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-19. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

FIGURE 4-19: CALL STACK FRAME

#### FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

#### 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

#### **11.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Change Noti-      |

|-------|----------------------------------------------|

|       | fication pins should always be disabled      |

|       | when the port pin is configured as a digital |

|       | output.                                      |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, WO | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

| REGISTE       | R 16-7: PWMC                                                         | CONX: PWMX (                                                                                                                      | CONTROL R      | EGISTER          |                      |                      |                     |  |  |  |  |  |  |  |

|---------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|--|--|--|--|--|--|--|

| HS/HC-        | 0 HS/HC-0                                                            | HS/HC-0                                                                                                                           | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |  |  |  |  |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>                                           | TRGSTAT                                                                                                                           | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |  |  |  |  |  |  |

| bit 15        | ·                                                                    | •                                                                                                                                 |                | ÷                |                      |                      | bit                 |  |  |  |  |  |  |  |

| R/W-0         | R/W-0                                                                | R/W-0                                                                                                                             | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |  |  |  |  |

| DTC1          |                                                                      | DTCP <sup>(3)</sup>                                                                                                               | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |  |  |  |  |  |  |

| bit 7         | DICO                                                                 | DICE                                                                                                                              | _              | INT DO           | CAIM                 | AFRES'               | bit                 |  |  |  |  |  |  |  |

|               |                                                                      |                                                                                                                                   |                |                  |                      |                      | <u> </u>            |  |  |  |  |  |  |  |

| Legend:       |                                                                      | HC = Hardware                                                                                                                     | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |  |  |  |  |  |  |  |

| R = Reada     | able bit                                                             | W = Writable bi                                                                                                                   | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |  |  |  |  |  |  |  |

| -n = Value    | at POR                                                               | '1' = Bit is set                                                                                                                  |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |  |  |  |  |  |  |  |

| bit 15        | ELTSTAT: ES                                                          | ult Intorrunt Stati                                                                                                               | is hit(1)      |                  |                      |                      |                     |  |  |  |  |  |  |  |

| DIL 15        |                                                                      | <b>FLTSTAT:</b> Fault Interrupt Status bit <sup>(1)</sup><br>1 = Fault interrupt is pending                                       |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | 1 = Fault interrupt is pending<br>0 = No Fault interrupt is pending                                                               |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | ared by setting F                                                                                                                 |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

| bit 14        |                                                                      | rent-Limit Interru                                                                                                                | •              |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | 1 = Current-limit interrupt is pending<br>0 = No current-limit interrupt is pending                                               |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | This bit is cleared by setting CLIEN = 0.                                                                                         |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

| bit 13        |                                                                      | TRGSTAT: Trigger Interrupt Status bit                                                                                             |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | 1 = Trigger interrupt is pending                                                                                                  |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | 0 = No trigger interrupt is pending<br>This bit is cleared by setting TRGIEN = 0.                                                 |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      |                                                                                                                                   |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

| bit 12        | FLTIEN: Fault Interrupt Enable bit<br>1 = Fault interrupt is enabled |                                                                                                                                   |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | rrupt is enabled                                                                                                                  | and the FLTS   | TAT bit is clear | ed                   |                      |                     |  |  |  |  |  |  |  |

| bit 11        |                                                                      | ent-Limit Interrup                                                                                                                |                |                  | cu .                 |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | mit interrupt is er                                                                                                               |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | mit interrupt is di                                                                                                               |                | e CLSTAT bit is  | s cleared            |                      |                     |  |  |  |  |  |  |  |

| bit 10        | TRGIEN: Trig                                                         | ger Interrupt En                                                                                                                  | able bit       |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | event generates                                                                                                                   |                |                  | T hit is cleared     |                      |                     |  |  |  |  |  |  |  |

| bit 9         |                                                                      | vent interrupts ar                                                                                                                |                |                  | i bit is cleared     |                      |                     |  |  |  |  |  |  |  |

| DIL 9         |                                                                      | <b>ITB:</b> Independent Time Base Mode bit <sup>(2)</sup><br>1 = PHASEx register provides time base period for this PWM generator |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | egister provides f                                                                                                                | •              |                  | •                    |                      |                     |  |  |  |  |  |  |  |

| bit 8         |                                                                      | er Duty Cycle Re                                                                                                                  |                |                  |                      |                      |                     |  |  |  |  |  |  |  |

|               |                                                                      | ister provides du<br>jister provides du                                                                                           |                |                  |                      | r                    |                     |  |  |  |  |  |  |  |

| Note 1:       | Software must clea                                                   |                                                                                                                                   |                |                  | -                    |                      | t controller        |  |  |  |  |  |  |  |

| Note 1.<br>2: | These bits should                                                    | -                                                                                                                                 |                | -                | -                    | the interrup         |                     |  |  |  |  |  |  |  |

| 3:            | DTC<1:0> = 11 fo                                                     | -                                                                                                                                 |                | -                | -                    |                      |                     |  |  |  |  |  |  |  |

| 4:            | The Independent T<br>CAM bit is ignored                              | Time Base (ITB =                                                                                                                  |                | •                |                      | igned mode. If       | TTB = 0, the        |  |  |  |  |  |  |  |

| 5:            | To operate in Exter                                                  |                                                                                                                                   | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |  |  |  |  |  |  |  |

## REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                                      | R/W-0 | R/W-0 | R/W-0            | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |  |  |  |

|--------------------------------------------|-------|-------|------------------|------------------------------------|-----------------|-------|-------|--|--|--|

|                                            |       |       | INDXH            | LD<15:8>                           |                 |       |       |  |  |  |

| bit 15                                     |       |       |                  |                                    |                 |       | bit 8 |  |  |  |

|                                            |       |       |                  |                                    |                 |       |       |  |  |  |

| R/W-0                                      | R/W-0 | R/W-0 | R/W-0            | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |  |  |  |

|                                            |       |       | INDXF            | ILD<7:0>                           |                 |       |       |  |  |  |

| bit 7                                      |       |       |                  |                                    |                 |       | bit 0 |  |  |  |

| Legend:                                    |       |       |                  |                                    |                 |       |       |  |  |  |

| R = Readable bit W = Writable bit          |       |       |                  | U = Unimplemented bit, read as '0' |                 |       |       |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = E |       |       | '0' = Bit is cle | ared                               | x = Bit is unkr | nown  |       |  |  |  |

## REGISTER 17-10: INDX1HLD: INDEX COUNTER 1 HOLD REGISTER

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDX1CNTH bits

#### REGISTER 17-11: QEI1ICH: QEI1 INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0                            | R/W-0                                   | R/W-0                                                                                 | R/W-0                                                                                                                                                     | R/W-0                                                                                         |  |  |  |

|------------------------------------|-------|----------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

|                                    |       | QEIIC                            | <31:24>                                 |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |

|                                    |       |                                  |                                         |                                                                                       |                                                                                                                                                           | bit 8                                                                                         |  |  |  |

|                                    |       |                                  |                                         |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |

| R/W-0                              | R/W-0 | R/W-0                            | R/W-0                                   | R/W-0                                                                                 | R/W-0                                                                                                                                                     | R/W-0                                                                                         |  |  |  |

|                                    |       | QEIIC                            | <23:16>                                 |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |

|                                    |       |                                  |                                         |                                                                                       |                                                                                                                                                           | bit 0                                                                                         |  |  |  |

|                                    |       |                                  |                                         |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |

|                                    |       |                                  |                                         |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |

| R = Readable bit W = Writable bit  |       |                                  |                                         | U = Unimplemented bit, read as '0'                                                    |                                                                                                                                                           |                                                                                               |  |  |  |

| -n = Value at POR '1' = Bit is set |       |                                  | '0' = Bit is cleared x = Bit is unknown |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |

|                                    | R/W-0 | R/W-0 R/W-0<br>it W = Writable I | QEIIC<br>R/W-0 R/W-0 QEIIC<br>QEIIC     | QEIIC<31:24><br>R/W-0 R/W-0 R/W-0<br>QEIIC<23:16><br>it W = Writable bit U = Unimplen | QEIIC<31:24>           R/W-0         R/W-0         R/W-0           QEIIC<23:16>           it         W = Writable bit         U = Unimplemented bit, real | QEIIC<31:24>           R/W-0         R/W-0         R/W-0         R/W-0           QEIIC<23:16> |  |  |  |

bit 15-0 **QEIIC<31:16>:** High Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

#### REGISTER 17-12: QEI1ICL: QEI1 INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|

|                                   |       |                  | QEII  | C<15:8>                            |       |                    |       |  |

| bit 15                            |       |                  |       |                                    |       |                    | bit 8 |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

|                                   |       |                  | QEI   | C<7:0>                             |       |                    |       |  |

| bit 7                             |       |                  |       |                                    |       |                    | bit C |  |

| Legend:                           |       |                  |       |                                    |       |                    |       |  |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at POR                 |       | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unknown |       |  |

bit 15-0 **QEIIC<15:0>:** Low Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

| REGISTER 24-6: | PTGSDLIM: PTG STEP DELAY LIMIT REGISTER <sup>(1,2)</sup> |

|----------------|----------------------------------------------------------|

|                |                                                          |

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|----------------------------------------------------------------------------|-------|----------------|-------|--------------|------------------|----------|-------|

|                                                                            |       |                | PTGSD | LIM<15:8>    |                  |          |       |

| bit 15                                                                     |       |                |       |              |                  |          | bit 8 |

|                                                                            |       |                |       |              |                  |          |       |

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                                                                            |       |                | PTGSE | )LIM<7:0>    |                  |          |       |

| bit 7                                                                      |       |                |       |              |                  |          | bit 0 |

|                                                                            |       |                |       |              |                  |          |       |

| Legend:                                                                    |       |                |       |              |                  |          |       |

| R = Readable                                                               | bit   | W = Writable b | it    | U = Unimplen | nented bit, read | d as '0' |       |

| -n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown |       |                |       |              |                  |          | nown  |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

**Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|----------------------------------------------------------------------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |                                                                      |                  | PTGC0 | LIM<15:8>                               |       |       |       |

| bit 15          |                                                                      |                  |       |                                         |       |       | bit 8 |

|                 |                                                                      |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |                                                                      |                  | PTGC  | )LIM<7:0>                               |       |       |       |

| bit 7           |                                                                      |                  |       |                                         |       |       | bit 0 |

|                 |                                                                      |                  |       |                                         |       |       |       |

| Legend:         |                                                                      |                  |       |                                         |       |       |       |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |       |                                         |       |       |       |

| -n = Value at P | POR                                                                  | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |

|--------|-----|-----|-----|----------|----------|----------|----------|

| —      | —   | —   | _   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |

| bit 15 |     |     |     |          |          |          | bit 8    |

|        |     |     |     |          |          |          |          |

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 15-12 Unimplemented: Read as '0'

| DIL 15-12 | Unimplemented. Read as 0                                                                                                                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8  | SELSRCC<3:0>: Mask C Input Select bits                                                                                                                                                                                                         |

|           | 1111 <b>= FLT4</b>                                                                                                                                                                                                                             |

|           | 1110 <b>= FLT2</b>                                                                                                                                                                                                                             |

|           | 1101 <b>= PTGO19</b>                                                                                                                                                                                                                           |

|           | 1100 = PTGO18                                                                                                                                                                                                                                  |

|           | 1011 = Reserved                                                                                                                                                                                                                                |

|           | 1010 = Reserved                                                                                                                                                                                                                                |

|           | 1001 = Reserved                                                                                                                                                                                                                                |

|           | 1000 = Reserved                                                                                                                                                                                                                                |

|           | 0111 = Reserved                                                                                                                                                                                                                                |

|           | 0110 = Reserved                                                                                                                                                                                                                                |

|           | 0101 = PWM3H                                                                                                                                                                                                                                   |

|           | 0100 = PWM3L                                                                                                                                                                                                                                   |

|           | 0011 = PWM2H                                                                                                                                                                                                                                   |

|           | 0010 = PWM2L                                                                                                                                                                                                                                   |

|           | 0001 = PWM1H                                                                                                                                                                                                                                   |

|           | 0000 = PWM1L                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits                                                                                                                                                                                                         |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits 1111 = FLT4                                                                                                                                                                                             |

| bit 7-4   | •                                                                                                                                                                                                                                              |

| bit 7-4   | 1111 <b>= FLT4</b>                                                                                                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2                                                                                                                                                                                                                     |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19                                                                                                                                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved                                                                                                                          |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved                                                                                                       |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved                                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM2L |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM1H |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM2L |

| DC CH        | ARACTE | RISTICS                                 | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |    |    |                                                                                                                                                                                       |  |  |

|--------------|--------|-----------------------------------------|-------------------------------------------------------|---|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol | Characteristic                          | Min. Typ. Max. Units Conditions                       |   |    |    |                                                                                                                                                                                       |  |  |

|              | liL    | Input Leakage Current <sup>(1,2)</sup>  |                                                       |   |    |    |                                                                                                                                                                                       |  |  |

| DI50         |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                                                    | — | +1 | μA | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in \ at \ high-impedance} \end{split}$                                                             |  |  |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | $\label{eq:VSS} \begin{array}{l} Vss \leq V \text{PIN} \leq V \text{DD}, \\ \text{Pin at high-impedance}, \\ -40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C} \end{array}$ |  |  |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +85^{\circ}C$                                                                                               |  |  |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                                                              |  |  |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +125^{\circ}C$                                                                                              |  |  |

| DI55         |        | MCLR                                    | -5                                                    | — | +5 | μA | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                                                              |  |  |

| DI56         |        | OSC1                                    | -5                                                    | — | +5 | μΑ | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &X{\sf T} \text{ and }H{\sf S} \text{ modes} \end{split}$                                                 |  |  |

#### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

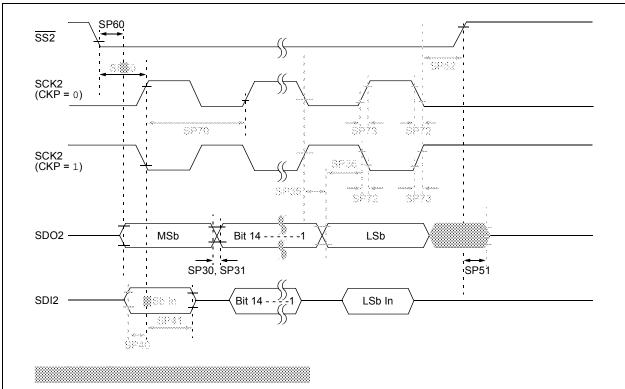

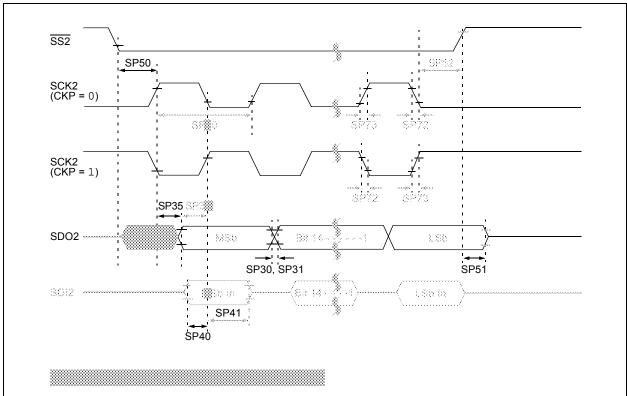

#### FIGURE 30-19: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

#### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

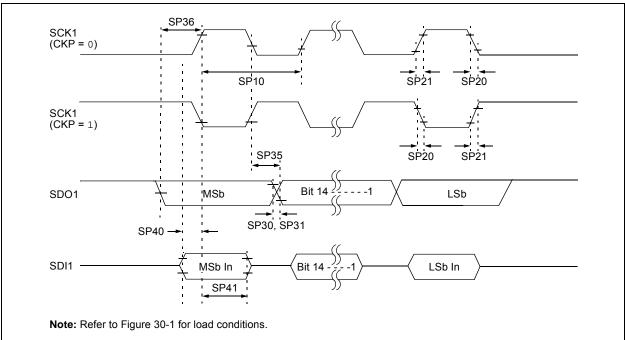

#### FIGURE 30-24: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-43:SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHA | RACTERIST             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |                     |      |       |                             |

|--------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|-----------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                     | Min. | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP10   | FscP                  | Maximum SCK1 Frequency                                                                                                                                                                                                                                                            | _    | —                   | 10   | MHz   | (Note 3)                    |

| SP20   | TscF                  | SCK1 Output Fall Time                                                                                                                                                                                                                                                             | —    | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP21   | TscR                  | SCK1 Output Rise Time                                                                                                                                                                                                                                                             | —    | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                                                                                                                                                                                                                                                        | —    | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                                                                                                                                                                                                                                                        | —    | _                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge                                                                                                                                                                                                                                         | —    | 6                   | 20   | ns    |                             |

| SP36   | TdoV2sc,<br>TdoV2scL  | SDO1 Data Output Setup to<br>First SCK1 Edge                                                                                                                                                                                                                                      | 30   | —                   | _    | ns    |                             |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data<br>Input to SCK1 Edge                                                                                                                                                                                                                                     | 30   | —                   | _    | ns    |                             |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge                                                                                                                                                                                                                                         | 30   |                     |      | ns    |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPI1 pins.

| AC CHARACTERISTICS |        |                                                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |         |       |       |                                         |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-----------------------------------------|