Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc504-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

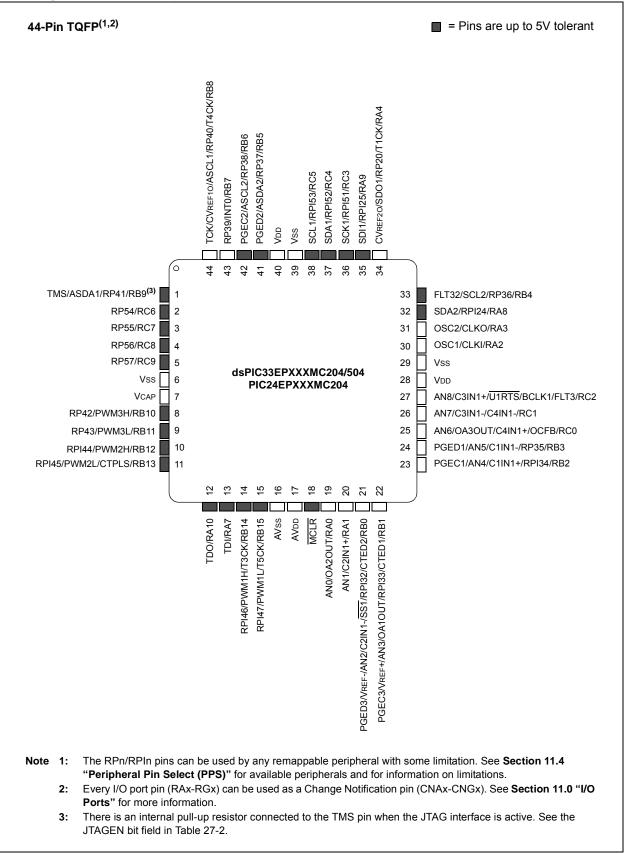

#### Pin Diagrams (Continued)

## **Table of Contents**

| 1.0   | Device Overview                                                                                    |     |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             |     |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           |     |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

|       | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     |     |

|       | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) |     |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

|       | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      |     |

|       | Universal Asynchronous Receiver Transmitter (UART)                                                 |     |

|       | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    |     |

|       | Charge Time Measurement Unit (CTMU)                                                                |     |

|       | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    |     |

|       | Peripheral Trigger Generator (PTG) Module                                                          |     |

| 25.0  | Op Amp/Comparator Module                                                                           |     |

|       | Programmable Cyclic Redundancy Check (CRC) Generator                                               |     |

| 27.0  |                                                                                                    |     |

|       |                                                                                                    |     |

| 29.0  | Development Support                                                                                |     |

|       | Electrical Characteristics                                                                         |     |

|       | High-Temperature Electrical Characteristics                                                        |     |

|       | DC and AC Device Characteristics Graphs                                                            |     |

|       | Packaging Information                                                                              |     |

|       | ndix A: Revision History                                                                           |     |

|       | (                                                                                                  |     |

|       | Vicrochip Web Site                                                                                 |     |

|       | omer Change Notification Service                                                                   |     |

|       | omer Support                                                                                       |     |

| Produ | uct Identification System                                                                          | 527 |

| TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                |     |                                                                                  |  |  |  |  |

|------------------------------------------------|-------------|----------------|-----|----------------------------------------------------------------------------------|--|--|--|--|

| Pin Name <sup>(4)</sup>                        | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                      |  |  |  |  |

| U2CTS                                          | Ι           | ST             | No  | UART2 Clear-To-Send.                                                             |  |  |  |  |

| U2RTS                                          | 0           | —              | No  | UART2 Ready-To-Send.                                                             |  |  |  |  |

| U2RX                                           | Ι           | ST             | Yes | UART2 receive.                                                                   |  |  |  |  |

| U2TX                                           | 0           | —              | Yes | UART2 transmit.                                                                  |  |  |  |  |

| BCLK2                                          | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                                       |  |  |  |  |

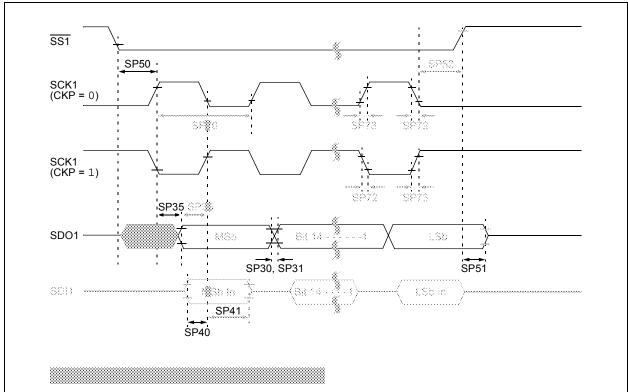

| SCK1                                           | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                                  |  |  |  |  |

| SDI1                                           | I           | ST             | No  | SPI1 data in.                                                                    |  |  |  |  |

| SDO1                                           | 0           | —              | No  | SPI1 data out.                                                                   |  |  |  |  |

| SS1                                            | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                                   |  |  |  |  |

| SCK2                                           | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                                  |  |  |  |  |

| SDI2                                           | I           | ST             | Yes | SPI2 data in.                                                                    |  |  |  |  |

| SDO2                                           | 0           | _              | Yes | SPI2 data out.                                                                   |  |  |  |  |

| SS2                                            | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.                                   |  |  |  |  |

| SCL1                                           | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                                  |  |  |  |  |

| SDA1                                           | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                                   |  |  |  |  |

| ASCL1                                          | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.                        |  |  |  |  |

| ASDA1                                          | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.                         |  |  |  |  |

| SCL2                                           | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                                  |  |  |  |  |

| SDA2                                           | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                                   |  |  |  |  |

| ASCL2                                          | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.                        |  |  |  |  |

| ASDA2                                          | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.                         |  |  |  |  |

| TMS <sup>(5)</sup>                             | Ι           | ST             | No  | JTAG Test mode select pin.                                                       |  |  |  |  |

| TCK                                            | Ι           | ST             | No  | JTAG test clock input pin.                                                       |  |  |  |  |

| TDI                                            | I           | ST             | No  | JTAG test data input pin.                                                        |  |  |  |  |

| TDO                                            | 0           | _              | No  | JTAG test data output pin.                                                       |  |  |  |  |

| C1RX <sup>(2)</sup>                            | Ι           | ST             | Yes | ECAN1 bus receive pin.                                                           |  |  |  |  |

| C1TX <sup>(2)</sup>                            | 0           | _              | Yes | ECAN1 bus transmit pin.                                                          |  |  |  |  |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup>      | Ι           | ST             | Yes | PWM Fault Inputs 1 and 2.                                                        |  |  |  |  |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup>      | Ι           | ST             | No  | PWM Fault Inputs 3 and 4.                                                        |  |  |  |  |

| FLT32 <sup>(1,3)</sup>                         | Ι           | ST             | No  | PWM Fault Input 32 (Class B Fault).                                              |  |  |  |  |

| DTCMP1-DTCMP3 <sup>(1)</sup>                   | Ι           | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                                   |  |  |  |  |

| PWM1L-PWM3L <sup>(1)</sup>                     | 0           | —              | No  | PWM Low Outputs 1 through 3.                                                     |  |  |  |  |

| PWM1H-PWM3H <sup>(1)</sup>                     | 0           | —              | No  | PWM High Outputs 1 through 3.                                                    |  |  |  |  |

| SYNCI1 <sup>(1)</sup>                          | Ι           | ST             |     | PWM Synchronization Input 1.                                                     |  |  |  |  |

| SYNCO1 <sup>(1)</sup>                          | 0           |                | Yes | PWM Synchronization Output 1.                                                    |  |  |  |  |

| INDX1 <sup>(1)</sup>                           | Ι           | ST             | Yes | Quadrature Encoder Index1 pulse input.                                           |  |  |  |  |

| HOME1 <sup>(1)</sup>                           | Ι           | ST             | Yes | Quadrature Encoder Home1 pulse input.                                            |  |  |  |  |

| QEA1 <sup>(1)</sup>                            | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                   |  |  |  |  |

| QEB1 <sup>(1)</sup>                            | ,           | ст             | Vee | external clock/gate input in Timer mode.                                         |  |  |  |  |

|                                                | Ι           | ST             | Yes |                                                                                  |  |  |  |  |

| CNTCMP1 <sup>(1)</sup>                         | 0           |                | Yes | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1. |  |  |  |  |

|                                                | 0           | <br>ompatible  | 162 |                                                                                  |  |  |  |  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

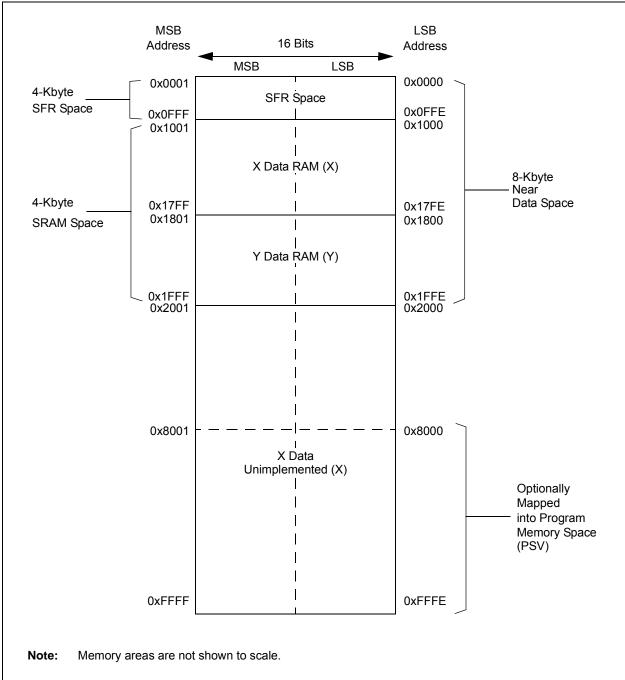

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC23        | 086E  |        | F      | PWM2IP<2:0 | )>      |         | Р      | WM1IP<2:   | 0>    |          |         | _           |         | —       | _      | -           |        | 4400          |

| IPC24        | 0870  |        | _      | _          | _       | -       | _      | _          | _     | _        | _       | _           | _       | _       | F      | WM3IP<2:0>  |        | 0004          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >       | -       |        | ICDIP<2:0  | >     | _        | _       | _           | _       | _       | _      | _           | _      | 4400          |

| IPC36        | 0888  |        | I      | PTG0IP<2:0 | )>      | -       | PT     | GWDTIP<    | 2:0>  | _        | P       | GSTEPIP<2:  | :0>     | _       | _      | _           | _      | 4440          |

| IPC37        | 088A  | _      | _      |            | —       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | •       | —       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | _       | _      | _          |       |          |         | _           |         | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      |            | —       | _       | _      | _          |       |          |         | DAE         | DOOVR   | _       | —      | _           |        | 0000          |

| INTCON4      | 08C6  | _      | _      |            | —       | _       | _      | _          | _     | _        |         | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | —      |            | —       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | JM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

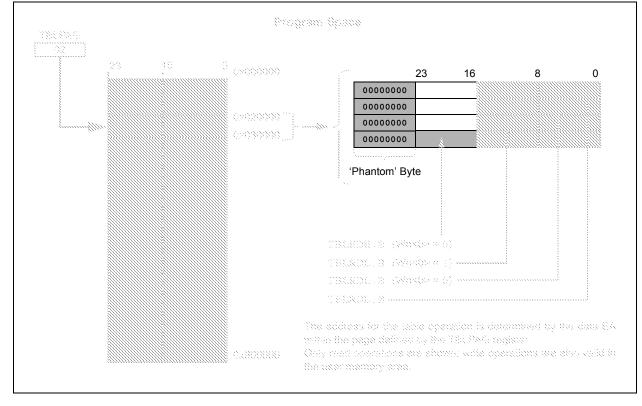

#### 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

# FIGURE 4-23: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# 9.3 Oscillator Control Registers

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0            | R-0                                                                | R-0                                  | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                |

|----------------|--------------------------------------------------------------------|--------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------|

| _              | COSC2                                                              | COSC1                                | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |

| bit 15         |                                                                    |                                      |                                    |                                    |                                    |                      | bit 8                |

| R/W-0          | R/W-0                                                              | R-0                                  | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                |

| CLKLOC         | CK IOLOCK                                                          | LOCK                                 |                                    | CF <sup>(3)</sup>                  |                                    |                      | OSWEN                |

| bit 7          |                                                                    |                                      |                                    |                                    |                                    |                      | bit (                |

| Legend:        |                                                                    | y = Value set                        | from Configur                      | ation bits on F                    | POR                                |                      |                      |

| R = Reada      | able bit                                                           | W = Writable                         | -                                  |                                    | mented bit, read                   | l as '0'             |                      |

| -n = Value     | at POR                                                             | '1' = Bit is se                      | t                                  | '0' = Bit is cle                   | eared                              | x = Bit is unkr      | nown                 |

| hit 1 <i>5</i> | Unimplemen                                                         | ted. Dood oo                         | 0'                                 |                                    |                                    |                      |                      |

| bit 15         | -                                                                  | ted: Read as                         |                                    |                                    |                                    |                      |                      |

| bit 14-12      |                                                                    | Current Oscill                       |                                    |                                    | ()                                 |                      |                      |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F   |                                    |                                    |                                    |                      |                      |

|                |                                                                    | ower RC Oscil                        |                                    |                                    |                                    |                      |                      |

|                | 100 = Reserv                                                       |                                      | ()                                 |                                    |                                    |                      |                      |

|                |                                                                    | y Oscillator (X                      |                                    | h PLL                              |                                    |                      |                      |

|                |                                                                    | y Oscillator (X                      |                                    |                                    |                                    |                      |                      |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F   |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |

| bit 11         |                                                                    | ted: Read as                         | ,                                  |                                    |                                    |                      |                      |

| bit 10-8       | NOSC<2:0>:                                                         | New Oscillato                        | r Selection bits                   | <sub>S</sub> (2)                   |                                    |                      |                      |

|                | 111 = Fast R                                                       | C Oscillator (F                      | RC) with Divid                     | le-by-n                            |                                    |                      |                      |

|                |                                                                    | C Oscillator (F                      |                                    | le-by-16                           |                                    |                      |                      |

|                |                                                                    | ower RC Oscil                        | ator (LPRC)                        |                                    |                                    |                      |                      |

|                | 100 = Reserv                                                       | /ed<br>y Oscillator (X               |                                    |                                    |                                    |                      |                      |

|                |                                                                    | y Oscillator (X                      |                                    | IFLL                               |                                    |                      |                      |

|                |                                                                    | C Oscillator (F                      |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |

|                |                                                                    | C Oscillator (F                      |                                    | ,                                  | ,                                  |                      |                      |

| bit 7          |                                                                    | Clock Lock Ena                       |                                    |                                    |                                    |                      |                      |

|                |                                                                    |                                      |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and       |

|                |                                                                    | figurations may<br>d PLL selectio    |                                    | ked, configurat                    | ions may be mo                     | odified              |                      |

| bit 6          |                                                                    | Lock Enable b                        |                                    | -                                  | -                                  |                      |                      |

|                | 1 = I/O lock is                                                    | s active                             |                                    |                                    |                                    |                      |                      |

|                | 0 = I/O lock is                                                    | s not active                         |                                    |                                    |                                    |                      |                      |

| bit 5          | LOCK: PLL L                                                        | ock Status bit                       | (read-only)                        |                                    |                                    |                      |                      |

|                |                                                                    | s that PLL is in<br>s that PLL is ou |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                      |

| Note 1:        | Writes to this regis                                               |                                      |                                    |                                    |                                    |                      | ʻdsPIC33/            |

| 2:             | Direct clock switch<br>This applies to cloo<br>mode as a transitio | es between ar<br>ck switches in      | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                      |

| 0              | This bit should only                                               |                                      |                                    |                                    |                                    |                      |                      |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

#### 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

#### **11.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Change Noti-      |

|-------|----------------------------------------------|

|       | fication pins should always be disabled      |

|       | when the port pin is configured as a digital |

|       | output.                                      |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, WO | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —            |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15       |              |                                                          |               |                   |                 |                 | bit 8 |

|              |              |                                                          |               |                   |                 |                 |       |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7        |              |                                                          |               |                   |                 |                 | bit C |

|              |              |                                                          |               |                   |                 |                 |       |

| Legend:      |              |                                                          |               |                   |                 |                 |       |

| R = Readab   | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0      | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

### REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      | —     |       |       | —          | —     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —      |       |       |       | U1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

#### REGISTER 11-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0' bit 6-0 U1RXR<6:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 . . . . . . . . . .

#### REGISTER 11-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| 0-0     | 0-0   | 0-0   | 0-0   | 0-0        | 0-0   | 0-0   | 0-0   |

|         | —     |       | _     | _          | —     | —     |       |

| bit 15  |       |       |       |            |       |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —       |       |       |       | U2RXR<6:0> | >     |       |       |

| bit 7   |       |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Legend: |       |       |       |            |       |       |       |

|         |       |       |       |            |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

<sup>0000000 =</sup> Input tied to Vss

# 16.3 PWMx Control Registers

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 | •                       |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit | t                     |  |

|-------------------|-----------------------------|----------------------------|-----------------------|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re  | nted bit, read as '0' |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown    |  |

| bit 15  | PTEN: PWMx Module Enable bit                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = PWMx module is enabled</li> <li>0 = PWMx module is disabled</li> </ul>                                                                     |

| bit 14  | Unimplemented: Read as '0'                                                                                                                              |

| bit 13  | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                            |

|         | <ul> <li>1 = PWMx time base halts in CPU Idle mode</li> <li>0 = PWMx time base runs in CPU Idle mode</li> </ul>                                         |

| bit 12  | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|         | <ul> <li>1 = Special event interrupt is pending</li> <li>0 = Special event interrupt is not pending</li> </ul>                                          |

| bit 11  | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|         | 1 = Special event interrupt is enabled                                                                                                                  |

|         | 0 = Special event interrupt is disabled                                                                                                                 |

| bit 10  | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Active Period register is updated immediately</li> <li>0 = Active Period register updates occur on PWMx cycle boundaries</li> </ul>        |

| bit 9   | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                       |

|         | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)                                                                                                     |

|         | 0 = SYNCI1/SYNCO1 is active-high                                                                                                                        |

| bit 8   | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                               |

|         | 1 = SYNCO1 output is enabled                                                                                                                            |

| L:1 7   | 0 = SYNCO1 output is disabled                                                                                                                           |

| bit 7   | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|         | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

|         |                                                                                                                                                         |

| Note 1: | These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user                                                   |

|         | application must program the period register with a value that is slightly larger than the expected period of                                           |

the external synchronization input signal.

2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| -                                                   |           |              |                         |              |                  |                  |                       |

|-----------------------------------------------------|-----------|--------------|-------------------------|--------------|------------------|------------------|-----------------------|

| R-0, HSC                                            | R-0, HSC  | U-0          | U-0                     | U-0          | R/C-0, HS        | R-0, HSC         | R-0, HSC              |

| ACKSTAT                                             | TRSTAT    | —            | —                       | —            | BCL              | GCSTAT           | ADD10                 |

| bit 15                                              |           |              |                         |              |                  |                  |                       |

|                                                     |           |              |                         |              |                  |                  |                       |

| R/C-0, HS                                           | R/C-0, HS | R-0, HSC     | R/C-0, HSC              | R/C-0, HSC   | R-0, HSC         | R-0, HSC         | R-0, HSC              |

| IWCOL                                               | I2COV     | D_A          | Р                       | S            | R_W              | RBF              | TBF                   |

| bit 7                                               |           |              |                         |              |                  |                  | bit 0                 |

|                                                     |           |              |                         |              |                  |                  |                       |

| Legend:                                             |           | C = Clearab  | le bit                  | HS = Hardwa  | re Settable bit  | HSC = Hardware S | ettable/Clearable bit |

| R = Readab                                          | le bit    | W = Writable | e bit                   | U = Unimplen | nented bit, read | as '0'           |                       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cle |           |              | ared x = Bit is unknown |              |                  |                  |                       |

#### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| hit 15    | ACKSTAT: Acknowledge Status bit (when operating as I <sup>2</sup> C™ master, applicable to master transmit operation)                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | 1 = NACK received from slave                                                                                                                   |

|           | 0 = ACK received from slave                                                                                                                    |

|           | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14    | <b>TRSTAT:</b> Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                        |

|           | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|           | 0 = Master transmit is not in progress                                                                                                         |

|           | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11 | Unimplemented: Read as '0'                                                                                                                     |

| bit 10    | BCL: Master Bus Collision Detect bit                                                                                                           |

|           | 1 = A bus collision has been detected during a master operation                                                                                |

|           | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| bit 9     | GCSTAT: General Call Status bit                                                                                                                |

| DIL 9     | 1 = General call address was received                                                                                                          |

|           | 0 = General call address was not received                                                                                                      |

|           | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8     | ADD10: 10-Bit Address Status bit                                                                                                               |

|           | 1 = 10-bit address was matched                                                                                                                 |

|           | 0 = 10-bit address was not matched                                                                                                             |

|           | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop detection.                               |

| bit 7     | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|           | 1 = An attempt to write to the I2CxTRN register failed because the I <sup>2</sup> C module is busy                                             |

|           | 1 = An attempt to write to the 120x million register laned because the 1-0 module is busy<br>0 = No collision                                  |

|           | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6     | I2COV: I2Cx Receive Overflow Flag bit                                                                                                          |

|           | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|           | 0 = No overflow                                                                                                                                |

|           | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5     | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|           | <ol> <li>I = Indicates that the last byte received was data</li> <li>I = Indicates that the last byte received was a device address</li> </ol> |

|           | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4     | P: Stop bit                                                                                                                                    |

|           | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|           | 0 = Stop bit was not detected last                                                                                                             |

|           | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                                                                     |

|           |                                                                                                                                                |

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | AMSK9 | AMSK8 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| AMSK7  | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7  |       |       |       |       |       |       | bit 0 |

#### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2CxMSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

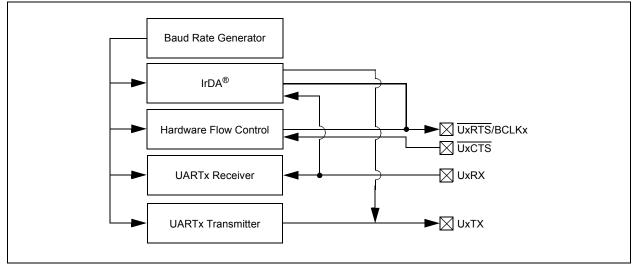

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

| U-0          | U-0                                          | R-0                        | R-0            | R-0                                | R-0   | R-0                | R-0   |  |  |  |  |

|--------------|----------------------------------------------|----------------------------|----------------|------------------------------------|-------|--------------------|-------|--|--|--|--|

| _            |                                              | FBP5                       | FBP4           | FBP3                               | FBP2  | FBP1               | FBP0  |  |  |  |  |

| bit 15       |                                              |                            |                |                                    |       |                    | bit 8 |  |  |  |  |

|              |                                              |                            |                |                                    |       |                    |       |  |  |  |  |

| U-0          | U-0                                          | R-0                        | R-0            | R-0                                | R-0   | R-0                | R-0   |  |  |  |  |

|              |                                              | FNRB5                      | FNRB4          | FNRB3                              | FNRB2 | FNRB1              | FNRB0 |  |  |  |  |

| bit 7        |                                              |                            |                |                                    |       |                    | bit ( |  |  |  |  |

| Legend:      |                                              |                            |                |                                    |       |                    |       |  |  |  |  |

| R = Readab   | le bit                                       | W = Writable               | bit            | U = Unimplemented bit, read as '0' |       |                    |       |  |  |  |  |

| -n = Value a | t POR                                        | '1' = Bit is set           |                | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |  |  |  |

|              |                                              |                            |                |                                    |       |                    |       |  |  |  |  |

| bit 15-14    | Unimpleme                                    | ented: Read as '           | 0'             |                                    |       |                    |       |  |  |  |  |

| bit 13-8     | FBP<5:0>: FIFO Buffer Pointer bits           |                            |                |                                    |       |                    |       |  |  |  |  |

|              | 011111 = RB31 buffer                         |                            |                |                                    |       |                    |       |  |  |  |  |

|              | 011110 = RB30 buffer                         |                            |                |                                    |       |                    |       |  |  |  |  |

|              | •                                            |                            |                |                                    |       |                    |       |  |  |  |  |

|              | •                                            |                            |                |                                    |       |                    |       |  |  |  |  |

|              | •<br>000001 = TRB1 buffer                    |                            |                |                                    |       |                    |       |  |  |  |  |

|              | 000001 = TRB1 buffer<br>000000 = TRB0 buffer |                            |                |                                    |       |                    |       |  |  |  |  |

| bit 7-6      | Unimpleme                                    | ented: Read as '           | 0'             |                                    |       |                    |       |  |  |  |  |

| bit 5-0      | FNRB<5:0                                     | >: FIFO Next Rea           | ad Buffer Poir | iter bits                          |       |                    |       |  |  |  |  |

|              | 011111 = RB31 buffer                         |                            |                |                                    |       |                    |       |  |  |  |  |

|              | 011110 <b>= F</b>                            | RB30 buffer                |                |                                    |       |                    |       |  |  |  |  |

|              | •                                            |                            |                |                                    |       |                    |       |  |  |  |  |

|              | •                                            |                            |                |                                    |       |                    |       |  |  |  |  |

|              | •                                            |                            |                |                                    |       |                    |       |  |  |  |  |

|              |                                              |                            |                |                                    |       |                    |       |  |  |  |  |

|              |                                              | FRB1 buffer<br>FRB0 buffer |                |                                    |       |                    |       |  |  |  |  |

#### REGISTER 21-5: CxFIFO: ECANx FIFO STATUS REGISTER

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |              |                                         |                                    |       |        |       |  |

|------------------------------------|-------|--------------|-----------------------------------------|------------------------------------|-------|--------|-------|--|

|                                    | R/W-0 | R/W-0        | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    | F7BF  | P<3:0>       |                                         |                                    | F6BF  | P<3:0> |       |  |

| bit 15                             |       |              |                                         |                                    |       |        | bit 8 |  |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    | F5BF  | °<3:0>       |                                         | F4BP<3:0>                          |       |        |       |  |

| bit 7                              |       |              |                                         |                                    |       |        | bit 0 |  |

| Legend:                            |       |              |                                         |                                    |       |        |       |  |

| R = Readable bi                    | t     | W = Writable | bit                                     | U = Unimplemented bit, read as '0' |       |        |       |  |

| -n = Value at POR '1' = Bit is set |       |              | '0' = Bit is cleared x = Bit is unknown |                                    |       | nown   |       |  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |

|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|----------------|--------|-------|--|

|               | F11BF                                              | P<3:0>                                                                                        |                                                | F10BP<3:0>                              |                |        |       |  |

| bit 15        |                                                    |                                                                                               |                                                |                                         |                |        | bit 8 |  |

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |

|               | F9BP                                               | 2<3:0>                                                                                        |                                                |                                         | F8B            | P<3:0> |       |  |

| bit 7         |                                                    |                                                                                               |                                                |                                         |                |        | bit 0 |  |

| Legend:       |                                                    |                                                                                               |                                                |                                         |                |        |       |  |

| R = Readabl   | le bit                                             | W = Writable                                                                                  | bit                                            | U = Unimplemented bit, read as '0'      |                |        |       |  |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                              |                                                | '0' = Bit is cleared x = Bit is unknown |                |        | nown  |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | RX Buffer Mar<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer<br>4                              |                |        |       |  |

| bit 11-8      | F10BP<3:0>                                         | : RX Buffer Ma                                                                                | sk for Filter 1                                | 0 bits (same val                        | ues as bits<1  | 5:12>) |       |  |

| bit 7-4       | F9BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 9 b                               | oits (same value                        | s as bits<15:1 | 2>)    |       |  |

| bit 3-0       | F8BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 8 k                               | oits (same value                        | s as bits<15:1 | 2>)    |       |  |

|               |                                                    |                                                                                               |                                                |                                         |                |        |       |  |

© 2011-2013 Microchip Technology Inc.

NOTES:

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                                  |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                    |  |  |

|--------------------|--------|------------------------------------------------------------------|------|-------------------------------------------------------|------|-------|--------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                                                   | Min. | Typ. <sup>(1)</sup>                                   | Max. | Units | Conditions         |  |  |

| OS50               | Fplli  | PLL Voltage Controlled Oscillator<br>(VCO) Input Frequency Range | 0.8  | —                                                     | 8.0  | MHz   | ECPLL, XTPLL modes |  |  |

| OS51               | Fvco   | On-Chip VCO System Frequency                                     | 120  | —                                                     | 340  | MHz   |                    |  |  |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                    | 0.9  | 1.5                                                   | 3.1  | ms    |                    |  |  |

| OS53               | DCLK   | CLKO Stability (Jitter) <sup>(2)</sup>                           | -3   | 0.5                                                   | 3    | %     |                    |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases, or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if Fosc = 120 MHz and the SPIx bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

#### TABLE 30-19: INTERNAL FRC ACCURACY