Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc504-i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

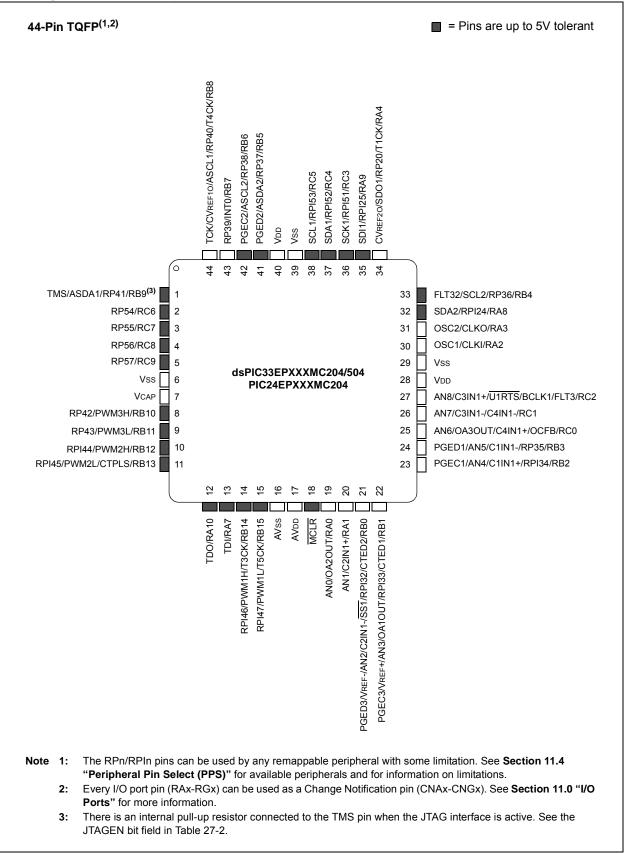

## Pin Diagrams (Continued)

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

|              |       |        |        | -      | -      | -          |        |       |       |       |       |       |       |            |       |       |       |               |

|--------------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0       | 06A0  | _      |        |        |        | NT1R<6:0>  |        |       |       |       | _     | _     | _     | _          |       | _     | _     | 0000          |

| RPINR1       | 06A2  |        | —      | —      | -      |            | -      |       |       | -     |       |       |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | -     | [2CKR<6:0> | >     |       |       | 0000          |

| RPINR7       | 06AE  | _      |        |        |        | IC2R<6:0>  |        |       |       | —     |       |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  | _      |        |        |        | IC4R<6:0>  |        |       |       | —     |       |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  | _      | _      | _      | —      | _          | _      | _     | _     | —     |       |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12      | 06B8  | _      |        |        | l      | =LT2R<6:0> |        |       |       | —     |       |       |       | FLT1R<6:0> | >     |       |       | 0000          |

| RPINR14      | 06BC  | _      |        |        | (      | QEB1R<6:0  | >      |       |       | —     |       |       | (     | QEA1R<6:0> | >     |       |       | 0000          |

| RPINR15      | 06BE  | _      |        |        | Н      | OME1R<6:0  | )>     |       |       | —     |       |       | I     | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  | _      | _      | _      | —      | —          | _      | _     | _     | —     |       |       | ι     | J1RXR<6:0> | >     |       |       | 0000          |

| RPINR19      | 06C6  | _      | _      | _      | _      | _          | _      | _     | _     | —     |       |       | ι     | J2RXR<6:0> | >     |       |       | 0000          |

| RPINR22      | 06CC  | _      |        | •      | S      | CK2INR<6:0 | )>     |       |       | _     |       |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      |        | _      | _          | _      | _     | _     | _     |       |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR37      | 06EA  | _      |        |        | S      | YNCI1R<6:0 | )>     |       |       | _     | _     | _     | _     | _          | _     | _     | _     | 0000          |

| RPINR38      | 06EC  | _      |        |        | DT     | CMP1R<6:   | 0>     |       |       | _     | _     | _     | _     |            | _     | _     | _     | 0000          |

| RPINR39      | 06EE  | _      |        |        | DT     | CMP3R<6:   | 0>     |       |       | —     |       |       | D     | CMP2R<6:   | 0>    |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | _      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND7        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | —     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | —      |        | _      | —      | PWM3MD | PWM2MD | PWM1MD | —      |       |       | _      | —      |        | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

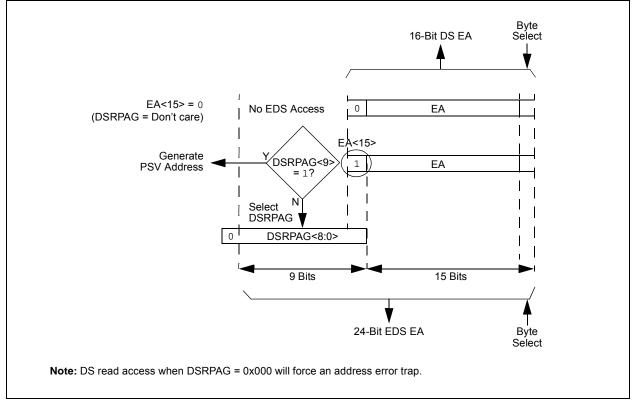

#### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

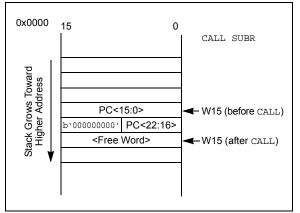

## 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack               |

|-------|---------------------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the hardware. |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-19 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-19. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

FIGURE 4-19: CALL STACK FRAME

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

## 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

## 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

|                   | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|-------------------|--------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|----------------------------|-----------------|-----------------|-----------------|

| _                 |                                            |                                                                            |                                              | FLT2R<6:0>                 |                 |                 |                 |

| bit 15            |                                            |                                                                            |                                              |                            |                 |                 | bit 8           |

|                   | <b>D</b> AALO                              | <b>D</b> 444 0                                                             | <b>D</b> 444 A                               | Date                       | <b>D</b> 444 0  | DAVA            | <b>D</b> # 44 0 |

| U-0               | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|                   |                                            |                                                                            |                                              | FLT1R<6:0>                 |                 |                 |                 |

| bit 7             |                                            |                                                                            |                                              |                            |                 |                 | bit C           |

| Legend:           |                                            |                                                                            |                                              |                            |                 |                 |                 |

| R = Readabl       | le bit                                     | W = Writable                                                               | bit                                          | U = Unimplen               | nented bit, rea | ad as '0'       |                 |

| -n = Value at     | t POR                                      | '1' = Bit is set                                                           |                                              | '0' = Bit is clea          | ared            | x = Bit is unkr | nown            |

| bit 14-8          | <b>FLT2R&lt;6:0&gt;</b><br>(see Table 11   | -2 for input pin                                                           | Fault 2 (FLT2)                               | ) to the Corresp<br>nbers) | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I                                                             | Fault 2 (FLT2)<br>selection nur<br>121       |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI                    | Fault 2 (FLT2)<br>selection nur<br>121<br>P1 |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8<br>bit 7 | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM | Fault 2 (FLT2<br>selection nur<br>121<br>P1  |                            | onding RPn F    | Pin bits        |                 |

NOTES:

NOTES:

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-1        | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 |

|--------------|-------|------------------|-------|--------------|------------------|----------|-------|

|              |       |                  | PTPE  | R<15:8>      |                  |          |       |

| bit 15       |       |                  |       |              |                  |          | bit 8 |

|              |       |                  |       |              |                  |          |       |

| R/W-1        | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-0            | R/W-0    | R/W-0 |

|              |       |                  | PTPE  | R<7:0>       |                  |          |       |

| bit 7        |       |                  |       |              |                  |          | bit 0 |

|              |       |                  |       |              |                  |          |       |

| Legend:      |       |                  |       |              |                  |          |       |

| R = Readable | bit   | W = Writable bit | t     | U = Unimpler | mented bit, read | l as '0' |       |

'0' = Bit is cleared

x = Bit is unknown

## REGISTER 16-3: PTPER: PWMx PRIMARY MASTER TIME BASE PERIOD REGISTER

bit 15-0 **PTPER<15:0>:** Primary Master Time Base (PMTMR) Period Value bits

'1' = Bit is set

#### REGISTER 16-4: SEVTCMP: PWMx PRIMARY SPECIAL EVENT COMPARE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | SEVTC | MP<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | SEVT  | CMP<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable bi  | t     | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 SEVTCMP<15:0>: Special Event Compare Count Value bits

-n = Value at POR

| REGISTER              | 16-7: PWMC                              | CONX: PWMX (                                                                       | CONTROL R                    | EGISTER          |                      |                      |                     |  |

|-----------------------|-----------------------------------------|------------------------------------------------------------------------------------|------------------------------|------------------|----------------------|----------------------|---------------------|--|

| HS/HC-0               | HS/HC-0                                 | HS/HC-0                                                                            | R/W-0                        | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |

| FLTSTAT <sup>(1</sup> | ) CLSTAT <sup>(1)</sup>                 | TRGSTAT                                                                            | FLTIEN                       | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |

| bit 15                |                                         |                                                                                    |                              |                  |                      |                      | bit 8               |  |

| R/W-0                 | R/W-0                                   | R/W-0                                                                              | U-0                          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |

| DTC1                  |                                         | DTCP <sup>(3)</sup>                                                                | 0-0                          | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |

|                       | DTC0                                    | DICPO                                                                              |                              | MIB3             | CAIM-, 7             | APRES <sup>67</sup>  | -                   |  |

| bit 7                 |                                         |                                                                                    |                              |                  |                      |                      | bit                 |  |

| Legend:               |                                         | HC = Hardware                                                                      | Clearable bit                | HS = Hardwa      | are Settable bit     |                      |                     |  |

| R = Readab            | le bit                                  | W = Writable b                                                                     | it                           | U = Unimple      | mented bit, rea      | d as '0'             |                     |  |

| -n = Value a          | t POR                                   | '1' = Bit is set                                                                   |                              | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |  |

| L:4 4 5               |                                         |                                                                                    |                              |                  |                      |                      |                     |  |

| bit 15                |                                         | ult Interrupt State<br>rrupt is pending                                            |                              |                  |                      |                      |                     |  |

|                       |                                         | interrupt is pending                                                               | ina                          |                  |                      |                      |                     |  |

|                       |                                         | ared by setting F                                                                  |                              |                  |                      |                      |                     |  |

| bit 14                | CLSTAT: Cur                             | rent-Limit Interru                                                                 | pt Status bit <sup>(1)</sup> |                  |                      |                      |                     |  |

|                       |                                         | mit interrupt is p                                                                 |                              |                  |                      |                      |                     |  |

|                       |                                         | nt-limit interrupt is                                                              | •                            |                  |                      |                      |                     |  |

| bit 13                |                                         | This bit is cleared by setting CLIEN = 0.<br>TRGSTAT: Trigger Interrupt Status bit |                              |                  |                      |                      |                     |  |

| DIL 15                | 1 = Trigger interrupt is pending        |                                                                                    |                              |                  |                      |                      |                     |  |

|                       |                                         | r interrupt is pen                                                                 |                              |                  |                      |                      |                     |  |

|                       | This bit is clea                        | ared by setting T                                                                  | RGIEN = 0.                   |                  |                      |                      |                     |  |

| bit 12                |                                         | t Interrupt Enabl                                                                  | e bit                        |                  |                      |                      |                     |  |

|                       |                                         | rrupt is enabled                                                                   | and the FLTC                 |                  | a d                  |                      |                     |  |

| bit 11                |                                         | rrupt is disabled<br>ent-Limit Interrup                                            |                              | TAT DILIS CIERT  | eu                   |                      |                     |  |

|                       |                                         | mit interrupt is e                                                                 |                              |                  |                      |                      |                     |  |

|                       |                                         | mit interrupt is di                                                                |                              | e CLSTAT bit is  | s cleared            |                      |                     |  |

| bit 10                | TRGIEN: Trig                            | ger Interrupt En                                                                   | able bit                     |                  |                      |                      |                     |  |

|                       |                                         | event generates                                                                    |                              |                  |                      |                      |                     |  |

|                       | ••                                      | vent interrupts ar                                                                 |                              | the TRGSTA       | F bit is cleared     |                      |                     |  |

| bit 9                 |                                         | dent Time Base                                                                     |                              |                  | () A                 |                      |                     |  |

|                       |                                         | register provides                                                                  |                              |                  | 0                    |                      |                     |  |

| bit 8                 |                                         | er Duty Cycle Re                                                                   |                              |                  | -                    |                      |                     |  |

|                       |                                         | ister provides du                                                                  | •                            |                  | WM generator         |                      |                     |  |

|                       |                                         | jister provides du                                                                 |                              |                  |                      | -                    |                     |  |

| Note 1: S             | oftware must clea                       | ar the interrupt s                                                                 | tatus here and               | in the corresp   | onding IFSx bit      | in the interrup      | t controller.       |  |

|                       | hese bits should                        | -                                                                                  |                              | -                | -                    |                      |                     |  |

|                       | DTC<1:0> = 11 fo                        |                                                                                    |                              | •                |                      |                      |                     |  |

|                       | The Independent T<br>CAM bit is ignored |                                                                                    | = 1) mode mus                | t be enabled to  | o use Center-Al      | igned mode. If       | ITB = 0, the        |  |

|                       | o operate in Exte                       |                                                                                    | et mode, the IT              | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |  |

## REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                | U-0   | U-0   | U-0                                | R/W-0  | R/W-0           | R/W-0  | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|--------|-----------------|--------|-------|

| —                                  | -     | —     | —                                  |        | LEB             | <11:8> |       |

| bit 15                             |       |       |                                    |        |                 |        | bit 8 |

|                                    |       |       |                                    |        |                 |        |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0  | R/W-0           | R/W-0  | R/W-0 |

|                                    |       |       | LEE                                | 3<7:0> |                 |        |       |

| bit 7                              |       |       |                                    |        |                 |        | bit 0 |

|                                    |       |       |                                    |        |                 |        |       |

| Legend:                            |       |       |                                    |        |                 |        |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimplemented bit, read as '0' |        |                 |        |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is clea                  | ared   | x = Bit is unkr | nown   |       |

## REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

| R/W-0         | R/W-0                          | R/W-0                                      | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |

|---------------|--------------------------------|--------------------------------------------|------------------|-------------------|------------------|-----------------|-------|--|--|

| QCAPEN        | FLTREN                         | QFDIV2                                     | QFDIV1           | QFDIV0            | OUTFNC1          | OUTFNC0         | SWPAB |  |  |

| bit 15        | •                              | ·                                          | •                | ÷                 |                  |                 | bit 8 |  |  |

| R/W-0         | R/W-0                          | R/W-0                                      | R/W-0            | R-x               | R-x              | R-x             | R-x   |  |  |

| HOMPOL        | IDXPOL                         | QEBPOL                                     | QEAPOL           | HOME              | INDEX            | QEB             | QEA   |  |  |

| bit 7         |                                |                                            |                  | TIOME             | INDEX            | QLD             | bit ( |  |  |

| Legend:       |                                |                                            |                  |                   |                  |                 |       |  |  |

| R = Readable  | e bit                          | W = Writable                               | bit              | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |

| -n = Value at |                                | '1' = Bit is set                           |                  | '0' = Bit is cle  |                  | x = Bit is unkn | own   |  |  |

|               |                                |                                            |                  |                   |                  |                 |       |  |  |

| bit 15        | QCAPEN: Q                      | EI Position Cou                            | nter Input Cap   | ture Enable bit   |                  |                 |       |  |  |

|               |                                | tch event trigge                           |                  |                   |                  |                 |       |  |  |

|               |                                | tch event does                             |                  | -                 |                  |                 |       |  |  |

| bit 14        |                                | Ax/QEBx/INDX                               | •                | tal Filter Enable | e bit            |                 |       |  |  |

|               |                                | digital filter is e<br>digital filter is d |                  | sed)              |                  |                 |       |  |  |

| bit 13-11     |                                | : QEAx/QEBx/II                             |                  | ,                 | Iter Clock Divid | le Select hits  |       |  |  |

|               | 111 = 1:128                    |                                            |                  | Bigital input i   |                  |                 |       |  |  |

|               | 110 = 1:64 cl                  |                                            |                  |                   |                  |                 |       |  |  |

|               | 101 = 1:32 clock divide        |                                            |                  |                   |                  |                 |       |  |  |

|               | 100 <b>= 1:16 cl</b>           |                                            |                  |                   |                  |                 |       |  |  |

|               | 011 = 1:8 clo                  |                                            |                  |                   |                  |                 |       |  |  |

|               | 010 = 1:4 clo<br>001 = 1:2 clo |                                            |                  |                   |                  |                 |       |  |  |

|               | 000 = 1:2 clo                  |                                            |                  |                   |                  |                 |       |  |  |

| bit 10-9      | OUTFNC<1:0                     | 0>: QEI Module                             | Output Functi    | on Mode Selec     | ct bits          |                 |       |  |  |

|               |                                | NCMPx pin goe                              | -                |                   |                  | GEC             |       |  |  |

|               |                                | NCMPx pin goe                              |                  |                   |                  |                 |       |  |  |

|               |                                | NCMPx pin goe                              | es high when P   | $OS1CNT \ge QE$   | IIGEC            |                 |       |  |  |

|               | 00 = Output i                  |                                            |                  |                   |                  |                 |       |  |  |

| bit 8         |                                | ap QEA and QE                              | •                |                   |                  |                 |       |  |  |

|               |                                | d QEBx are sw<br>d QEBx are not            |                  | quadrature dec    | oder logic       |                 |       |  |  |

| bit 7         |                                | OMEx Input Po                              |                  |                   |                  |                 |       |  |  |

|               | 1 = Input is in                |                                            |                  |                   |                  |                 |       |  |  |

| bit 6         |                                | Ot Inverted<br>DXx Input Polari            | tv Select hit    |                   |                  |                 |       |  |  |

|               | 1 = Input is in                | -                                          | ty Select bit    |                   |                  |                 |       |  |  |

|               | 0 = Input is n                 |                                            |                  |                   |                  |                 |       |  |  |

| bit 5         | -                              | EBx Input Polar                            | ity Select bit   |                   |                  |                 |       |  |  |

|               | 1 = Input is i                 | nverted                                    |                  |                   |                  |                 |       |  |  |

|               | 0 = Input is r                 | not inverted                               |                  |                   |                  |                 |       |  |  |

| bit 4         | QEAPOL: QE                     | EAx Input Polar                            | ity Select bit   |                   |                  |                 |       |  |  |

|               | 1 = Input is i                 | nverted                                    |                  |                   |                  |                 |       |  |  |

|               |                                |                                            |                  |                   |                  |                 |       |  |  |

|               | 0 = Input is r                 | not inverted                               |                  |                   |                  |                 |       |  |  |

| bit 3         |                                | not inverted<br>is of HOMEx In             | put Pin After Po | plarity Control   |                  |                 |       |  |  |

# REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER

### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

## 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                               | U-0              | R/W-x         | R/W-x                                   | R/W-x                              | R/W-x | R/W-x |  |  |  |

|---------------|-----------------------------------|------------------|---------------|-----------------------------------------|------------------------------------|-------|-------|--|--|--|

|               | —                                 |                  | SID10         | SID9                                    | SID8                               | SID7  | SID6  |  |  |  |

| bit 15        |                                   |                  |               |                                         |                                    |       | bit 8 |  |  |  |

| R/W-x         | R/W-x                             | R/W-x            | R/W-x         | R/W-x                                   | R/W-x                              | R/W-x | R/W-x |  |  |  |

| SID5          | SID4                              | SID3             | SID2          | SID1                                    | SID0                               | SRR   | IDE   |  |  |  |

| bit 7         |                                   | •                |               |                                         |                                    |       | bit 0 |  |  |  |

| Legend:       |                                   |                  |               |                                         |                                    |       |       |  |  |  |

| R = Readabl   | R = Readable bit W = Writable bit |                  |               |                                         | U = Unimplemented bit, read as '0' |       |       |  |  |  |

| -n = Value at | POR                               | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is unknown |                                    |       | nown  |  |  |  |

|               |                                   |                  |               |                                         |                                    |       |       |  |  |  |

| bit 15-13     | Unimplemen                        | ted: Read as '   | כי            |                                         |                                    |       |       |  |  |  |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S         | tandard Identifi | ier bits      |                                         |                                    |       |       |  |  |  |

| bit 1         | SRR: Substitu                     | ute Remote Re    | quest bit     |                                         |                                    |       |       |  |  |  |

|               | When IDE =                        | ):               |               |                                         |                                    |       |       |  |  |  |

|               | 1 = Message                       | will request rer | note transmis | ssion                                   |                                    |       |       |  |  |  |

|               | 0 = Normal m                      | lessage          |               |                                         |                                    |       |       |  |  |  |

|               | When IDE = 1                      | L <u>:</u>       |               |                                         |                                    |       |       |  |  |  |

|               | The SRR bit r                     | must be set to ' | 1'.           |                                         |                                    |       |       |  |  |  |

| bit 0         | IDE: Extende                      | d Identifier bit |               |                                         |                                    |       |       |  |  |  |

|               | 1 = Message                       | will transmit Ex | tended Ident  | ifier                                   |                                    |       |       |  |  |  |

|               |                                   | will transmit St |               |                                         |                                    |       |       |  |  |  |

|               |                                   |                  |               |                                         |                                    |       |       |  |  |  |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0                               | U-0                                | U-0   | U-0                                | R/W-x            | R/W-x | R/W-x           | R/W-x |

|-----------------------------------|------------------------------------|-------|------------------------------------|------------------|-------|-----------------|-------|

| —                                 | —                                  | —     |                                    | EID17            | EID16 | EID15           | EID14 |

| bit 15                            |                                    |       |                                    |                  |       |                 | bit 8 |

|                                   |                                    |       |                                    |                  |       |                 |       |

| R/W-x                             | R/W-x                              | R/W-x | R/W-x                              | R/W-x            | R/W-x | R/W-x           | R/W-x |

| EID13                             | EID12                              | EID11 | EID10                              | EID9             | EID8  | EID7            | EID6  |

| bit 7                             |                                    |       |                                    |                  |       |                 | bit 0 |

|                                   |                                    |       |                                    |                  |       |                 |       |

| Legend:                           |                                    |       |                                    |                  |       |                 |       |

| R = Readable bit W = Writable bit |                                    | bit   | U = Unimplemented bit, read as '0' |                  |       |                 |       |

| -n = Value at P                   | -n = Value at POR '1' = Bit is set |       |                                    | '0' = Bit is cle | ared  | x = Bit is unkr | nown  |

| L                                 |                                    |       |                                    |                  |       |                 |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

## REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit ( |

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

# REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|---------|-------|-------|-------|

|        |       |       | PTGHOL | D<15:8> |       |       |       |

| bit 15 |       |       |        |         |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0   | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------|-------|-------|----------|---------|-------|-------|-------|--|--|--|--|

|       |       |       | PTGHO    | LD<7:0> |       |       |       |  |  |  |  |

| bit 7 |       |       | bit 7 bi |         |       |       |       |  |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

NOTES:

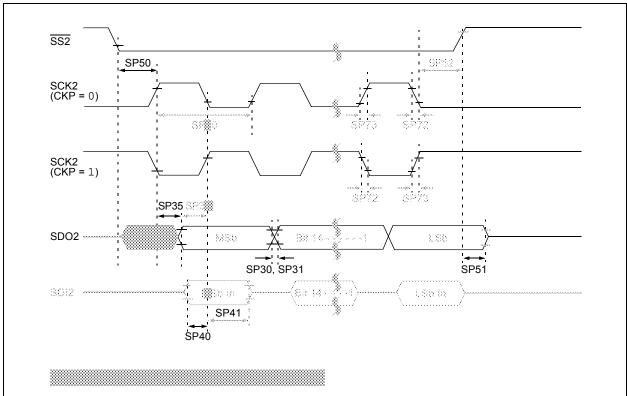

#### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS