Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 256KB (85.5K x 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

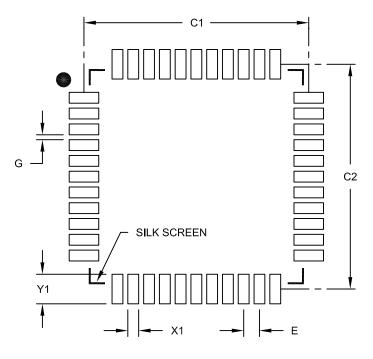

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 44-VTLA (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc504t-i-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |  |  |  |  |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AN0-AN15                                       | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |  |  |  |  |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |  |  |  |  |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |  |  |  |  |

| OSC1                                           | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |  |  |  |  |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |  |  |  |  |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |  |  |  |  |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |  |  |  |  |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |  |  |  |  |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |  |  |  |  |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |  |  |  |  |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |  |  |  |  |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |  |  |  |  |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |  |  |  |  |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |  |  |  |  |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |  |  |  |  |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |  |  |  |  |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |  |  |  |  |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |  |  |  |  |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |  |  |  |  |

| U1RTS                                          | 0                   |                         | No               | 5                                                                                                                                                                                  |  |  |  |  |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |  |  |  |  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |  |  |  |  |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |  |  |  |  |

### TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

# TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15                                       | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4               | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|----------------------------------------------|--------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|---------------------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN                                        | _      | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |                     | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _                                            | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |                     | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244  | FRMEN                                        | SPIFSD | FRMPOL  | _      | _      | -      | _          | _            | —           | _          | _      | _                   | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |                                              |        |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |                     |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN                                        | _      | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |                     | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _                                            | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  | SPRE<2:0> PPRE<1:0> |            |       | 0000   |        |               |

| SPI2CON2 | 0264  | FRMEN                                        | SPIFSD | FRMPOL  | _      | _      | -      | _          | _            | —           | _          | _      | _                   | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  | 68 SPI2 Transmit and Receive Buffer Register |        |         |        |        |        |            |              | 0000        |            |        |                     |            |       |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

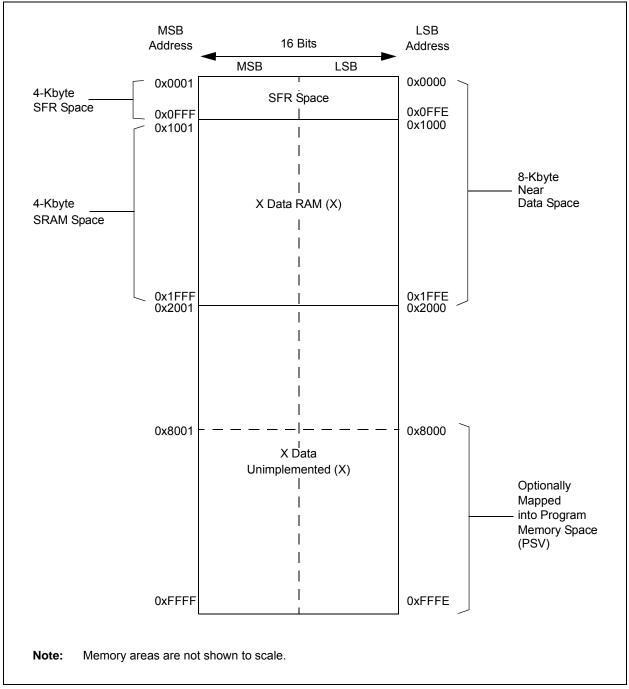

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

#### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

#### EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

DS70000657H-page 154

#### © 2011-2013 Microchip Technology Inc.

# FIGURE 9-2: PLL BLOCK DIAGRAM

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

#### 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# 9.3 Oscillator Control Registers

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0            | R-0                                        | R-0                                                                                                | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                                                                                                                                                                |  |  |  |  |  |  |  |  |

|----------------|--------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| _              | COSC2                                      | COSC1                                                                                              | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup>                                                                                                                                                 |  |  |  |  |  |  |  |  |

| bit 15         |                                            |                                                                                                    |                                    |                                    |                                    |                      | bit 8                                                                                                                                                                |  |  |  |  |  |  |  |  |

| R/W-0          | R/W-0                                      | R-0                                                                                                | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                                                                                                                                                                |  |  |  |  |  |  |  |  |

| CLKLOC         | CK IOLOCK                                  | LOCK                                                                                               |                                    | CF <sup>(3)</sup>                  |                                    |                      | OSWEN                                                                                                                                                                |  |  |  |  |  |  |  |  |

| bit 7          |                                            |                                                                                                    |                                    |                                    |                                    |                      | bit (                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Legend:        |                                            | y = Value set                                                                                      | from Configur                      | ation bits on F                    | POR                                |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| R = Reada      | able bit                                   | W = Writable                                                                                       | -                                  |                                    | mented bit, read                   | l as '0'             |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| -n = Value     | at POR                                     | '1' = Bit is se                                                                                    | t                                  | '0' = Bit is cle                   | eared                              | x = Bit is unkr      | nown                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| hit 1 <i>5</i> | Unimplemen                                 | ted. Dood oo                                                                                       | 0'                                 |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| bit 15         | -                                          | ted: Read as                                                                                       |                                    |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| bit 14-12      |                                            | Current Oscill                                                                                     |                                    |                                    | /)                                 |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | C Oscillator (F<br>C Oscillator (F                                                                 |                                    |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | ower RC Oscil                                                                                      |                                    |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                | 100 = Reserv                               |                                                                                                    | ()                                 |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | y Oscillator (X                                                                                    |                                    | h PLL                              |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | y Oscillator (X                                                                                    |                                    |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | 001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |                                    |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| bit 11         |                                            | Unimplemented: Read as '0'                                                                         |                                    |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| bit 10-8       | NOSC<2:0>:                                 | New Oscillato                                                                                      | r Selection bits                   | <sub>S</sub> (2)                   |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                | 111 = Fast R                               | C Oscillator (F                                                                                    | RC) with Divid                     | le-by-n                            |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | C Oscillator (F                                                                                    |                                    | le-by-16                           |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | ower RC Oscil                                                                                      | ator (LPRC)                        |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                | 100 = Reserv                               | /ed<br>y Oscillator (X                                                                             |                                    |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | y Oscillator (X                                                                                    |                                    | IFLL                               |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | C Oscillator (F                                                                                    |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | C Oscillator (F                                                                                    |                                    | ,                                  | ,                                  |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| bit 7          |                                            | Clock Lock Ena                                                                                     |                                    |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            |                                                                                                    |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and                                                                                                                                                       |  |  |  |  |  |  |  |  |

|                |                                            | figurations may<br>d PLL selectio                                                                  |                                    | ked, configurat                    | ions may be mo                     | odified              |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| bit 6          |                                            | Lock Enable b                                                                                      |                                    | -                                  | -                                  |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                | 1 = I/O lock is                            | s active                                                                                           |                                    |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                | 0 = I/O lock is                            | s not active                                                                                       |                                    |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| bit 5          | LOCK: PLL L                                | ock Status bit                                                                                     | (read-only)                        |                                    |                                    |                      |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                |                                            | s that PLL is in<br>s that PLL is ou                                                               |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Note 1:        | Writes to this regis                       |                                                                                                    |                                    |                                    |                                    |                      | ʻdsPIC33/                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 2:             | Direct clock switch<br>This applies to clo | es between ar<br>ck switches in                                                                    | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| 0              |                                            |                                                                                                    |                                    |                                    |                                    |                      | as a transitional clock source between the two PLL modes.<br>t should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an |  |  |  |  |  |  |  |  |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

NOTES:

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-1        | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 |

|--------------|-------|------------------|-------|--------------|------------------|----------|-------|

|              |       |                  | PTPE  | R<15:8>      |                  |          |       |

| bit 15       |       |                  |       |              |                  |          | bit 8 |

|              |       |                  |       |              |                  |          |       |

| R/W-1        | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-0            | R/W-0    | R/W-0 |

|              |       |                  | PTPE  | R<7:0>       |                  |          |       |

| bit 7        |       |                  |       |              |                  |          | bit 0 |

|              |       |                  |       |              |                  |          |       |

| Legend:      |       |                  |       |              |                  |          |       |

| R = Readable | bit   | W = Writable bit | t     | U = Unimpler | mented bit, read | l as '0' |       |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 16-3: PTPER: PWMx PRIMARY MASTER TIME BASE PERIOD REGISTER

bit 15-0 **PTPER<15:0>:** Primary Master Time Base (PMTMR) Period Value bits

'1' = Bit is set

#### REGISTER 16-4: SEVTCMP: PWMx PRIMARY SPECIAL EVENT COMPARE REGISTER

| R/W-0                                                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0    | R/W-0 | R/W-0 |

|-------------------------------------------------------------------------|-------|-------|-------|----------|----------|-------|-------|

|                                                                         |       |       | SEVTC | MP<15:8> |          |       |       |

| bit 15                                                                  |       |       |       |          |          |       | bit 8 |

|                                                                         |       |       |       |          |          |       |       |

| R/W-0                                                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0    | R/W-0 | R/W-0 |

|                                                                         |       |       | SEVT  | CMP<7:0> |          |       |       |

| bit 7                                                                   |       |       |       |          |          |       | bit 0 |

|                                                                         |       |       |       |          |          |       |       |

| Legend:                                                                 |       |       |       |          |          |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'    |       |       |       |          | d as '0' |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unki |       |       |       | nown     |          |       |       |

bit 15-0 SEVTCMP<15:0>: Special Event Compare Count Value bits

-n = Value at POR

### REGISTER 17-4: POSICNTH: POSITION COUNTER 1 HIGH WORD REGISTER

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x |       |       | x = Bit is unkr | nown                               |       |       |       |  |  |

|-----------------------------------------------------------|-------|-------|-----------------|------------------------------------|-------|-------|-------|--|--|

| R = Readable bit W = Writable bit                         |       |       | it              | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| Legend:                                                   |       |       |                 |                                    |       |       |       |  |  |

|                                                           |       |       |                 |                                    |       |       |       |  |  |

| bit 7                                                     |       |       |                 |                                    |       |       | bit 0 |  |  |

|                                                           |       |       | POSCN           | IT<23:16>                          |       |       |       |  |  |

| R/W-0                                                     | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

| bit 15                                                    |       |       |                 |                                    |       |       | bit 8 |  |  |

|                                                           |       |       | POSCN           | IT<31:24>                          |       |       |       |  |  |

| R/W-0                                                     | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

bit 15-0 **POSCNT<31:16>:** High Word Used to Form 32-Bit Position Counter Register (POS1CNT) bits

#### REGISTER 17-5: POS1CNTL: POSITION COUNTER 1 LOW WORD REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| POSCNT<15:8> |       |       |       |       |       |       |       |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |

|              |       |       |       |       |       |       |       |  |

| R/W-0       | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------------|-------|-------|-------|-------|-------|-------|--|--|

| POSCNT<7:0> |             |       |       |       |       |       |       |  |  |

| bit 7       | bit 7 bit 0 |       |       |       |       |       |       |  |  |

| Legend:                                                              |                  |                      |                    |  |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-0 POSCNT<15:0>: Low Word Used to Form 32-Bit Position Counter Register (POS1CNT) bits

#### REGISTER 17-6: POS1HLD: POSITION COUNTER 1 HOLD REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0    | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|----------|-----------------|-------|-------|

|                                    |       |       | POSHL                              | _D<15:8> |                 |       |       |

| bit 15                             |       |       |                                    |          |                 |       | bit 8 |

|                                    |       |       |                                    |          |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0    | R/W-0           | R/W-0 | R/W-0 |

|                                    |       |       | POSH                               | LD<7:0>  |                 |       |       |

| bit 7                              |       |       |                                    |          |                 |       | bit 0 |

|                                    |       |       |                                    |          |                 |       |       |

| Legend:                            |       |       |                                    |          |                 |       |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimplemented bit, read as '0' |          |                 |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x =           |          | x = Bit is unkr | nown  |       |

bit 15-0 **POSHLD<15:0>:** Hold Register for Reading and Writing POS1CNTH bits

| R-0, HSC                           | R-0, HSC                          | U-0               | U-0                                | U-0                | R/C-0, HS       | R-0, HSC                              | R-0, HSC |  |

|------------------------------------|-----------------------------------|-------------------|------------------------------------|--------------------|-----------------|---------------------------------------|----------|--|

| ACKSTAT                            | TRSTAT                            | _                 | _                                  | —                  | BCL             | GCSTAT                                | ADD10    |  |

| bit 15                             |                                   |                   |                                    |                    |                 |                                       | bit 8    |  |

|                                    |                                   |                   |                                    |                    |                 |                                       |          |  |

| R/C-0, HS                          | R/C-0, HS                         | R-0, HSC          | R/C-0, HSC                         | R/C-0, HSC         | R-0, HSC        | R-0, HSC                              | R-0, HSC |  |

| IWCOL                              | I2COV                             | D_A               | Р                                  | S                  | R_W             | RBF                                   | TBF      |  |

| bit 7                              |                                   |                   |                                    |                    |                 |                                       | bit 0    |  |

|                                    |                                   |                   |                                    |                    |                 |                                       |          |  |

| Legend:                            |                                   | C = Clearab       | le bit                             | HS = Hardwa        | re Settable bit | HSC = Hardware Settable/Clearable bit |          |  |

| R = Readabl                        | R = Readable bit W = Writable bit |                   | U = Unimplemented bit, read as '0' |                    |                 |                                       |          |  |

| -n = Value at POR '1' = Bit is set |                                   | '0' = Bit is clea | ared                               | x = Bit is unknown |                 |                                       |          |  |

#### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

| U-0                     | U-0                            | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |

|-------------------------|--------------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|

| _                       | _                              |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |

| bit 15                  | <b>I</b>                       | •                                  |         |                  |                 |                 | bit 8   |

|                         |                                |                                    |         |                  |                 |                 |         |

| U-0                     | R-1                            | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |

| _                       | ICODE6                         | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |

| bit 7                   |                                |                                    |         |                  |                 |                 | bit     |

| Logondi                 |                                |                                    |         |                  |                 |                 |         |

| Legend:<br>R = Readable | - hit                          |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |

| -n = Value at           |                                | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |

| -n = value at           | POR                            | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |

| bit 15-13               | Unimplemen                     | ted: Read as '                     | 0'      |                  |                 |                 |         |

| bit 12-8                | =                              | Filter Hit Num                     |         |                  |                 |                 |         |

|                         |                                | 1 = Reserved                       |         |                  |                 |                 |         |

|                         | 01111 <b>= Filte</b>           | r 15                               |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         |                                | - 1                                |         |                  |                 |                 |         |

|                         | 00001 = Filte<br>00000 = Filte |                                    |         |                  |                 |                 |         |

| bit 7                   |                                | ted: Read as '                     | 0'      |                  |                 |                 |         |

| bit 6-0                 | -                              | Interrupt Flag                     |         |                  |                 |                 |         |

|                         |                                | 11111 = Rese                       |         |                  |                 |                 |         |

|                         |                                | IFO almost full                    |         |                  |                 |                 |         |

|                         |                                | eceiver overflo                    |         |                  |                 |                 |         |

|                         | 1000010 = K<br>1000001 = E     | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |

|                         | 1000000 = N                    |                                    |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         |                                | 11111 = Rese                       |         |                  |                 |                 |         |

|                         | •                              | B15 buffer inte                    | inupt   |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         | 0001001 <b>= R</b>             | B9 buffer inter                    | rupt    |                  |                 |                 |         |

|                         |                                | B8 buffer inter                    |         |                  |                 |                 |         |

|                         |                                | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |

|                         |                                | RB5 buffer inte                    |         |                  |                 |                 |         |

|                         |                                | RB4 buffer inte                    |         |                  |                 |                 |         |

|                         | 0000011 <b>= T</b>             | RB3 buffer inte                    | errupt  |                  |                 |                 |         |

|                         |                                |                                    |         |                  |                 |                 |         |

|                         |                                | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |

### REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

# 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

| U-0          | U-0                                                                                                | U-0                                                                                                                                               | U-0                                                                                                       | U-0                                                                                                          | U-0                               | U-0      | R/W-0   |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------|----------|---------|--|--|--|--|

| —            | _                                                                                                  | —                                                                                                                                                 |                                                                                                           | —                                                                                                            | _                                 | —        | ADDMAEN |  |  |  |  |

| bit 15       |                                                                                                    |                                                                                                                                                   |                                                                                                           |                                                                                                              |                                   |          | bit 8   |  |  |  |  |

| U-0          | U-0                                                                                                | U-0                                                                                                                                               | U-0                                                                                                       | U-0                                                                                                          | R/W-0                             | R/W-0    | R/W-0   |  |  |  |  |

| 0-0          | 0-0                                                                                                | 0-0                                                                                                                                               | 0-0                                                                                                       | 0-0                                                                                                          |                                   |          | -       |  |  |  |  |

|              | —                                                                                                  | —                                                                                                                                                 | _                                                                                                         | —                                                                                                            | DMABL2                            | DMABL1   | DMABL0  |  |  |  |  |

| bit 7        |                                                                                                    |                                                                                                                                                   |                                                                                                           |                                                                                                              |                                   |          | bit 0   |  |  |  |  |

| Legend:      |                                                                                                    |                                                                                                                                                   |                                                                                                           |                                                                                                              |                                   |          |         |  |  |  |  |

| R = Readab   | le bit                                                                                             | W = Writable b                                                                                                                                    | bit                                                                                                       | U = Unimpler                                                                                                 | mented bit, read                  | 1 as '0' |         |  |  |  |  |

| -n = Value a | t POR                                                                                              | '1' = Bit is set                                                                                                                                  |                                                                                                           | '0' = Bit is cle                                                                                             | nown                              |          |         |  |  |  |  |

|              |                                                                                                    |                                                                                                                                                   |                                                                                                           |                                                                                                              |                                   |          |         |  |  |  |  |

| bit 15-9     | Unimplemen                                                                                         | ted: Read as '0                                                                                                                                   | 3                                                                                                         |                                                                                                              |                                   |          |         |  |  |  |  |

| bit 8        | ADDMAEN: A                                                                                         | ADDMAEN: ADC1 DMA Enable bit                                                                                                                      |                                                                                                           |                                                                                                              |                                   |          |         |  |  |  |  |

|              |                                                                                                    |                                                                                                                                                   |                                                                                                           | 0                                                                                                            | ster for transfer<br>ADC1BUFF reg | 0        |         |  |  |  |  |

| bit 7-3      | Unimplemen                                                                                         | ted: Read as '0                                                                                                                                   | ,                                                                                                         |                                                                                                              |                                   |          |         |  |  |  |  |

| bit 2-0      | DMABL<2:0>                                                                                         | Selects Numb                                                                                                                                      | per of DMA B                                                                                              | uffer Locations                                                                                              | per Analog Inpu                   | ut bits  |         |  |  |  |  |

|              | 110 = Allocat<br>101 = Allocat<br>100 = Allocat<br>011 = Allocat<br>010 = Allocat<br>001 = Allocat | es 128 words of<br>es 64 words of<br>es 32 words of<br>es 16 words of<br>es 8 words of b<br>es 4 words of b<br>es 2 words of b<br>es 1 word of bu | buffer to each<br>buffer to each<br>buffer to each<br>uffer to each<br>uffer to each a<br>uffer to each a | analog input<br>analog input<br>analog input<br>analog input<br>analog input<br>analog input<br>analog input |                                   |          |         |  |  |  |  |

### REGISTER 23-4: AD1CON4: ADC1 CONTROL REGISTER 4

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

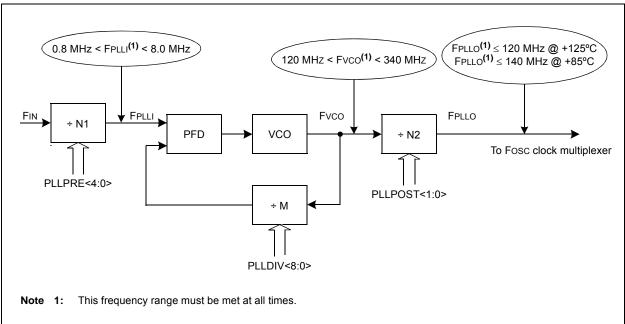

# 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.