Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc506-h-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

## 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2 | SFA: Stack Frame Active Status bit                                                        |

|-------|-------------------------------------------------------------------------------------------|

|       | 1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and |

|       | DSWPAG values                                                                             |

|       | 0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space              |

| hit 1 | PND: Dounding Mode Select hit(1)                                                          |

- bit 1 **RND:** Rounding Mode Select bit<sup>(1)</sup>

- 1 = Biased (conventional) rounding is enabled

- 0 = Unbiased (convergent) rounding is enabled

bit 0 IF: Integer or Fractional Multiplier Mode Select bit<sup>(1)</sup> 1 = Integer mode is enabled for DSP multiply 0 = Fractional mode is enabled for DSP multiply

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

- **2:** This bit is always read as '0'.

- 3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

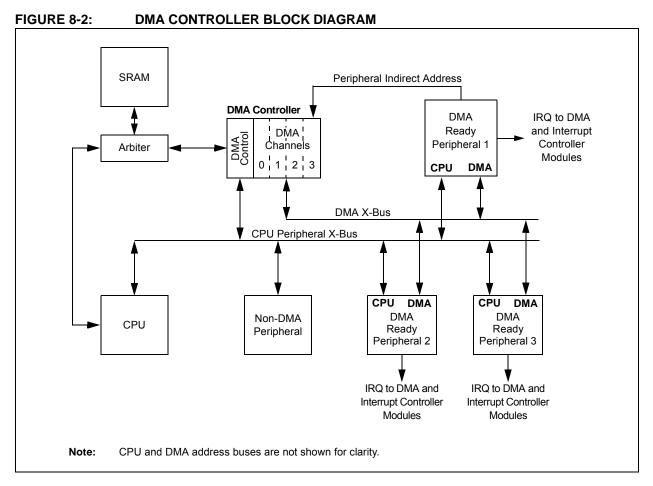

## 8.1 DMA Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

## 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 8.2 DMAC Registers

Each DMAC Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/S-0                | U-0                                                                                 | U-0              | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------|------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| FORCE <sup>(1)</sup> |                                                                                     | _                | _                     | —                |                  | _               |         |  |  |  |  |

| bit 15               |                                                                                     |                  |                       |                  |                  |                 | bit 8   |  |  |  |  |

|                      |                                                                                     |                  |                       |                  |                  |                 |         |  |  |  |  |

| R/W-0                | R/W-0                                                                               | R/W-0            | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

| IRQSEL7              | IRQSEL6                                                                             | IRQSEL5          | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |  |  |

| bit 7                |                                                                                     |                  |                       |                  |                  |                 | bit     |  |  |  |  |

| Legend:              |                                                                                     | S = Settable b   | oit                   |                  |                  |                 |         |  |  |  |  |

| R = Readable         | bit                                                                                 | W = Writable     | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value at F      | POR                                                                                 | '1' = Bit is set |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |

|                      |                                                                                     |                  |                       |                  |                  |                 |         |  |  |  |  |

| bit 15               | FORCE: Force                                                                        | e DMA Transfe    | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |  |  |

|                      | 1 = Forces a                                                                        | single DMA tra   | insfer (Manua         | l mode)          |                  |                 |         |  |  |  |  |

|                      | 0 = Automatic DMA transfer initiation by DMA request                                |                  |                       |                  |                  |                 |         |  |  |  |  |

| bit 14-8             | Unimplemen                                                                          | ted: Read as 'd  | )'                    |                  |                  |                 |         |  |  |  |  |

| bit 7-0              | IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits                                  |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 01000110 = ECAN1 – TX Data Request <sup>(2)</sup>                                   |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00100110 = IC4 – Input Capture 4                                                    |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00100101 = IC3 – Input Capture 3<br>00100010 = ECAN1 – RX Data Ready <sup>(2)</sup> |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     | SPI2 Transfer I  | -                     |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     | UART2TX – UA     |                       | itter            |                  |                 |         |  |  |  |  |

|                      |                                                                                     |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011110 = UART2RX – UART2 Receiver<br>00011100 = TMR5 – Timer5                     |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011011 = TMR4 – Timer4                                                            |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011010 = OC4 – Output Compare 4                                                   |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011001 = OC3 – Output Compare 3                                                   |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001101 = ADC1 – ADC1 Convert done                                                 |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001100 = UART1TX – UART1 Transmitter                                              |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001011 = UART1RX – UART1 Receiver                                                 |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001010 = SPI1 – Transfer Done<br>00001000 = TMR3 – Timer3                         |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001000 = TMR3 - TIMer3<br>00000111 = TMR2 - Timer2                                |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00000111 - 10002 - 100012<br>00000110 = OC2 - Output Compare 2                      |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     | IC2 – Input Ca   |                       |                  |                  |                 |         |  |  |  |  |

|                      | 0000010 =                                                                           | OC1 – Output (   | Compare 1             |                  |                  |                 |         |  |  |  |  |

|                      |                                                                                     | IC1 – Input Ca   |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00000000 =                                                                          | INT0 – Externa   | I Interrupt 0         |                  |                  |                 |         |  |  |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

## 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

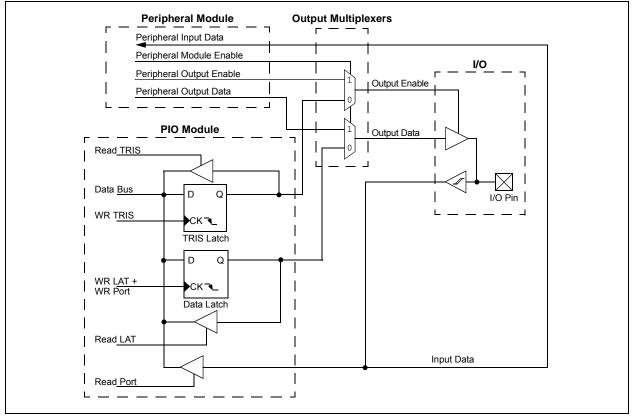

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment | Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment |

|--------------------------------------------------|------------------|----------------|--------------------------------------------------|------------------|----------------|

| 010 1000                                         | I/O              | RP40           | 101 0101                                         | —                | _              |

| 010 1001                                         | I/O              | RP41           | 101 0110                                         | —                | —              |

| 010 1010                                         | I/O              | RP42           | 101 0111                                         | —                | —              |

| 010 1011                                         | I/O              | RP43           | 101 1000                                         |                  | —              |

| 010 1100                                         | I                | RPI44          | 101 1001                                         |                  | —              |

| 101 1010                                         | —                | _              | 110 1101                                         | —                | _              |

| 101 1011                                         | —                | —              | 110 1110                                         |                  | —              |

| 101 1100                                         | —                | —              | 110 1111                                         |                  | —              |

| 101 1101                                         | —                | _              | 111 0000                                         | —                | _              |

| 101 1110                                         | 1                | RPI94          | 111 0001                                         | —                | _              |

| 101 1111                                         | I                | RP195          | 111 0010                                         |                  | —              |

| 110 0000                                         | I                | RPI96          | 111 0011                                         | —                | —              |

| 110 0001                                         | I/O              | RP97           | 111 0100                                         |                  | —              |

| 110 0010                                         | —                | —              | 111 0101                                         |                  | —              |

| 110 0011                                         | —                | —              | 111 0110                                         | I/O              | RP118          |

| 110 0100                                         | —                | —              | 111 0111                                         | Ι                | RPI119         |

| 110 0101                                         | —                | —              | 111 1000                                         | I/O              | RP120          |

| 110 0110                                         | _                |                | 111 1001                                         | I                | RPI121         |

| 110 0111                                         |                  |                | 111 1010                                         | —                |                |

| 110 1000                                         | —                | _              | 111 1011                                         | —                | _              |

| 110 1001                                         | —                |                | 111 1100                                         | —                |                |

| 110 1010                                         |                  |                | 111 1101                                         | —                |                |

| 110 1011                                         | —                | _              | 111 1110                                         | —                |                |

| 110 1100                                         | —                | _              | 111 1111                                         | _                |                |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

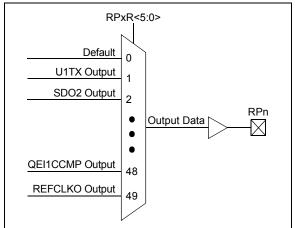

#### 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

#### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

#### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|--------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|

| —            |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |

| bit 15       |                                          |                                                                              |               |                   |               |                 | bit 8  |

|              |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|              |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |

| bit 7        |                                          |                                                                              |               |                   |               |                 | bit 0  |

|              |                                          |                                                                              |               |                   |               |                 |        |

| Legend:      |                                          |                                                                              |               |                   |               |                 |        |

| R = Readab   |                                          | W = Writable                                                                 |               | U = Unimplen      |               |                 |        |

| -n = Value a | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |

|              |                                          | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss                     | P1            |                   |               |                 |        |

| bit 7        | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |

| bit 6-0      | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |

## REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|-------------------|-------|-----------------|-------|

|                                   |       |                  | TRGC                               | MP<15:8>          |       |                 |       |

| bit 15                            |       |                  |                                    |                   |       |                 | bit 8 |

|                                   |       |                  |                                    |                   |       |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                                   |       |                  | TRGC                               | MP<7:0>           |       |                 |       |

| bit 7                             |       |                  |                                    |                   |       |                 | bit 0 |

| Legend:                           |       |                  |                                    |                   |       |                 |       |

| R = Readable bit W = Writable bit |       | oit              | U = Unimplemented bit, read as '0' |                   |       |                 |       |

| -n = Value at P                   | OR    | '1' = Bit is set |                                    | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |

## REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

NOTES:

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-17: CxRXFnEID: ECANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 21-18: CxFMSKSEL1: ECANx FILTER 7-0 MASK SELECTION REGISTER 1

| R/W-0         | R/W-0                                                                  | R/W-0                                                        | R/W-0            | R/W-0             | R/W-0            | R/W-0              | R/W-0  |  |

|---------------|------------------------------------------------------------------------|--------------------------------------------------------------|------------------|-------------------|------------------|--------------------|--------|--|

| F7MSK<1:0>    |                                                                        | F6MSK<1:0>                                                   |                  | F5MSK<1:0>        |                  | F4MSK<1:0>         |        |  |

| bit 15        |                                                                        | ·                                                            |                  |                   |                  |                    | bit    |  |

| R/W-0         | R/W-0                                                                  | R/W-0                                                        | R/W-0            | R/W-0             | R/W-0            | R/W-0              | R/W-0  |  |

| F3MS          | SK<1:0>                                                                | F2MS                                                         | K<1:0>           | F1MS              | K<1:0>           | F0MS               | K<1:0> |  |

| bit 7         |                                                                        |                                                              |                  |                   |                  |                    | bit (  |  |

| Legend:       |                                                                        |                                                              |                  |                   |                  |                    |        |  |

| R = Readable  | e bit                                                                  | W = Writable                                                 | bit              | U = Unimplen      | nented bit, read | d as '0'           |        |  |

| -n = Value at | POR                                                                    | '1' = Bit is set                                             |                  | '0' = Bit is clea | ared             | x = Bit is unknown |        |  |

|               | 01 = Accept                                                            | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg | gisters contain  | mask              |                  |                    |        |  |

| bit 13-12     | F6MSK<1:0                                                              | >: Mask Source                                               | for Filter 6 bit | s (same values    | s as bits<15:14  | >)                 |        |  |

| bit 11-10     | F5MSK<1:0                                                              | >: Mask Source                                               | for Filter 5 bit | s (same values    | s as bits<15:14  | >)                 |        |  |

| bit 9-8       | F4MSK<1:0                                                              | >: Mask Source                                               | for Filter 4 bit | s (same values    | s as bits<15:14  | >)                 |        |  |

| bit 7-6       | F3MSK<1:0                                                              | >: Mask Source                                               | for Filter 3 bit | s (same values    | s as bits<15:14  | >)                 |        |  |

| bit 5-4       | F2MSK<1:0                                                              | >: Mask Source                                               | for Filter 2 bit | s (same values    | s as bits<15:14  | >)                 |        |  |

| bit 3-2       | F1MSK<1:0>: Mask Source for Filter 1 bits (same values as bits<15:14>) |                                                              |                  |                   |                  |                    |        |  |

|               |                                                                        |                                                              |                  |                   |                  | . )                |        |  |

NOTES:

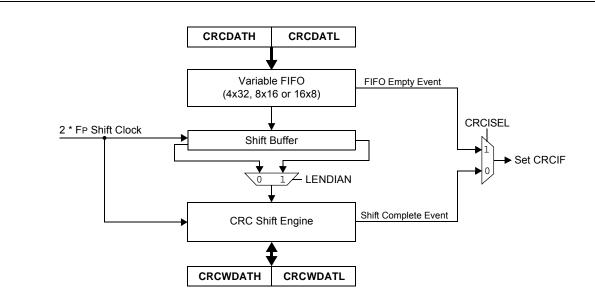

## 26.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Cyclic Redundancy Check (CRC)" (DS70346) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-programmable (up to 32nd order) polynomial CRC equation

- Interrupt output

- Data FIFO

The programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- Configurable interrupt output

- Data FIFO

A simplified block diagram of the CRC generator is shown in Figure 26-1. A simple version of the CRC shift engine is shown in Figure 26-2.

#### FIGURE 26-1: CRC BLOCK DIAGRAM

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

# **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>    | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | -0.3V to +3.6V       |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                       |                      |

| Maximum current sunk/sourced by any 4x I/O pin                                    | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                    | 25 mA                |

| Maximum current sunk by all ports <sup>(2,4)</sup>                                | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Exceptions are: dsPIC33EPXXXGP502, dsPIC33EPXXXMC202/502 and PIC24EPXXXGP/MC202 devices, which have a maximum sink/source capability of 130 mA.

| AC CHA       | RACTER  | ISTICS           |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |             |            |                        |  |  |

|--------------|---------|------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|------------------------|--|--|

| Param<br>No. | Symbol  | Characte         | eristic <sup>(4)</sup>    | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                     | -40<br>Max. | Units      | Conditions             |  |  |

| IM10         | TLO:SCL | Clock Low Time   | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         | _           | μS         |                        |  |  |

|              |         |                  | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         |             | μ <b>S</b> |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         |             | μs         |                        |  |  |

| IM11         | THI:SCL | Clock High Time  | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |             | μS         |                        |  |  |

|              |         | Ū                | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |             | μ <b>S</b> |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         |             | μS         |                        |  |  |

| IM20         | TF:SCL  | SDAx and SCLx    | 100 kHz mode              |                                                                                                                                                                                                                                                                                         | 300         | ns         | CB is specified to be  |  |  |

|              |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300         | ns         | from 10 to 400 pF      |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                                                                                                         | 100         | ns         | -                      |  |  |

| IM21         | TR:SCL  | SDAx and SCLx    | 100 kHz mode              |                                                                                                                                                                                                                                                                                         | 1000        | ns         | CB is specified to be  |  |  |

|              |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300         | ns         | from 10 to 400 pF      |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                                                                                                         | 300         | ns         | -                      |  |  |

| IM25         | TSU:DAT | Data Input       | 100 kHz mode              | 250                                                                                                                                                                                                                                                                                     |             | ns         |                        |  |  |

|              |         | Setup Time       | 400 kHz mode              | 100                                                                                                                                                                                                                                                                                     |             | ns         |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                                                                                                                                                                      |             | ns         | -                      |  |  |

| IM26 1       | THD:DAT | Data Input       | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                       |             | μS         |                        |  |  |

|              |         | Hold Time        | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                       | 0.9         | μ <b>S</b> |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                                                                                                                                                                     |             | μs         | -                      |  |  |

| IM30         | TSU:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |             | μ <b>S</b> | Only relevant for      |  |  |

|              |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |             | μS         | Repeated Start         |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |             | μs         | condition              |  |  |

| IM31         | THD:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |             | μ <b>s</b> | After this period, the |  |  |

|              |         | Hold Time        | 400 kHz mode              | Tcy/2 (BRG +2)                                                                                                                                                                                                                                                                          |             | μS         | first clock pulse is   |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         |             | μS         | generated              |  |  |

| IM33         | Tsu:sto | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         | _           | μS         |                        |  |  |

|              |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                         | _           | μS         |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         | _           | μS         |                        |  |  |

| IM34         | THD:STO | Stop Condition   |                           | μS                                                                                                                                                                                                                                                                                      |             |            |                        |  |  |

|              |         | Hold Time        | 400 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         | _           | μS         |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                         | _           | μS         |                        |  |  |

| IM40         | TAA:SCL | Output Valid     | 100 kHz mode              | —                                                                                                                                                                                                                                                                                       | 3500        | ns         |                        |  |  |

|              |         | From Clock       | 400 kHz mode              | —                                                                                                                                                                                                                                                                                       | 1000        | ns         |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                       | 400         | ns         |                        |  |  |

| IM45         | TBF:SDA | Bus Free Time    | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                     | _           | μs         | Time the bus must be   |  |  |

|              |         |                  | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                     | _           | μ <b>s</b> | free before a new      |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                                                                                                                                                                     |             | μ <b>s</b> | transmission can star  |  |  |

| IM50         | Св      | Bus Capacitive L |                           | _                                                                                                                                                                                                                                                                                       | 400         | pF         |                        |  |  |

| IM51         | TPGD    | Pulse Gobbler De | -                         | 65                                                                                                                                                                                                                                                                                      | 390         | ns         | (Note 3)               |  |  |

#### TABLE 30-49: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the l<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to "Inter-Integrated Circuit (l<sup>2</sup>C<sup>™</sup>)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site for the latest family reference manual sections.

- 2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

- **3:** Typical value for this parameter is 130 ns.

- 4: These parameters are characterized, but not tested in manufacturing.

| AC CHARACTERISTICS        |        |                                                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |         |       |       |                                         |  |

|---------------------------|--------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-----------------------------------------|--|

| Param<br>No.              | Symbol | Characteristic                                                                                            | Min.                                                                                                                                                                                                                                                                                          | Тур.    | Max.  | Units | Conditions                              |  |

|                           | -      | Cloci                                                                                                     | k Paramet                                                                                                                                                                                                                                                                                     | ters    |       |       |                                         |  |

| AD50 TAD ADC Clock Period |        |                                                                                                           |                                                                                                                                                                                                                                                                                               | _       | _     | ns    |                                         |  |

| AD51                      | tRC    | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                          |                                                                                                                                                                                                                                                                                               | 250     | _     | ns    |                                         |  |

|                           |        | Conv                                                                                                      | version R                                                                                                                                                                                                                                                                                     | ate     |       |       |                                         |  |

| AD55                      | tCONV  | Conversion Time                                                                                           | _                                                                                                                                                                                                                                                                                             | 14 Tad  |       | ns    |                                         |  |

| AD56                      | FCNV   | Throughput Rate                                                                                           | _                                                                                                                                                                                                                                                                                             | _       | 500   | ksps  |                                         |  |

| AD57a                     | TSAMP  | Sample Time when Sampling any ANx Input                                                                   | 3 Tad                                                                                                                                                                                                                                                                                         | —       | _     |       |                                         |  |

| AD57b                     | TSAMP  | Sample Time when Sampling the Op<br>Amp Outputs (Configuration A and<br>Configuration B) <sup>(4,5)</sup> | 3 Tad                                                                                                                                                                                                                                                                                         | —       | -     |       |                                         |  |

|                           |        | Timin                                                                                                     | g Parame                                                                                                                                                                                                                                                                                      | ters    |       |       |                                         |  |

| AD60                      | tPCS   | Conversion Start from Sample<br>Trigger <sup>(2,3)</sup>                                                  | 2 Tad                                                                                                                                                                                                                                                                                         | -       | 3 Tad | —     | Auto-convert trigger is<br>not selected |  |

| AD61                      | tPSS   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2,3)</sup>                                           | 2 Tad                                                                                                                                                                                                                                                                                         | —       | 3 Tad |       |                                         |  |

| AD62                      | tcss   | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2,3)</sup>                                      |                                                                                                                                                                                                                                                                                               | 0.5 Tad | —     |       |                                         |  |

| AD63                      | tdpu   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup>                                 | —                                                                                                                                                                                                                                                                                             | —       | 20    | μS    | (Note 6)                                |  |

## TABLE 30-60: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- **6:** The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACT               | ERISTICS |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |                                                      |      |                                               |  |

|--------------------------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|-----------------------------------------------|--|

| Parameter<br>No.         | Typical  | Мах  | Units                                                                                                                               | Conditions                                           |      |                                               |  |

| Power-Down Current (IPD) |          |      |                                                                                                                                     |                                                      |      |                                               |  |

| HDC60e                   | 1400     | 2500 | μA                                                                                                                                  | A +150°C 3.3V Base Power-Down Currer<br>(Notes 1, 3) |      |                                               |  |

| HDC61c                   | 15       | —    | μΑ                                                                                                                                  | +150°C                                               | 3.3V | Watchdog Timer Current: ∆IwDT<br>(Notes 2, 4) |  |

#### TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off and VREGS (RCON<8>) = 1.

2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

3: These currents are measured on the device containing the most memory in this family.

4: These parameters are characterized, but are not tested in manufacturing.

#### TABLE 31-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARAG        | CTERISTICS |     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |                     |  |         |  |

|------------------|------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|--|---------|--|

| Parameter<br>No. | Typical    | Мах | Units                                                                                                                             | Conditions          |  |         |  |

| HDC44e           | 12         | 30  | mA                                                                                                                                | +150°C 3.3V 40 MIPS |  | 40 MIPS |  |

#### TABLE 31-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARAC        | CTERISTICS |     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |                     |      |         |

|------------------|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|---------|

| Parameter<br>No. | Typical    | Max | Units                                                                                                                               | Conditions          |      |         |

| HDC20            | 9          | 15  | mA                                                                                                                                  | +150°C 3.3V 10 MIPS |      |         |

| HDC22            | 16         | 25  | mA                                                                                                                                  | +150°C 3.3V 20 MIPS |      |         |

| HDC23            | 30         | 50  | mA                                                                                                                                  | +150°C              | 3.3V | 40 MIPS |

#### TABLE 31-7: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARA              | (unless oth | erwise s | <b>Conditions</b><br>tated)<br>re -40°C ≤ |       |            |      |         |

|-----------------------|-------------|----------|-------------------------------------------|-------|------------|------|---------|

| Parameter<br>No.      | Typical     | Мах      | Doze<br>Ratio                             | Units | Conditions |      |         |

| HDC72a                | 24          | 35       | 1:2                                       | mA    |            |      |         |

| HDC72f <sup>(1)</sup> | 14          | —        | 1:64                                      | mA    | +150°C     | 3.3V | 40 MIPS |

| HDC72g <sup>(1)</sup> | 12          |          | 1:128                                     | mA    |            |      |         |

Note 1: Parameters with Doze ratios of 1:64 and 1:128 are characterized, but are not tested in manufacturing.

NOTES: