Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc506-h-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

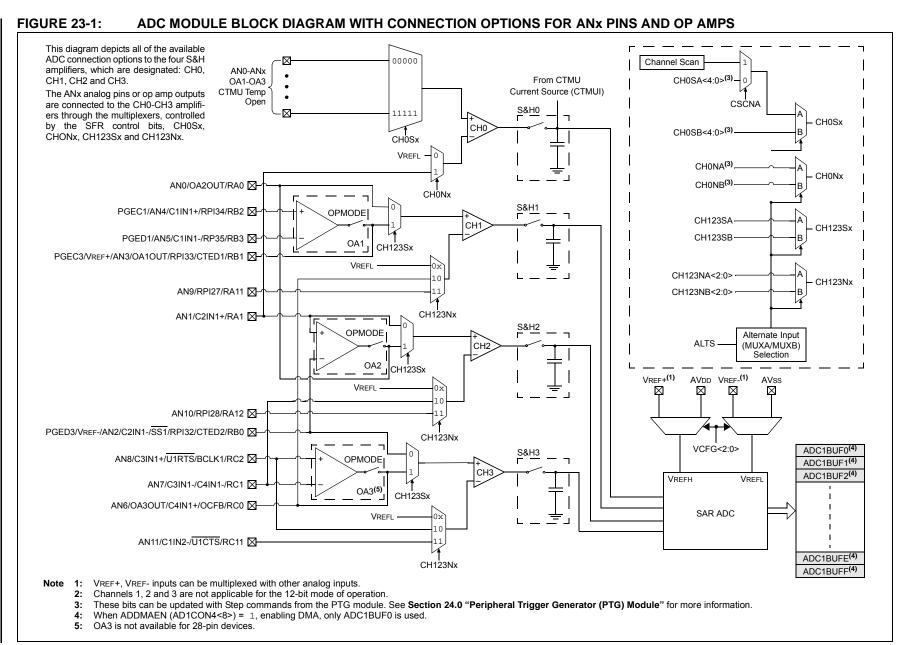

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

## 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00             |        |        |              | 011 401    |        |       | 20/0/00/  |        |       |        |         |          |         | -     | r     |               |

|-----------|-------|------------------|--------|--------|--------------|------------|--------|-------|-----------|--------|-------|--------|---------|----------|---------|-------|-------|---------------|

| File Name | Addr. | Bit 15           | Bit 14 | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8     | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2   | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |                  |        |        |              |            |        |       | W0 (WR    | EG)    |       |        |         |          |         |       |       | xxxx          |

| W1        | 0002  |                  |        |        |              |            |        |       | W1        |        |       |        |         |          |         |       |       | xxxx          |

| W2        | 0004  |                  | W2 x   |        |              |            |        |       |           |        |       |        | xxxx    |          |         |       |       |               |

| W3        | 0006  |                  | W3 2   |        |              |            |        |       |           |        |       |        | xxxx    |          |         |       |       |               |

| W4        | 8000  |                  |        |        |              |            |        |       | W4        |        |       |        |         |          |         |       |       | xxxx          |

| W5        | 000A  |                  |        |        |              |            |        |       | W5        |        |       |        |         |          |         |       |       | xxxx          |

| W6        | 000C  |                  |        |        |              |            |        |       | W6        |        |       |        |         |          |         |       |       | xxxx          |

| W7        | 000E  |                  |        |        |              |            |        |       | W7        |        |       |        |         |          |         |       |       | xxxx          |

| W8        | 0010  |                  |        |        |              |            |        |       | W8        |        |       |        |         |          |         |       |       | xxxx          |

| W9        | 0012  |                  |        |        |              |            |        |       | W9        |        |       |        |         |          |         |       |       | xxxx          |

| W10       | 0014  |                  |        |        |              |            |        |       | W10       |        |       |        |         |          |         |       |       | xxxx          |

| W11       | 0016  |                  |        |        |              |            |        |       | W11       |        |       |        |         |          |         |       |       | xxxx          |

| W12       | 0018  |                  |        |        |              |            |        |       | W12       |        |       |        |         |          |         |       |       | xxxx          |

| W13       | 001A  |                  |        |        |              |            |        |       | W13       |        |       |        |         |          |         |       |       | xxxx          |

| W14       | 001C  |                  |        |        |              |            |        |       | W14       |        |       |        |         |          |         |       |       | xxxx          |

| W15       | 001E  |                  |        |        |              |            |        |       | W15       |        |       |        |         |          |         |       |       | xxxx          |

| SPLIM     | 0020  |                  |        |        |              |            |        |       | SPLI      | N      |       |        |         |          |         |       |       | 0000          |

| ACCAL     | 0022  |                  |        |        |              |            |        |       | ACCA      | L      |       |        |         |          |         |       |       | 0000          |

| ACCAH     | 0024  |                  |        |        |              |            |        |       | ACCA      | H      |       |        |         |          |         |       |       | 0000          |

| ACCAU     | 0026  |                  |        | Si     | gn Extensior | n of ACCA< | 39>    |       |           |        |       |        | ACO     | CAU      |         |       |       | 0000          |

| ACCBL     | 0028  |                  |        |        |              |            |        |       | ACCB      | L      |       |        |         |          |         |       |       | 0000          |

| ACCBH     | 002A  |                  |        |        |              |            |        |       | ACCB      | Н      |       |        |         |          |         |       |       | 0000          |

| ACCBU     | 002C  |                  |        | Si     | gn Extensior | n of ACCB< | 39>    |       |           |        |       |        | ACO     | CBU      |         |       |       | 0000          |

| PCL       | 002E  |                  |        |        |              |            |        | F     | PCL<15:0> |        |       |        |         |          |         |       |       | 0000          |

| PCH       | 0030  | _                | _      | _      | —            | _          | _      | —     | _         | _      |       |        |         | PCH<6:0> |         |       |       | 0000          |

| DSRPAG    | 0032  | _                | _      | _      | _            | _          | _      |       |           |        |       | DSRPAC | 6<9:0>  |          |         |       |       | 0001          |

| DSWPAG    | 0034  | _                |        | _      | —            |            | _      | _     |           |        |       | DS     | WPAG<8: | 0>       |         |       |       | 0001          |

| RCOUNT    | 0036  |                  |        |        |              |            |        |       | RCOUNT<   | :15:0> |       |        |         |          |         |       |       | 0000          |

| DCOUNT    | 0038  | DCOUNT<15:0>     |        |        |              |            |        |       | 0000      |        |       |        |         |          |         |       |       |               |

| DOSTARTL  | 003A  | DOSTARTL<15:1>   |        |        |              |            |        | 0000  |           |        |       |        |         |          |         |       |       |               |

| DOSTARTH  | 003C  | DOSTARTH<5:0>    |        |        |              |            |        |       | 0000      |        |       |        |         |          |         |       |       |               |

| DOENDL    | 003E  | DOENDL<15:1> — ( |        |        |              |            |        |       | 0000      |        |       |        |         |          |         |       |       |               |

| DOENDH    | 0040  | _                | —      | —      | —            | —          | —      | _     | —         | —      | —     |        |         | DOEND    | )H<5:0> |       |       | 0000          |

|           |       |                  |        |        |              |            |        |       |           |        |       |        |         |          |         |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

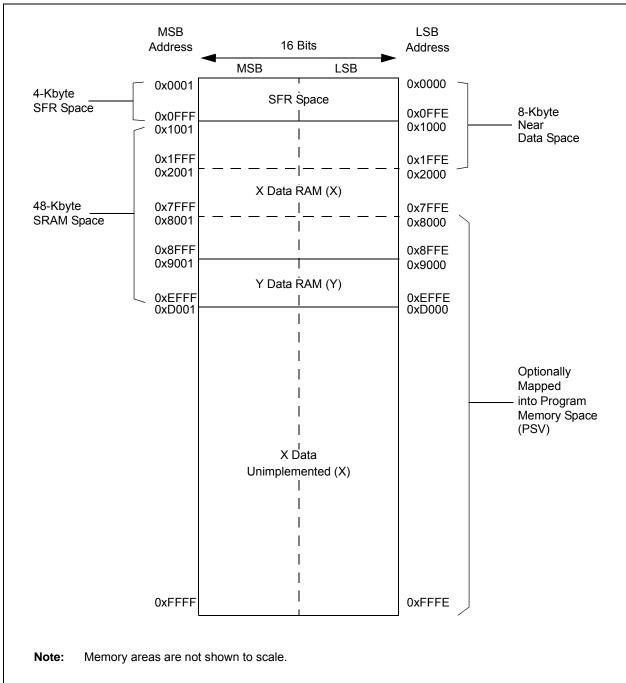

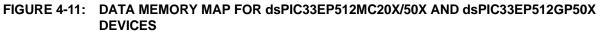

## 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

## 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

| R/W-1        | R/W-0                                             | R/W-0                                                              | U-0          | U-0              | U-0              | U-0             | U-0    |  |  |  |  |

|--------------|---------------------------------------------------|--------------------------------------------------------------------|--------------|------------------|------------------|-----------------|--------|--|--|--|--|

| GIE          | DISI                                              | SWTRAP                                                             |              |                  |                  | _               |        |  |  |  |  |

| bit 15       |                                                   |                                                                    |              |                  |                  |                 | bit 8  |  |  |  |  |

|              |                                                   |                                                                    |              |                  |                  |                 |        |  |  |  |  |

| U-0          | U-0                                               | U-0                                                                | U-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|              | —                                                 |                                                                    |              |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |  |

| bit 7        |                                                   |                                                                    |              |                  |                  |                 | bit C  |  |  |  |  |

| Legend:      |                                                   |                                                                    |              |                  |                  |                 |        |  |  |  |  |

| R = Readab   | le bit                                            | W = Writable                                                       | bit          | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |  |

| -n = Value a |                                                   | '1' = Bit is set                                                   |              | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |  |  |  |

|              |                                                   |                                                                    |              |                  |                  |                 |        |  |  |  |  |

| bit 15       | GIE: Global                                       | Interrupt Enable                                                   | e bit        |                  |                  |                 |        |  |  |  |  |

|              | 1 = Interrupts and associated IE bits are enabled |                                                                    |              |                  |                  |                 |        |  |  |  |  |

|              |                                                   | s are disabled, I                                                  | •            | still enabled    |                  |                 |        |  |  |  |  |

| bit 14       | DISI: DISI                                        | nstruction Statu                                                   | s bit        |                  |                  |                 |        |  |  |  |  |

|              |                                                   | struction is active<br>struction is not a                          | -            |                  |                  |                 |        |  |  |  |  |

| bit 13       | SWTRAP: S                                         | Software Trap St                                                   | atus bit     |                  |                  |                 |        |  |  |  |  |

|              |                                                   | e trap is enabled<br>e trap is disabled                            |              |                  |                  |                 |        |  |  |  |  |

| bit 12-3     | Unimpleme                                         | nted: Read as '                                                    | 0'           |                  |                  |                 |        |  |  |  |  |

| bit 2        | INT2EP: Ext                                       | ternal Interrupt 2                                                 | 2 Edge Detec | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|              |                                                   | on negative edg                                                    |              |                  |                  |                 |        |  |  |  |  |

| bit 1        | INT1EP: Ext                                       | <b>NT1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit |              |                  |                  |                 |        |  |  |  |  |

|              |                                                   | on negative edg                                                    |              |                  |                  |                 |        |  |  |  |  |

| bit 0        | INTOEP: Ext                                       | ternal Interrupt C                                                 | Edge Detec   | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|              |                                                   | on negative edg                                                    |              |                  |                  |                 |        |  |  |  |  |

## REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

## 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

## 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

## 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

## **11.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Change Noti-      |

|-------|----------------------------------------------|

|       | fication pins should always be disabled      |

|       | when the port pin is configured as a digital |

|       | output.                                      |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

## 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

## BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                                           | U-0               | R/W-x         | R/W-x                                   | R/W-x            | R/W-x    | R/W-x |  |

|---------------|-----------------------------------------------|-------------------|---------------|-----------------------------------------|------------------|----------|-------|--|

|               | —                                             | _                 | SID10         | SID9                                    | SID8             | SID7     | SID6  |  |

| bit 15        |                                               |                   |               |                                         |                  |          | bit 8 |  |

| R/W-x         | R/W-x                                         | R/W-x             | R/W-x         | R/W-x                                   | R/W-x            | R/W-x    | R/W-x |  |

| SID5          | SID4                                          | SID3              | SID2          | SID1                                    | SID0             | SRR      | IDE   |  |

| bit 7         |                                               |                   |               |                                         | •                |          | bit 0 |  |

| Legend:       |                                               |                   |               |                                         |                  |          |       |  |

| R = Readabl   | e bit                                         | W = Writable      | bit           | U = Unimpler                            | mented bit, read | l as '0' |       |  |

| -n = Value at | POR                                           | '1' = Bit is set  |               | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |

|               |                                               |                   |               |                                         |                  |          |       |  |

| bit 15-13     | Unimplemen                                    | ted: Read as '    | כי            |                                         |                  |          |       |  |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S                     | Standard Identifi | ier bits      |                                         |                  |          |       |  |

| bit 1         | SRR: Substitu                                 | ute Remote Re     | quest bit     |                                         |                  |          |       |  |

|               | When IDE =                                    | 0:                |               |                                         |                  |          |       |  |

|               | 1 = Message                                   | will request rer  | note transmis | ssion                                   |                  |          |       |  |

|               | 0 = Normal m                                  | nessage           |               |                                         |                  |          |       |  |

|               | When IDE = 1                                  | <u>1:</u>         |               |                                         |                  |          |       |  |

|               | The SRR bit r                                 | must be set to '  | 1'.           |                                         |                  |          |       |  |

| bit 0         | IDE: Extende                                  | d Identifier bit  |               |                                         |                  |          |       |  |

|               | 1 = Message                                   | will transmit Ex  | tended Ident  | ifier                                   |                  |          |       |  |

|               | 0 = Message will transmit Standard Identifier |                   |               |                                         |                  |          |       |  |

|               |                                               |                   |               |                                         |                  |          |       |  |

## BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0             | U-0   | U-0              | U-0   | R/W-x            | R/W-x            | R/W-x              | R/W-x |  |

|-----------------|-------|------------------|-------|------------------|------------------|--------------------|-------|--|

| —               | —     | —                | _     | EID17            | EID17 EID16      |                    | EID14 |  |

| bit 15          |       |                  |       |                  |                  |                    | bit 8 |  |

|                 |       |                  |       |                  |                  |                    |       |  |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x            | R/W-x              | R/W-x |  |

| EID13           | EID12 | EID11            | EID10 | EID9             | EID9 EID8        |                    | EID6  |  |

| bit 7           |       |                  |       |                  |                  |                    | bit 0 |  |

|                 |       |                  |       |                  |                  |                    |       |  |

| Legend:         |       |                  |       |                  |                  |                    |       |  |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimpler     | nented bit, read | as '0'             |       |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

|                 |       |                  |       |                  |                  |                    |       |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

## 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

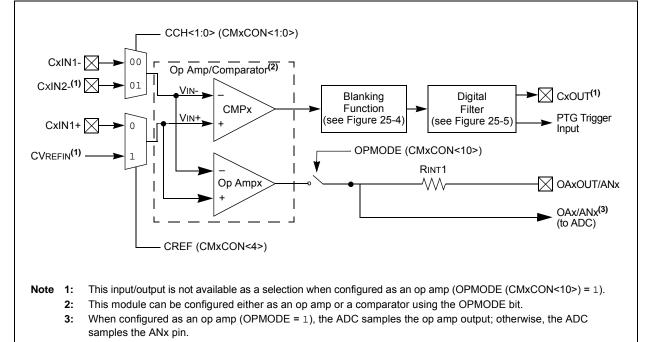

# 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

## FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

## REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN-0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax         | Description                              | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|-------|-------------------------|------------------------------------------|---------------|-------------------------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc <sup>(1)</sup>      | Add Accumulators                         | 1             | 1                             | OA,OB,SA,SB              |

|                    |                      | ADD   | f                       | f = f + WREG                             | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG                  | WREG = f + WREG                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn               | Wd = lit10 + Wd                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd                | Wd = Wb + Ws                             | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd             | Wd = Wb + lit5                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc          | 16-bit Signed Add to Accumulator         | 1             | 1                             | OA,OB,SA,SE              |

| 2                  | ADDC                 | ADDC  | f                       | f = f + WREG + (C)                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG                  | WREG = $f + WREG + (C)$                  | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn               | Wd = Iit10 + Wd + (C)                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd                | Wd = Wb + Ws + (C)                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,#lit5,Wd             | Wd = Wb + lit5 + (C)                     | 1             | 1                             | C,DC,N,OV,Z              |

| 3                  | AND                  | AND   | f                       | f = f .AND. WREG                         | 1             | 1                             | N,Z                      |

|                    |                      | AND   | f,WREG                  | WREG = f .AND. WREG                      | 1             | 1                             | N,Z                      |

|                    |                      | AND   | #lit10,Wn               | Wd = lit10 .AND. Wd                      | 1             | 1                             | N,Z                      |

|                    |                      | AND   | Wb,Ws,Wd                | Wd = Wb .AND. Ws                         | 1             | 1                             | N,Z                      |

|                    |                      | AND   | Wb,#lit5,Wd             | Wd = Wb .AND. lit5                       | 1             | 1                             | N,Z                      |

| 4                  | ASR                  | ASR   | f                       | f = Arithmetic Right Shift f             | 1             | 1                             | C,N,OV,Z                 |

|                    | non                  | ASR   | f,WREG                  | WREG = Arithmetic Right Shift f          | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | ASR   | Ws,Wd                   | Wd = Arithmetic Right Shift Ws           | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | ASR   | Wb, Wns, Wnd            | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1                             | N,Z                      |

|                    |                      | ASR   | Wb,#lit5,Wnd            | Wind = Arithmetic Right Shift Wb by Wils | 1             | 1                             | N,Z                      |

| 5                  | BCLR                 | BCLR  | f,#bit4                 | Bit Clear f                              | 1             | 1                             | None                     |

| 5                  | BCLIK                |       |                         | Bit Clear Ws                             | 1             | 1                             | None                     |

| 6                  | DD 3                 | BCLR  | Ws,#bit4                |                                          | 1             |                               | None                     |

| 6                  | BRA                  | BRA   | C,Expr                  | Branch if Carry                          |               | 1 (4)                         |                          |

|                    |                      | BRA   | GE, Expr                | Branch if greater than or equal          | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | GEU, Expr               | Branch if unsigned greater than or equal | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | GT, Expr                | Branch if greater than                   | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | GTU, Expr               | Branch if unsigned greater than          | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | LE,Expr                 | Branch if less than or equal             | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | LEU,Expr                | Branch if unsigned less than or equal    | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | LT,Expr                 | Branch if less than                      | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | LTU, Expr               | Branch if unsigned less than             | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | N,Expr                  | Branch if Negative                       | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | NC,Expr                 | Branch if Not Carry                      | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | NN,Expr                 | Branch if Not Negative                   | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | NOV,Expr                | Branch if Not Overflow                   | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | NZ,Expr                 | Branch if Not Zero                       | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | OA, Expr(1)             | Branch if Accumulator A overflow         | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | OB, Expr <sup>(1)</sup> | Branch if Accumulator B overflow         | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | OV, Expr(1)             | Branch if Overflow                       | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | SA, Expr <sup>(1)</sup> | Branch if Accumulator A saturated        | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | SB, Expr <sup>(1)</sup> | Branch if Accumulator B saturated        | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | Expr                    | Branch Unconditionally                   | 1             | 4                             | None                     |

|                    |                      | BRA   | Z,Expr                  | Branch if Zero                           | 1             | 1 (4)                         | None                     |

|                    |                      | BRA   | Wn                      | Computed Branch                          | 1             | 4                             | None                     |

| 7                  | BSET                 | BSET  | f,#bit4                 | Bit Set f                                | 1             | 1                             | None                     |

|                    |                      | BSET  | Ws,#bit4                | Bit Set Ws                               | 1             | 1                             | None                     |

| 8                  | BSW                  | BSW.C | Ws,Wb                   | Write C bit to Ws <wb></wb>              | 1             | 1                             | None                     |

|                    |                      | BSW.Z | Ws,Wb                   | Write Z bit to Ws <wb></wb>              | 1             | 1                             | None                     |

## TABLE 28-2: INSTRUCTION SET OVERVIEW

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

## 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>    | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | -0.3V to +3.6V       |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                       |                      |

| Maximum current sunk/sourced by any 4x I/O pin                                    | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                    | 25 mA                |

| Maximum current sunk by all ports <sup>(2,4)</sup>                                | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Exceptions are: dsPIC33EPXXXGP502, dsPIC33EPXXXMC202/502 and PIC24EPXXXGP/MC202 devices, which have a maximum sink/source capability of 130 mA.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

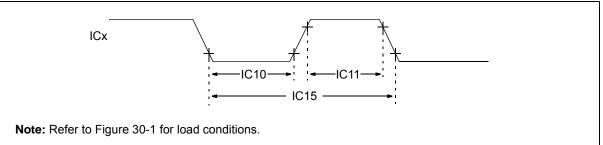

## FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

## TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHA                                              | RACTERI | STICS               | Standard Operati<br>(unless otherwise<br>Operating tempera | e stated | )<br>∙40°C ≤ <sup>-</sup> | <b>3.0V to 3.6V</b><br>「A ≤ +85°C for Indu<br>「A ≤ +125°C for Ext |                                  |

|-----------------------------------------------------|---------|---------------------|------------------------------------------------------------|----------|---------------------------|-------------------------------------------------------------------|----------------------------------|

| Param.<br>No. Symbol Characteristics <sup>(1)</sup> |         |                     | Min.                                                       | Max.     | Units                     | Con                                                               | ditions                          |

| IC10                                                | TccL    | ICx Input Low Time  | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25             |          | ns                        | Must also meet<br>Parameter IC15                                  |                                  |

| IC11                                                | ТссН    | ICx Input High Time | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25             | —        | ns                        | Must also meet<br>Parameter IC15                                  | N = prescale value<br>(1, 4, 16) |

| IC15                                                | TccP    | ICx Input Period    | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50              | _        | ns                        |                                                                   |                                  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

| AC CHARACTERISTICS |        |                                                      | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |         |                                   |          |                                                                                               |  |  |

|--------------------|--------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------|----------|-----------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                                       | Min.                                                                                                                                                                                                                                                                                            | Тур.    | Max.                              | Units    | Conditions                                                                                    |  |  |

|                    |        |                                                      | Devi                                                                                                                                                                                                                                                                                            | ce Sup  | ply                               |          |                                                                                               |  |  |

| AD01               | AVDD   | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or 3.0                                                                                                                                                                                                                                                              |         | Lesser of:<br>VDD + 0.3<br>or 3.6 | V        |                                                                                               |  |  |

| AD02               | AVss   | Module Vss Supply                                    | Vss – 0.3                                                                                                                                                                                                                                                                                       |         | Vss + 0.3                         | V        |                                                                                               |  |  |

|                    |        |                                                      | Refere                                                                                                                                                                                                                                                                                          | ence In | puts                              |          |                                                                                               |  |  |

| AD05               | Vrefh  | Reference Voltage High                               | AVss + 2.5                                                                                                                                                                                                                                                                                      |         | AVDD                              | V        | VREFH = VREF+<br>VREFL = VREF- <b>(Note 1)</b>                                                |  |  |

| AD05a              |        |                                                      | 3.0                                                                                                                                                                                                                                                                                             | _       | 3.6                               | V        | VREFH = AVDD<br>VREFL = AVSS = 0                                                              |  |  |

| AD06               | VREFL  | Reference Voltage Low                                | AVss                                                                                                                                                                                                                                                                                            |         | AVDD - 2.5                        | V        | (Note 1)                                                                                      |  |  |

| AD06a              |        |                                                      | 0                                                                                                                                                                                                                                                                                               |         | 0                                 | V        | VREFH = AVDD<br>VREFL = AVSS = 0                                                              |  |  |

| AD07               | VREF   | Absolute Reference<br>Voltage                        | 2.5                                                                                                                                                                                                                                                                                             | _       | 3.6                               | V        | VREF = VREFH - VREFL                                                                          |  |  |

| AD08               | IREF   | Current Drain                                        |                                                                                                                                                                                                                                                                                                 |         | 10<br>600                         | μΑ<br>μΑ | ADC off<br>ADC on                                                                             |  |  |

| AD09               | Iad    | Operating Current <sup>(2)</sup>                     | —                                                                                                                                                                                                                                                                                               | 5       | _                                 | mA       | ADC operating in 10-bit mode (Note 1)                                                         |  |  |

|                    |        |                                                      | —                                                                                                                                                                                                                                                                                               | 2       | —                                 | mA       | ADC operating in 12-bit mode (Note 1)                                                         |  |  |

|                    | •      |                                                      | Ana                                                                                                                                                                                                                                                                                             | log Inp | ut                                |          |                                                                                               |  |  |

| AD12               | Vinh   | Input Voltage Range<br>VinH                          | VINL                                                                                                                                                                                                                                                                                            | _       | Vrefh                             | V        | This voltage reflects Sample-and-<br>Hold Channels 0, 1, 2 and 3<br>(CH0-CH3), positive input |  |  |

| AD13               | VINL   | Input Voltage Range<br>VINL                          | Vrefl                                                                                                                                                                                                                                                                                           | _       | AVss + 1V                         | V        | This voltage reflects Sample-and-<br>Hold Channels 0, 1, 2 and 3<br>(CH0-CH3), negative input |  |  |

| AD17               | Rin    | Recommended<br>Impedance of Analog<br>Voltage Source | _                                                                                                                                                                                                                                                                                               | _       | 200                               | Ω        | Impedance to achieve maximum<br>performance of ADC                                            |  |  |

## TABLE 30-57: ADC MODULE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: Parameter is characterized but not tested in manufacturing.

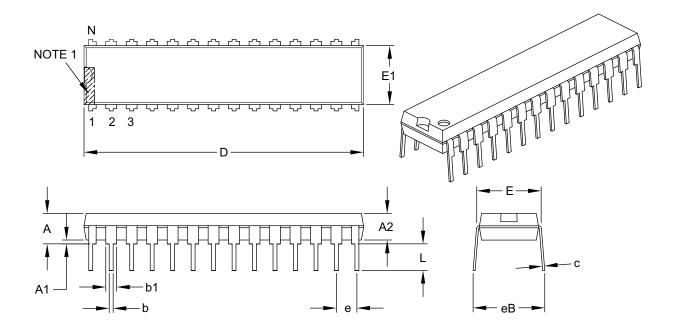

## 33.2 Package Details

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |          | INCHES |       |

|----------------------------|----------|----------|--------|-------|

| Dimension                  | n Limits | MIN      | NOM    | MAX   |

| Number of Pins             | Ν        |          | 28     |       |

| Pitch                      | е        | .100 BSC |        |       |

| Top to Seating Plane       | Α        | -        | -      | .200  |

| Molded Package Thickness   | A2       | .120     | .135   | .150  |

| Base to Seating Plane      | A1       | .015     | -      | -     |

| Shoulder to Shoulder Width | E        | .290     | .310   | .335  |

| Molded Package Width       | E1       | .240     | .285   | .295  |

| Overall Length             | D        | 1.345    | 1.365  | 1.400 |

| Tip to Seating Plane       | L        | .110     | .130   | .150  |

| Lead Thickness             | С        | .008     | .010   | .015  |

| Upper Lead Width           | b1       | .040     | .050   | .070  |

| Lower Lead Width           | b        | .014     | .018   | .022  |

| Overall Row Spacing §      | eB       | _        | -      | .430  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

| Section Name                    | Update Description                                                                                                                                                   |  |  |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Section 30.0 "Electrical        | These SPI2 Timing Requirements were updated:                                                                                                                         |  |  |  |  |

| Characteristics"<br>(Continued) | <ul> <li>Maximum value for Parameter SP10 and the minimum clock period value for<br/>SCKx in Note 3 (see Table 30-36, Table 30-37, and Table 30-38)</li> </ul>       |  |  |  |  |

|                                 | <ul> <li>Maximum value for Parameter SP70 and the minimum clock period value for<br/>SCKx in Note 3 (see Table 30-40 and Table 30-42)</li> </ul>                     |  |  |  |  |

|                                 | The Maximum Data Rate values were updated for the SPI2 Maximum Data/Clock<br>Rate Summary (see Table 30-43)                                                          |  |  |  |  |

|                                 | These SPI1 Timing Requirements were updated:                                                                                                                         |  |  |  |  |

|                                 | Maximum value for Parameters SP10 and the minimum clock period value for SCKx in Note 3 (see Table 30-44, Table 30-45, and Table 30-46)                              |  |  |  |  |

|                                 | Maximum value for Parameters SP70 and the minimum clock period value for SCKx in Note 3 (see Table 30-47 through Table 30-50)                                        |  |  |  |  |

|                                 | <ul> <li>Minimum value for Parameters SP40 and SP41 see Table 30-44 through<br/>Table 30-50)</li> </ul>                                                              |  |  |  |  |

|                                 | Updated all Typical values for the CTMU Current Source Specifications (see Table 30-55).                                                                             |  |  |  |  |

|                                 | Updated Note1, the Maximum value for Parameter AD06, the Minimum value for AD07, and the Typical values for AD09 in the ADC Module Specifications (see Table 30-56). |  |  |  |  |

|                                 | Added Note 1 to the ADC Module Specifications (12-bit Mode) (see Table 30-57).                                                                                       |  |  |  |  |

|                                 | Added Note 1 to the ADC Module Specifications (10-bit Mode) (see Table 30-58).                                                                                       |  |  |  |  |

|                                 | Updated the Minimum and Maximum values for Parameter AD21b in the 10-bit Mode ADC Module Specifications (see Table 30-58).                                           |  |  |  |  |

|                                 | Updated Note 2 in the ADC Conversion (12-bit Mode) Timing Requirements (see Table 30-59).                                                                            |  |  |  |  |

|                                 | Updated Note 1 in the ADC Conversion (10-bit Mode) Timing Requirements (see Table 30-60).                                                                            |  |  |  |  |

## TABLE A-2: MAJOR SECTION UPDATES (CONTINUED)