Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc506t-e-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

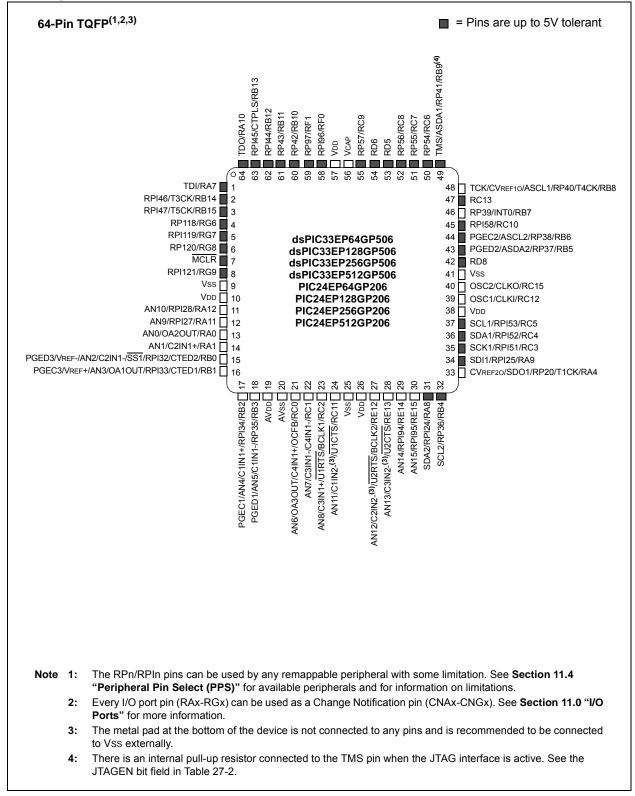

### **Pin Diagrams (Continued)**

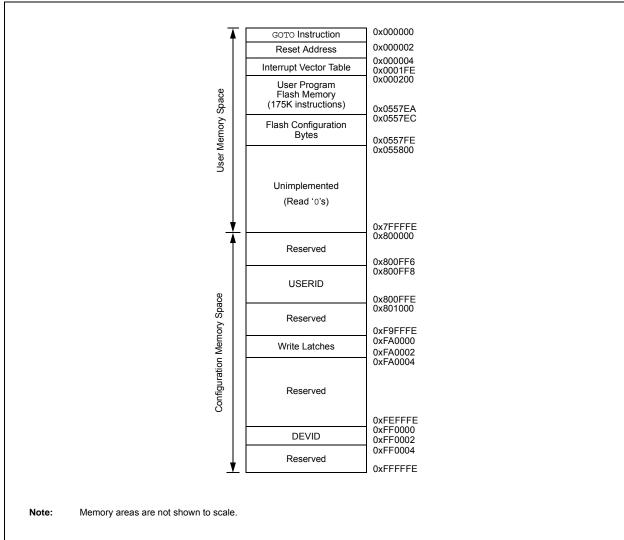

### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

### 4.4.1 PAGED MEMORY SCHEME

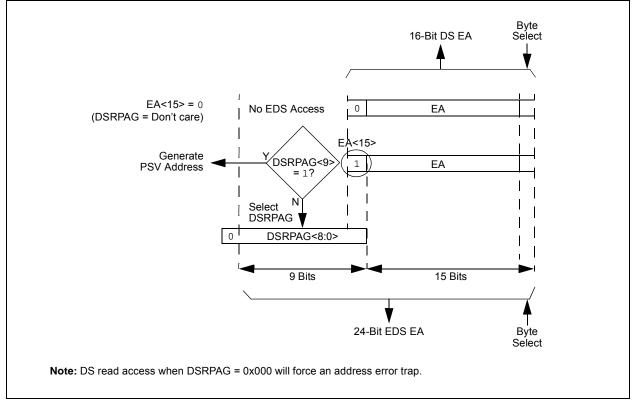

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |  |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |  |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |  |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |  |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |  |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |  |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |  |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |  |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |  |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |  |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |  |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |  |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |  |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |  |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |  |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |  |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |  |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |  |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |  |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |  |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |  |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |  |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |  |

### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

NOTES:

## 9.3 Oscillator Control Registers

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0            | R-0                                                                | R-0                                  | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                |

|----------------|--------------------------------------------------------------------|--------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------|

| _              | COSC2                                                              | COSC1                                | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |

| bit 15         |                                                                    |                                      |                                    |                                    |                                    |                      | bit 8                |

| R/W-0          | R/W-0                                                              | R-0                                  | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                |

| CLKLOC         | CK IOLOCK                                                          | LOCK                                 |                                    | CF <sup>(3)</sup>                  |                                    |                      | OSWEN                |

| bit 7          |                                                                    |                                      |                                    |                                    |                                    |                      | bit (                |

| Legend:        |                                                                    | y = Value set                        | from Configur                      | ation bits on F                    | POR                                |                      |                      |

| R = Reada      | able bit                                                           | W = Writable                         | -                                  |                                    | mented bit, read                   | l as '0'             |                      |

| -n = Value     | at POR                                                             | '1' = Bit is se                      | t                                  | '0' = Bit is cle                   | eared                              | x = Bit is unkr      | nown                 |

| hit 1 <i>5</i> | Unimplemen                                                         | ted. Dood oo                         | 0'                                 |                                    |                                    |                      |                      |

| bit 15         | -                                                                  | ted: Read as                         |                                    |                                    |                                    |                      |                      |

| bit 14-12      |                                                                    | Current Oscill                       |                                    |                                    | ()                                 |                      |                      |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F   |                                    |                                    |                                    |                      |                      |

|                |                                                                    | ower RC Oscil                        |                                    |                                    |                                    |                      |                      |

|                | 100 = Reserv                                                       |                                      | ()                                 |                                    |                                    |                      |                      |

|                |                                                                    | y Oscillator (X                      |                                    | h PLL                              |                                    |                      |                      |

|                |                                                                    | y Oscillator (X                      |                                    |                                    |                                    |                      |                      |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F   |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |

| bit 11         |                                                                    | ted: Read as                         | ,                                  |                                    |                                    |                      |                      |

| bit 10-8       | NOSC<2:0>:                                                         | New Oscillato                        | r Selection bits                   | <sub>S</sub> (2)                   |                                    |                      |                      |

|                | 111 = Fast R                                                       | C Oscillator (F                      | RC) with Divid                     | le-by-n                            |                                    |                      |                      |

|                |                                                                    | C Oscillator (F                      |                                    | le-by-16                           |                                    |                      |                      |

|                |                                                                    | ower RC Oscil                        | ator (LPRC)                        |                                    |                                    |                      |                      |

|                | 100 = Reserv                                                       | /ed<br>y Oscillator (X               |                                    |                                    |                                    |                      |                      |

|                |                                                                    | y Oscillator (X                      |                                    | IFLL                               |                                    |                      |                      |

|                |                                                                    | C Oscillator (F                      |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |

|                |                                                                    | C Oscillator (F                      |                                    | ,                                  | ,                                  |                      |                      |

| bit 7          |                                                                    | Clock Lock Ena                       |                                    |                                    |                                    |                      |                      |

|                |                                                                    |                                      |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and       |

|                |                                                                    | figurations may<br>d PLL selectio    |                                    | ked, configurat                    | ions may be mo                     | odified              |                      |

| bit 6          |                                                                    | Lock Enable b                        |                                    | -                                  | -                                  |                      |                      |

|                | 1 = I/O lock is                                                    | s active                             |                                    |                                    |                                    |                      |                      |

|                | 0 = I/O lock is                                                    | s not active                         |                                    |                                    |                                    |                      |                      |

| bit 5          | LOCK: PLL L                                                        | ock Status bit                       | (read-only)                        |                                    |                                    |                      |                      |

|                |                                                                    | s that PLL is in<br>s that PLL is ou |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                      |

| Note 1:        | Writes to this regis                                               |                                      |                                    |                                    |                                    |                      | ʻdsPIC33/            |

| 2:             | Direct clock switch<br>This applies to cloo<br>mode as a transitio | es between ar<br>ck switches in      | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                      |

| 0              | This bit should only                                               |                                      |                                    |                                    |                                    |                      |                      |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

| U-0             | U-0                                       | U-0              | U-0             | U-0                                | U-0             | U-0                | R/W-0   |

|-----------------|-------------------------------------------|------------------|-----------------|------------------------------------|-----------------|--------------------|---------|

| _               | —                                         | —                |                 | —                                  | —               | —                  | PLLDIV8 |

| bit 15          |                                           |                  |                 |                                    |                 |                    | bit 8   |

|                 |                                           |                  |                 |                                    |                 |                    |         |

| R/W-0           | R/W-0                                     | R/W-1            | R/W-1           | R/W-0                              | R/W-0           | R/W-0              | R/W-0   |

| PLLDIV7         | PLLDIV6                                   | PLLDIV5          | PLLDIV4         | PLLDIV3                            | PLLDIV2         | PLLDIV1            | PLLDIV0 |

| bit 7           |                                           |                  |                 |                                    |                 |                    | bit 0   |

|                 |                                           |                  |                 |                                    |                 |                    |         |

| Legend:         |                                           |                  |                 |                                    |                 |                    |         |

| R = Readable    | bit                                       | W = Writable     | bit             | U = Unimplemented bit, read as '0' |                 |                    |         |

| -n = Value at P | OR                                        | '1' = Bit is set |                 | '0' = Bit is cle                   | ared            | x = Bit is unknown |         |

|                 |                                           |                  |                 |                                    |                 |                    |         |

| bit 15-9        | Unimplemen                                | ted: Read as '   | 0'              |                                    |                 |                    |         |

| bit 8-0         | PLLDIV<8:0>                               | : PLL Feedba     | ck Divisor bits | (also denoted                      | as 'M', PLL mul | tiplier)           |         |

|                 | 111111111 =                               | = 513            |                 |                                    |                 |                    |         |

|                 | •                                         |                  |                 |                                    |                 |                    |         |

|                 | •                                         |                  |                 |                                    |                 |                    |         |

|                 | •                                         |                  |                 |                                    |                 |                    |         |

|                 | 000110000 <b>= 50 (default)</b>           |                  |                 |                                    |                 |                    |         |

|                 |                                           |                  |                 |                                    |                 |                    |         |

|                 | •                                         |                  |                 |                                    |                 |                    |         |

|                 | 000000010 =<br>000000001 =<br>000000000 = | = 3              |                 |                                    |                 |                    |         |

|                 |                                           |                  |                 |                                    |                 |                    |         |

### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

## 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### REGISTER 11-16: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38 (dsPIC33EPXXXMC20X AND PIC24EPXXXMC20X DEVICES ONLY)

|              | -         |                                      |       |                                    |                   | -                  |                |

|--------------|-----------|--------------------------------------|-------|------------------------------------|-------------------|--------------------|----------------|

| U-0          | R/W-0     | R/W-0                                | R/W-0 | R/W-0                              | R/W-0             | R/W-0              | R/W-0          |

|              |           |                                      |       | DTCMP1R<6:                         | 0>                |                    |                |

| bit 15       |           |                                      |       |                                    |                   |                    | bit 8          |

|              |           |                                      |       |                                    |                   |                    |                |

| U-0          | U-0       | U-0                                  | U-0   | U-0                                | U-0               | U-0                | U-0            |

| —            | —         | —                                    | _     |                                    | _                 | —                  | —              |

| bit 7        |           |                                      |       |                                    |                   |                    | bit C          |

|              |           |                                      |       |                                    |                   |                    |                |

| Legend:      |           |                                      |       |                                    |                   |                    |                |

| R = Readal   | ole bit   | W = Writable bit                     |       | U = Unimplemented bit, read as '0' |                   |                    |                |

| -n = Value a | at POR    | '1' = Bit is set                     |       | '0' = Bit is cleared               |                   | x = Bit is unknown |                |

|              |           |                                      |       |                                    |                   |                    |                |

| bit 15       | Unimpleme | nted: Read as '                      | 0'    |                                    |                   |                    |                |

| bit 14-8     |           | 6:0>: Assign PV<br>1-2 for input pin |       | •                                  | on Input 1 to the | e Corresponding    | g RPn Pin bits |

|              | 1111001 = | Input tied to RP                     | 1121  |                                    |                   |                    |                |

|              | •         |                                      |       |                                    |                   |                    |                |

|              | •         |                                      |       |                                    |                   |                    |                |

|              |           | Input tied to CM                     | P1    |                                    |                   |                    |                |

|              |           | Input tied to Vss                    |       |                                    |                   |                    |                |

| bit 7-0      |           | nted: Read as '                      |       |                                    |                   |                    |                |

|              |           |                                      | -     |                                    |                   |                    |                |

| U-0    | U-0          | R/W-0      | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|--------------|------------|------------|-------|-------|-------|-------|--|

| —      | —            |            | RP43R<5:0> |       |       |       |       |  |

| bit 15 | bit 15 bit 8 |            |            |       |       |       |       |  |

|        |              |            |            |       |       |       |       |  |

| U-0    | U-0          | R/W-0      | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

| —      | —            | RP42R<5:0> |            |       |       |       |       |  |

### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —      | —   |       | RP55R<5:0> |       |       |       |       |  |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |  |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| —     | —   |       | RP54R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

| R/W-0         | R/W-0                                                                      | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                                | R/W-0          | R/W-0  | R/W-0  |  |  |

|---------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------|----------------|--------|--------|--|--|

|               | F15B                                                                       | P<3:0>                                                                                                                     |                                                | F14BP<3:0>                           |                |        |        |  |  |

| bit 15        |                                                                            |                                                                                                                            |                                                |                                      |                |        | bit 8  |  |  |

| R/W-0         | R/W-0                                                                      | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                                | R/W-0          | R/W-0  | R/W-0  |  |  |

| 1010 0        |                                                                            | P<3:0>                                                                                                                     | 1011 0                                         |                                      |                | P<3:0> | 1010 0 |  |  |

| bit 7         |                                                                            |                                                                                                                            |                                                |                                      |                |        | bit 0  |  |  |

| Legend:       |                                                                            |                                                                                                                            |                                                |                                      |                |        |        |  |  |

| R = Readabl   | e bit                                                                      | W = Writable                                                                                                               | bit                                            | U = Unimplemented bit, read as '0'   |                |        |        |  |  |

| -n = Value at | t POR                                                                      | '1' = Bit is set                                                                                                           | :                                              | '0' = Bit is cleared x = Bit is unkn |                |        | nown   |  |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte                                               | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | differ<br>4                          |                |        |        |  |  |

| bit 11-8      | F14BP<3:0:                                                                 | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val                     | ues as bits<15 | :12>)  |        |  |  |

| bit 7-4       | F13BP<3:0;                                                                 | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 3 bits (same val                     | ues as bits<15 | :12>)  |        |  |  |

| bit 3-0       | F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits<15:12>) |                                                                                                                            |                                                |                                      |                |        |        |  |  |

## REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

### 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                                           | U-0              | R/W-x         | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |  |

|---------------|-----------------------------------------------|------------------|---------------|-----------------------------------------|-------|-------|-------|--|--|--|

|               | —                                             |                  | SID10         | SID9                                    | SID8  | SID7  | SID6  |  |  |  |

| bit 15        |                                               |                  |               |                                         |       |       | bit 8 |  |  |  |

| R/W-x         | R/W-x                                         | R/W-x            | R/W-x         | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |  |

| SID5          | SID4                                          | SID3             | SID2          | SID1                                    | SID0  | SRR   | IDE   |  |  |  |

| bit 7         |                                               | •                |               |                                         |       |       | bit 0 |  |  |  |

| Legend:       |                                               |                  |               |                                         |       |       |       |  |  |  |

| R = Readabl   | e bit                                         | W = Writable     | bit           | U = Unimplemented bit, read as '0'      |       |       |       |  |  |  |

| -n = Value at | POR                                           | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |  |

|               |                                               |                  |               |                                         |       |       |       |  |  |  |

| bit 15-13     | Unimplemen                                    | ted: Read as '   | כי            |                                         |       |       |       |  |  |  |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S                     | tandard Identifi | ier bits      |                                         |       |       |       |  |  |  |

| bit 1         | SRR: Substitu                                 | ute Remote Re    | quest bit     |                                         |       |       |       |  |  |  |

|               | When IDE =                                    | ):               |               |                                         |       |       |       |  |  |  |

|               | 1 = Message                                   | will request rer | note transmis | ssion                                   |       |       |       |  |  |  |

|               | 0 = Normal m                                  | lessage          |               |                                         |       |       |       |  |  |  |

|               | When IDE = 1                                  | L:               |               |                                         |       |       |       |  |  |  |

|               | The SRR bit r                                 | must be set to ' | 1'.           |                                         |       |       |       |  |  |  |

| bit 0         | IDE: Extende                                  | d Identifier bit |               |                                         |       |       |       |  |  |  |

|               | 1 = Message                                   | will transmit Ex | tended Ident  | ifier                                   |       |       |       |  |  |  |

|               | 0 = Message will transmit Standard Identifier |                  |               |                                         |       |       |       |  |  |  |

|               |                                               |                  |               |                                         |       |       |       |  |  |  |

### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0                                | U-0   | U-0   | U-0   | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|

| —                                  | —     | —     |       | EID17                                   | EID16 | EID15 | EID14 |  |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |  |

|                                    |       |       |       |                                         |       |       |       |  |

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

| EID13                              | EID12 | EID11 | EID10 | EID9                                    | EID8  | EID7  | EID6  |  |

| bit 7                              |       |       |       |                                         |       |       | bit 0 |  |

|                                    |       |       |       |                                         |       |       |       |  |

| Legend:                            |       |       |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

| L                                  |       |       |       |                                         |       |       |       |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

| R/W-0                                                   | R/W-0 | R/W-0                                  | R/W-0           | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|---------------------------------------------------------|-------|----------------------------------------|-----------------|----------|-------|-------|-------|

| CSS15                                                   | CSS14 | CSS13                                  | CSS12           | CSS11    | CSS10 | CSS9  | CSS8  |

| bit 15                                                  |       |                                        |                 | ·        | •     | ·     | bit 8 |

|                                                         |       |                                        |                 |          |       |       |       |

| R/W-0                                                   | R/W-0 | R/W-0                                  | R/W-0           | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

| CSS7                                                    | CSS6  | CSS5                                   | CSS4            | CSS3     | CSS2  | CSS1  | CSS0  |

| bit 7                                                   | -     |                                        |                 |          | •     |       | bit ( |

|                                                         |       |                                        |                 |          |       |       |       |

| Legend:                                                 |       |                                        |                 |          |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit |       |                                        | mented bit, rea | d as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0                   |       | '0' = Bit is cleared x = Bit is unknow |                 |          | nown  |       |       |

# REGISTER 23-8: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

bit 15-0 CSS<15:0>: ADC1 Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all AD1CSSL bits can be selected by the user. However, inputs selected for scan, without a corresponding input on the device, convert VREFL.

**2:** CSSx = ANx, where x = 0-15.

## 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

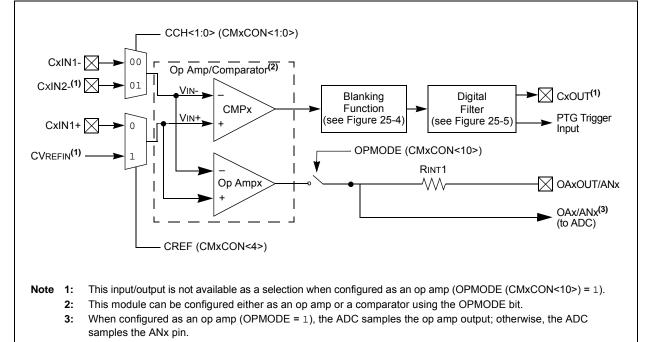

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

### FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

| Bit Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCP                    | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = Code protection is enabled for the entire program memory space                                                                                                                                                                                                                                                                                     |

| GWRP                   | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                           |

| IESO                   | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start up device with user-selected oscillator source</li> </ul>                                                                                                                                                                                           |

| PWMLOCK <sup>(1)</sup> | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                        |

| FNOSC<2:0>             | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Fast RC Oscillator with Divide-by-16 (FRCDIV16)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use<br>011 = Primary Oscillator with PLL module (XT + PLL, HS + PLL, EC + PLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |

| FCKSM<1:0>             | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                           |

| IOL1WAY                | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                                        |

| OSCIOFNC               | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                                          |

| POSCMD<1:0>            | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                           |

| FWDTEN                 | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                                                 |

| WINDIS                 | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                                              |

| PLLKEN                 | PLL Lock Enable bit<br>1 = PLL lock is enabled<br>0 = PLL lock is disabled<br>nly available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.                                                                                                                                                                                                                                                                                           |

## TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

| DC CHARACT       | ERISTICS                  |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |        |            |           |  |

|------------------|---------------------------|------|-------------------------------------------------------|--------|------------|-----------|--|

| Parameter<br>No. | Тур.                      | Max. | Units                                                 |        | Conditions |           |  |

| Operating Cur    | rent (IDD) <sup>(1)</sup> |      |                                                       |        |            |           |  |

| DC20d            | 9                         | 15   | mA                                                    | -40°C  |            |           |  |

| DC20a            | 9                         | 15   | mA                                                    | +25°C  | 3.3V       | 10 MIPS   |  |

| DC20b            | 9                         | 15   | mA                                                    | +85°C  | 3.3V       | 10 1011-5 |  |

| DC20c            | 9                         | 15   | mA                                                    | +125°C |            |           |  |

| DC22d            | 16                        | 25   | mA                                                    | -40°C  |            |           |  |

| DC22a            | 16                        | 25   | mA                                                    | +25°C  | 3.3∨       | 20 MIPS   |  |

| DC22b            | 16                        | 25   | mA                                                    | +85°C  | 3.3V       | 20 MIF 3  |  |

| DC22c            | 16                        | 25   | mA                                                    | +125°C |            |           |  |

| DC24d            | 27                        | 40   | mA                                                    | -40°C  |            |           |  |

| DC24a            | 27                        | 40   | mA                                                    | +25°C  | 3.3V       | 40 MIPS   |  |

| DC24b            | 27                        | 40   | mA                                                    | +85°C  | 3.3V       | 40 1011-5 |  |

| DC24c            | 27                        | 40   | mA                                                    | +125°C |            |           |  |

| DC25d            | 36                        | 55   | mA                                                    | -40°C  |            |           |  |

| DC25a            | 36                        | 55   | mA                                                    | +25°C  | 3.3V       | 60 MIPS   |  |

| DC25b            | 36                        | 55   | mA                                                    | +85°C  | 3.3V       | OU IVIIPS |  |

| DC25c            | 36                        | 55   | mA                                                    | +125°C | 7          |           |  |

| DC26d            | 41                        | 60   | mA                                                    | -40°C  |            |           |  |

| DC26a            | 41                        | 60   | mA                                                    | +25°C  | 3.3V       | 70 MIPS   |  |

| DC26b            | 41                        | 60   | mA                                                    | +85°C  |            |           |  |

#### TABLE 30-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) {NOP(); } statement

- · JTAG is disabled

### TABLE 30-54: OP AMP/COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| AC CHARACTERISTICS |        |                | $ \begin{array}{l} \mbox{Standard Operating Conditions (see Note 2): 3.0V to 3.6V \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |  |  |  |  |  |

|--------------------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Param.             | Symbol | Characteristic | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| VR310              | TSET   | Settling Time  | — 1 10 μs (Note 1)                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

**Note 1:** Settling time is measured while CVRR = 1 and CVR<3:0> bits transition from '0000' to '1111'.

2: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-55: OP AMP/COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |            |     |               |  |  |  |

|--------------------|--------|--------------------------------------------|------------------------------------------------------|------|------------|-----|---------------|--|--|--|

| Param<br>No.       | Symbol | Characteristics                            | Min. Typ. Max. Units Conditions                      |      |            |     |               |  |  |  |

| VRD310             | CVRES  | Resolution                                 | CVRSRC/24                                            | _    | CVRSRC/32  | LSb |               |  |  |  |

| VRD311             | CVRAA  | Absolute Accuracy <sup>(2)</sup>           | —                                                    | ±25  | _          | mV  | CVRSRC = 3.3V |  |  |  |

| VRD313             | CVRSRC | Input Reference Voltage                    | 0                                                    | _    | AVDD + 0.3 | V   |               |  |  |  |

| VRD314             | CVRout | Buffer Output<br>Resistance <sup>(2)</sup> | _                                                    | 1.5k | _          | Ω   |               |  |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: Parameter is characterized but not tested in manufacturing.

### TABLE 31-11: INTERNAL RC ACCURACY

| AC CH        | ARACTERISTICS                      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stateOperating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |     |     |       |                                           | herwise stated) |  |

|--------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-------------------------------------------|-----------------|--|

| Param<br>No. | Characteristic                     | Min                                                                                                                              | Тур | Max | Units | Conditions                                |                 |  |

|              | LPRC @ 32.768 kHz <sup>(1,2)</sup> |                                                                                                                                  |     |     |       |                                           |                 |  |

| HF21         | LPRC                               | -30                                                                                                                              | _   | +30 | %     | $-40^{\circ}C \leq TA \leq +150^{\circ}C$ | VDD = 3.0-3.6V  |  |

Note 1: Change of LPRC frequency as VDD changes.

2: LPRC accuracy impacts the Watchdog Timer Time-out Period (TwDT). See Section 27.5 "Watchdog Timer (WDT)" for more information.